Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматизации экспериментальных исследований как для регистрации, так и для непосредственного ввода аналоговой информации в ЭВМ.

Цель изобретения - повышение быстродействия устройства.

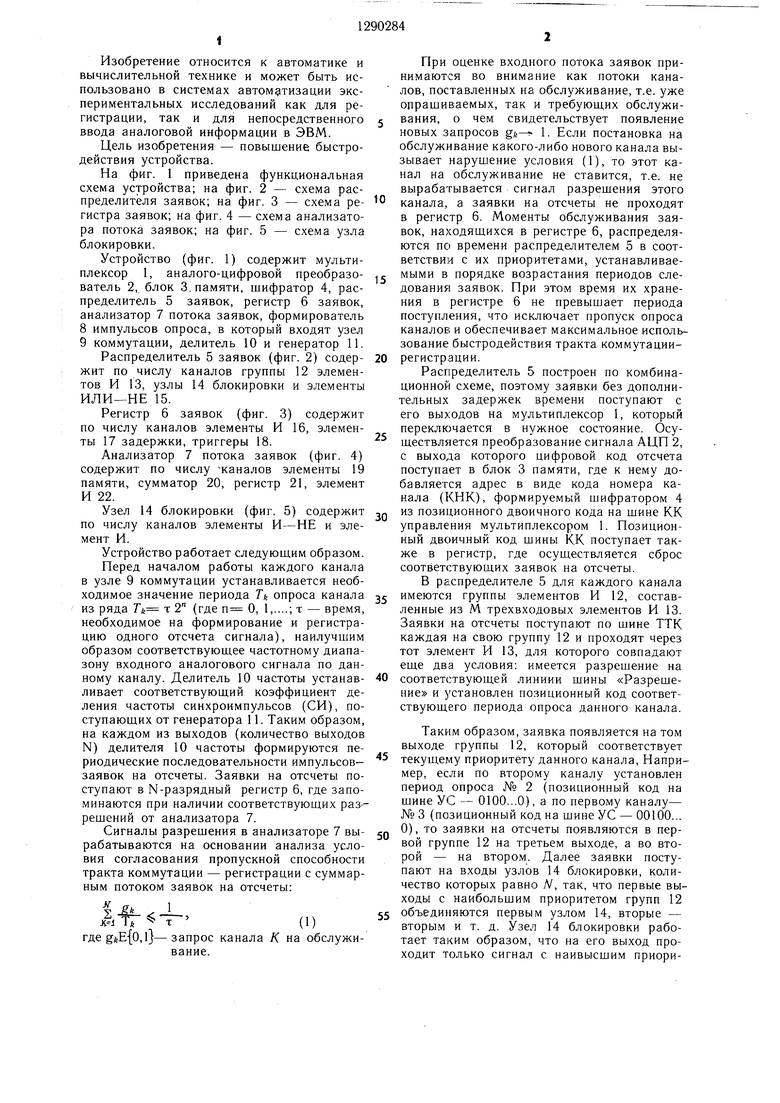

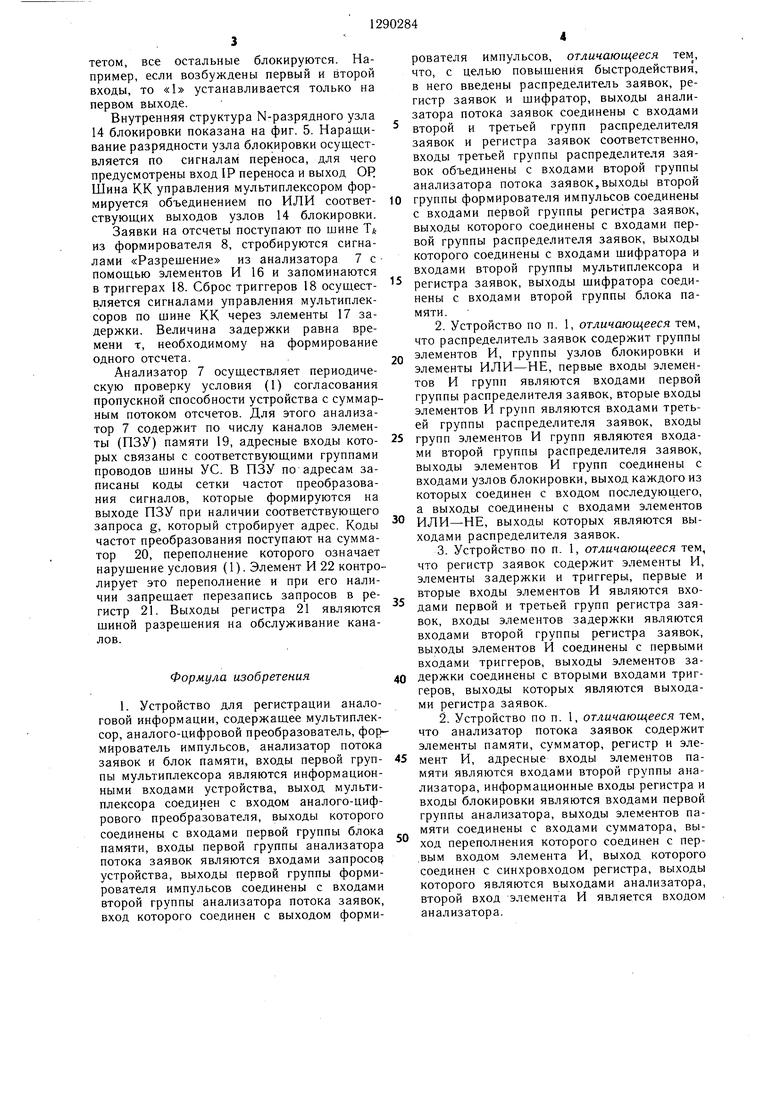

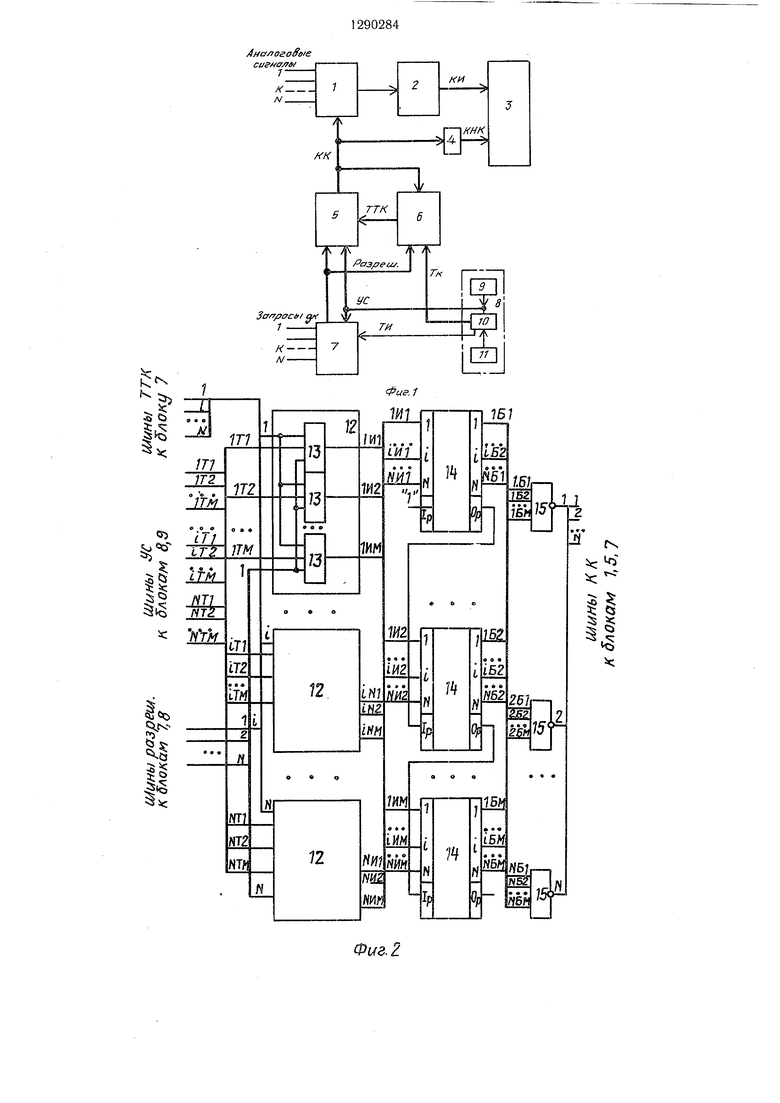

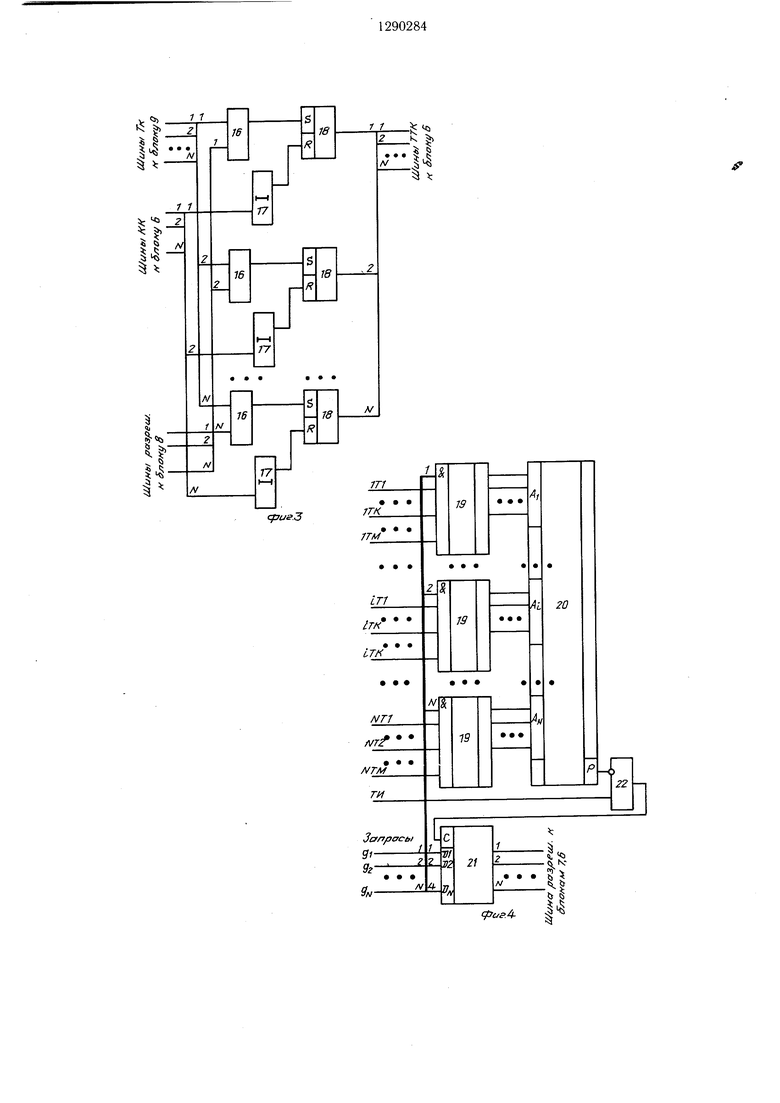

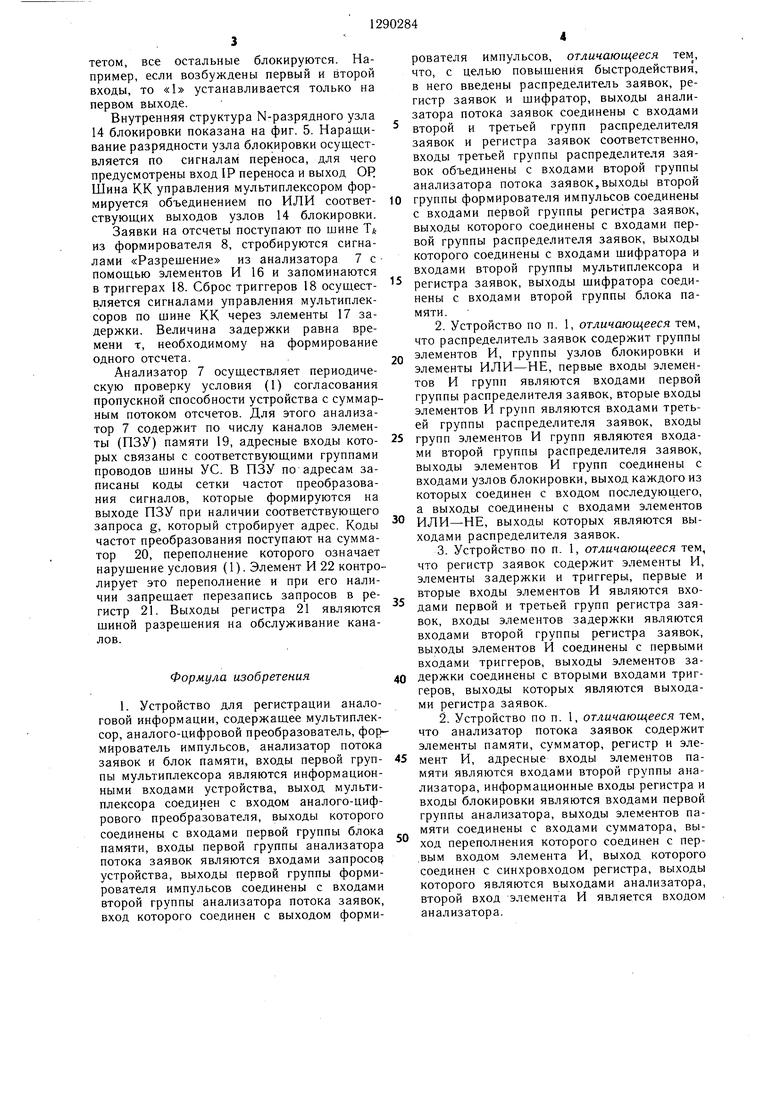

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - схема распределителя заявок; на фиг. 3 - схема регистра заявок; на фиг. 4 - схема анализатора потока заявок; на фиг. 5 - схема узла блокировки.

Устройство (фиг. 1) содержит мультиплексор 1, аналого-цифровой преобразователь 2, блок 3. памяти, шифратор 4, распределитель 5 заявок, регистр 6 заявок, анализатор 7 потока заявок, формирователь

8импульсов опроса, в который входят узел

9коммутации, делитель 10 и генератор 11.

Распределитель 5 заявок (фиг. 2) содержит по числу каналов группы 12 элементов И 13, узлы 14 блокировки и элементы ИЛИ-НЕ 15.

Регистр 6 заявок (фиг. 3) содержит по числу каналов элементы И 16, элементы 17 задержки, триггеры 18.

Анализатор 7 потока заявок (фиг. 4) содержит по числу жаналов элементы 19 памяти, сумматор 20, регистр 21, элемент И 22.

Узел 14 блокировки (фиг. 5) содержит по числу каналов элементы И-НЕ и элемент И.

Устройство работает следующим образом.

Перед началом работы каждого канала в узле 9 коммутации устанавливается необходимое значение периода Tk опроса канала из ряда 7fe т 2 (где п О, 1,....; т - время, необходимое на формирование и регистрацию одного отсчета сигнала), наилучшим образом соответствуюш,ее частотному диапазону входного аналогового сигнала по данному каналу. Делитель 10 частоты устанавливает соответствующий коэффициент деления частоты синхроимпульсов (СИ), поступающих от генератора 11. Таким образом, на каждом из выходов (количество выходов N) делителя 10 частоты формируются периодические последовательности импульсов- заявок на отсчеты. Заявки на отсчеты поступают в N-разрядный регистр 6, где запоминаются при наличии соответствующих раз-решений от анализатора 7.

Сигналы разрешения в анализаторе 7 вырабатываются на основании анализа условия согласования пропускной способности тракта коммутации - регистрации с суммарным потоком заявок на отсчеты:

(1)

гдедАЕ{0,1}-запрос канала К на обслуживание.

При оценке входного потока заявок принимаются во внимание как потоки каналов, поставленных на обслуживание, т.е. уже опрашиваемых, так и требующих обслужи- вания, о чем свидетельствует появление новых запросов 1. Если постановка на обслуживание какого-либо нового канала вызывает нарушение условия (1), то этот канал на обслуживание не ставится, т.е. не вырабатывается сигнал разрешения этого

канала, а заявки на отсчеты не проходят

в регистр 6. Моменты обслуживания заявок, находящихся в регистре 6, распределяются по времени распределителем 5 в соответствии с их приоритетами, устанавливаег мыми в порядке возрастания периодов следования заявок. При этом время их хранения в регистре 6 не превышает периода поступления, что исключает пропуск опроса каналов и обеспечивает максимальное использование быстродействия тракта коммутации0 регистрации.

Распределитель 5 построен по комбинационной схеме, поэтому заявки без дополнительных задержек времени поступают с его выходов на мультиплексор 1, который переключается в нужное состояние. Осу ществляется преобразование сигнала АЦП 2, с выхода которого цифровой код отсчета поступает в блок 3 памяти, где к нему добавляется адрес в виде кода номера канала (КНК), формируемый шифратором 4

Q из позиционного двоичного кода на шине КК управления мультиплексором 1. Позиционный двоичный код шины КК поступает также в регистр, где осуществляется сброс соответствующих заявок на отсчеты.

В распределителе 5 для каждого канала

5 имеются группы элементов И 12, составленные из М трехвходовых элементов И 13. Заявки на отсчеты поступают по шине ТТК каждая на свою группу 12 и проходят через тот элемент И 13, для которого совпадают еще два условия: имеется разрешение на

0 соответствующей линиии шины «Разрешение и установлен позиционный код соответствующего периода опроса данного канала.

Таким образом, заявка появляется на том выходе группы 12, который соответствует

5 текущему приоритету данного канала. Например, если по второму каналу установлен период опроса № 2 (позиционный код на шине УС - 0100...0), а по первому каналу- № 3 (позиционный код на шине УС - 00100... 0), то заявки на отсчеты появляются в первой группе 12 на третьем выходе, а во второй - на втором. Далее заявки поступают на входы узлов 14 блокировки, количество которых равно N, так, что первые выходы с наибольшим приоритетом групп 12

5 объединяются первым узлом 14, вторые - вторым и т. д. Узел 14 блокировки работает таким образом, что на его выход проходит только сигнал с наивысшим приори0

тетом, все остальные блокируются. Например, если возбуждены первый и второй входы, то «1 устанавливается только на первом выходе.

Внутренняя структура N-разрядного узла 14 блокировки показана на фиг. 5. Наращивание разрядности узла блокировки осуществляется по сигналам переноса, для чего предусмотрены вход IP переноса и выход OR Шина КК управления мультиплексором форрователя импульсов, отличающееся тем, что, с целью повышения быстродействия, в него введены распределитель заявок, регистр заявок и шифратор, выходы анализатора потока заявок соединены с входами второй и третьей групп распределителя заявок и регистра заявок соответственно, входы третьей группы распределителя заявок объединены с входами второй группы анализатора потока заявок,выходы второй

мируется объединением по ИЛИ соответ- 10 группы формирователя импульсов соединены ствующих выходов узлов 14 блокировки.с входами первой группы регистра заявок

Заявки на отсчеты поступают по шине Т; из формирователя 8, стробируются сигналами «Разрешение из анализатора 7 с

помощью элементов И 16 и запоминаются.. .,

в триггерах 18. Сброс триггеров 18 осущест- регистра заявок, выходы шифратора соеди вляется сигналами управления мультиплек-нены с входами второй группы блока пасоров по шине КК через элементы 17 задержки. Величина задержки равна времени т, необходимому на формирование одного отсчета.

Анализатор 7 осуществляет периодическую проверку условия (1) согласования пропускной способности устройства с суммарным потоком отсчетов. Для этого анализатор 7 содержит по числу каналов элементы (ПЗУ) памяти 19, адресные входы кото- 25 групп элементов И групп являются входа- рых связаны с соответствующими группамими второй группы распределителя заявок,

выходы элементов И групп соединены с

входами узлов блокировки, выход каждого из которых соединен с входом последующего,

. а выходы соединены с входами элементов

запроса g, который стробирует адрес. Коды ИЛИ-НЕ, выходы которых являются вы- частот преобразования поступают на сумма-ходами распределителя заявок,

тор 20, переполнение которого означает нарушение условия (1). Элемент И 22 контролирует это переполнение и при его наливыходы которого соединены с входами первой группы распределителя заявок, выходы которого соединены с входами шифратора и входами второй группы мультиплексора и

мяти.

2. Устройство по п. 1, отличающееся тем, что распределитель заявок содержит группы 2Q элементов И, группы узлов блокировки и элементы ИЛИ-НЕ, первые входы элементов И групп являются входами первой группы распределителя заявок, вторые входы элементов И групп являются входами третьей группы распределителя заявок, входы

проводов шины УС. В ПЗУ по адресам записаны коды сетки частот преобразования сигналов, которые формируются на выходе ПЗУ при наличии соответствующего

3. Устройство по п. 1, отличающееся тем, что регистр заявок содержит элементы И, элементы задержки и триггеры, первые и вторые входы элементов И являются входами первой и третьей групп регистра заявок, входы элементов задержки являются входами второй группы регистра заявок, выходы элементов И соединены с первыми входами триггеров, выходы элементов за- 40 держки соединены с вторыми входами триггеров, выходы которых являются выходами регистра заявок.

чии запрещает перезапись запросов в регистр 21. Выходы регистра 21 являются шиной разрешения на обслуживание каналов.

Формула изобретения

3. Устройство по п. 1, отличающееся тем что регистр заявок содержит элементы И, элементы задержки и триггеры, первые и вторые входы элементов И являются входами первой и третьей групп регистра заявок, входы элементов задержки являются входами второй группы регистра заявок, выходы элементов И соединены с первыми входами триггеров, выходы элементов за- 40 держки соединены с вторыми входами триггеров, выходы которых являются выходами регистра заявок.

2. Устройство по п. 1, отличающееся тем, что анализатор потока заявок содержит элементы памяти, сумматор, регистр и эле1. Устройство для регистрации аналоговой информации, содержащее мультиплексор, аналого-цифровой преобразователь, формирователь импульсов, анализатор потока

заявок и блок памяти, входы первой груп- 45 мент И, адресные входы элементов папы мультиплексора являются информацион-мяти являются входами второй группы анаными входами устройства, выход мультиплексора соединен с входом аналого-цифрового преобразователя, выходы которого соединены с входами первой группы блока памяти, входы первой группы анализатора потока заявок являются входами запросов устройства, выходы первой группы формирователя импульсов соединены с входами второй группы анализатора потока заявок, вход которого соединен с выходом формирователя импульсов, отличающееся тем, что, с целью повышения быстродействия, в него введены распределитель заявок, регистр заявок и шифратор, выходы анализатора потока заявок соединены с входами второй и третьей групп распределителя заявок и регистра заявок соответственно, входы третьей группы распределителя заявок объединены с входами второй группы анализатора потока заявок,выходы второй

.. .,

регистра заявок, выходы шифратора соеди нены с входами второй группы блока павыходы которого соединены с входами первой группы распределителя заявок, выходы которого соединены с входами шифратора и входами второй группы мультиплексора и

групп элементов И групп являются входа- ми второй группы распределителя заявок,

мяти.

2. Устройство по п. 1, отличающееся тем, что распределитель заявок содержит группы элементов И, группы узлов блокировки и элементы ИЛИ-НЕ, первые входы элементов И групп являются входами первой группы распределителя заявок, вторые входы элементов И групп являются входами третьей группы распределителя заявок, входы

ИЛИ-НЕ, выходы которых являются вы- ходами распределителя заявок,

3. Устройство по п. 1, отличающееся тем, что регистр заявок содержит элементы И, элементы задержки и триггеры, первые и вторые входы элементов И являются входами первой и третьей групп регистра заявок, входы элементов задержки являются входами второй группы регистра заявок, выходы элементов И соединены с первыми входами триггеров, выходы элементов за- держки соединены с вторыми входами триггеров, выходы которых являются выходами регистра заявок.

2. Устройство по п. 1, отличающееся тем, что анализатор потока заявок содержит элементы памяти, сумматор, регистр и элемент И, адресные входы элементов памяти являются входами второй группы ана0

лизатора, информационные входы регистра и входы блокировки являются входами первой группы анализатора, выходы элементов памяти соединены с входами сумматора, выход переполнения которого соединен с пер- ,вым входом элемента И, выход которого соединен с синхровходом регистра, выходы которого являются выходами анализатора, второй вход элемента И является входом анализатора.

Ана/зогоЗо/е

5й 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1552196A1 |

| Устройство для организации очереди | 1982 |

|

SU1070554A1 |

| Устройство для ввода аналоговой информации | 1986 |

|

SU1377848A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Система коммутации | 1986 |

|

SU1359783A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Устройство для организации очередности приема информации | 1983 |

|

SU1128255A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

Изобретение относится к средствам регистрации аналоговых сигналов в цифровой форме с целью последующей обработки на ЭВМ. Изобретение позволяет повысить быстродействие устройства за счет уменьшения затрат времени на управление коммутацией информационных входов. Указанная задача решается путем введения в известное устройство распределителя заявок, регистра заявок и шифратора. 3 з.п.ф-лы 5 ил. ts:) со о сх 4

«У5

Jo«0

S

iS

:s i§

CD

tx§5c§

i§

I S

Ui fx i ioФи.2

1

U

1

:

S-«u

1 1

1

i:

I

Л/

I

жод IP

переноса

фиг. 5

O-l

л/

8er/jfoff

OP

freppHoca

| 0 |

|

SU402865A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для регистрации аналоговой информации | 1982 |

|

SU1164548A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-02-15—Публикация

1985-07-05—Подача