Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автома- тизации исследований как для регистрации, так и для непосредственного ввода аналоговой информации в ЭВМ.

Целью изобретения является повышение быстродействия устройства за счет снижения затрат времени на управление трактом коммутации, преобразования и регистрации отсчетов.

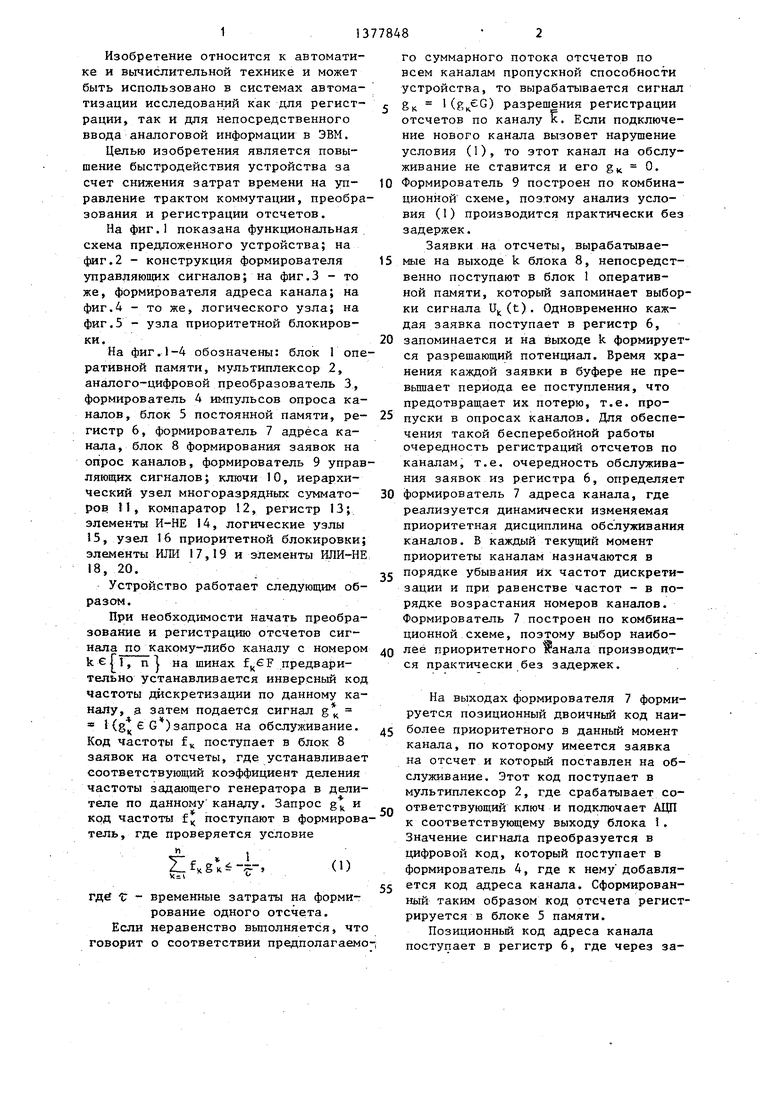

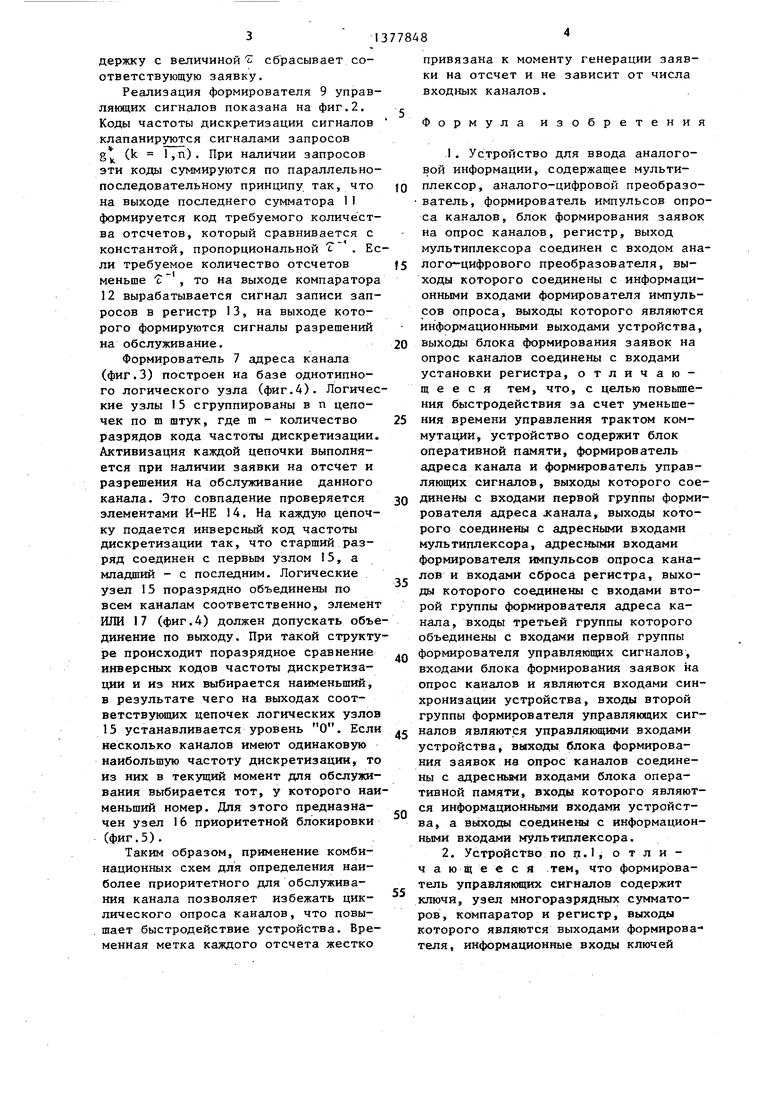

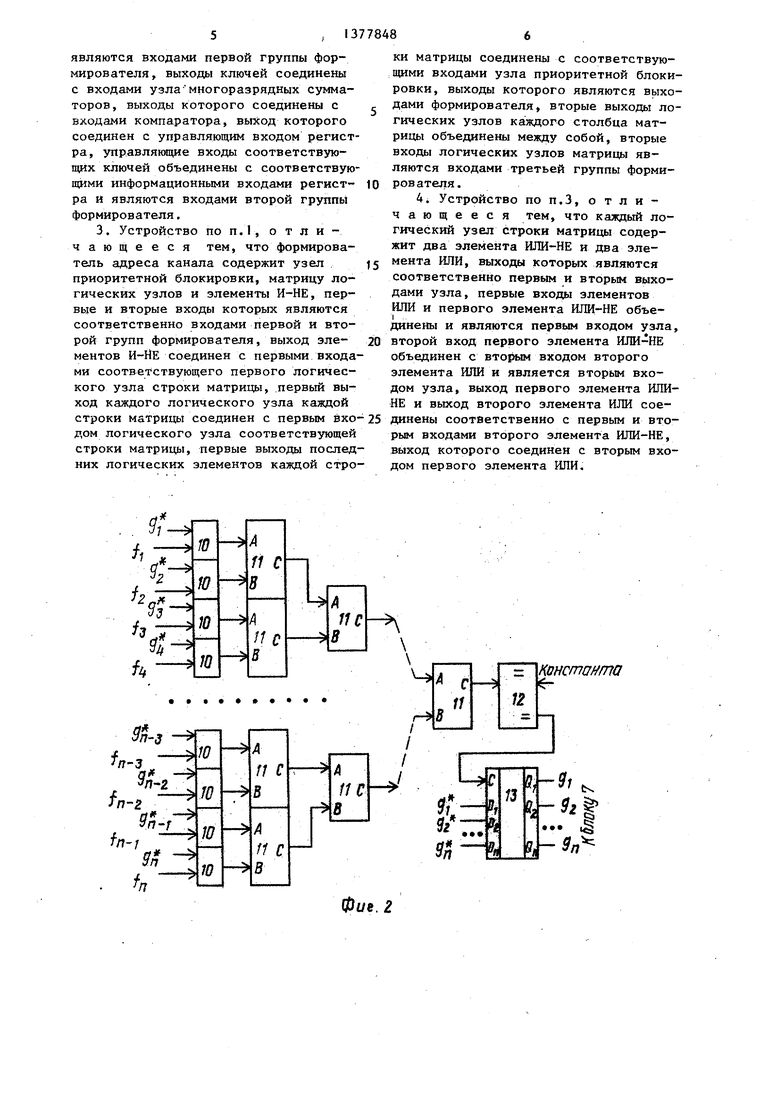

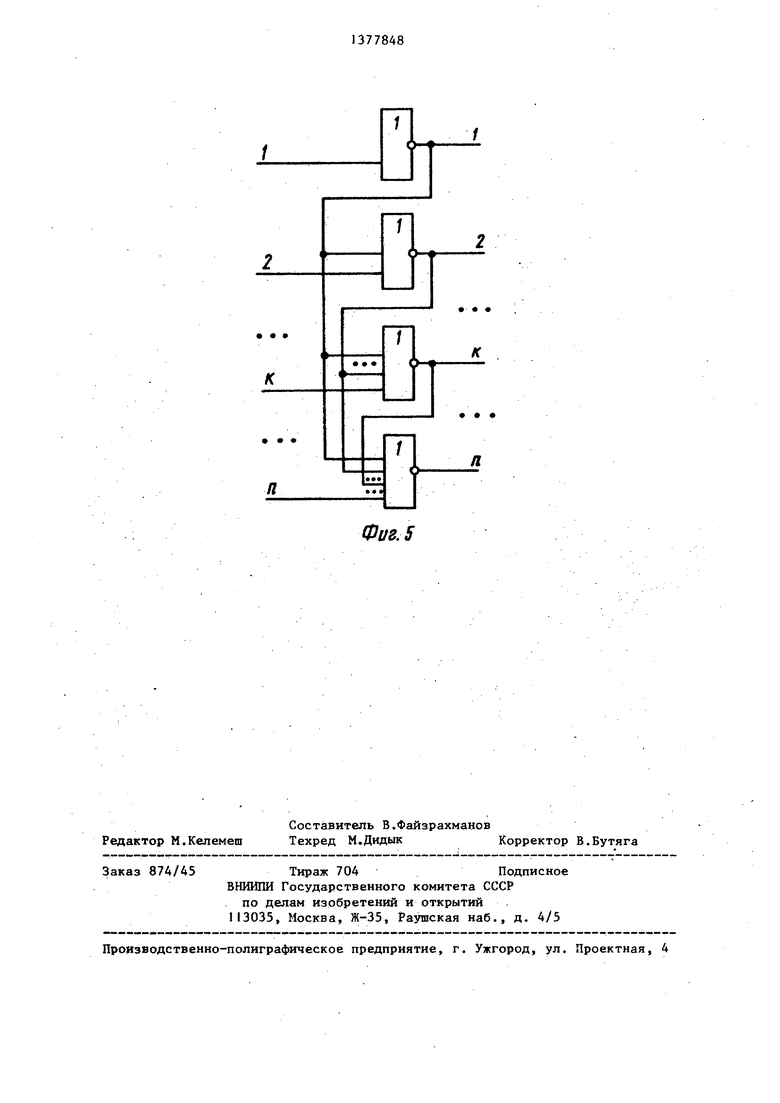

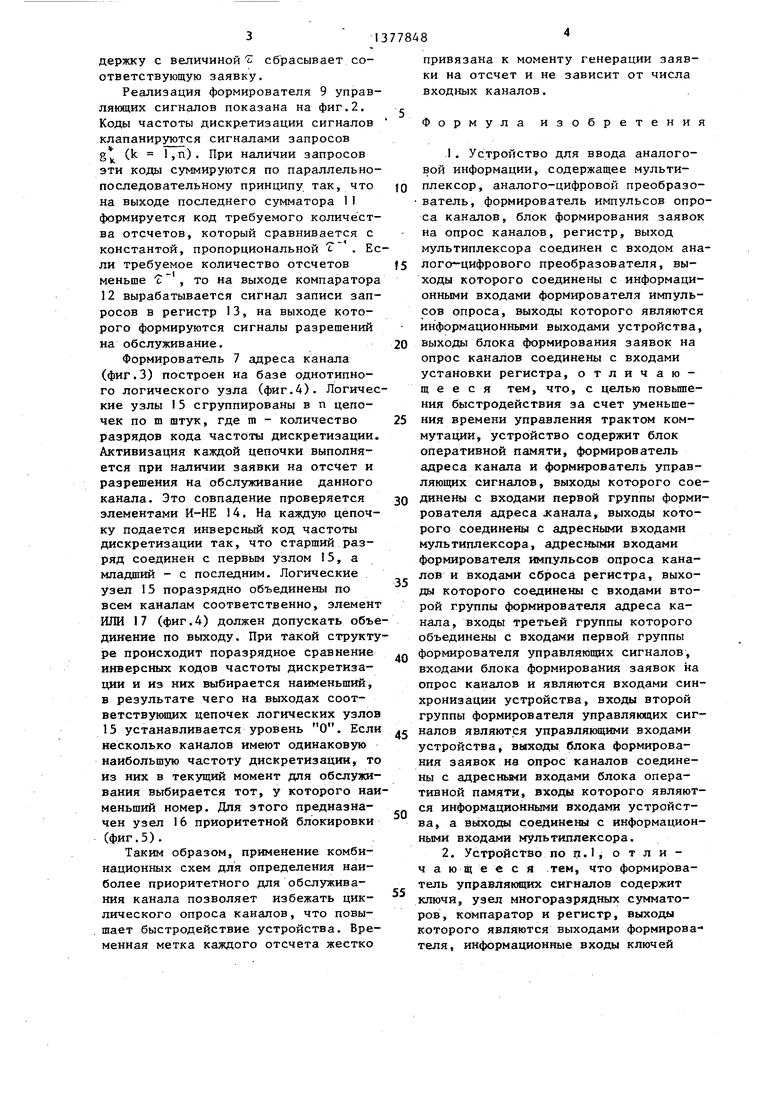

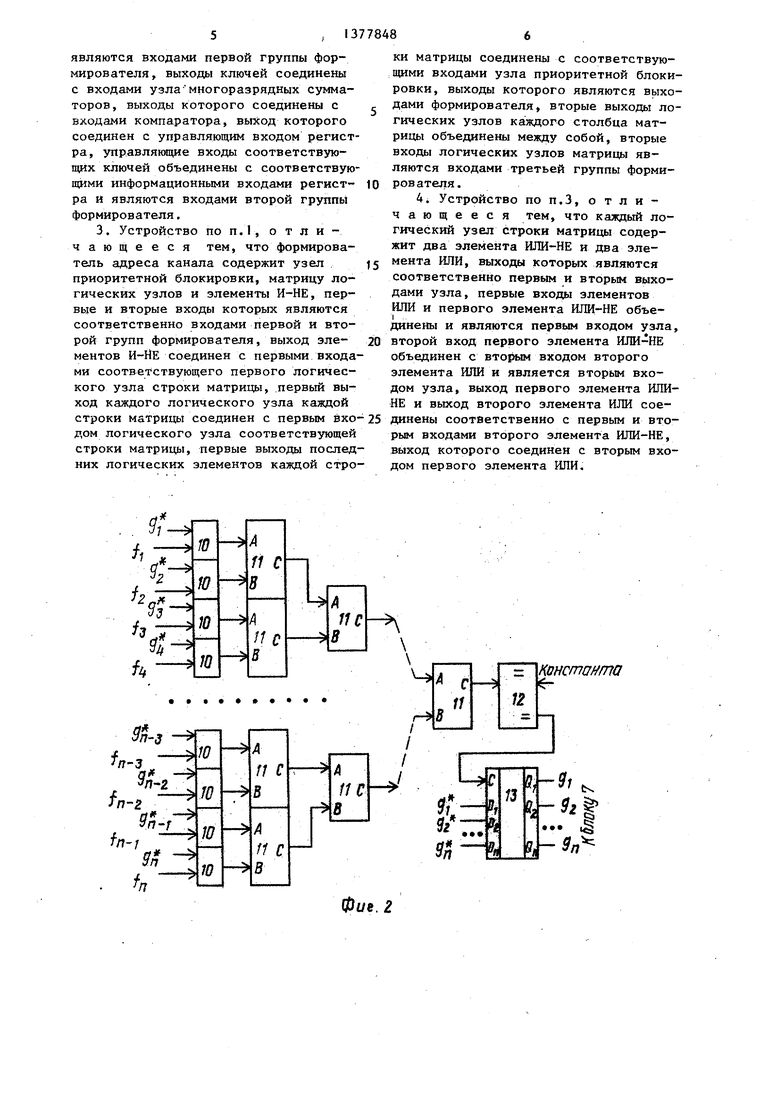

На фиг.1 показана функциональная схема предложенного устройства; на фиг.2 - конструкция формирователя управляющих сигналов; на фиг.3 - то же, формирователя адреса канала; на фиг.4 - то же, логического узла; на фиг.5 - узла приоритетной блокировки.

На фиг.1-4 обозначены: блок Г оперативной памяти, мультиплексор 2, аналого-цифровой преобразователь 3, формирователь 4 импульсов опроса каналов, блок 5 постоянной памяти, регистр 6, формирователь 7 адреса канала, блок 8 формирования заявок на опрос каналов, формирователь 9 управляющих сигналов; ключи 10, иерархический узел многоразрядных суммато- роэ t1, компаратор 12, регистр 13; элементы И-НЕ I4, логические узлы 55, узел 16 приоритетной блокировки; элементы ИЛИ 17,19 и элементы ИПИ-НЕ 18, 20.

Устройство работает следующим образом.

При необходимости начать преобразование и регистрацию отсчетов сигнала цо какому-либо каналу с номером , п I на шинах предварительно устанавливается инверсный код частоты дискретизации по данному ка- наЛу, 3 затем подается сигнал g I( G)запроса на обслуживание. Код частоты f поступает в блок 8 заявок на отсчеты, где устанавливает соответствующий коэффициент деления частоты задающего генератора в делителе по данному каналу. Запрос g и код частоты f поступают в формирователь, где проверяется условие м

Ilf.

(1)

где т - временные затраты на формирование одного отсчета. Если неравенство вьтолняется, что говорит о соответствии предполагаемого суммарного потока отсчетов по всем каналам пропускной способности устройства, то вырабатывается сигнал

8к () разрешения регистрации отсчетов по каналу k. Если подключение нового канала вызовет нарушение условия (1), то этот канал на обслуживание не ставится и его Вк О

Формирователь 9 построен по комбинационной схеме, поэтому анализ условия (1) производится практически без задержек.

Заявки на отсчеты, вырабатываемые на выходе k блока 8, непосредственно поступают в блок 1 оперативной памяти, который запоминает выборки сигнала U(t). Одновременно каждая заявка поступает в регистр 6,

запоминается и на выходе k формируется разрешающий потенциал. Время хранения каждой заявки в буфере не пре- вьш1ает периода ее поступления, что предотвращает их потерю, т.е. пропуски в опросах каналов. Для обеспечения такой бесперебойной работы очередность регистрации отсчетов по каналам, т.е. очередность обслуживания заявок из регистра 6, определяет

формирователь 7 адреса канала, где реализуется динамически изменяемая приоритетная дисциплина обслуживания каналов. В каждый текущий момент приоритеты каналам назначаются в

порядке убывания их частот дискретизации и при равенстве частот - в порядке возрастания номеров каналов. Формирователь 7 построен по комбинационной схеме, поэтому выбор наиболее приоритетного Канала производится практически без задержек.

На выходах формирователя 7 формируется позиционный двоичный код наиболее приоритетного в данный момент канала, по которому имеется заявка на отсчет и который поставлен на обслуживание. Этот код поступает в мультиплексор 2, где срабатывает соответствующий ключ и подключает АЦП к соотвеТствукщему выходу блока 1. Значение сигнала преобразуется в цифровой код, который поступает в формирователь 4, где к нему добавляется код адреса канала. Сформированный таким образом код отсчета регистрируется в блоке 5 памяти.

Позиционньй код адреса канала поступает в регистр 6, где через задержку с величиной 6 сбрасывает соответствующую заявку.

Реализация формирователя 9 управляющих сигналов показана на фиг.2. Коды частоты дискретизации сигналов клапанирутотся сигналами запросов g (k 1,п). При наличии запросов эти коды суммируются по параллельно- последовательному принципу так, что на выходе последнего сумматора 11 формируется код требуемого количества отсчетов, который сравнивается с константой, пропорциональной t . Если требуемое количество отсчетов меньше с , то на выходе компаратора 12 вырабатывается сигнал записи запросов в регистр 13, на выходе которого формируются сигналы разрешений на обслуживание.

Формирователь 7 адреса канала (фиг.З) построен на базе однотипного логического узла (фиг.4). Логические узлы 5 сгруппированы в п цепочек по m штук, где m - количество разрядов кода частоты дискретизации. Активизация каждой цепочки выполняется при наличии заявки на отсчет и разрешения на обслуживание данного канала. Это совпадение проверяется элементами И-НЕ 14. На каждую цепочку подается инверсный код частоты дискретизации так, что старший разряд соединен с первым узлом 15, а младший - с последним. Логические узел 15 поразрядно объединены по всем каналам соответственно, элемент ИЛИ 17 (фиг.4) должен допускать объединение по вьпсоду. При такой структуре происходит поразрядное сравнение инверсных кодов частоты дискретизации и из них выбирается наименьший, в результате чего на выходах соответствующих цепочек логических узлов 15 устанавливается уровень О. Если несколько каналов имеют одинаковую наибольшую частоту дискретизации, то из них в текущий момент для обслуживания выбирается тот, у которого наименьший номер. Для этого предназначен узел 16 приоритетной блокировки (фиг.5).

Таким образом, применение комбинационных схем для определения наиболее приоритетного для обслуживания канала позволяет избежать циклического опроса каналов, что повышает быстродействие устройства. Временная метка каждого отсчета жестко

привязана к моменту генерации заявки на отсчет и не зависит от числа входных каналов.

Формула изобретения

1. Устройство для ввода аналоговой информации, содержащее мульти- 0 плексор, аналого-цифровой преобразо- ватель, формирователь импульсов опроса каналов, блок формирования заявок на опрос каналов, регистр, выход мультиплексора соединен с входом ана- 5 лого цифрового преобразователя, выходы которого соединены с информационными входами формирователя импульсов опроса, выходы которого являются информационными выходами устройства, 0 выходы блока формирования заявок на опрос каналов соединены с входами установки регистра, отличающееся тем, что, с целью повьш1е- ния быстродействия за счет уменьше- 5 ния времени управления трактом коммутации, устройство содержит блок оперативной памяти, формирователь адреса канала и формирователь управляющих сигналов, выходы которого сое- 0 динены с входами первой группы формирователя адреса лсанала, выходы которого соединены с адресными входами мультиплексора, адресными входами формирователя импульсов опроса кана- лов и входами сброса регистра, выходы которого соединены с входами второй группы формирователя адреса канала, входы третьей группы которого объединены с входами первой группы 0 формирователя управляюш 1х сигналов, входами блока формирования заявок на опрос каналов и являются входами синхронизации устройства, входы второй группы формирователя управляющих сиг- 5 налов являются управляющими входами устройства, вмходы блока формирования заявок на оп$юс каналов соединены с адресньми входами блока оперативной памяти, входы которого являются информационными входами устройства, а выхо;рл соединегал с информационными входами мультиплексора.

2. Устройство по П.1, о т л и - чающееся тем, что формирователь управляющих сигналов содержит КЛЮЧИ, узел многоразрядных сумматоров, кЬмпаратор и регистр, выходы которого являются выходами формирова- теля, информационные входы ключей

0

5

являются входами первой группы формирователя, выходы ключей соединены с входами узла многоразрядных сумматоров , выходы которого соединены с входами компаратора, выход которого соединен с управляющим входом регистра, управляющие входы соответствующих ключей объединены с соответствующими информационными входами регистра и являются входами второй группы формирователя.

3. Устройство по п,1, о т л и - чающееся тем, что формирователь адреса канала содержит узел приоритетной блокировки, матрицу логических узлов и элементы И-НЕ, первые и вторые входы которых являются соответственно входами первой и второй групп формирователя, выход элементов И-НЕ соединен с первыми входами соответствующего первого логического узла строки матрицы, первый выход каждого логического узла каждой

ки матрицы соединены с соответствующими входами узла приоритетной блокировки, выходы которого являются выхо- дами формирователя, вторые выходы логических узлов ка ждого столбца матрицы объединены между собой, вторые входы логических узлов матрицы являются входами третьей группы формирователя.

4. Устройство по п.3, отличающееся тем, что каждый логический узел строки матрицы содержит два элемента ИЛИ-НЕ и два элемента ИЛИ, выходы которых являются соответственно первым и вторым выходами узла, первые входы элементов

ИЛИ и первого элемента ИЛИ-НЕ объеI .,

динены и являются первым входом узла,

второй вход первого элемента ИЛИ-НЕ объединен с вторым входом второго элемента ИЛИ и является вторым входом узла, выход первого элемента ИЛИ- НЕ и выход второго элемента ИЛИ сое

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации аналоговой информации | 1982 |

|

SU1164548A1 |

| Устройство для регистрации аналоговой информации | 1985 |

|

SU1290284A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1290325A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Устройство для управления обменом информацией | 1990 |

|

SU1783525A1 |

| Устройство для сигнализации | 1986 |

|

SU1481824A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| УСТРОЙСТВО ТЕЛЕИЗМЕРЕНИЯ ДЛЯ РАССРЕДОТОЧЕННЫ | 1973 |

|

SU386423A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматизации исследований для регистрации или ввода в ЭВМ аналоговой информации. Цель изобретения - повьипе- ние быстродействия устройства за АномШие CUtWMf счет уменьшения времени управления трактом коммутации. Устройство содержит блок 1 оперативной памяти, мультиплексор 2, аналого-цифровой преобразователь 3, формирователь 4 импульсов опроса каналов, блок 5 постоянной памяти, регистр 6, формирователь 7 адреса канала, блок формирования 8 заявок на опрос каналов, формирователь 9 управлякяцих сигналов. Значение аналогового сигнала по соответствующему каналу заносится в блок 1 оперативной памяти при генерации заявки на обслуживание. Формирователь 9 управляющих сигналов оценивает загруженность устройства заявками и ставит запрос на обслуживание при наличии заявки. Адрес наиболее приоритетного для обслуживания канала вырабатывает формирователь 7. Выбор канала производится по комбинационному принципу. 3 з.п. ф-лы, 5 iin. s (Л

строки матрицы соединен с первым вхо- 25динены соответственно с первым и втодом логического узла соответствующейрым входами второго элемента ИЛИ-НЕ,

строки матрицы, первые выходы послед-выход которого соединен с вторым вхоних логических элементов каждой стро-дом первого элемента ИЛИ,

Фие.2

П

«о

фце.З

Фог

Фив. 5

| Устройство для регистрации информации | 1978 |

|

SU824180A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для регистрации аналоговой информации | 1982 |

|

SU1164548A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-02-28—Публикация

1986-06-26—Подача