изобретение относится к -области автоматики и вычислительной техники и может быть использовано в устройствах управления очередностью обслуживания .

Известно устройство для организации очередности, содержащее элемент ИЛИ, два счетчика, узел сравнения, причем группа входов элемента ИЛИ является группой запросных входов устройства, первый выход каждого счетчика соединен с соответствую11.им входом узла сравнения. Устройство также содержит блок памяти, шифратор и дешифратор, причем адресный- выход шифратора соединен с адресным входом блока памяти, блокирующий выход шифратора соединен с первым входом первого счетчика, выход- элемента ИЛИ соединен -с вторым входом первого счетчика, первый выход узла сравнения соедин,ен с третьим входом.первого счетчика, второй выход узла сравнения соединен с перэым входом счетчика, второй вход которого является управляющим входом устройства, второй выход- каждого счетчика соединен с соответствующим входом блока памяти, выход блока памяти соединен с входом дешифратора , группа выходов дешифратора является группой выходов устройства, а группа входов ишфратора - группой запросных входов устройства LI И.

Однако данное устройство не обеспечивает организации очереди при одновременном поступлении, нескольких сигналов заявок, т.е. поступившие заявки остаются без обслуживания, что снижает надежность работы устройства.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для управления очередностью об-служивания запросов, содержащее регйстр, группу элементов И, распределитель управлк.ощих сигналов, коммутатор, блок памяти, причем - группа информационных входов, регистра является группой информационных входов устройства, разрядные - выходы регистра соединены с первыми входами соответствующих элементов И группы, группа выходов блока памяти соединена с первой группой входов коммутатора, первый выход распределителя управляющих сигналов соединен с входом комг утатора,. второй выход распределителя управляющих сигналов соединен с входом блока памяти. Устройство также, содержит генератор импульсов, шифратор, дешифратор, два эдемвн.т-а ИЛИ, счетчик, блок разделения сигналов, причем второй вход каждого элемента И группы соединен с соответствующим выходом генератора импульсов, третий вход-каждого элемента И группы соединен с третьим выходом распределителя управляющих сигналов выходы элементов И группы соединены с группой входов шифратора, группа выходов шифрато- ра соединен с второй группой входов коммутатора, первая группа выходов коммутатора соединена с группой входов блока памяти, группа выходов элементов И группы соединена с группой управляющих входов регистра и с входами первого элемента ИЛИ, выход первого элемента ИЛИ соедине.н с первым входом коммутатора, с суммирующим входом счетчика и с первым входом блока разделения сигналов, группа входов второго элемента ИЛИ. является группой управляющих входов устройства, выход второго элемента ИЛИ соединен с вторым входом блока разделения сигналов, выход которого соединен с вторым входом распределителя управляющих сигналов и с вычитающим входом счетчика, управляющий вход устройства соединен с управляющим входом счетчика и с третьим входом распределителя управляющих сигналов, выход счетчика соединен с четвертым входом распределителя управд,яющих сигналов, группа выходов дешифратора является группой информационных.выходов устройства 2..

. Однако известное устройство не защищено от помех, наличие которых на входах устройства запоминается в регистре и обрабатывается как поступающие запросы. Кроме того, в случае присутствия на входах устройства запросов, длительность которых превышает цикл работы опросового генератора, возникает повторная обработка одних и тех же запросов, что также приводит к ложной регистрации запросов, снижающей достоверность передаваемой устройством информации.

Целью изобретения является повышение надежности.

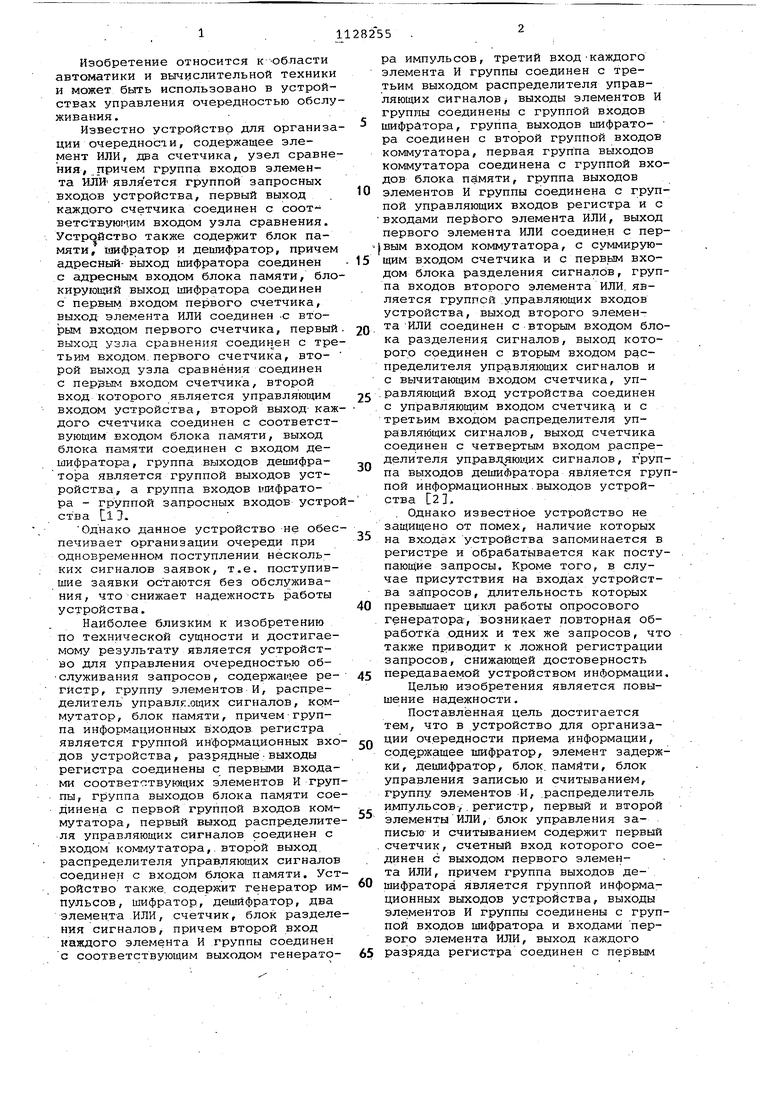

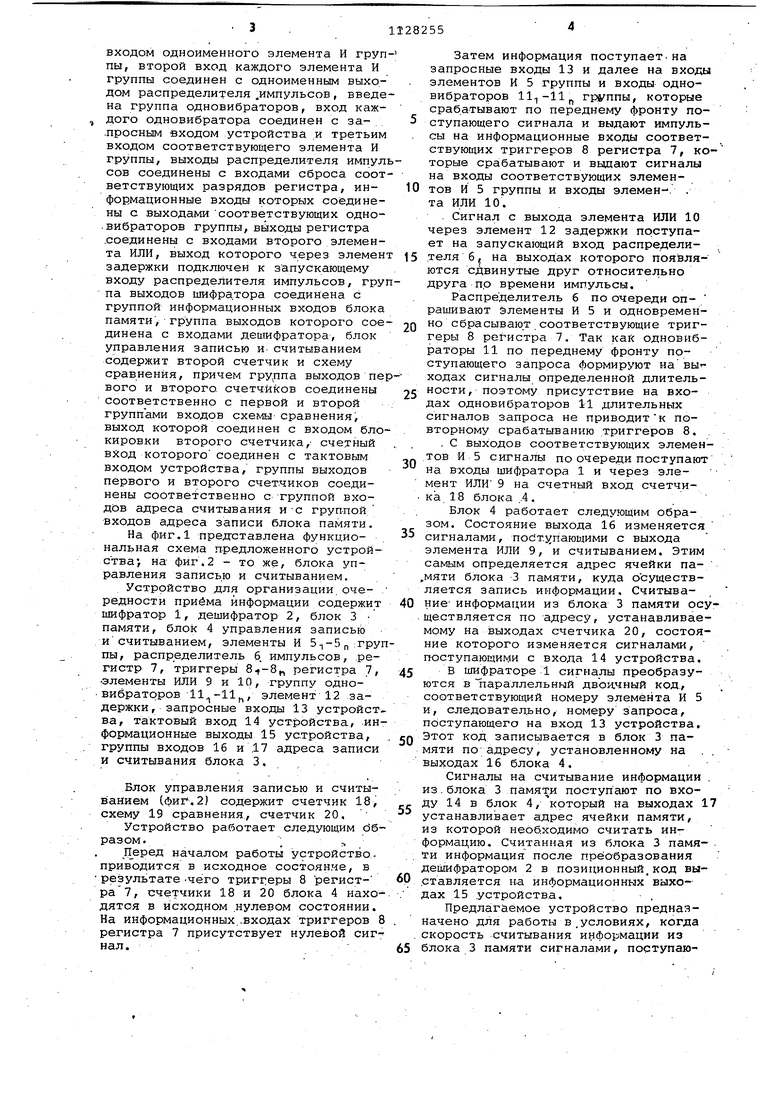

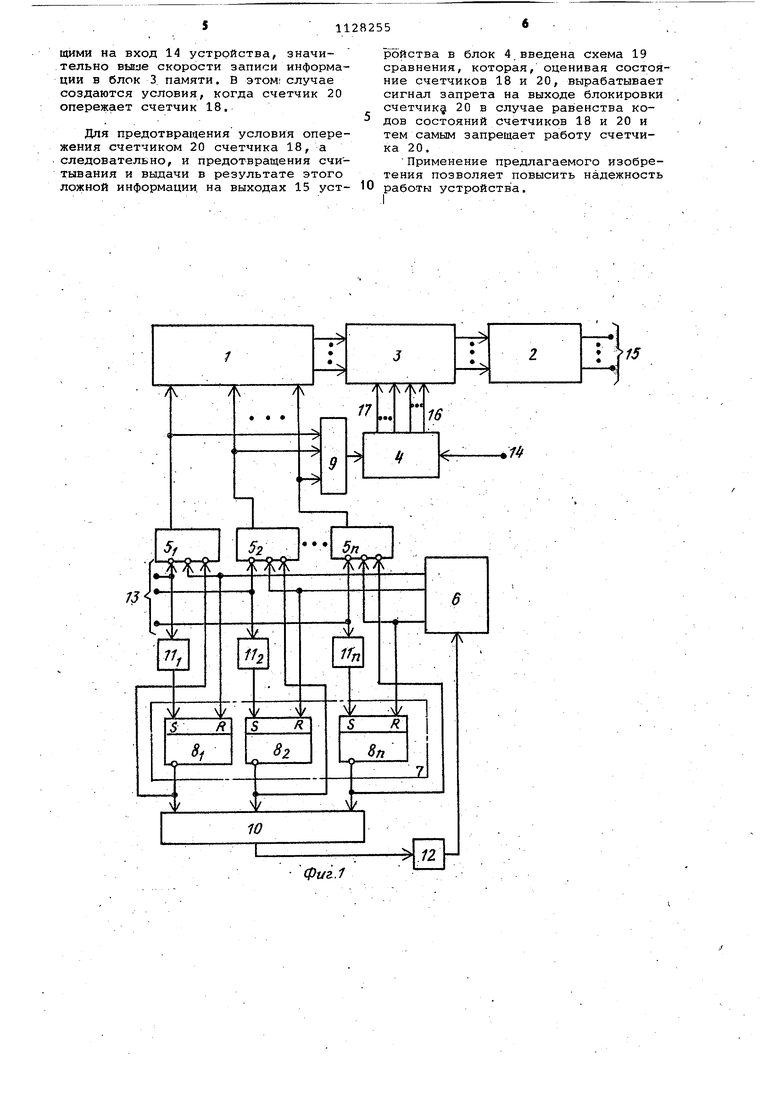

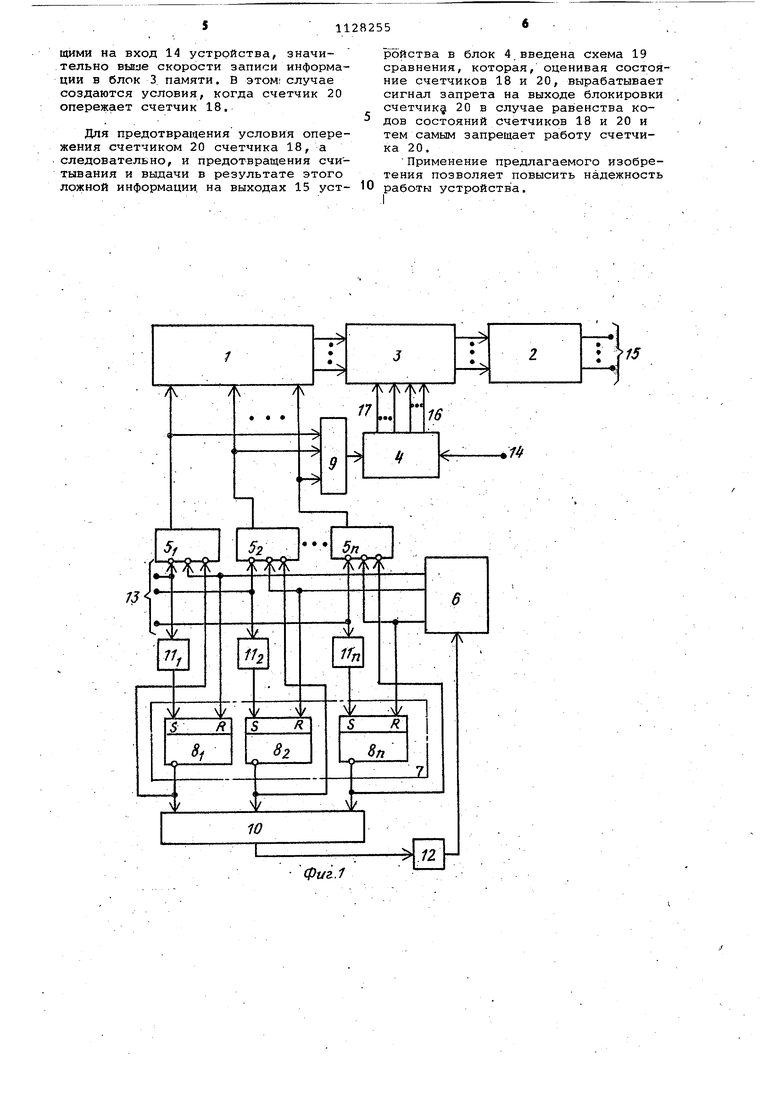

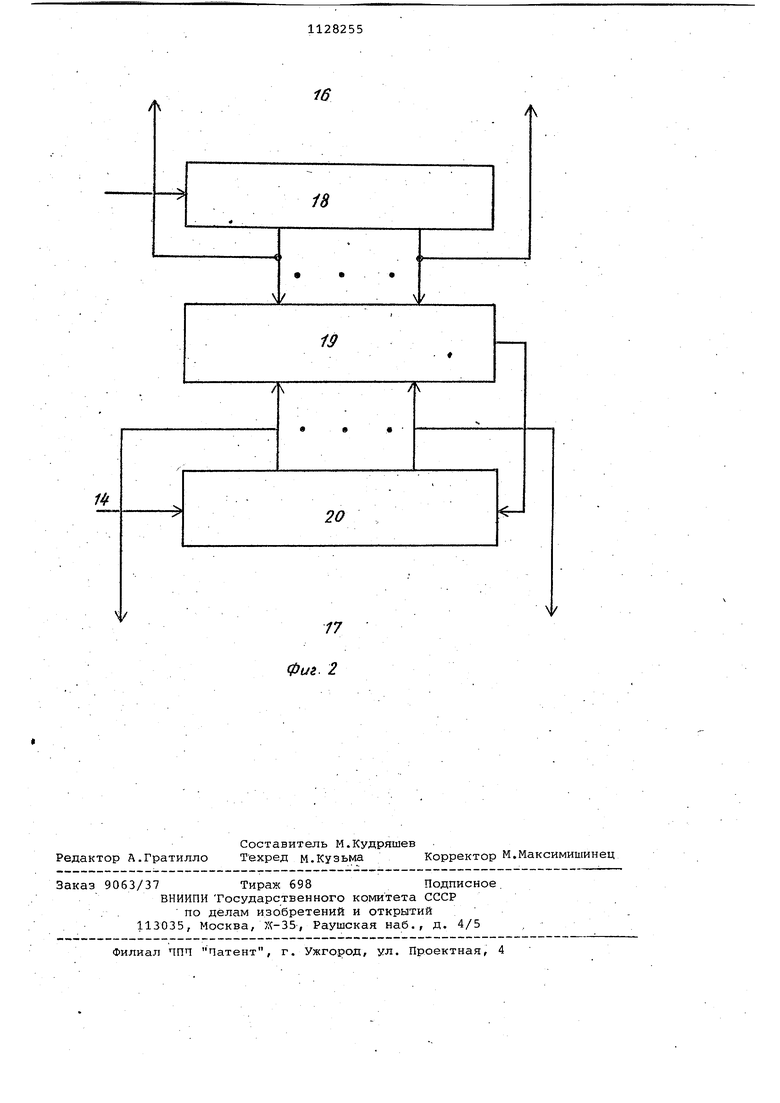

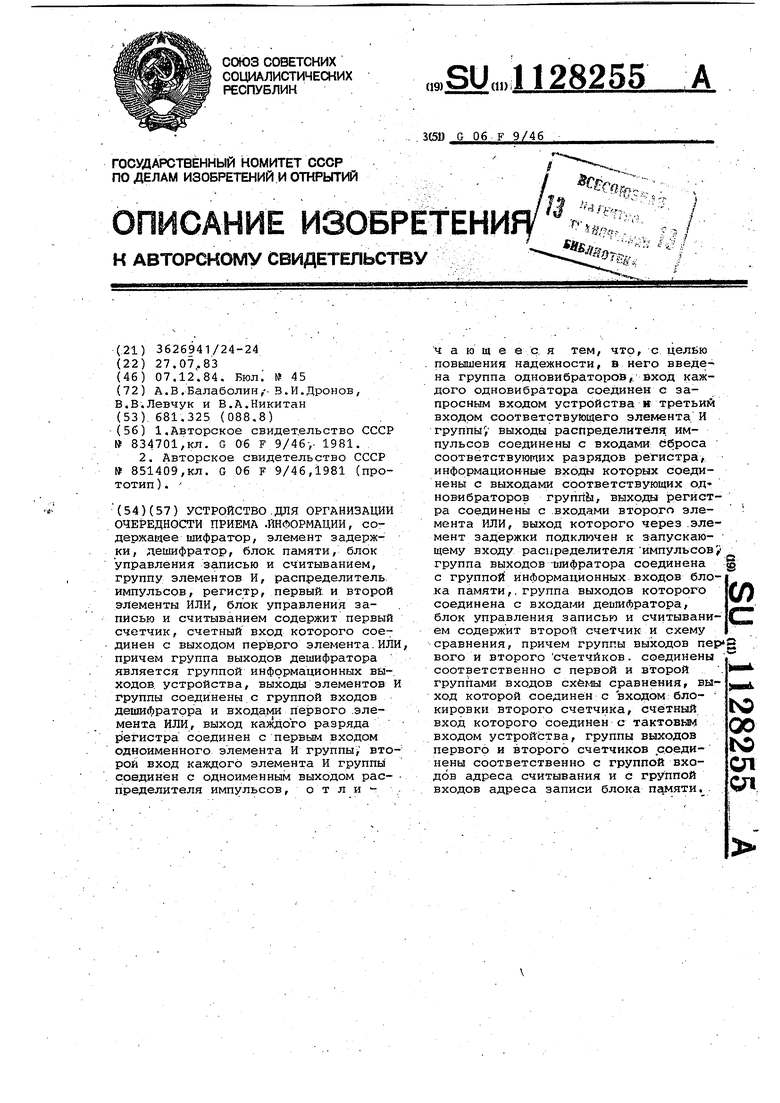

Поставленная цель достигается тем, что в устройство для организации очередности приема информации, соде ржащее шифратор, элемент задержки, дешифратор, блок, памйти, блок управления записью и считыванием, группу элементов И, .распределитель импульсов-,. регистр, первый и второй элементы ИЛИ, блок управления записью- и считыванием содержит первый счетчик, счетный вход которого соединен с выходом первого элемента ИЛИ, причем группа выходов дешифратора является группой информационных выходов устройства, выходы элементов И группы соединены с группой входов шифратора и входами первого элемента ИЛИ, выход каждого разряда регистра соединен с первым входом одноименного элемента И труп пы, второй вход каждого элемента И группы соединен с одноименным выходом распределителя .импульсов, введе на группа одновибраторов, вход каж,, дого одновибратора соединен с за.просным входом устройства и третьим входом соответствующего элемента И группы, выходы распределителя импул сов соединены с входами сброса соот ветствующих разрядов регистра, информационные входы которых соединены с выходами соответствующих одно.вибраторов группы, вйходы регистра .соединены с входами второго элемента ИЛИ, выход которого через элемен задержки подключен к запускающему входу распределителя импульсов, гру па выходов шифра.тора соединена с группой информационных входов блока памяти, группа выходов которого сое динена с входами дешифратора, блок управления записью и- считыванием содержит второй счетчик и схему сравнения, причем выходов пе вого и второго, счетчиков соединены соответственно с первой и второй группами входов схемы-сравнения, выход которой соединен с входом бло кировки второго счетчика,- вход которого соединен с тактовым входом устройства, группы выходов первого и второго счетчиков соединены соответственно с группой входов адреса считывания и-с груп-пой входов адреса записи блока памяти. На фиг.1 Представлена функциональная схема предложенного устройства на фиг.2 - то же, блока управления записью и считыванием. Устройство для организации, очередности приёма информации содержит шифратор 1, дешифратор 2, блок 3 памяти, блок 4 управления записью исчитыванием, элементы И 5-,-5п:Гру пы, распределитель б. импульсов, регистр 7, триггеры регистра 7, элементы ИЛИ 9 и 10, группу одно- вибраторов , элемент 12 задержки, запросные входы 13 устройст ва, тактовый вход 14 устройства, ин формационные выходы 15 устройства, . группы входов 16 и .17 адреса записи и считывания блока 3. Блок управления записью и считыванием (фиг. 2) содержит счетчик 18, схему 19 сравнения, счетчик 20. Устройство работает следующим d6 разом.; г, . Перед началом работы устройствоприводится в исходное состояние, в результате -чего тригг еры 8 регистра 7, счетчики 18 и 20 блока 4 нахо дятся в исходном .нулевом состоянии. На информационных..входах триггеров регистра 7 присутствует нулевой сигнал. Затем информация поступает-на запросные входы 13 и далее на входы элементов И 5 группы и входы одновибраторов грйппы, которые сраба-тывают по переднему фронту поступающего сигнала и выдают импульсы на информационные входы соответствующих триггеров 8 регистра 7, которые срабатывают и вьщают сигналы на входы соответствующих элементов И 5 группы и входы элемен-. . та ИЛИ 10. . Сигнал с выхода элемента ИЛИ 10 через элемент 12 задержки поступает на запускающий вход распредели.теля 6, на выходах которого появляются сдвинутые друг относительно друга п.о времени импульсы. Распределитель 6 по очереди опрашивают Элементы И 5 и одновременно сбрасывают соответствующие триггеры 8 регистра 7. Так как одновибраторы 11 по переднему фронту поступающего запроса формируют на вы ходах сигналы определенной длительности, поэтому присутствие на входах одновибраторов 11 длительных сигналов запроса не приводитк повторному срабатыванию триггеров 8. . . С выходов соответствующих элементов И 5 сигналы по очереди поступают на в-ходы шифратора 1 и через элемент ИЛИ 9 на счетный вход счетчика 18 блока ..4. Блок 4 работает следующим образом. Состояние выхода 16 изменяется сигналами, пойт.з пающими с выхода элемента ИЛИ 9, и считыванием. Этим самым определяется адрес ячейки памяти блока 3 памяти, куда осуществляется запись информации. Считыва- , ние информации из блока 3 памяти осуществляется по адресу, устанавливаемому на выходах счетчика 20, состояние которого изменяется сигналами, поступающими с входа 14 устройства. В шифраторе 1 сигналы преобразуются в параллельный двоичный код., соответствующий номеру элемента И 5 и, следовательно, номеру запроса, поступающего на вход 13 устройства. Этот код записывается в блок 3 памяти по адресу, установленному на . . выходах 16 блока 4. Сигналы на считывание информации . из.блока 3 памяти поступают по входу 14 в блок 4,Который на выходах 17 устанавливает адрес ячейки памяти, из которой необходимо считать информацию. Считанная из блока 3 памяти информация после преобразования дешифратором 2 в позиционный,код вы.ставляется на информационных выходах 15 .устройств.а. - . Предлагаемое устройство предназначено для работы в .условиях, когда скорость считывания информации из блока 3 памяти сигналами, поступающими на вход 14 устройства, значительно выше скорости записи информации в блок 3. памяти. В этом; случае создаются условия, когда счетчик 20 опережает счетчик 18.

Для предотвращения условия опережения счетчиком 20 счетчика 18, а следовательно, и предотвращения считывания и выдачи в результате этого ложной информации, на выходах 15 устройства в блок 4 введена схема 19 сравнения, которая, оценивая состояние счетчиков 18 и 20, вырабатывает сигнал запрета на выходе блокировки счетчику 20 в случае равенства кодов состояний счетчиков 18 и 20 и тем самым запрещает работу счетчика 20.

Применение предлагаемого изобретения позволяет повысить надежность работы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для организации очереди | 1982 |

|

SU1070554A1 |

| Устройство для оценки состояния каналов в симплексных системах связи | 1987 |

|

SU1554749A2 |

| Устройство для обслуживания запросов | 1985 |

|

SU1264174A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1562921A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1989 |

|

SU1686453A1 |

| Устройство обмена информацией между ЭВМ и абонентами | 1990 |

|

SU1835545A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство для оценки состояния каналов в симплексных системах связи | 1984 |

|

SU1197124A1 |

Ё

-О-О-О

AlNA. AA/v

Фиг.

16

/

l

f

/20

N/

17 фиг. 2

l

f

/

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления очеред-НОСТью ОбСлужиВАНия зАпРОСОВ | 1979 |

|

SU851409A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-07—Публикация

1983-07-27—Подача