Изобретение относится к вычислительной технике и может быть использовано в графических дисплеях векторного типа.

Цель изобретения - упрощение блока синхронизации и расширение области применения его за счет обеспечения возможности осуществления режима автогенерации синхроимпульсов.

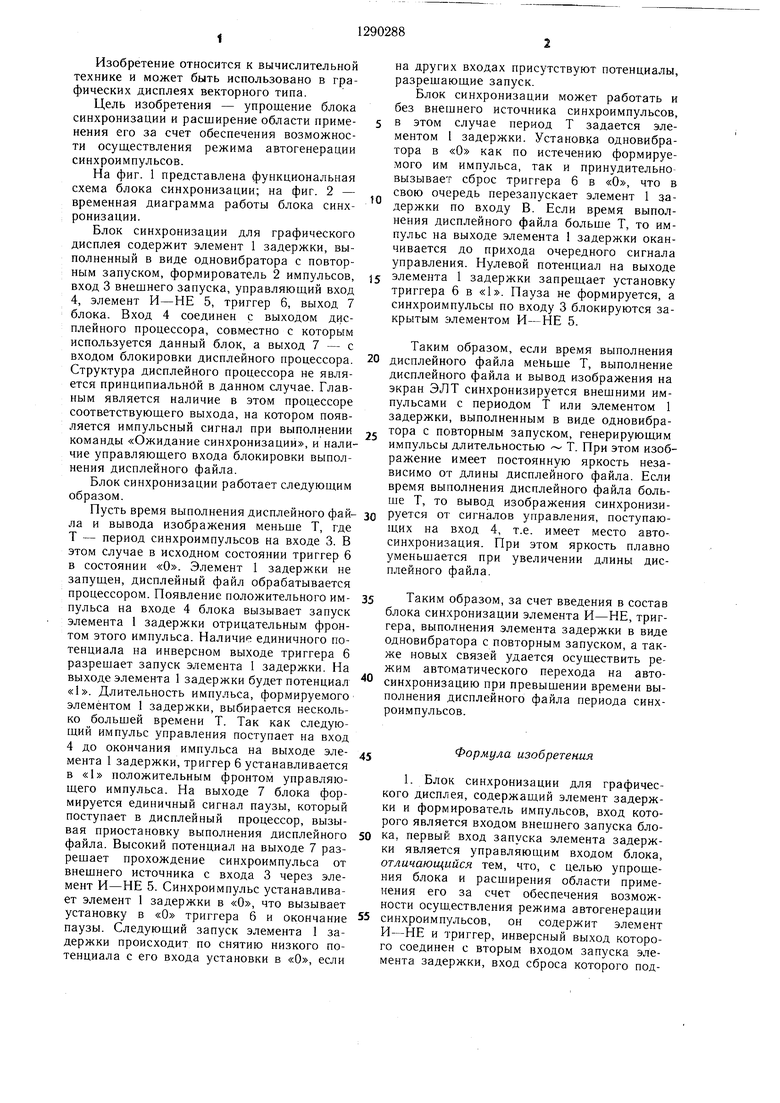

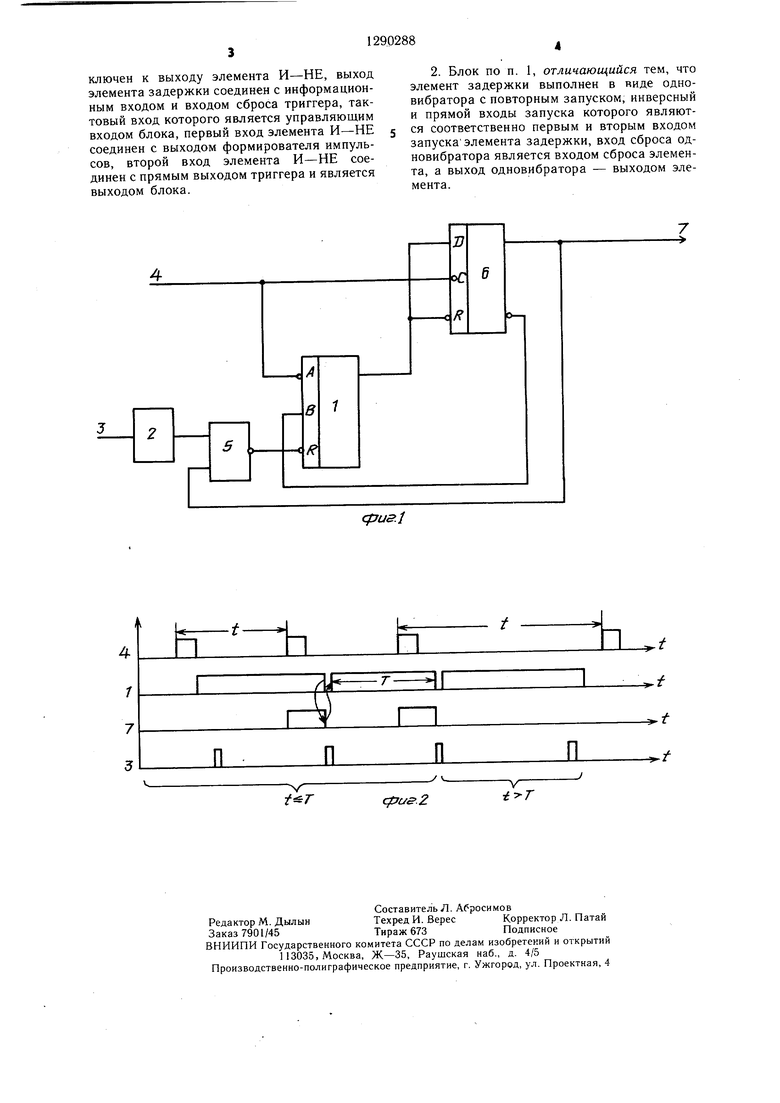

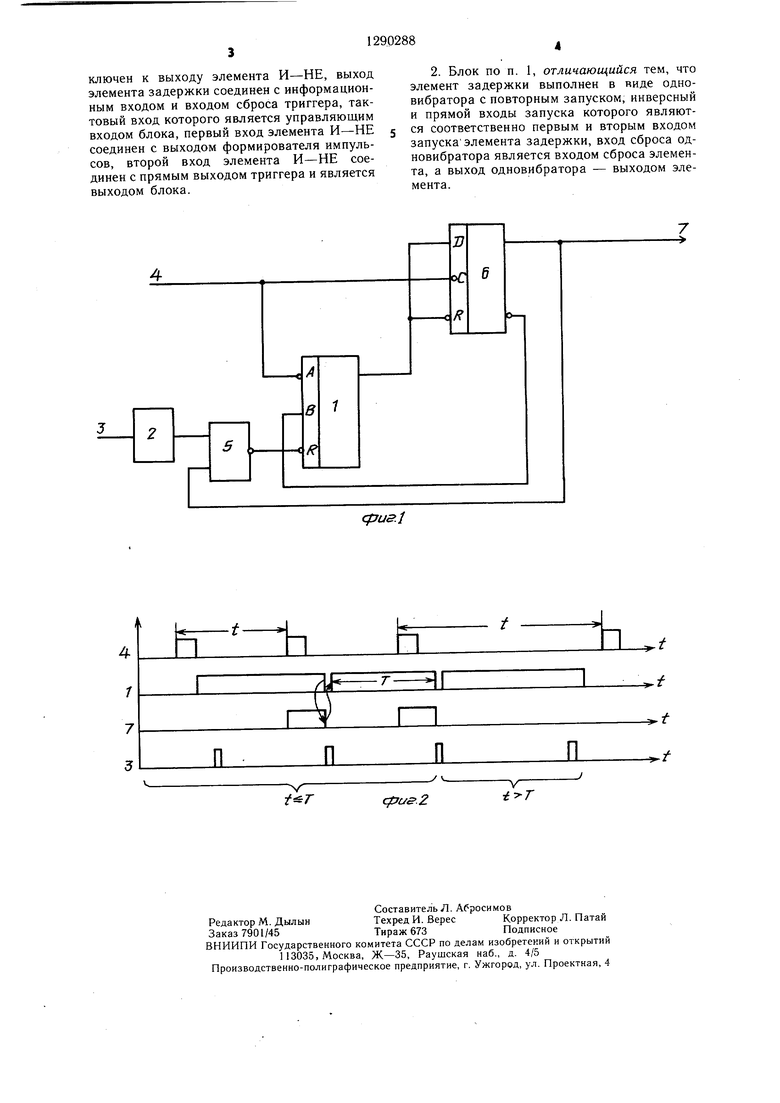

На фиг. 1 представлена функциональная схема блока синхронизации; на фиг. 2 - временная диаграмма работы блока синхронизации.

Блок синхронизации для графического дисплея содержит элемент 1 задержки, выполненный в виде одновибратора с повторным запуском, формирователь 2 импульсов, вход 3 внешнего запуска, управляющий вход 4, элемент И-НЕ 5, триггер 6, выход 7 блока. Вход 4 соединен с выходом дисплейного процессора, совместно с которым используется данный блок, а выход 7 - с входом блокировки дисплейного процессора. Структура дисплейного процессора не является принципиальной в данном случае. Главным является наличие в этом процессоре соответствующего выхода, на котором появляется импульсный сигнал при выполнении команды «Ожидание синхронизации, и наличие управляющего входа блокировки выполнения дисплейного файла.

Блок синхронизации работает следующим образом.

Нусть время выполнения дисплейного файла и вывода изображения меньше Т, где Т - период синхроимпульсов на входе 3. В этом случае в исходном состоянии триггер 6 в состоянии «О. Элемент 1 задержки не запущен, дисплейный файл обрабатывается процессором. Появление положительного импульса на входе 4 блока вызывает запуск элемента 1 задержки отрицательным фронтом этого импульса. Наличие единичного потенциала на инверсном выходе триггера 6 разрешает запуск элемента 1 задержки. На выходе элемента 1 задержки будет потенциал «1. Длительность импульса, формируемого элементом 1 задержки, выбирается несколько большей времени Т. Так как следующий импульс управления поступает на вход 4 до окончания импульса на выходе элемента 1 задержки, триггер 6 устанавливается в «1 положительным фронтом управляющего импульса. На выходе 7 блока формируется единичный сигнал паузы, который поступает в дисплейный процессор, вызывая приостановку выполнения дисплейного файла. Высокий потенциал на выходе 7 раз- рещает прохождение синхроимпульса от внещнего источника с входа 3 через элемент И-НЕ 5. Синхроимпульс устанавливает элемент 1 задержки в «О, что вызывает установку в «О триггера б и окончание паузы. Следующий запуск элемента 1 задержки происходит по снятию низкого потенциала с его входа установки в «О, если

0

на других входах присутствуют потенциалы, разрешающие запуск.

Блок синхронизации может работать и без внешнего источника синхроимпульсов, в этом случае период Т задается элементом 1 задержки. Установка одновибратора в «О как по истечению формируемого им импульса, так и принудительно вызывает сброс триггера б в «О, что в свою очередь перезапускает элемент 1 задержки по входу В. Если время выполнения дисплейного файла больше Т, то импульс на выходе элемента 1 задержки оканчивается до прихода очередного сигнала управления. Нулевой потенциал на выходе 5 элемента 1 задержки запрещает установку триггера 6 в «1. Пауза не формируется, а синхроимпульсы по входу 3 блокируются закрытым ; лементом И-НЕ 5.

Таким образом, если время выполнения 0 дисплейного файла меНьще Т, выполнение дисплейного файла и вывод изображения на экран ЭЛТ синхронизируется внещними импульсами с периодом Т или элементом 1 задержки, выполненным в виде одновибра- , тора с повторным запуском, генерирующим импульсы длительностью Т. При этом изображение имеет постоянную яркость независимо от длины дисплейного файла. Если время выполнения дисплейного файла больше Т, то вывод изображения синхронизи- 0 руется от сигналов управления, поступающих на вход 4, т.е. имеет место автосинхронизация. При этом яркость плавно уменьшается при увеличении длины дисплейного файла.

5 Таким образом, за счет введения в состав блока синхронизации элемента И-НЕ, триггера, выполнения элемента задержки в виде одновибратора с повторным запуском, а также новых связей удается осуществить режим автоматического перехода на автосинхронизацию при превыщении времени выполнения дисплейного файла периода синхроимпульсов.

0

45

Формула изобретения

1. Блок синхронизации для графического дисплея, содержащий элемент задержки и формирователь импульсов, вход которого является входом внешнего запуска блока, первый вход запуска элемента задержки является управляющим входом блока, отличающийся тем, что, с целью упрощения блока и расширения области применения его за счет обеспечения возможности осуш,ествления режима автогенерации

синхроимпульсов, он содержит элемент И-НЕ и триггер, инверсный выход которого соединен с вторым входом запуска элемента задержки, вход сброса которого подключей к выходу элемента И-НЕ, выход элемента задержки соединен с информационным входом н входом сброса триггера, тактовый вход которого является управляющим входом блока, первый вход элемента И-НЕ соединен с выходом формирователя импульсов, второй вход элемента И-НЕ соединен с прямым выходом триггера и является выходом блока.

2. Блок по п. 1, отличающийся тем, что элемент задержки выполнен в виде одно- вибратора с повторным запуском, инверсный и прямой входы запуска которого являются соответственно первым и вторым входом запуска элемента задержки, вход сброса од- новибратора является входом сброса элемента, а выход одновибратора - выходом элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство для регистрации телевизионного изображения | 1989 |

|

SU1720168A1 |

| Устройство для управления включением-отключением электропитания внешних устройств в вычислительной системе | 1988 |

|

SU1580372A1 |

| Цифровой осциллограф | 1990 |

|

SU1793387A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Генератор развертки | 1984 |

|

SU1170357A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для сопряжения ЦВМ с магнитофоном | 1987 |

|

SU1451708A1 |

| Устройство для сопряжения процессора с абонентами | 1984 |

|

SU1244669A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

Изобретение относится к области вычислительной техники и может быть использовано в графических дисплеях векторного типа. Целью изобретения является упрощение блока синхронизации и расщирение области применения его за счет обеспечения возможности осуществления режима автогенерации синхроимпульсов. Блок синхронизации содержит элемент задержки, выполненный в виде одновибратора с повторным запуском, формирователь импульсов, элемент И-НЕ и триггер. Блок осуществляет формирование сигнала паузы, который приостанавливает вывод изображения на экран, если время выполнения дисплейного файла меньше периода следования синхроимпульсов, тем самым делая время вывода изображения всегда постоянным и равным периоду следования синхроимпульсов. Блок обеспечивает плавное уменьшение яркости изображения при превышении времени выполнения дисплейного файла величины периода синхроимпульсов за счет перехода на автосинхронизацию. 1 з.п. ф-лы, 2 ил. i (Л С о N9 00 00

в

ffJCIS.l

| Экранный пульт графический (ЭПГ- СМ) | |||

| Техническое описание | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| - М., ИНЭУМ, 1978 | |||

| Intel Component Data Catalog, - Intel Corporation, 1979, p | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-02-15—Публикация

1984-10-15—Подача