Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных машинах (УВМ).

Известно устройство для контроля электронной вычислительной машины [1] содержащее блок счетчиков, дешифратор, пять триггеров, два элемента ИЛИ, три элемента И, элемент И-НЕ, элемент ИЛИ-НЕ, два формирователя импульсов, два элемента задержки, два регистра и схему сравнения, вход первого элемента задержки соединен с выходом первого элемента ИЛИ, а выход первого элемента задержки соединен с выходом первого элемента ИЛИ, а выход первого элемента задержки подключен к управляющему входу-выходу устройства, первому входу второго элемента ИЛИ, управляющему входу дешифратора и группе счетных входов блока счетчиков, вход дешифратора соединен с адресным входом-выходом устройства, а выход дешифратора подключен к входу первого элемента ИЛИ, второму входу второго элемента ИЛИ, входу первого формирователя импульсов и входу выдачи информации блока счетчиков, вход запрета счета, первый и второй входы приема информации, информационные входы, группа входов-выходов и выходы блока счетчиков соединены соответственно с выходами элемента И-НЕ, второго и первого формирователя импульсов, дополнительным информационным входом-выходом устройства и входами элемента ИЛИ-НЕ, выход которого подключен к первому входу первого элемента И и информационному входу первого триггера, выход второго элемента И соединен с вторым входом первого элемента И и синхровходом первого триггера, установочный вход и инверсный выход которого подключен соответственно к выходу дешифратора и первому входу элемента И-НЕ, первый и второй входы и выход второго триггера соединены соответственно с выходами дешифратора и второго элемента ИЛИ и вторым входом элемента И-НЕ, выход первого элемента И подключен к входу второго формирователя импульсов, а выход элемента И-НЕ соединен с первым входом второго элемента И и выходом устройства, первый и второй входы схемы сравнения подключены к выходам соответственно первого и второго регистров, информационные входы первого и второго регистров соединены соответственно с дополнительным информационным входом-выходом и информационным входом-выходом устройства, синхровходы первого и второго регистров, третьего и четвертого триггеров и установочные входы третьего, четвертого и пятого триггеров подключены к управляющему входу-выходу устройства, информационные входы третьего и четвертого триггеров соединены с общей шиной устройства, первый и второй входы и выход третьего элемента И подключены соответственно к выходам третьего и четвертого триггеров и входу второго элемента задержки, при этом информационный вход, синхровход и выход пятого триггера соединены соответственно с выходами схемы сравнения и второго элемента задержки и вторым входом второго элемента И.

Устройство обладает следующими недостатками:

1. Низкая оперативность контроля, так как ошибка обнаруживается только в конце линейного участка.

2. Ограниченная область применения, так как не может работать с современными микропроцессорами с конвейерами команд, где используется опережающая выборка команд.

3. Ограниченная достоверность и полнота контроля, так как не контролируется правильность перехода на новый линейный участок программы.

Известно устройство для контроля управляющей вычислительной машины [2] содержащее первый и второй блоки памяти, счетчик, регистр управления, триггер очистки, триггер ошибки, регистр адреса, первую и вторую схемы сравнения, причем группа информационных входов регистра адреса является группой адресных входов устройства, группа информационных выходов регистра адреса соединена с группой адресных входов второго блока памяти, группа информационных выходов которого соединена с второй группой адресных входов первого блока памяти, группа информационных выходов и выход дополнительного разряда которого соединены соответственно с первой группой информационных входов и входом первой схемы сравнения, выход которой соединен с информационным входом триггера ошибки, выход которого является выходом сбоя устройства, вход установки триггера ошибки является входом установки устройства, вход установки триггера ошибки является входом запроса ПЗУ программ устройства, синхровход триггера очистки является входом очистки устройства, информационный вход триггера очистки подключен к шине нулевого потенциала устройства, выход триггера очистки соединен с синхровходом регистра адреса и входом сброса счетчика, вход разрешения счета которого соединен с выходом второй схемы сравнения, первая группа информационных входов которой, вторая группа информационных входов первой схемы сравнения и группа информационных входов регистра управления подключены к входу контролируемых сигналов устройства, вторая группа информационных входов второй схемы сравнения соединена с выходами регистра управления, синхровход которого, синхровходы счетчика и триггера ошибки подключены к синхровходу устройства, выходы счетчика соединены с первой группой адресных входов первого блока памяти.

Известное устройство [2] обладает следующими недостатками:

1. Ограниченные функциональные возможности в силу нарушения работы устройства при наличии прерываний в контролируемой УВМ.

2. Ограниченная полнота и достоверность контроля. Контролируется правильность работы УВМ при выполнении линейных участков программы. Правильность же перехода на новый линейный участок не контролируется.

Наиболее близким по технической сущности к заявленному техническому решению является выбранное за ближайший аналог устройство для контроля управляющей вычислительной машины [3] содержащее первый и второй блоки памяти, счетчик, регистр, триггер очистки, триггер ошибки, первую и вторую схемы сравнения, одновибратор, три элемента И, причем выходы счетчика соединены с группой адресных входов первого блока памяти, группа выходов которого соединена с первой группой входов первой схемы сравнения, выход которой соединен с информационным входом триггера ошибки, инверсный вход установки которого является входом начальной установки устройства, выход триггера ошибки является выходом сбоя устройства, первая группа входов второй схемы сравнения, вторая группа входов первой схемы сравнения, группа информационных входов регистра подключены к группе входов контролируемых сигналов устройства, вторая группа входов второй схемы сравнения соединена с выходами регистра, синхровход счетчика подключен к входу синхронизации устройства, инверсный вход установки триггера очистки является входом запроса ПЗУ программ устройства, группа адресных входов второго блока памяти является группой адресных входов устройства, группа выходов второго блока памяти соединена с группой информационных входов счетчика, вход сброса которого является входом очистки устройства и соединен с инверсным входом сброса триггера очистки, выход которого соединен с входом одновибратора, выход которого соединен с входом параллельной записи счетчика, синхровходы триггера ошибки и регистра соединены с выходом первого элемента И, первый вход которого соединен с входом синхронизации устройства, второй вход первого элемента И и первый вход второго элемента И соединены с выходом третьего элемента И, первый вход которого является входом подтверждения прерывания устройства, а второй вход соединен с входом запроса ПЗУ программ устройства, второй вход второго элемента И соединен с выходом второй схемы сравнения, выход второго элемента И соединен с входом разрешения счета счетчика.

Известное устройство [3] обладает ограниченной полнотой и достоверностью контроля. Оно контролирует правильность работы УВМ только на линейных участках программы, правильность же перехода на новый линейный участок программы (например по команде условного или безусловного перехода) не контролируется.

Задачей, на решение которой направлено заявляемое изобретение, является повышение полноты и достоверности контроля за счет возможности контроля правильности перехода УВМ на новый линейный участок программы.

Поставленная задача достигается устройством, содержащим первый и второй блоки памяти, счетчик, регистр, триггер очистки, триггер ошибки, первую и вторую схемы сравнения, первый одновибратор, три элемента И, причем группа адресных входов второго блока памяти является группой адресных входов устройства, группа выходов второго блока памяти соединена с группой информационных входов счетчика, выходы которого соединены с группой адресных входов первого блока памяти, группа выходов которого соединена с первой группой входов первой схемы сравнения, выход которой соединен с информационным входом триггера ошибки, инверсный вход установки которого является входом начальной установки устройства, выход выходом сбоя устройства, синхровходы триггера ошибки и регистра соединены с выходом первого элемента И, первый вход которого соединен с входом синхронизации устройства и сионхровходом счетчика, а второй вход соединен с первым входом второго элемента И, выход которого соединен с входом разрешения счета счетчика, а второй вход соединен с выходом второй схемы сравнения, вторая группа входов которого соединена с выходами регистра, первая группа входов второй схемы сравнения, вторая группа входов первой схемы сравнения, группа информационных входов регистра подключены к группе входов контролируемых сигналов устройства, инверсный вход установки триггера очистки соединен с вторым входом третьего элемента И и является входом запроса ПЗУ программ устройства, инверсный вход сброса входом очистки устройства, выход соединен с входом первого одновибратора, выход которого соединен с входом параллельной записи счетчика, в которое введен третий блок памяти, триггер блокировки, триггер прерывания, второй одновибратор, элемент ИЛИ, четвертый элемент И, первый блок памяти снабжен дополнительным выходом, причем группа адресных входов третьего блока памяти соединена с выходами счетчика, а группа выходов соединена с группой информационных входов счетчика, дополнительный выход первого блока памяти соединен с первым входом элемента ИЛИ, выход которого соединен с входом выборки второго блока памяти и инверсным входом выборки третьего блока памяти, инверсный вход сброса триггера блокировки соединен с входом очистки устройства, инверсный вход установки соединен с выходом третьего элемента И, выход соединен с третьим входом первого элемента И, второй вход которого соединен с входом запроса ПЗУ программ устройства, вход устройства запроса стека соединен с первым входом третьего элемента И и синхровходом второго одновибратора, вход разрешения запуска которого соединен с выходом триггера очистки, выход соединен с входом сброса счетчика, а инверсный выход с первым входом четвертого элемента И, второй вход которого соединен с входом начальной установки устройства, а выход с инверсным входом установки триггера прерывания, информационный вход которого подключен к шине нулевого потенциала устройства, синхровход соединен с выходом первого одновибратора, а выход соединен с вторым входом элемента ИЛИ.

Отличительные признаки заявляемого изобретения обусловливают появление в нем новых свойств по сравнению с аналогичными решениями.

Элементы памяти, элементы ИЛИ, триггеры повсеместно используются в цифровой технике [4, 6] В заявляемом техническом решении их применение, а также введение дополнительных связей между элементами устройства позволяют получить качественно ранее неизвестное улучшение характеристик устройства для контроля управляющей вычислительной машины, поскольку расширяет полноту и достоверность контроля за счет возможности контроля не только правильности работы УВМ на линейных участках программы, но и возможности проконтролировать правильность перехода на новый линейный участок программы.

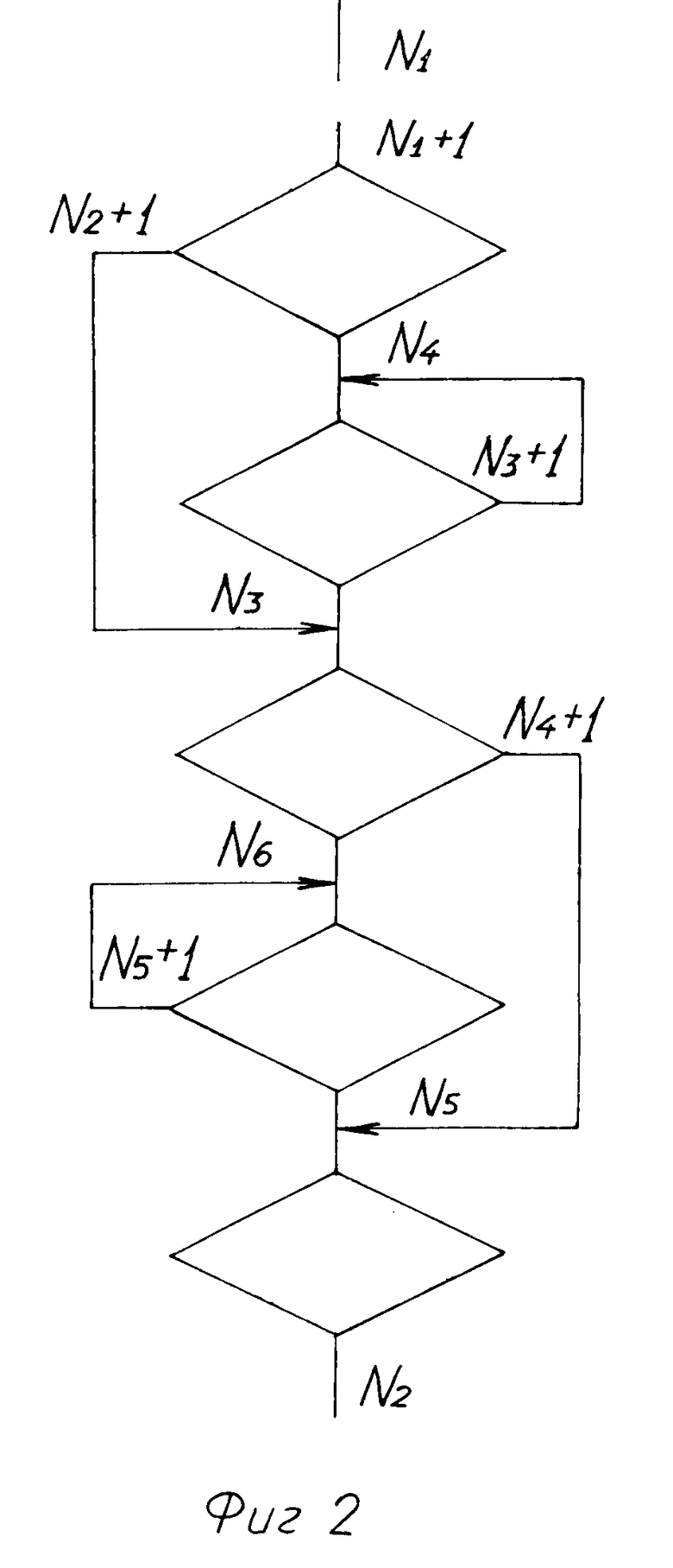

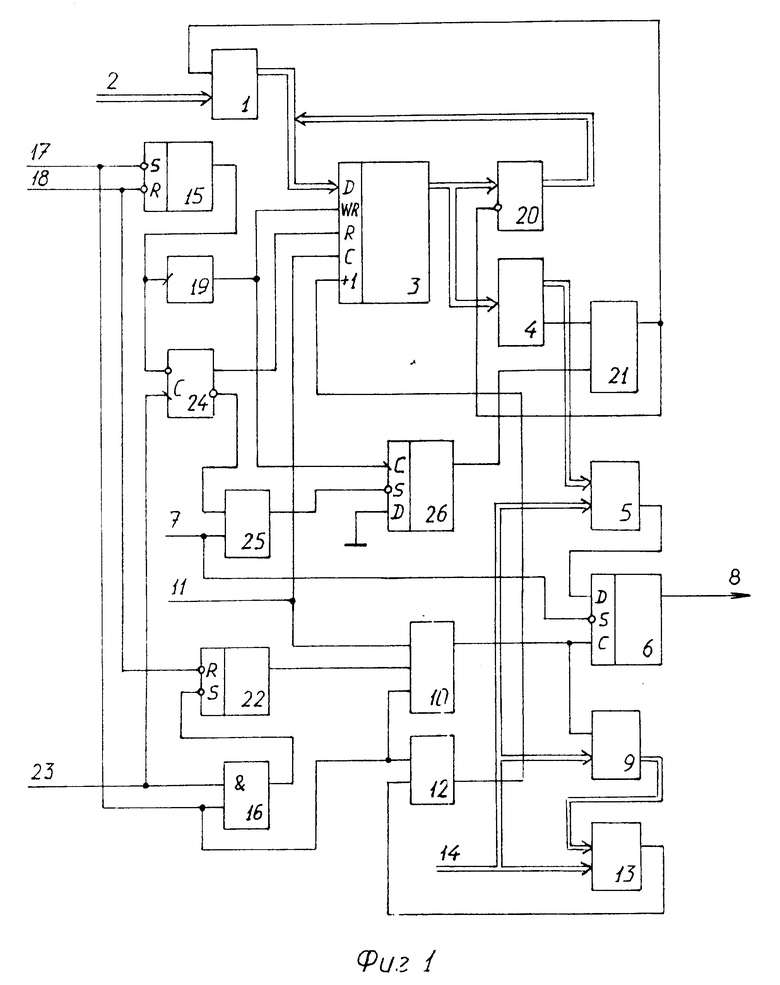

На фиг. 1 показана структурная схема устройства; на фиг. 2 пример части программы.

Устройство для контроля управляющей вычислительной машины содержит второй блок памяти 1, группа адресных входов которого является группой адресных входов 2 устройства, а группа выходов соединена с группой информационных входов счетчика 3, выходы которого соединены с группой адресных входов первого блока памяти 4, группа выходов которого соединена с первой группой входов первой схемы сравнения 5, выход которой соединен с информационным входом триггера ошибки 6, инверсный вход установки которого является входом начальной установки устройства, выход выходом сбоя 8 устройства, синхровходы триггера ошибки 6 и регистра 9 соединены с выходом первого элемента И 10, первый вход которого соединен с входом синхронизации 11 устройства и синхровходом счетчика 3, а второй вход соединен с первым входом второго элемента И 12, выход которого соединен с входом разрешения счета счетчика 3, а второй вход соединен с выходом второй схемы сравнения 13, вторая группа входов которой соединена с выходами регистра 9, первая группа входов второй схемы сравнения 13, вторая группа входов первой схемы сравнения 5, группа информационных входов регистра 9 подключена к группе входов контролируемых сигналов устройства 14, инверсный вход установки триггера очистки 15 соединен с вторым входом третьего элемента И 16 и является входом запроса ПЗУ программ 17 устройства, инверсный вход сброса -входом очистки 18 устройства, выход соединен с входом первого одновибратора 19, выход которого соединен с входом параллельной записи счетчика 3, группа адресных входов третьего блока памяти 20 соединена с выходами счетчика 3, а группа выходов соединена с группой информационных входов счетчика 3, дополнительный выход первого блока памяти 4 соединен с первым входом элемента ИЛИ 21, выход которого соединен с входом выборки второго блока памяти 1 и инверсным входом выборки третьего блока памяти 20, инверсный вход сброса триггера блокировки 22 соединен с входом очистки 18 устройства, инверсный вход установки соединен с выходом третьего элемента И 16, выход соединен с третьим входом первого элемента И 10, второй вход которого соединен с входом запроса ПЗУ программ 17 устройства, вход устройства запроса стека 23 соединен с первым входом третьего элемента И 16 и синхровходом второго одновибратора 24, вход разрешения запуска которого соединен с выходом триггера очистки 15, выход соединен с входом сброса счетчика 3, инверсный выход с первым входом четвертого элемента И 25, второй вход которого соединен с входом начальной установки устройства 7, а выход с инверсным входом установки триггера прерывания 26, информационный вход которого подключен к шине нулевого потенциала устройства, синхровход соединен с выходом первого одновибратора 19, а выход соединен с вторым входом элемента ИЛИ 21.

Входы начальной установки 7, запроса ПЗУ программ 17, запроса стека 23, синхронизации 11, очистки 18 соединены с соответствующими линиями процессора контролируемой УВМ, группа адресных входов 2 устройства с шиной адреса контролируемой УВМ, входы 14 контролируемых сигналов устройства с линиями управления передачи адресов и данных (Ввод, Вывод, СИП, Байт и т.д.), в том числе линиями выборки модулей УВМ (Запрос ОЗУ, Запрос устройств ввода-вывода и т.д.). Выход сбоя 8 устройства может соединяться с входом сброса (перезапуска) или немаскируемого прерывания процессора УВМ.

В программе все такты выполнения команд, в которых происходит изменение сигналов на линиях управления передачей адресов и данных 14, пронумерованы. Начальные номера 0.N соответствуют временной программе перехода к обработке прерывания (т.е. занесения точки возврата в стек и считывания векторов прерывания). Остальные номера, начиная с N1 + 1, присвоены тактам выполнения команд, в которых происходит изменение сигналов самой рабочей программы УВМ и программ обработки прерываний. В пределах линейных участков номера наращиваются последовательно.

Заявляемое устройство может быть реализовано на серийно выпускаемых микросхемах: триггеры 15, 22, 26, 6 К555ТМ2, блоки памяти 1, 4, 20 573РФ8, одновибраторы 19, 24 К555АГ3, элементы 2И 12, 16, 25-155ЛИ5, элемент 3И 10 - 555 ЛИ6, элемент ИЛИ 21 555ЛЛ1, счетчик 3 555ИЕ10, регистр 9 155ИР13, схемы сравнения 5, 13 555СП1.

Устройство предназначено для контроля управляющих вычислительных машин, построенных на базе современных процессоров, имеющих конвейер команд (например, микропроцессоры 1810ВМ86, INTEL i80x896) [4, 5]

В данных процессорах используется опережающая выборка команд и формируется очередь команд. При передаче управления в другое место программы конвейер команд очищается, после чего начинает заполняться новыми командами программы. Сигнал очистки конвейера (для микропроцессора 1810ВМ86 [4] например, это сигнал  активный уровень ("0") которого появляется при QS1 0, QS0 1), идентифицирует переход к началу нового линейного участка программы и подается на соответствующий вход устройства.

активный уровень ("0") которого появляется при QS1 0, QS0 1), идентифицирует переход к началу нового линейного участка программы и подается на соответствующий вход устройства.

Контроль работы УВМ осуществляется проверкой последовательности следования сигналов управления передачи адресов и данных (Ввод, Вывод, СИП, Байт и т.д.), в том числе сигналов выборки модулей УВМ (Запрос ОЗУ, Запрос устройств ввода-вывода и т.д.) при выполнении команд. Используется то, что поведение УВМ при выполнении команд программы, а также при переходе к обработке прерываний строго детерминировано в том смысле, что при отсутствии сбоев на линиях управления передачи адресов и данных 14 будет сформирована строго определенная временная диаграмма, которую можно вычислить еще до начала программы.

Таким образом обеспечивается:

1) контроль правильности порядка обращения процессора проверяемой УВМ к остальным ее модулям (ОЗУ, устройствам ввода-вывода и т.д.) на линейных участках программы;

2) контроль правильности порядка включения в работу подпрограмм обслуживания прерываний как от внутренних, так и от внешних устройств;

3) контроль правильности перехода на новый линейный участок программы.

Дополнительная третья контрольная функция удачно дополняет контроль правильности управляющих сигналов на линейных участках контролем правильности перехода УВМ на новый линейный участок, обеспечивая тем самым всесторонность контроля и повышение его достоверности.

Расположение в общей временной диаграмме УВМ процесса считывания команд при наличии прерываний в контролируемой УВМ является недетерминированным. Связано это с недетерминированным характером прерываний, необходимостью повторного считывания команд, которые уже были считаны до момента прерывания. Поэтому правильность считывания команд проверяется не непосредственно (при считывании команд за счет активного уровня ("0") на линии запроса ПЗУ программы 17 блокированы элементы И 10, 12 и все устройство), а по правильности временной диаграммы их выполнения.

При переходе к обработке прерывания контролируется общая для внешних и внутренних прерываний часть временной диаграммы, связанная с занесением точки возврата в стек и считыванием векторов прерывания.

При считывании номера вектора прерывания, что имеет место только при считывании внешнего прерывания, происходит блокировка устройства за счет перевода в активное состояние ("0") триггера блокировки 22. Перевод триггера блокировки 22 в активное состояние происходит по активному уровню сигнала очистки конвейера команд на линии 18, а перевод в пассивное состояние по сигналу запроса стека на линии 23, возникающего при занесении точек возврата в стек. При обычном переходе на новый линейный участок программы, не связанном с переходом к обработке прерывания установки триггера блокировки в пассивное состояние, происходит по первому же сигналу на линии запроса ПЗУ программ 17. Это препятствует ложной блокировке устройства при переходе на новый линейный участок программы.

Блок памяти 1 прошит так, что по адресам команд программы УВМ записаны номера первого такта выполнения данной команды.

Блок памяти 20 прошит так, что по каждому адресу, равному номеру такта временной диаграммы, в который возможен переход на новый линейный участок, записан номер первого такта временной диаграммы выполнения команд этого нового линейного участка. По остальным адресам прошита произвольная информация, например число большее на N1 длины в тактах контролируемой временной диаграммы выполнения команд рабочей программы УВМ.

Блок памяти 4 прошит так, что номер такта временной диаграммы, (выполняющего для него роль адреса), ставится в соответствии с правильными значениями сигналов на линиях 14 в данном такте. Ячейки этого блока памяти имеют дополнительный разряд по отношению к числу контролируемых линий 14. Он соединен с входом выборки блока памяти 1 и инверсным входом выборки блоков памяти 20. Этот бит имеет значение "1" по адресам, соответствующим номерам тактов временной диаграммы, при которых возможен переход на новый линейный участок программы, но его начало (номер первого его такта) затруднительно или невозможно предсказать (например, при возврате из прерывания, при косвенной адресации через ячейку ОЗУ). По остальным адресам данный бит имеет значение "0".

Запись информации в регистр 9, триггер 6, а также наращивание счетчика 3 происходит по фронту 0/1 на их синхровходах. Причем наращивание счетчика 3 происходит только при наличии сигнала логической "1" на его входе разрешения счета.

Запись информации в триггер 26 происходит по фронту 1/0 на его синхровходе.

Одновибратор 19 формирует положительный импульс на своем выходе при появлении фронта 0/1 на входе. Длительность импульса на выходе одновибратора 19 в пределах 1.2T, где T период синхроимпульсов на линии 11. Это обеспечивает надежную параллельную запись счетчика 3.

Одновибратор 24 формирует положительный импульс на своем выходе и отрицательный на своем инверсном выходе при появлении фронта 1/0 на своем синхровходе при наличии активного уровня сигнала ("0") на входе разрешения запуска. Длительность импульса устанавливается минимально возможной для надежного сброса счетчика 3.

Активный ("0") уровень сигнала "Запрос ПЗУ программы" на линии 17 и сигнала "Запрос стека" на линии 23 вырабатывается процессором УВМ (например, с помощью входящего в его состав селектора адреса) при его обращении соответственно к зоне адресов, где хранится программа, выполняемая УВМ, и к зоне адресов стека и сохраняется до конца цикла обращения к ячейке памяти. Векторы прерывания хранятся по адресам, не входящим в указанные области адресов, при их извлечении активный уровень сигналов на данных линиях не формируется.

При равенстве сигналов на первой и второй группе входов схем сравнения 5, 13 на их выходе сигнал логического "1", при неравенстве логической "0". Регистр 9 и вторая схема сравнения 13 обеспечивают управление счетчиком 3. Если значения сигналов на контролируемых линиях 14 к моменту перехода фронта 0/1 синхроимпульса совпадают с их значениями, записанными в регистр 9 во время фронта 0/1 предыдущего синхроимпульса, то в этот момент на выходе схемы сравнения 13 и на выходе элемента И 12 логический "0", что препятствует наращиванию счетчика по фронту 0/1. В регистре 9 сохраняется старое значение. Если значения сигналов на проверяемых линиях 14 за время такта изменились, то к моменту прихода фронта 0/1 значения сигналов на входах схемы сравнения 13 не совпадают, на ее выходе появляется логическая "1", что обеспечивает при отсутствии блокировки элементов И 10, 12 наращивание счетчика 3 по фронту 0/1. В регистр 9 по этому же фронту записывается новое значение сигналов на контролируемых линиях 14. Подобное управление счетчиком уменьшает развертку временной диаграммы и тем самым объем блоков памяти 4 и 20. Значения сигналов рассматриваются только во время фронтов 0/1 синхроимпульсов, в блоках памяти 4, 20 отсутствует повторение тактов с неизменным значением сигналов на контролируемых линиях 14.

Устройство работает следующим образом.

При включении питания процессор УВМ формирует активный уровень сигнала ("0") начальной установки на линии 7, который устанавливает в пассивное состояние ("1") триггер ошибки 6, устанавливает в "1" триггер прерывания 26, на выходе элемента ИЛИ 21 появляется сигнал логической единицы, обеспечивающий блокировку третьего блока памяти 20 и выбор блока памяти 1. При включении питания так же, как и при переходе на новый линейный участок программы, происходит очистка конвейера команд процессора УВМ, сопровождающаяся появлением активного ("0") уровня сигнала на линии очистки 18, приводящего к сбросу триггера очистки 15.

Процессор УВМ обращается к ПЗУ программ УВМ за первой командой нового линейного участка программы, выдавая его адрес. Обращение сопровождается появлением активного ("0") уровня сигнала на линии запроса ПЗУ программ 17, по которому происходит установка триггера очистки 15. По появляющемуся на выходе триггера очистки фронту 0/1 на выходе одновибратора 19 формируется импульс разрешения записи для счетчика 3. В счетчик 3 по фронту синхроимпульса 0/1 на линии 11 производится запись информации о номере такта управляющего сигнала, поступающая с выхода блока памяти 1 или блока памяти 20 в зависимости от состояния сигнала на выходе элемента ИЛИ 21.

После включения питания установка в "1" триггера прерывания 26 обеспечивает на выходе элемента ИЛИ 21 сигнал логической единицы, в счетчик 3 записывается из блока памяти 1 номер такта временной диаграммы, соответствующий фактическому адресу начала линейного участка (первой выполняемой команды программы).

Задним (1/0) фронтом сигнала на выходе первого одновибратора 19 происходит сброс триггера прерывания 26, на выходе элемента ИЛИ 21 появляется сигнал логического "0", обеспечивающий блокировку первого блока памяти и выбор третьего блока памяти.

Процессор УВМ начинает выполнять линейный участок программы.

По мере поступления синхроимпульсов на линии 11 при наличии логической "1" на выходе элемента И 12 происходит наращивание счетчика 3. На выходах блока памяти 4 формируется прогнозируемая временная диаграмма управляющих сигналов, которая поступает на первую группу входов схемы сравнения 5, на вторую группу входов которой поступают реальные сигналы с контролируемых линий 14. При отсутствии сбоев к приходу фронта 0/1 очередного синхроимпульса значения сигналов на обеих группах входов схемы сравнения 5 совпадают, на ее выходе "1", триггер ошибки 6 остается в установленном состоянии, активный уровень ("0") сигнала сбоя на линию 8 не выдается.

При сбое из-за возникающего несоответствия между сигналами на входах схемы сравнения 5 в моменты прихода фронта 0/1 синхросигнала на линии 11 на выходе схемы сравнения 5 "0", а следовательно, и на выходе триггера ошибки 6 появляется активный уровень ("0"), который подается на линию сбоя устройства 8. По нему процессор УВМ вырабатывает сигнал начальной установки на линии 7, который устанавливает триггер ошибки 6 в пассивное состояние ("1"). Процессор УВМ переходит к программе обработки прерывания.

Контроль правильности перехода на новый линейный участок программы.

Блок памяти 20 прошит так, что выдает на группу своих выходов номер такта временной диаграммы, соответствующий началу нового линейного участка, на который возможен переход в данный момент времени (в данный такт временной диаграммы). Он подается на группу информационных входов счетчика. При переходе на новый линейный участок в счетчик происходит запись прогнозируемого номера такта временной диаграммы, соответствующего новому линейному участку программы. При сбое и переходе в нерасчетную точку программы временная диаграмма управляющих сигналов будет отличаться от прогнозируемой, приводя к появлению сигнала сбоя. Таким образом контролируется правильность перехода на новый линейный участок программы.

В ряде случаев адрес перехода и соответствующий номер такта временной диаграммы не может быть определен заранее. К их числу относятся:

1) переход к обработке прерывания, когда адрес перехода зависит от считываемого вектора прерывания;

2) возврат из прерывания, когда адрес перехода определяется точкой, в которой произошло прерывание основной программы УВМ;

3) косвенная адресация перехода, когда адрес перехода зависит от изменяющегося содержания определенной ячейки ОЗУ УВМ.

При этом при переходе на новый линейный участок программы в счетчик записывается из блока памяти 1 номер такта, соответствующий фактическому адресу перехода на новый линейный участок программы.

Это обеспечивается тем, что дополнительный бит блока памяти 4 имеет значение "1" по адресам номеров тактов временной диаграммы, в которых возможен переход на новый линейный участок программы, адрес которого не может быть определен заранее. При этом происходит блокировка выходов блока памяти 20, блок памяти 1 наоборот разблокируется и информация с его выхода подается на информационную группу входов счетчика 3, в который она записывается как было рассмотрено ранее по фронту 0/1 синхросигнала на линии 11 при возникновении разрешения записи на выходе первого одновибратора 19.

Контроль правильности включения в работу подпрограмм обслуживания прерывания происходит следующим образом.

Переход к обработке прерывания сопровождается появлением активного ("0") уровня сигнала на линии очистки 18. Это приводит к сбросу триггера очистки 15 и появлению активного уровня сигнала на входе разрешения запуска второго одновибратора 24; к переводу в активное состояние ("0") триггера блокировки 22. Контролируется общая для внутренних и внешних программных и аппаратных прерываний временная диаграмма процесса занесения в стек точки возврата и считывания вектора прерывания. Активное состояние триггера блокировки 22 обеспечивает блокировку устройства на время считывания номера вектора прерывания, что имеет место только при переходе к обработке внешнего векторного прерывания.

Запись точки возврата в стек сопровождается появлением активного ("0") уровня сигнала запроса стека на линии 23. Первое его появлении приводит к установке в пассивное состояние ("1") триггера блокировки 22 и снятия блокировки с устройства, а также к запуску второго одновибратора 24. На выходе одновибратора 24 появляется короткий положительный импульс, обеспечивающий сброс счетчика 3, короткий отрицательный импульс на инверсном выходе обеспечивает установку триггера прерывания 26.

По мере поступления синхроимпульсов на линии 11 при наличии логической "1" на выходе элемента И 12 происходит наращивание от 0 счетчика 3 и формирование ожидаемой временной диаграммы, аналогично первому режиму работы происходит ее сравнение с реальной.

Установленный в "1" триггер прерывания 26 обеспечивает блокировку блока памяти 20 и выбор блока памяти 1. При считывании первой команды программы обработки прерывания, сопровождающейся сигналом запроса ПЗУ программы, на линии 17 происходит установка триггера очистки 15, на выходе одновибратора 19 формируется положительный импульс разрешения записи для счетчика 3. В счетчик 3 по фронту синхроимпульса 0/1 на линии 11 производится запись из блока памяти 1 номера такта начала линейного участка, соответствующего адресу фактического перехода (началу программы обработки прерывания). По заднему фронту 1/0 импульса на выходе первого одновибратора 19 происходит сброс триггера прерывания 26.

Заявляемое устройство по сравнению с ближайшим аналогом расширяет полноту и достоверность контроля за счет возможности контролировать правильность работы УВМ не только на линейных участках программы, но и позволяет проконтролировать правильность перехода на новый линейный участок программы.

В случае использования заявляемого устройства в многопроцессорной управляющей системе, в системе автоматического управления газотурбинным генератором электрической энергии, эффективность его применения можно оценить следующим образом. Повышение достоверности контроля увеличивает надежность, что уменьшает вероятность ложного отключения исправного двигателя или его поломку в случае выдачи неправильных воздействий на его исполнительные механизмы. Экономическая эффективность заявляемого устройства и расчет потребности народного хозяйства не рассчитывается в связи с отсутствием данных у организации заявителя.

Источники информации

1. Авторское свидетельство N 1159024, кл. G 06 F 11/30, Устройство для контроля управляющей вычислительной машины /Шевкопляс Б.В. Бюл N 9, 1985.

2. Авторское свидетельство N 1815644, кл G 06 F 11/28, Устройство для контроля управляющей вычислительной машины/Иванов А.И. Кладов В.Е. Михайлов А.М. Бюл. N 18, 1993.

3. Патент РФ N 2011216, кл G 06 F 11/28, Устройство для контроля управляющей вычислительной машины/Иванов А.И. Кладов В.Е. Михайлов А.М. Бюл. N 7, 1994.

4. Микропроцессоры и микропроцессорные комплекты интегральных микросхем. Справочник. Под ред. Шахнова В.А. т. 2, М. Радио и связь, 1988.

5. Говорун В.Н. Горбунов Н.В. и др. МикроЭВМ и управляющие модули на базе БИС 1810 // Микропроцесосрные средства и системы, 1986, 6, с. 13 16.

6. Микропроцессоры. Под ред. Преснухина Л.Н. кн. 3, Минск, Вышейшая школа, 1987.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1991 |

|

RU2011216C1 |

| Устройство для контроля хода программы управляющей вычислительной машины | 1990 |

|

SU1815644A1 |

| Устройство для контроля управляющей вычислительной машины | 1990 |

|

SU1815645A1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2109399C1 |

| Устройство для контроля управляющей вычислительной машины | 1987 |

|

SU1464163A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1522216A1 |

| Многоканальное устройство приоритетного обслуживания | 1989 |

|

SU1675886A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1619280A1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ | 1999 |

|

RU2171967C2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СУБОПТИМАЛЬНОГО РАЗМЕЩЕНИЯ И ЕГО ОЦЕНКИ | 2001 |

|

RU2193796C2 |

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных машинах (УВМ), например в системах управления газотурбинного двигателя. Изобретение позволяет повысить достоверность контроля за счет возможности контроля работы УВМ при переходе на новый линейный участок программы. Устройство содержит три блока памяти (БКП), один триггер очистки (ТГО), четыре элемента И, два одновибратора (ОБ), один счетчик (СТ), один регистр (РС), две схемы сравнения (СМС), один триггер ошибки (ТГО), триггер прерывания (ТГП), триггер блокировки (ТБК), элемент ИЛИ. 2 ил.

Устройство для контроля управляющей вычислительной машины, содержащее первый и второй блоки памяти, счетчик, регистр, триггер очистки, триггер ошибки, первую и вторую схемы сравнения, первый одновибратор, три элемента И, причем группа адресных входов второго блока памяти является группой адресных входов устройства, группа выходов второго блока памяти соединена с группой информационных входов счетчика, выходы которого соединены с группой адресных входов первого блока памяти, группа выходов которого соединена с первой группой входов первой схемы сравнения, выход которой соединен с информационным входом триггера ошибки, инверсный вход установки которого является входом начальной установки устройства, выход выходом сбоя устройства, синхровходы триггера ошибки и регистра соединены с выходом первого элемента И, первый вход которого соединен с входом синхронизации устройства и синхровходом счетчика, а второй вход соединен с первым входом второго элемента И, выход которого соединен с входом разрешения счета счетчика, а второй вход соединен с выходом второй схемы сравнения, вторая группа входов которой соединена с выходами регистра, первая группа входов второй схемы сравнения, вторая группа входов первой схемы сравнения, группа информационных входов регистра подключены к группе входов контролируемых сигналов устройства, инверсный вход установки триггера очистки соединен с вторым входом третьего элемента И и является входом запроса ПЗУ программ устройства, инверсный вход сброса входом очистки устройства, выход соединен с входом первого одновибратора, вход которого соединен с входом параллельной записи счетчика, отличающееся тем, что в устройство введены третий блок памяти, триггер блокировки, триггер прерывания, второй одновибратор, элемент ИЛИ, четвертый элемент И, первый блок памяти снабжен дополнительным выходом, причем группа адресных входов третьего блока памяти соединена с выходами счетчика, а группа выходов соединена с группой информационных входов счетчика, дополнительный выход первого блока памяти соединен с первым входом элемента ИЛИ, выход которого соединен с входом выборки второго блока памяти и инверсным входом выборки третьего блока памяти, инверсный вход сброса триггера блокировки соединен с входом очистки устройства, инверсный вход установки соединен с выходом третьего элемента И, выход соединен с третьим входом первого элемента И, второй вход которого соединен с входом запроса ПЗУ программ устройства, вход устройства запроса стека соединен с первым входом третьего элемента И и синхровходом второго одновибратора, вход разрешения запуска которого соединен с выходом триггера очистки, выход соединен с входом сброса счетчика, а инверсный выход с первым входом четвертого элемента И, второй вход которого соединен с входом начальной установки устройства, а выход с инверсным входом установки триггера прерывания, информационный вход которого подключен к шине нулевого потенциала устройства, синхровход соединен с выходом первого одновибратора, а выход соединен с вторым входом элемента ИЛИ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР N 1159024, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля хода программы управляющей вычислительной машины | 1990 |

|

SU1815644A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1991 |

|

RU2011216C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-10-27—Публикация

1995-07-18—Подача