1 . . 1

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных устройствах, построенных по принципу обще магистрали.

Цель изобретения - повьппение достоверности передачи информа ции между процессором и абонентами.

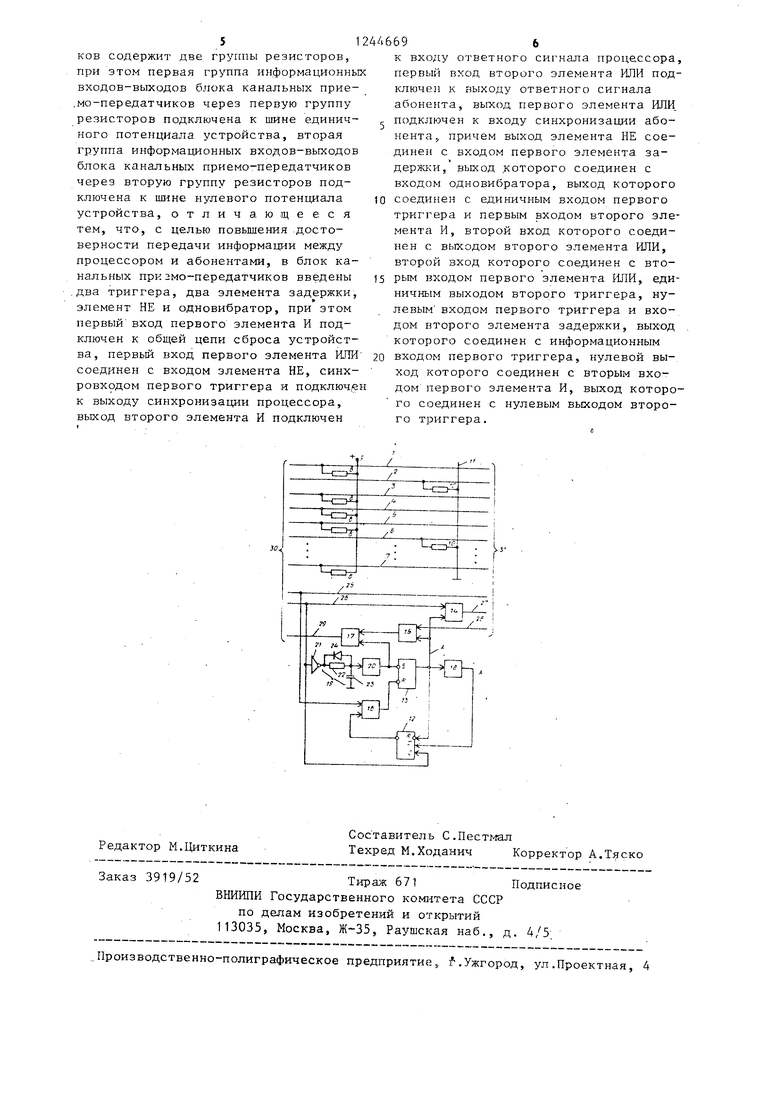

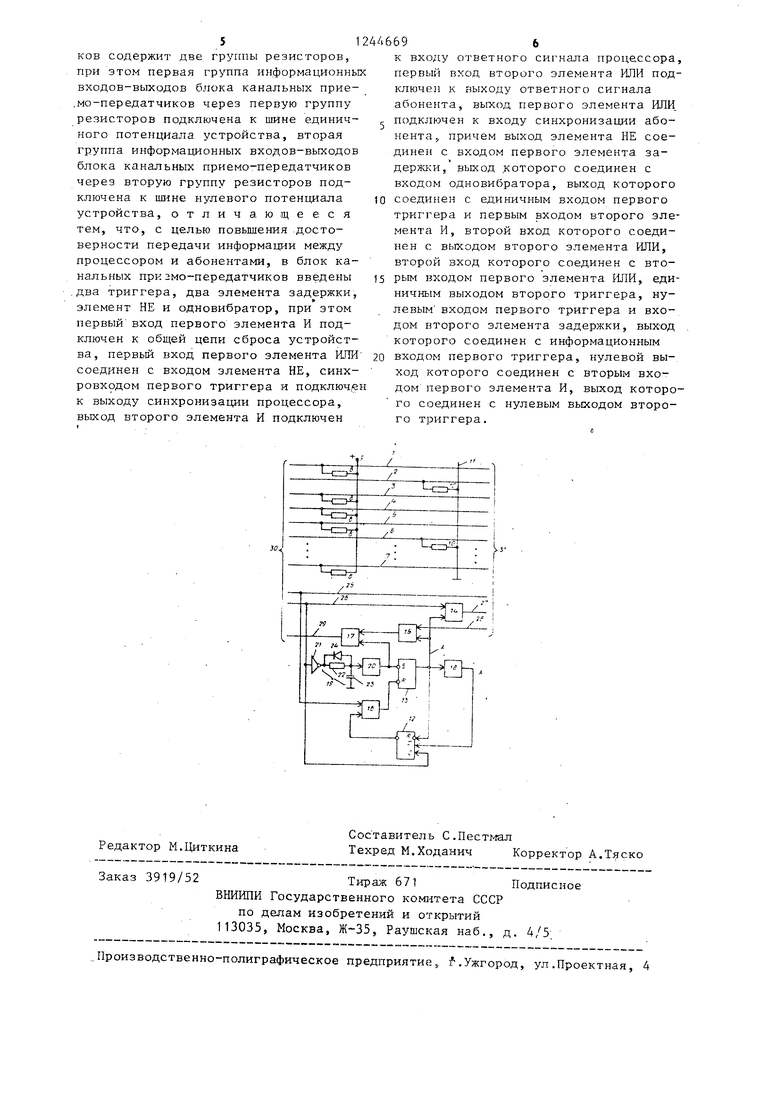

На чертеже представлена функциональная схема устройства.

Устройство содержит информационны входы-выходы 1-7 блока канальных приемо-передатчиков, которые условно делятся на две группы, К первой группе относятся входы-выходы 1 ,,3,4,5,7, к второй - 2 и 6, Первая группа информационных входов-выходов через первую группу резисторов 8 подключена к шине 9 единичного потенциала устройства. Вторая группа информационных входов-выходов через вторую группу резисторов 10 подключена к шине 11 нулевого потенциала устройства. Устройство также содержит первый .12 и второй 13 триггеры, первый 14 и второй 15 элементы ИЛИ, первый. 16 и второй 17 элементы И,второй 18 и первый 19 элементы задержки, одно- вибратор 20 и элемент НЕ 21. Элемент задержки 19 в данном случае выполнен в виде интегрирующей RC-цепи на ре- зисторе 22 и конденсатора 23 с дио- .дом 24,включенным параллельно резистору 22. Катод диода 24 является входом элемента задержки 19, а анод - выходом этого элемента. Устройство также содержит линии 25-29 входных и выходных управляющих сигналов.

Элемент 18. может быть вьтолнен .на тех же элементах, что и элемент 1 В этом случае обеспечивается задержка только положительных фронтов входных сигналов. .

Группа информационных входов-выходов 1-7 является шиной данных. Уст- ройство служит для подключения центрального процессора к прочим устройствам, например5 к памяти, контроллерам и т,п„ Для подключения процессора отведены выводы 30, а для подключения прочих устройств - выводи 31,

Шина данных (линии 1-7) предназ- .начена для двунаправленной передачи кодов между процессором и прочими блоками. Шина данных может быть либо свободной, когда ни один из блоков ЭВМ не вьщает в нее информацию, ли- бо занятой, тогда один из блоков (на пример, постоянное запоминающее уст

9

ройство) передает в другой блок (например, в процессор) нужную информацию. Далее предполагается, что передатчики, подключенные к линиям шины данных9 могут находиться в трех состояниях: О, 1 и Выключено. Первые два состояния обеспечивают поддержание на линии соответственно низкого и высокого потенциалов. Выходное сопротивление передатчика в этих реж1г1мах низкое - не превьшает 50 Ом. Третье состояние передатчика (Выключено), характеризуется неопределенным потенциалом, передаваемым в линию через весьма высокое выходное сопротивление, например, превышающее 10 МОм. Сопротивление резисторов 8 и 10 выбирается намного большим, чем выходное сопротивление передатчика в первых двух состояниях, и намного меньшим, чем выходное сопротивление передатчика в третьм состоянии. Этим условиям в данном случае удовлетворяет сопротивление, рав- ное, например, 15 кОм. С помощью резисторов 8 и 10 шина данных в пассивном состоянии доопределяется до нужI

ных логических уровней: на линиях первой группы устанавливаются., сигна0

5

0

5

0

лы Т

на линиях второй группы

сигналы О

Распаянный таким образом код соответствует команде безусловной передачи управления в некоторую ячейку памяти. При нормальной (безошибочной) работе передатчики не чувствуют резисторов 8 и 10, так как сопротивление этих резисторов, как отмечалось, выбрано достаточно большим.

Устройство работает следуюпщм образом.

Устройство приводится в исходное состояние при подаче отрицательного импульса на линию 25 сброса устройства. Этот импульс проходит через элемент И 16 и сбрасывает триггер 13 по нулевому входу. Нулевой сигнал с выхода триггера 13 воздейству-ет на нулевой вход триггера 12 и поддерживает его в сброшенном состоянии. В исходном состоянии на линии 26 поддерживается сигнал 1, на выходе элемента НЕ 21 - О, на входе одно- вибра.тора 20 - О, на выходе одно- вибратора 20 - 1, Таким образом, 5 в устройстве подготовлены пути прямой и обратной передачи сигналов (отрицательных импульсов) по цепи 26- 14-27 прямой передачи синхроимпульса и 28-15-17-29 обратной передачи ответного сигнала.

При правильной работе процессора указанное.состояние триггеров 12 и 13 остается стабильным. Сигнал на линии 26 подтверждает истинность адреса, установленного на адресной шине (не показана). Сигнал на линии 28 свидетельствует о том, что адрес опознан и соответствующая операция (запись или чтение) вьшолнена адресуемым устройством. При получении ответного сигнала по линии 29 процессор снимает сигнал с линии 26. Адресуемое устройство, в свою очередь, снимает ответный сигнал с линии 28, на этом сеанс ббмена заканчивается. При правильной работе конденсатор 23 не успевает зарядиться через резистор 22 до .порогового напряжения одно вибратора 20 за время существования отрицательного импульса на линии 26. Поэтому на выходе одновибратора 20 постоянно поддерживается сигнал 1, открьшающий элемент И 17 для переда- чи нормального ответного сигнала с выхода элемента ИЛИ 15 на линию 29 и далее в процессор.

При .обращении процессора по несу- ществующему адресу, потенхщал на ли- НИИ 26 остается низким, так как ответного сигнала от устройства нет (эта ситуация называется зависанием По времени, превьппающего максимально допустимое время обмена между устройствами, например, по ис- ,течении 10 мкс (RC-цепи 22-23) сраба тьшает одновибратор 20, на его выходе формируется отрицателвньй импульс, который через, элемент И 17 поступает, в процессор в качестве искусственного ответа, одновременно с этим устанавливается триггер 13 в единичное состояние. Сигнал. А 1 с выхода этого триггера запирает эле- менты ИЛИ 14 и 15, после чего обращение по любому, в том числе и по .правильному адресу остается безответ ;ным. Другими словами, на данном эта- пе устройство усугубило и без того ошибочную ситуацию, полностью изолировав процессор от внешнего мира по управляющим линиям 26 и 29, чтобы процессор обязательно дошел до фазы выбора очередной команды из па- мяти, продвигаясь от зависания к зависанию с периодом, приблизительно равным 10 МКС. Если, например, самая

сложная команда из системы команд процессора требует пяти обращений к памяти, то, в худшем случае, на пятом искусственном зависании процессор обращается за очередной командой (предьщущ11е обращения к магистрали бьии связаны с выполнением этой сложной команды). Таким образом, если изолировать с помощью сигнала А 1 процессор, например, на 100 мкс то он обязательно попадает в ловушку, восприняв в одном из циклов зависания распаянный код как команду, а не как адрес или операнд.

После того как команда воспринята, процессор пытается ее выполнить. Распаянная однословная команда безусловной передачи управления предписывает процессору перейти в фиксированную ячейку памяти в пределах нулевой страницы, например в ячейку OOOF. До тех пор пока магистраль разомкнута сигналом А 1, процессор видит в ячейке OOOF ту ж самую рас паянную команду, хотя в действительности в этой ячейке хранится первая команда программы реакции на зависание. Другими словами, до тех пор по- ,ка А 1, процессор, попав в ловуш- ку, зацикливается на единственньй искусственно заданной команде.

Через интервал времени, определя- емьй элементом задержки 18 (в данном случае приблизительно через 100 мкм) сигнал А 1 поступает на информационный вход триггера 12, и по окончании очередного цикла зависания триггер 12 устанавливается в единичное состояние, так как он срабатывает по положительному фронту сигнала на линии 26. Сигнал О с инверсного выхода триггера 12 проходит через элемент И 16 и вызывает сброс триггера 13 (А 0) , после чего устройство переходит в исходное состояние, при котрром процессор подключается к абонентам. Поэтому процессор при очередной попытке выбора команды из ячейки OOOF увидит в ней настоящую команду и в дальнейшем будет продвигаться по программе реакции на зависание.

Формула изобретения

Устройство для сопряжения процессора с абонентами, содержащее блок канальных приемо-передатчиков, причем блок канальных приемо-передатчиков содержит две группы резисторов, при этом первая группа информационных входов-выходов блока канальных прие.МО-передатчиков через первую группу резисторов подключена к шине единичного потенциала устройства, вторая группа информационных входов-выходов блока канальных приемо-передатчиков через вторую группу резисторов подключена к шине нулевого потенциала устройства, отличающееся тем, что, с целью повьшения .достоверности передачи информации между процессором и абонентами, в блок канальных при2мо-передатчиков введены

.два триггера, два элемента задержки, элемент НЕ и одновибратор, при этом первый вход первого элемента И подключен к общей цепи сброса устройства, первый вход первого элемента ИЛИ соединен с входом элемента НЕ, синх- ровходом первого триггера и подключе к выходу синхронизации процессора, выход второго элемента И подключен

к входу ответного сигнала процессора, первый вход второго элемента ИЛИ подключен к выходу ответного сигнала абонента, выход первого элемента ИЛИ подключен к входу синхронизации абонента,, причем выход элемента НЕ соединен с входом первого элемента за- держ1си, выход которого соединен с входом одновибратора, выход которого соединен с единичным входом первого триггера и первым входом второго элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с вто- рым входом первого элемента ИЛИ, единичным выходом второго триггера, нулевым входом первого триггера и входом второго элемента задержки, выход , которого соединен с информационным входом первого триггера, нулевой выход которого соединен с вторым входом первого элемента И, выход которого соединен с нулевым выходом второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1982 |

|

SU1076895A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1983 |

|

SU1132283A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для управления обменом информации процессора с внешними устройствами | 1988 |

|

SU1508223A1 |

| Устройство для контроля данных электронной вычислительной машины при прерываниях питания | 1983 |

|

SU1129615A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для подключения абонентов к общей магистрали | 1983 |

|

SU1180912A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных устройствах, построенных по принципу общей магистрали. Целью изобрете-- ния является повышение достоверности передачи информации между процессором и абонентами. В устройстве содержится блок канальных приемо-передат- чиков, состоящий из двух групп резисторов, двух триггеров, двух элементов И, двух элементов ИЛИ , двух элементов задержки, элемента НЕ, одно- вибратора. При этом разрядные цепи через две группы резисторов подключены к шинам единичного и нулевого потенциалов устройства таким образом, что на общей информационной магистрали, Защита будет однословная команда безусловной передачи управления в некоторую ячейку памяти. Логика работы устройства построена таким образом, что при любой сбойной ситуации управление передается всегда на начало программы реакции на сбойную ситуацию. 1 ил. i (Л 1С 4 4 Од СЬ СО

Редактор М.Циткина

Заказ 39t9/52Тираж 671Подписное

ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

.Производственно-полиграфическое предприятие .Ужгород, ул .Проектная, 4

Составитель С.Пестг-гал

Техред М.Ходанич Корректор А,

| Авторское свидетельство СССР № 1043621, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения непредельных спиртов | 1936 |

|

SU51905A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-15—Публикация

1984-12-21—Подача