Изобретение относится к цифровой вычислительной технике, в частности к устройствам для подключения нескольких источников информации к общей магистрали, и может быть использовано в системах обработки данных для управления доступом к коллективно используемым ресурсам.

Целью изобретения является повышение быстродействия устройства за счет сокращения времени прохождения сигнала кольцевого опроса через каналы, не имеющие заявок на обслуживание.

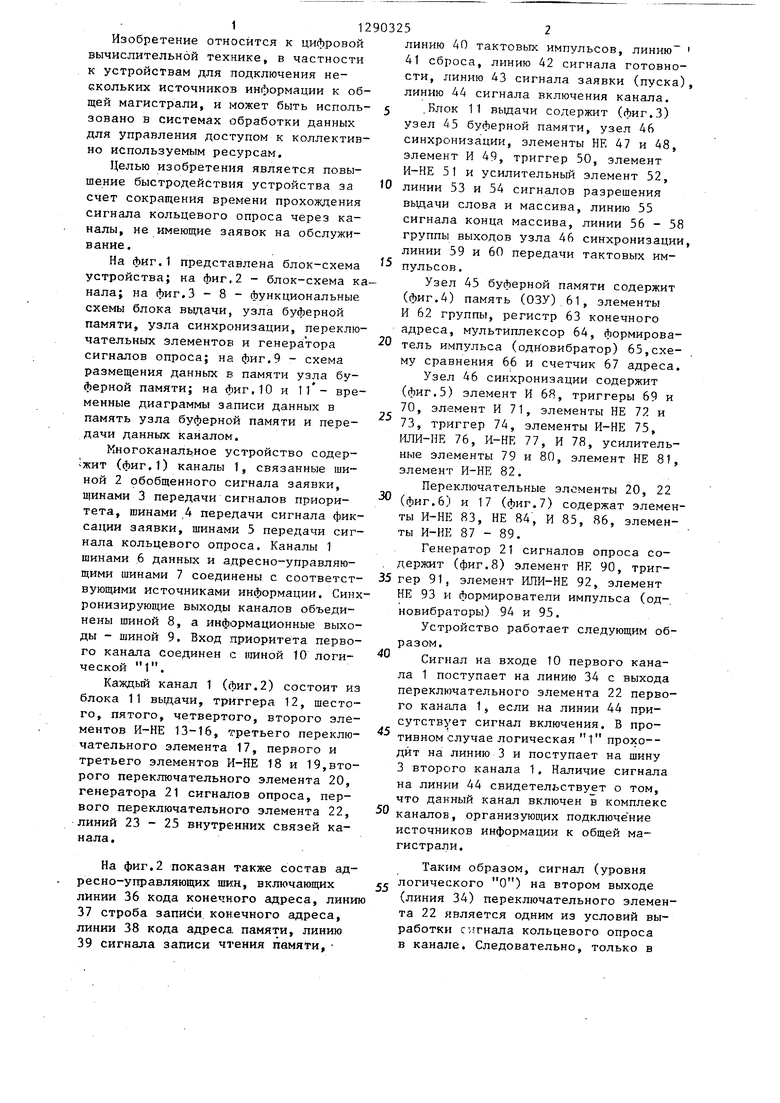

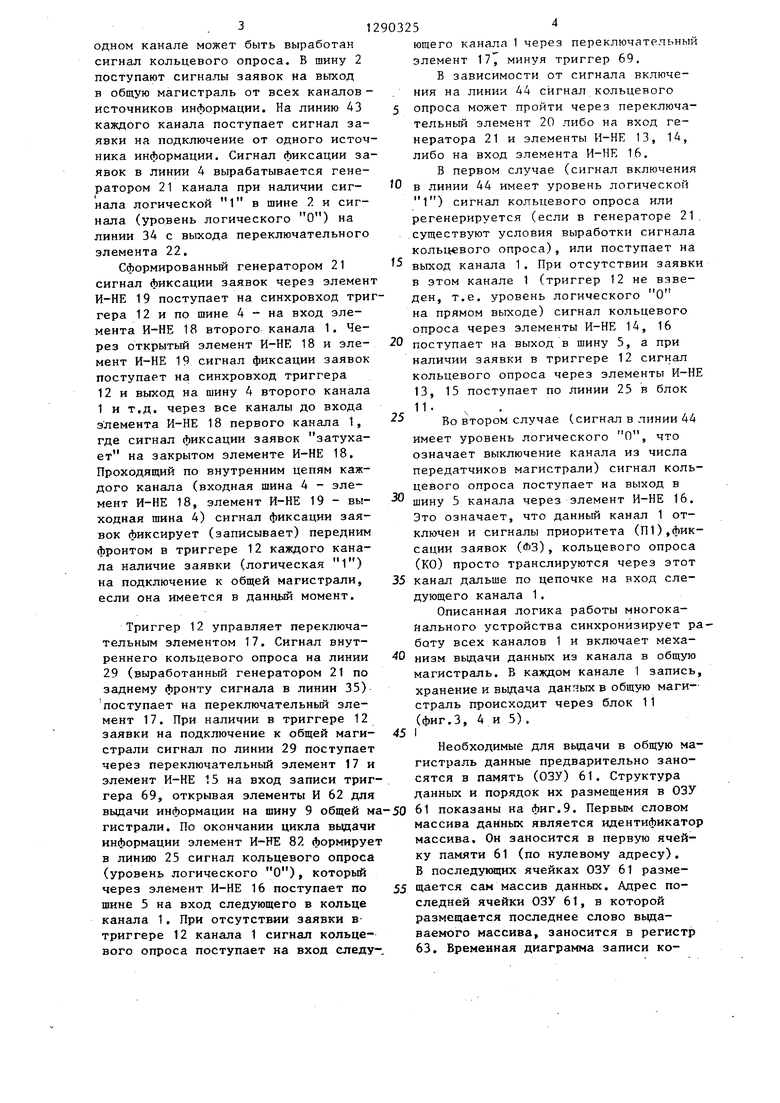

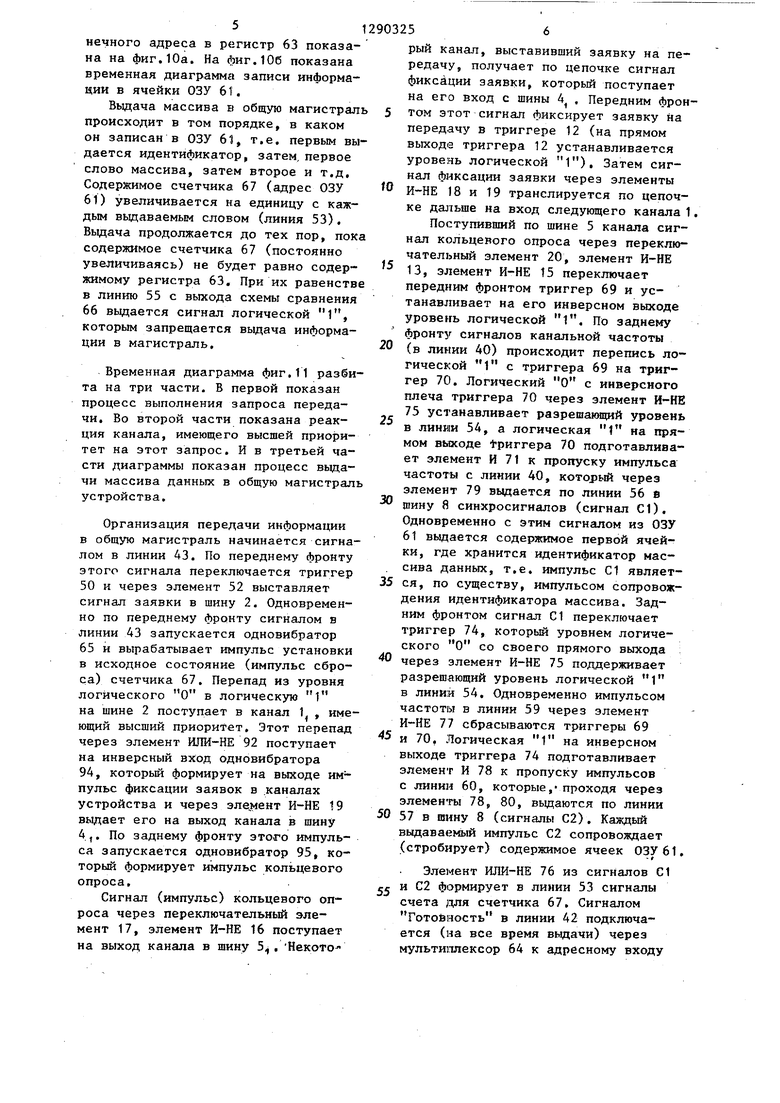

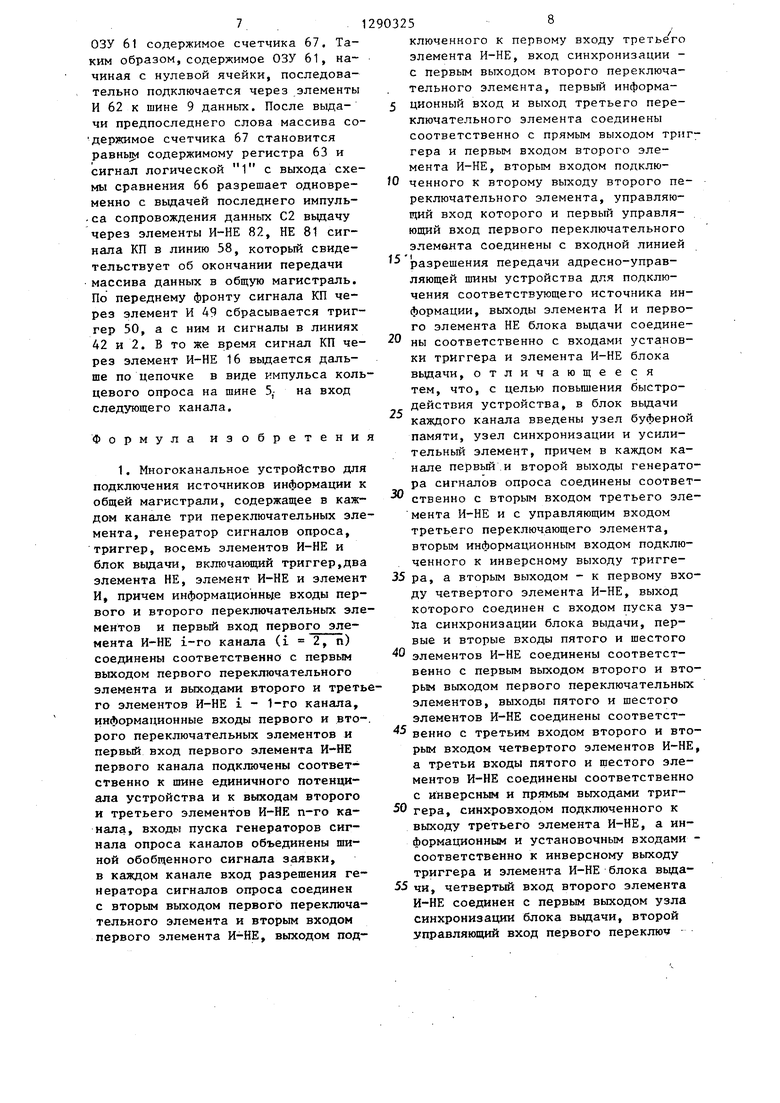

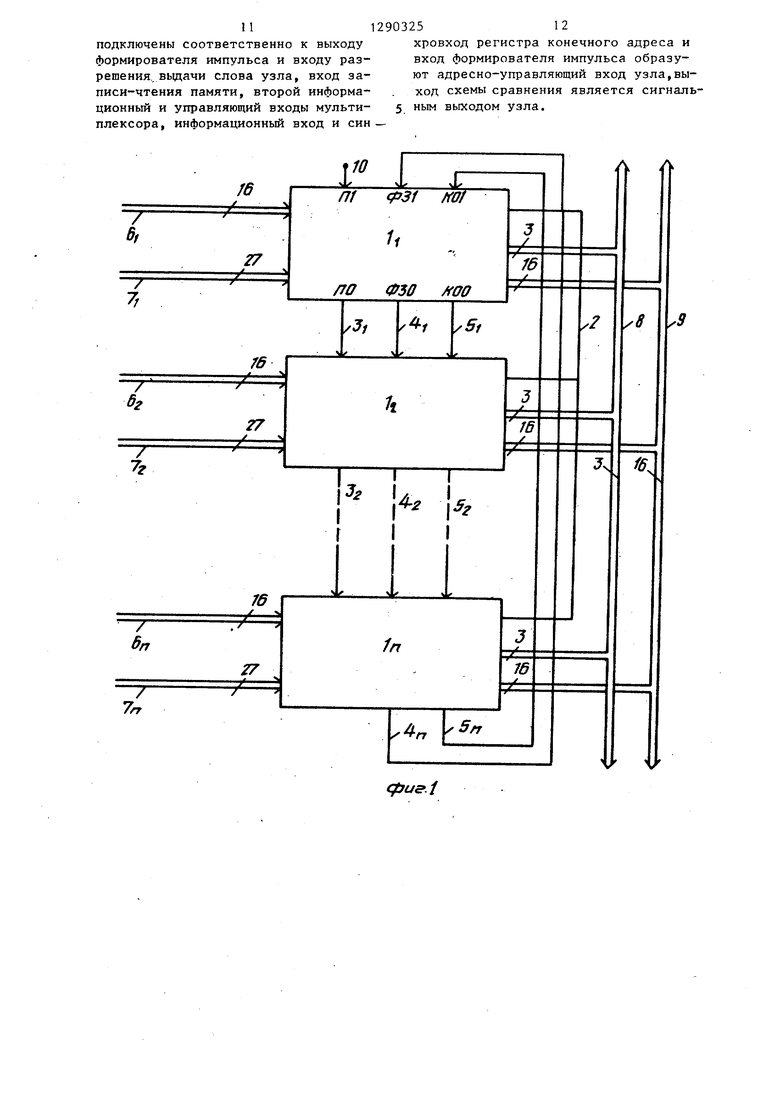

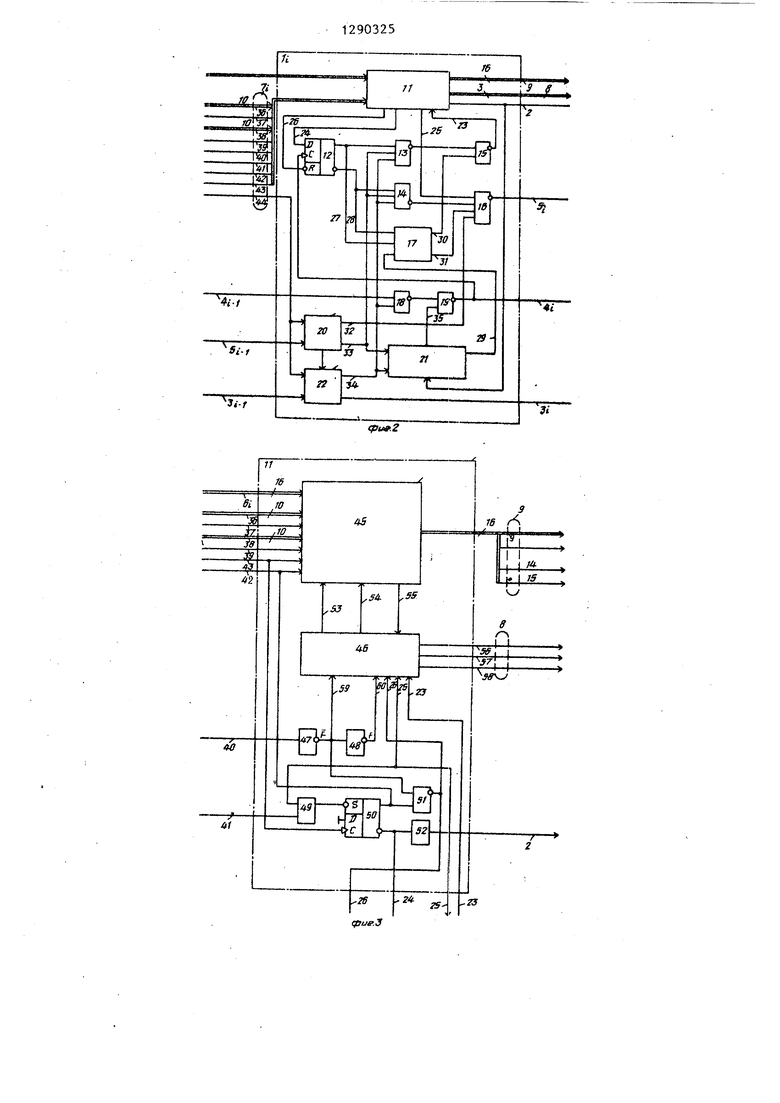

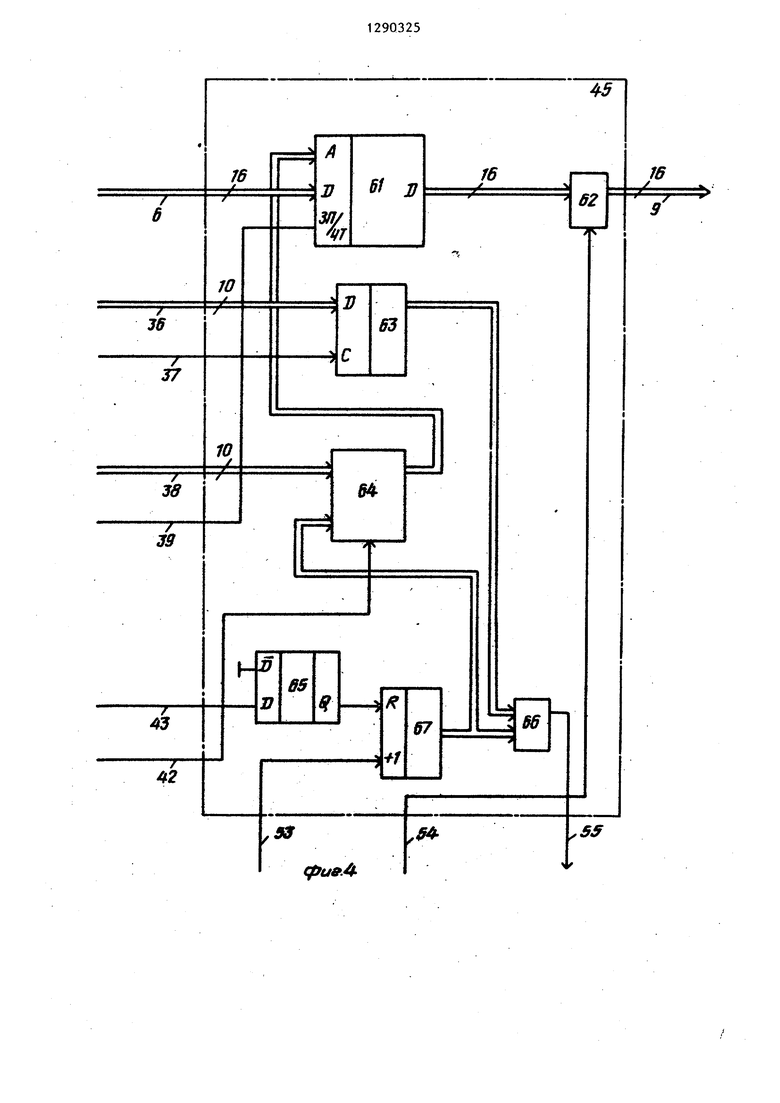

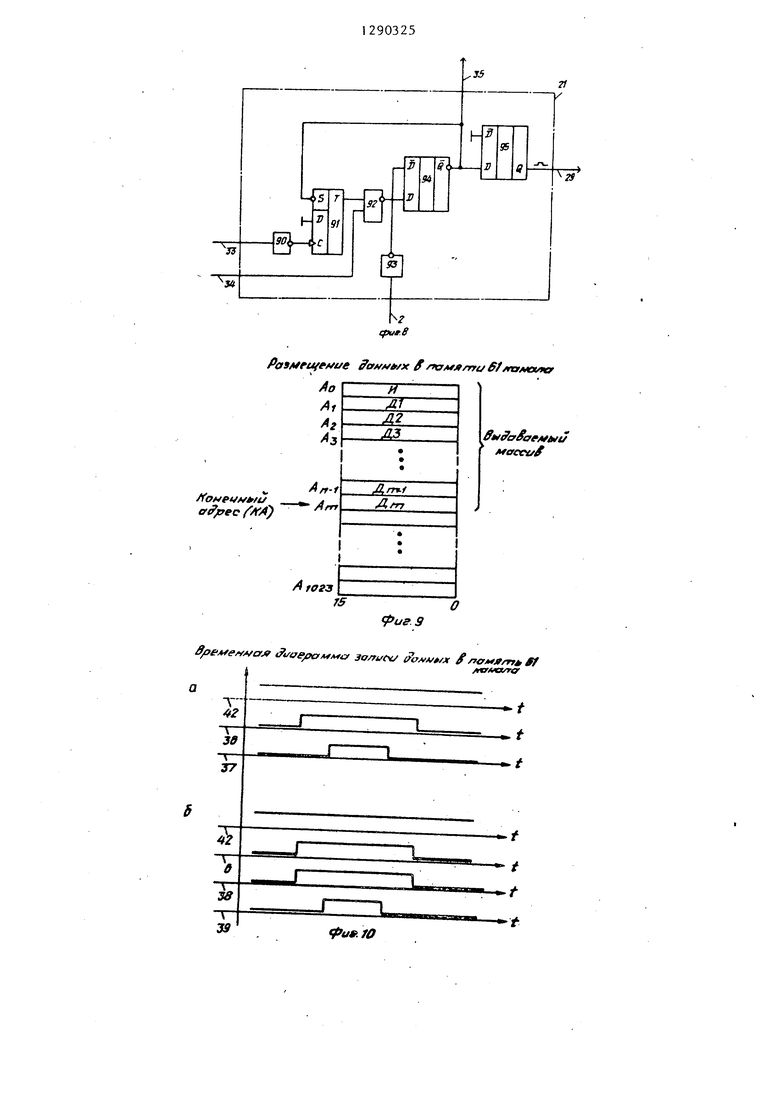

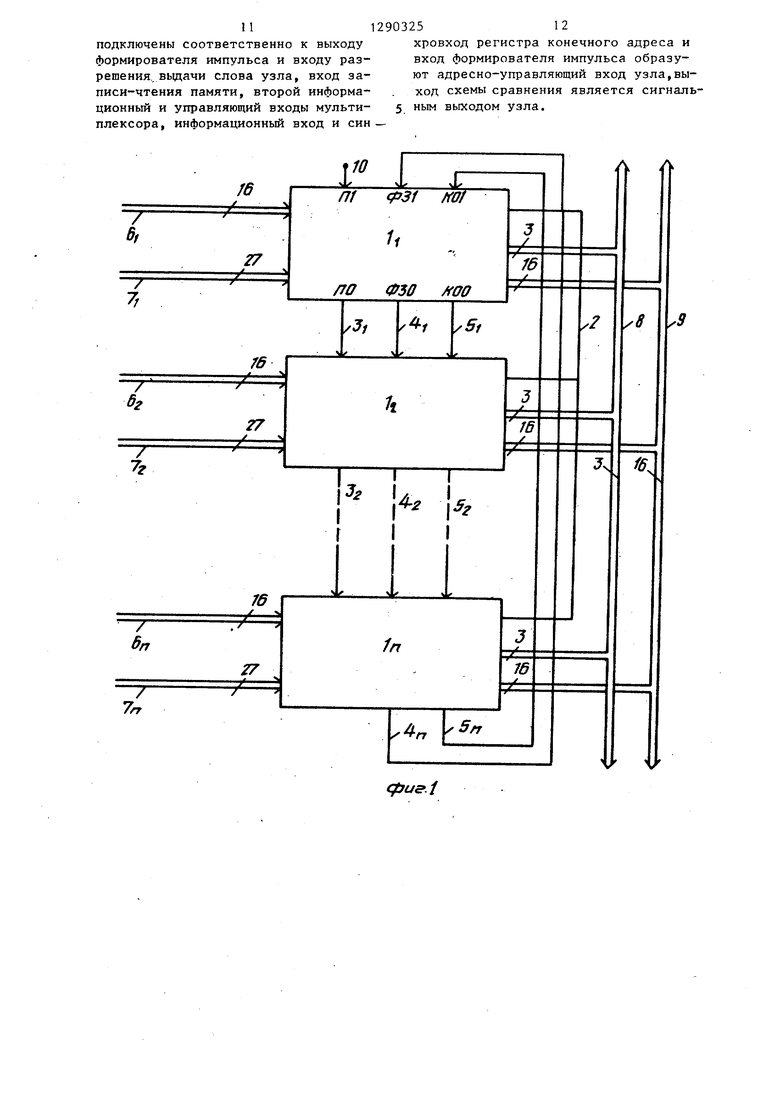

На фиг.1 представлена блок-схема устройства; на фиг,2 - блок-схема канала; на фиг.З - 8 - функциональные схемы блока выдачи, узла буферной памяти, узла синхронизации, переключательных элементоЕ и генератора сигналов опроса; на фиг.9 - схема размещения данных в памяти узла буферной памяти; на фиг.10 и 11 - временные диаграммы записи данных в память узла буферной памяти и передачи данных каналом.

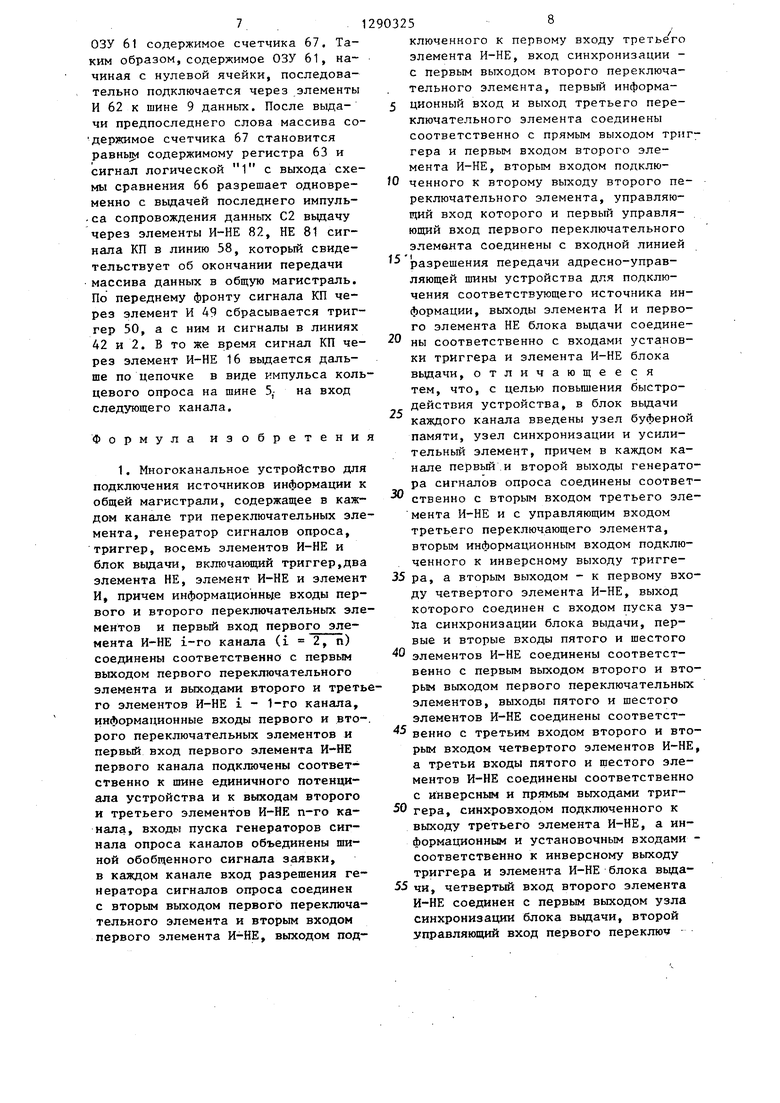

Многоканальное устройство содер- -жит (фиг.1) каналы 1, связанные шиной 2 обобщенного сигнала заявки, щинами 3 передачи сигналов приоритета, шинами ,4 передачи сигнала фиксации заявки, шинами 5 передачи сигнала кольцевого опроса. Каналы 1 шинами 6 данных и адресно-управляю- щими шинами 7 соединены с соответствующими источниками информации. Синхронизирующие выходы каналов объединены шиной 8, а информационные выходы - шиной 9. Вход приоритета первого канала соединен с нтиной 10 логической 1.

Каждый канал 1 (фиг.2) состоит из блока 11 выдачи, триггера 12, шестого, пятого, четвертого, второго элементов И-НЕ 13-16, третьего переключательного элемента 17, первого и третьего элементов И-НЕ 18 и 19,второго переключательного элемента 20, генератора 21 сигналов опроса, первого переключательного элемента 22, линий 23 - 25 внутренних связей канала .

На фиг.2 показан также состав ад- ресно-уиравляющих шин, включающих линии 36 кода конечного адреса, лини 37 строба записи, конечного адреса, линии 38 кода адреса памяти, линию 39 сигнала записи чтения памяти,

5

0

5

линию АО тактовых импульсов, линию 41 сброса, линию 42 сигнала готовности, линию 43 сигнала заявки (пуска), линию 44 сигнала включения канала. .Блок 11 вьщачи содержит (фиг.З) узел 45 буферной памяти, узел 46 синхронизации, элементы НЕ 47 и 48, элемент И 49, триггер 50, элемент И-НЕ 51 и усилительный элемент 52, линии 53 и 54 сигналов разрешения выдачи слова и массива, линию 55 сигнала конца массива, линии 56 - 58 группы выходов узла 46 синхронизации, линии 59 и 60 передачи тактовых импульсов.

Узел 45 буферной памяти содержит (фиг.4) память (ОЗУ) 61, элементы И 62 группы, регистр 63 конечного адреса, мультиплексор 64, формирователь импульса (одновибратор) 65,схему сравнения 66 и счетчик 67 адреса.

Узел 46 синхронизации содержит (фиг.5) элемент И 68, триггеры 69 и 70, элемент И 71, элементы НЕ 72 и 73, триггер 74, элементы И-НЕ 75, ИЛИ-НЕ 76, И-НЕ 77, И 78, усилительные элементы 79 и 80, элемент НЕ 81, элемент И-НЕ 82.

Переключательные элементы 20, 22 (фиг.6) и 17 (фиг.7) содержат элементы И-НЕ 83, НЕ 84, И 85, 86, элементы И-НЕ 87-89.

Генератор 21 сигналов опроса со- . держит (фиг.8) элемент НЕ 90, триг- 5 гер 91, элемент ИЛИ-НЕ 92, элемент НЕ 93 и формирователи импульса (од- новибраторы) 94 и 95.

Устройство работает следующим образом.

Сигнал на входе 10 первого канала 1 поступает на линию 34 с выхода переключательного элемента 22 первого канала 1, если на линии 44 присутствует сигнал включения. В противном случае логическая 1 прохо-- дйт на линию 3 и поступает на шину 3 второго канала 1. Наличие сигнала на линии 44 свидетельствует о том, что данный канал включен в комплекс каналов, организуюо1их подключе ние источников информации к общей магистрали.

Таким образом, сигнал (уровня логического О) на втором выходе (линия 34) переключательного элемента 22 является одним из условий выработки С ,гнала кольцевого опроса в канале. Следовательно, только в

0

0

50

55

одном канале может быть выработан сигнал кольцевого опроса. В шину 2 поступают сигналы заявок на выход в общую магистраль от всех каналов - источников информации. На линию A3 каждого канала поступает сигнал заявки на подключение от одного источника информации. Сигнал фиксации заявок в линии 4 вырабатывается генератором 21 канала при наличии сиг- нала логической 1 в шине 2 и сигнала (уровень логического О) на линии 34 с выхода переключательного элемента 22.

Сформированный генератором 21 сигнал фиксации заявок через элемен И-НЕ 19 поступает на синхровход тригера 12 и по шине 4 - на вход элемента И-НЕ 18 второго канала 1. Через открытый элемент И-НЕ 18 и элемент И-НЕ 19 сигнал фиксации заявок поступает на синхровход триггера 12 и выход на шину 4 второго канала 1 и т.д. через все каналы до входа элемента И-НЕ 18 первого канала 1, где сигнал фиксации заявок затухает на закрытом элементе И-НЕ 18. Проходящий по внутренним цепям каждого канала (входная шина 4 - элемент И-НЕ 18, элемент И-НЕ 19 - выходная шина 4) сигнал фиксации заявок фиксирует (записывает) передним фронтом в триггере 12 каждого канала наличие заявки (логическая 1) на подключение к общей магистрали, если она имеется в данный момент.

Триггер 12 управляет переключательным элементом 17. Сигнал внутреннего кольцевого опроса на линии 40 29 (выработанный генератором 21 по заднему фронту сигнала в линии 35) поступает на переключательный элемент 17. При наличии в триггере 12 заявки на подключение к общей маги- 45 I страли сигнал по линии 29 поступает через переключательный элемент 17 и элемент И-НЕ 15 на вход записи триггера 69, открывая элементы И 62 для

Описанная логика работы многоканального устройства синхронизирует работу всех каналов 1 и включает механизм вьщачи данных из канала в общую магистраль. В каждом канале 1 запись, хранение и вьщача данных в общую магистраль происходит через блок 11 (фиг.З, 4 и 5).

Необходимые для вьщачи в общую магистраль данные предварительно заносятся в память (ОЗУ) 61. Структура данных и порядок их размещения в ОЗУ выдачи информации на шину 9 общей на-50 61 показаны на фиг.9. Первым словом гистрали. По окончании цикла выдачи массива данных является идентификатор

информации элемент И-НЕ 82 формирует в линию 25 сигнал кольцевого опроса (уровень логического О), который через элемент И-НЕ 16 поступает по шине 5 на вход следующего в кольце канала 1. При отсутствии заявки в триггере 12 канала 1 сигнал кольцевого опроса поступает на вход следу-.

О

5 5

0

5

0

0 5 I

ющего канала 1 через переключательный элемент 17 минуя триггер 69.

В зависимости от сигнала включения на линии 44 сигнал кольцевого опроса может пройти через лереключа- тельньсй элемент 20 либо на вход генератора 21 и элементы И-НЕ 13, 14, либо на вход элемента И-НЕ 16.

В первом случае (сигнал включения в линии 44 имеет уровень логической 1) сигнал кольцевого опроса или регенерируется (если в генераторе 21 существуют условия выработки сигнала кольцевого опроса), или поступает на выход канала 1. При отсутствии заявки в этом канале 1 (триггер 12 не взведен, т.е. уровень логического О на прямом выходе) сигнал кольцевого опроса через элементы И-НЕ 14, 16 поступает на выход в шину 5, а при наличии заявки в триггере 12 сигнал кольцевого опроса через элементы И-НЕ 13, 15 поступает по линии 25 в блок 11.

Во втором случае (сигнал в линии 44

имеет уровень логического О, что означает выключение канала из числа передатчиков магистрали) сигнал кольцевого опроса поступает на выход в шину 5 канала через элемент И-НЕ 16. Это означает, что данный канал 1 отключен и сигналы приоритета (П1),фиксации заявок (лз), кольцевого опроса (ко) просто транслируются через этот канал дальше по цепочке на вход следующего канала 1.

Описанная логика работы многоканального устройства синхронизирует работу всех каналов 1 и включает механизм вьщачи данных из канала в общую магистраль. В каждом канале 1 запись, хранение и вьщача данных в общую магистраль происходит через блок 11 (фиг.З, 4 и 5).

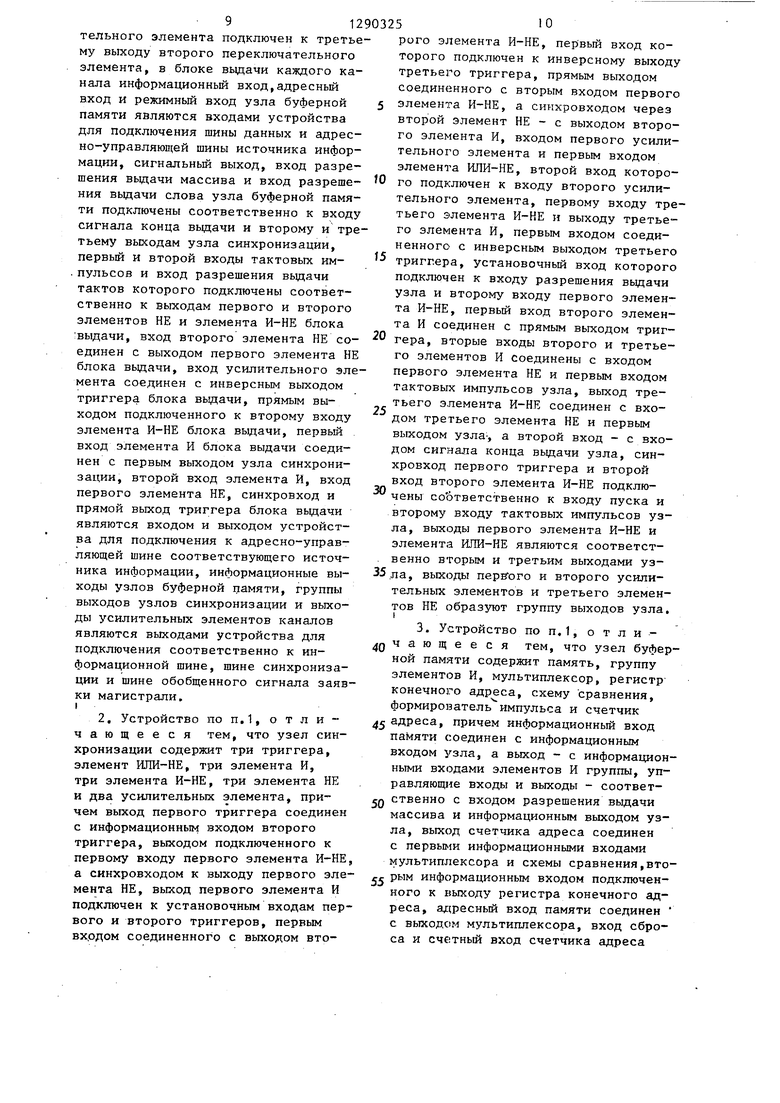

массива. Он заносится в первую ячейку памяти 61 (по нулевому адресу), В последующих ячейках ОЗУ 61 разме- 55 щается сам массив данных. Адрес последней ячейки ОЗУ 61, в которой размещается последнее слово выдаваемого массива, заносится в регистр 63. Временная диаграмма записи ковечного адреса в регистр 63 показана на фиг.Юа. На фиг. 106 показана временная диаграмма записи информации в ячейки ОЗУ 61.

Выдача массива в общую магистрал происходит в том порядке, в каком он записан в ОЗУ 61, т.е. первым выдается идентификатор, затем, первое слово массива, затем второе и т.д. Содержимое счетчика 67 (адрес ОЗУ 61) увеличивается на единицу с каждым вьщаваемым словом (линия 53). Выдача продолжается до тех пор, пок содержимое счетчика 67 (постоянно увеличиваясь) не будет равно содер жимому регистра 63, При их равенств в линию 55 с выхода схемы сравнения 66 выдается сигнал логической 1, которым запрещается выдача информации в магистраль.

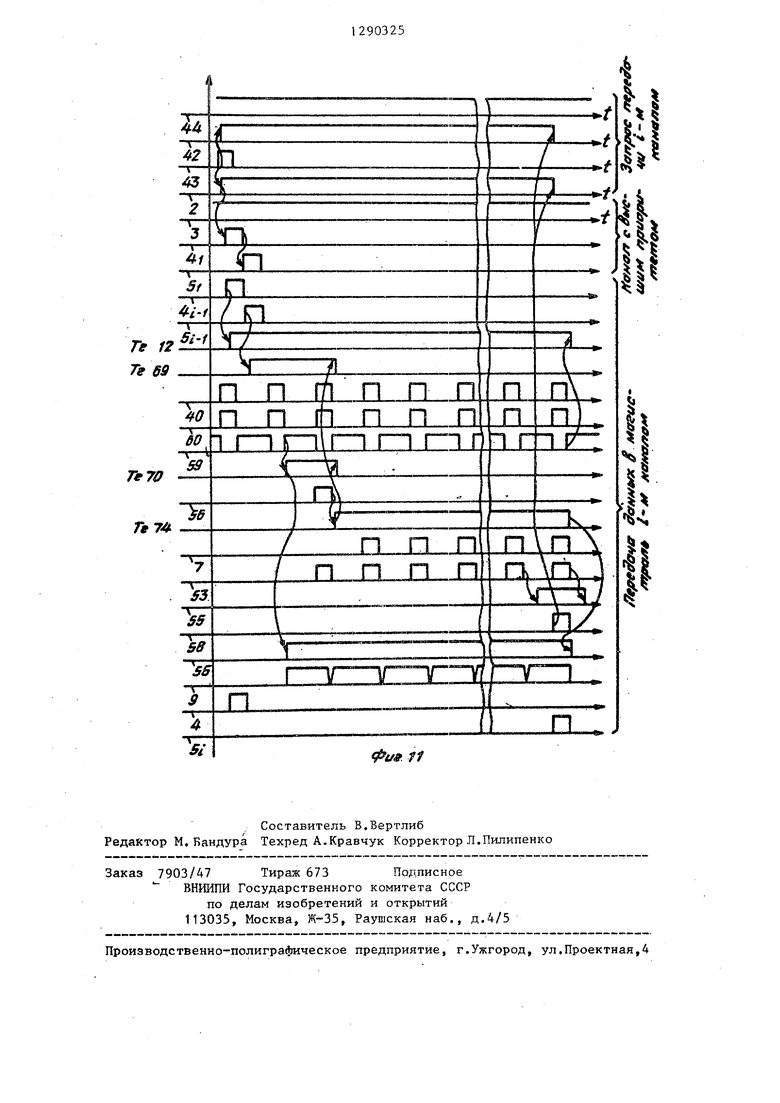

Временная диаграмма фиг.11 разбита на три части. В первой показан процесс выполнения запроса передачи. Во второй части показана реакция канала, имеющего высшей приоритет на этот запрос. И в третьей части диаграммы показан процесс вьща- чи массива данных в общую магистрал устройства.

Организация передачи информации в общую магистраль начинается сигналом в линии 43. По переднему фронту этого сигнала переключается триггер 50 и через элемент 52 выставляет сигнал заявки в шину 2. Одновременно по переднему фронту сигналом в линии 43 запускается одновибратор 65 и вырабатывает импульс установки в исходное состояние (импульс сброса) счетчика 67. Перепад из уровня логического О в логическую 1 на шине 2 поступает в канал 1 , имеющий высший приоритет. Этот перепад через элемент ИЛИ-НЕ 92 поступает на инверсный вход одновибратора 94, которьй формирует на выходе импульс фиксации заявок в каналах устройства и через элемент И-НЕ 19 выдает его на выход канала в щину 4.,. По заднему фронту этого импульса запускается одновибратор 95, который формирует импульс кольцевого опроса.

Сигнал (импульс) кольцевого опроса через переключательньй элемент 17, элемент И-НЕ 16 поступает на выход канала в шину 5. Некото

рый канал, выставивший заявку на передачу, получает по цепочке сигнал фиксации заявки, который поступает на его вход с шины 4 . Передним фронтом этот сигнал фиксирует заявку На передачу в триггере 12 (на прямом выходе триггера 12 устанавливается уровень логической 1), Затем сигнал фиксации заявки через элементы

И-НЕ 18 и 19 транслируется по цепочке дальше на вход следующего канала 1.

Поступивший по шине 5 канала сигнал кольцевого опроса через переключательный элемент 20, элемент И-НЕ

13, элемент И-НЕ 15 переключает передним фронтом триггер 69 и устанавливает на его инверсном выходе уровень логической 1. По заднему фронту сигналов канальной частоты

(в линии 40) происходит перепись логической 1 с триггера 69 на триггер 70. Логический О с инверсного плеча триггера 70 через элемент И-НЕ 75 устанавливает разрешающий уровень в линии 54, а логическая 1 на прямом выходе tpHrrepa 70 подготавливает элемент И 71 к пропуску импульса частоты с линии 40, который через элемент 79 ведается по линии 56 в

тину 8 синхросигналов (сигнал С1). Одновременно с этим сигналом из ОЗУ 61 вьздается содержимое первой ячейки, где хранится идентификатор мас- сива данных, т.е. импульс С1 является, по существу, импульсом сопровождения идентификатора массива. Задним фронтом сигнал С1 переключает триггер 74, которьй уровнем логического О со своего прямого выхода

через элемент И-НЕ 75 поддерживает разрешающий уровень логической 1 в линий 54. Одновременно импульсом частоты в линии 59 через элемент И-НЕ 77 сбрасываются триггеры 69

и 70, Логическая 1 на инверсном выходе триггера 74 подготавливает элемент И 78 к пропуску импульсов с линии 60, которые, проходя через элементы 78, 80, вьщаются по линии

57 в шину 8 (сигналы С2). Каждый выдавае№)1Й импульс С2 сопровождает (стробирует) содержимое ячеек ОЗУ 61.

Элемент ИЛИ-НЕ 76 из сигналов С1 и С2 формирует в линии 53 сигналы счета для счетчика 67. Сигналом Готойность в линии 42 подключается (на все время выдачи) через мультиплексор 64 к адресному входу

ОЗУ 61 содержимое счетчика 67. Таким образом, содержимое ОЗУ 61, начиная с нулевой ячейки, последовательно подключается через элементы И 62 к шине 9 данных. После выдачи предпоследнего слова массива со держнмое счетчика 67 становится равньм содержимому регистра 63 и сигнал логической 1 с выхода схемы сравнения 66 разрешает одновременно с вьщачей последнего импуль- -са сопровождения данных С2 вьщачу через элементы И-НЕ 82, НЕ 81 сигнала КП в линию 58, который свидетельствует об окончании передачи массива данных в общую магистраль. По переднему фронту сигнала КП через элемент И 49 сбрасывается триггер 50, а с ним и сигналы в линиях 42 и 2. В то же время сигнал КП через элемент И-НЕ 16 выдается дальше по цепочке в виде импульса кольцевого опроса на шине 5,- на вход следующего канала.

Формула изобретени

1. Многоканальное устройство для подключения источников информации к общей магистрали, содержащее в каждом канале три переключательных элемента, генератор сигналов опроса, триггер, восемь элементов И-НЕ и блок вьщачи, включающий триггер,два элемента НЕ, элемент И-НЕ и элемент И, причем информационные входы первого и второго переключательных элементов и первый вход первого эле- мента И-НЕ i-ro канала (i 2, п) соединены соответственно с первым выходом первого переключательного элемента и выходами второго и третьго элементов И-НЕ i - 1-го канала, информационные входы первого и второго переключательных элементов и первый вход первого элемента И-НЕ первого канала подключены соответственно к шине единичного потенциала устройства и к выходам второго и третьего элементов И-НЕ п-го канала, входы пуска генераторов сигнала опроса каналов объединены шиной обобщенного сигнала заявки, в каждом канале вход разрешения генератора сигналов опроса соединен с вторым выходом первого переключательного элемента и вторым входом первого элемента И-НЕ, выходом цод

5

0

5

0

5

0

5

0

5

ключенного к первому входу третьего элемента И-НЕ, вход синхронизации - с первым выходом второго переключательного элемента, первый информационный вход и выход третьего переключательного элемента соединены соответственно с прямым выходом триггера и первым входом второго элемента И-НЕ, вторым входом подключенного к второму выходу второго переключательного элемента, управляющий вход которого и первый управляющий вход первого переключательного элемента соединены с входной линией разрешения передачи адресно-управ- ляющей шины устройства для подключения соответствующего источника информации, выходы элемента И и первого элемента НЕ блока выдачи соединены соответственно с входами установки триггера и элемента И-НЕ блока выдачи, отличающееся тем, что, с целью повьш1ения быстродействия устройства, в блок выдачи каждого канала введены узел буферной памяти, узел синхронизации и усилительный элемент, причем в каждом канале первый и второй выходы генератора сигналов опроса соединены соответственно с вторым входом третьего эле- мента И-НЕ и с управляющим входом третьего переключающего элемента, вторым информационным входом подключенного к инверсному выходу триггера, а вторым выходом - к первому входу четвертого элемента И-НЕ, выход которого соединен с входом пуска уз- Jia синхронизации блока выдачи, первые и вторые входы пятого и шестого элементов И-НЕ соединены соответственно с первым выходом второго и вторым выходом первого переключательных элементов, выходы пятого и шестого элементов И-НЕ соединены соответственно с третьим входом второго и вторым входом четвертого элементов И-НЕ, а третьи входы пятого и щестого элементов И-НЕ соединены соответственно с инверсным и прямым выходами триггера, синхровходом подключенного к выходу третьего элемента И-НЕ, а информационным и установочным входами - соответственно к инверсному выходу триггера и элемента И-НЕ блока выдачи, четвертый вход второго элемента И-НЕ соединен с первым выходом узла синхронизации блока выдачи, второй управляющий вход первого переключ

ельного элемента подключен к третьеу выходу второго переключательного лемента, в блоке выдачи каждого каала информационньй вход,адресный вход и режимный вход узла буферной памяти являются входами устройства ля подключения шины данных и адрес- но-управляющей шины источника инфорации, сигнальный выход, вход разреения выдачи массива и вход разрешеия выдачи слова узла буферной памяти подключены соответственно к входу сигнала конца вьщачи и второму и третьему выходам узла синхронизации, первый и второй входы тактовых им- пульсов и вход разрешения выдачи тактов которого подключены соответственно к выходам первого и второго элементов НЕ и элемента И-НЕ блока выдачи, вход второго элемента НЕ соединен с выходом первого элемента НЕ блока вьщачи, вход усилительного элемента соединен с инверсным выходом триггера блока выдачи, прямым выходом подключенного к второму входу элемента И-НЕ блока вьщачи, первый вход элемента И блока выдачи соединен с первым выходом узла синхронизации, второй вход элемента И, вход первого элемента НЕ, синхровход и прямой вьпсод триггера блока вьщачи являются входом и выходом устройства для подключения к адресно-управ- ляющей шине соответствующего источника информации, информационные выходы узлов буферной памяти, группы выходов узлов синхронизации и выходы усилительных элементов каналов являются вькодами устройства для подключения соответственно к информационной шине, шине синхронизации и шине обобщенного сигнала заявки магистрали, I

2. Устройство по п.1, о т л и - чающееся тем, что узел синхронизации содержит три триггера, элемент ИЛИ-НЕ, три элемента И, три элемента И-НЕ, три элемента НЕ и два усилительных элемента, причем выход первого триггера соединен с информационным входом второго триггера, выходом подключенного к первому входу первого элемента И-НЕ, а синхровходом к выходу первого элемента НЕ, выход первого элемента И подключен к установочным входам первого и второго триггеров, первьм вх.одом соединенного с выходом вто

5

рого элемента И-НЕ, первый вход которого подключен к инверсному выходу третьего триггера, прямым выходом соединенного с вторым входом первого элемента И-НЕ, а синхровходом через второй элемент НЕ - с выходом второго элемента И, входом первого усилительного элемента и первым входом элемента ИЛИ-НЕ, второй вход которого подключен к входу второго усилительного элемента, первому входу третьего элемента И-НЕ и выходу третьего элемента И, первьм входом соединенного с инверсным выходом третьего триггера, установочный вход которого подключен к входу разрешения вьщачи узла и второму входу первого элемента И-НЕ, первый вход второго элемента И соединен с прямым выходом триггера, вторые входы второго и третьего элементов И соединены с входом первого элемента НЕ и первым входом тактовых импульсов узла, выход третьего элемента И-НЕ соединен с входом третьего элемента НЕ и первым выходом узла-, а второй вход - с входом сигнала конца вьщачи узла, синхровход первого триггера и второй вход второго элемента И-НЕ подключены соответственно к входу пуска и второму входу тактовых импульсов узла, выходы первого элемента И-НЕ и элемента ИЛИ-НЕ являются соответст- . веяно вторым и третьим выходами уз- 5 ла, выходы и второго усилительных элементов и третьего элементов НЕ образJTOT группу выходов узла.

0

5

0

3. Устройство по п.1, о

т л и чающееся тем, что узел буферной памяти содержит память, группу элементов И, мультиплексор, регистр конечного адреса, схему сравнения, формирователь импульса и счетчик

адреса, причем информационный вход памяти соединен с информационным входом узла, а выход - с информационными входами элементов И группы, управляющие входы и выходы - соответCQ ственно с входом разрешения вьщачи массива и информационным выходом узла, выход счетчика адреса соединен с первыми информационными входами мультиплексора и схемы сравнения,втоее рым информационным входом подключенного к выходу регистра конечного адреса, адресный вход памяти соединен с выходом мультиплексора, вход сброса и счетный вход счетчика адреса

11

подключены соответственно к выходу формирователя импульса и входу разрешения, выдачи слова узла, вход записи-чтения памяти, второй информационный и управляющий входы мультиплексора, информационный вход и син

1290325

12

н

хровход регистра конечного адреса и вход формирователя импульса образуют адресно-управляющий вход узла,выход схемы сравнения является сигналь- 5 ным выходом узла.

fpue.i

epuf.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для подключения источников информации к общей магистрали | 1987 |

|

SU1432539A2 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1305698A1 |

| Устройство для сопряжения | 1980 |

|

SU903853A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1455342A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Устройство для управления обменом информации процессора с внешними устройствами | 1988 |

|

SU1508223A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в системах, имеющих несколько источников информации. Целью изобретения является повьше- ние быстродействия устройства за счет ускоренной трансляции сигнала опроса заявок через каналы, не имеющие заявок на передачу. Цель достигается тем, что в устройство, содержащее в каждом канале три переключательных элемента, генератор сигналов опроса, триггер, восемь элементов И-НЕ и блок выдачи 11, включающий триггер, два элемента НЕ, элемент И-НЕ и элемент И, введены в блоки вьщачи каналов узел буферной памяти, узел синхронизации и усилительный элемент. 2 з.п. ф-лы, 11 ил. с ьо :о ьс ел

to

lEI

,ю

t Se

IS

42

«f

Ef-S

45

9

/g ,

i /4

.55

75

4

45

W

-Ji№ j5

27

ta

41

J2

,2

X

гзг

76

/4 27

ЗЛ/ /ui

7 J

10

D

38

h

27

es

SI

/ЛЗГ

(

Sf D

16

л

;

6467

x

55

gyuf.S

а

Si.f

Л-1

(риг.6

Т

J2

ffSQ

33

..j

87

J4

85

V

Г7

Л-

J/

Pa9AtfUfffft/e ffoMMf/x f fra fJt/rruBf faMOi/ e

A/1-i

л

Л А)

750

ff ue 9

ff/je e cf Л/аге/юл мо foMf/t M / /icr fjr/Tr ff

/fOffOffOr

T «

и

5

J9

s

1

ftuf.JO

i t

-t

Те 12 Те 69

Составитель В.Вертлиб Редактор М, Бандура Техред А.Кравчук Корректор Л.Пилипенко

Заказ 7903/47 Тираж 673 Подписное ВНЙИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Многоканальное устройство для подключения источников информации к общей магистрали | 1977 |

|

SU684536A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1981 |

|

SU1012233A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-08-06—Подача