Фиг.Г

|дпя передачи сигналов; она работает IB параллельном или последовательном |режиме, задаваемом сигналами на ее входах. Запрос от любого процессора поступает в блок 1. Блок 1 при наличии в нем заявки выдает в ответ на запрос сигнал разрешения, последовательно проходящий через процессоры Zf-Zn, и заявку на шину данньк и шину адреса. Заявка поступает для обработки в свободный процессор с высшим приоритетом. В случае звзаимозависи - мык заявок каждая очередная заявка поступает в буферный блок 10 того процессора, который в данньй момент обрабатывает заявку с тем же адресом. В зависимости от признака алгоритма

14553А2

обработки процессор переходит либо к. рекуррентной, либо к массивной технологии обработки. При рекуррентной обработке поступившие в процессор зависимые заявки считываются из накопителя буферного блока 10 последовательно по принципу первым пришел, первым обслужен, при этом буферный блок 10 работает как обычный кольцевой буфер. При массивной обработке происходит предварительное накопление массива заявок в одном накопителе буферного блока 10 и считывание на обработку по произвольным адресам заявок из другого накопителя буферного блока 10, при этом буферньй блок 10 работает как двухкарманный буфер. 16 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451713A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451712A1 |

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1290325A1 |

| Адаптивная система обработки данных | 1988 |

|

SU1552195A1 |

| Устройство для сопряжения | 1981 |

|

SU1001072A1 |

| Адаптивная система обработки данных | 1988 |

|

SU1509921A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1987 |

|

SU1432539A2 |

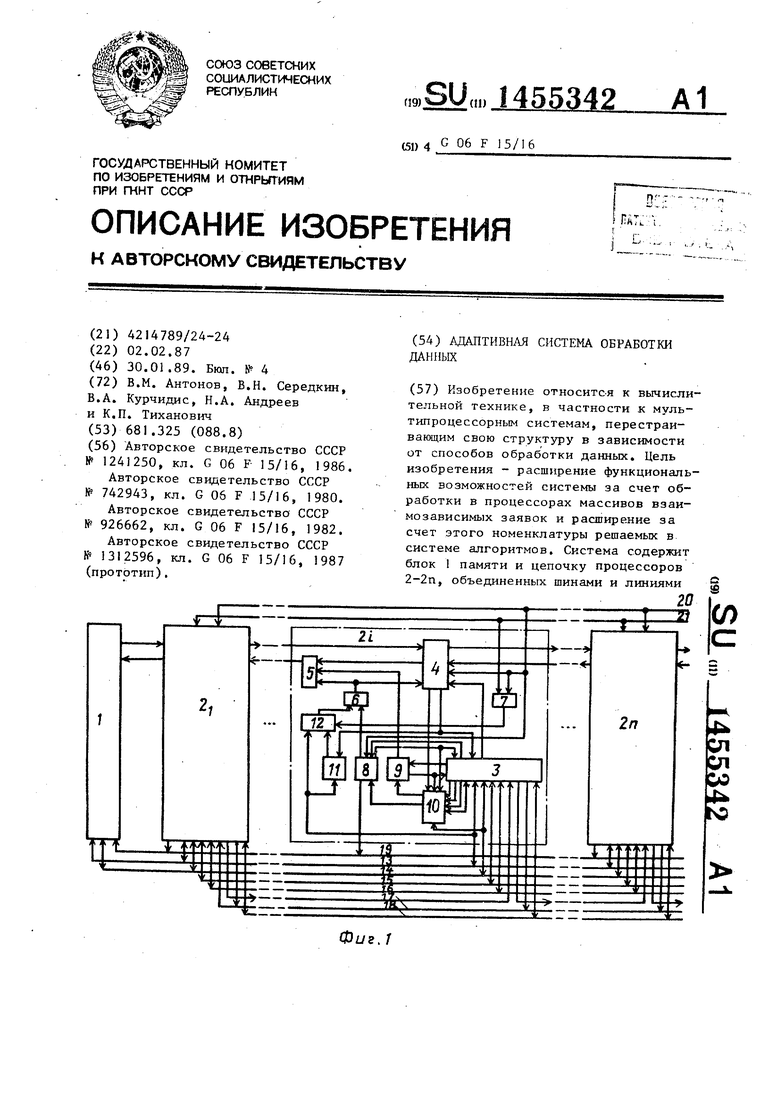

Изобретение относится к вычислительной технике, в частности к мультипроцессорным системам, перестраивающим свою структуру в зависимости от способов обработки данных. Цель изобретения - расширение функциональных возможностей системы за счет обработки в процессорах массивов взаимозависимых заявок и расширение за счет этого номенклатуры решаемых в системе алгоритмов. Система содержит блок 1 памяти и цепочку процессоров 2-2п, объединенных шинами и линиями 12 а б СП ел ел

1

Изобретение относится к вычиспи- I тельной технике, в частности к адаптивным мультипроцессорным системам, перёстраиванщим свою структуру в за- висимости от заданных способов обработки данных, и может быть применено в измерительно-вычислительных ком- плексах и в автоматизированных системах управления технологическими процессами, в системах автоматизации испытаний и контроля сложных объек- I тов и в других подобных системах, I Цель изобретения - раопирение i функциональных возможностей системы : за счет введения режима обработки массивов данных, т,е. обработки заявок по массивной технологии.

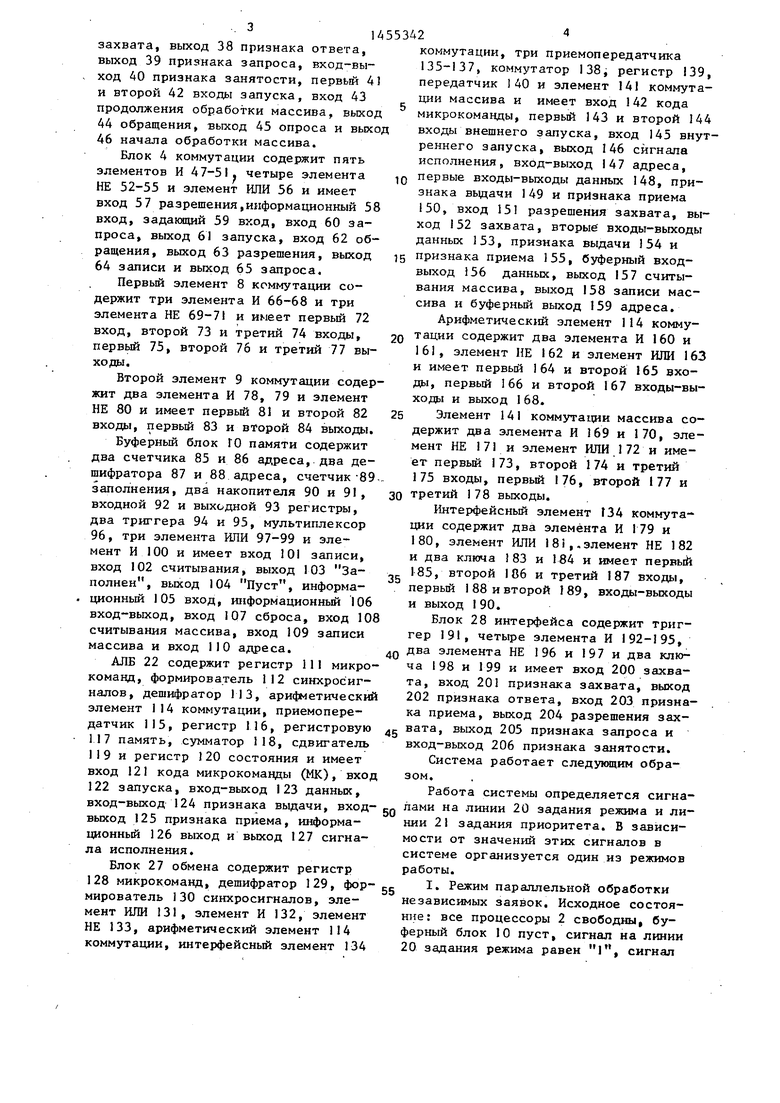

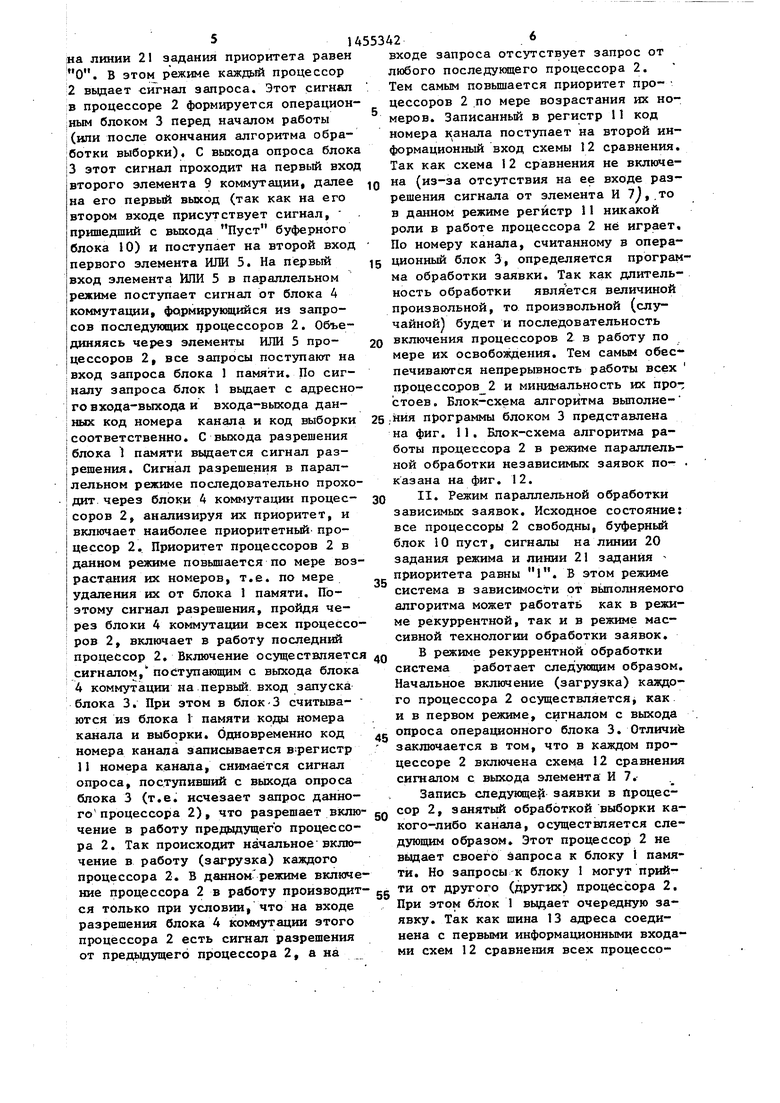

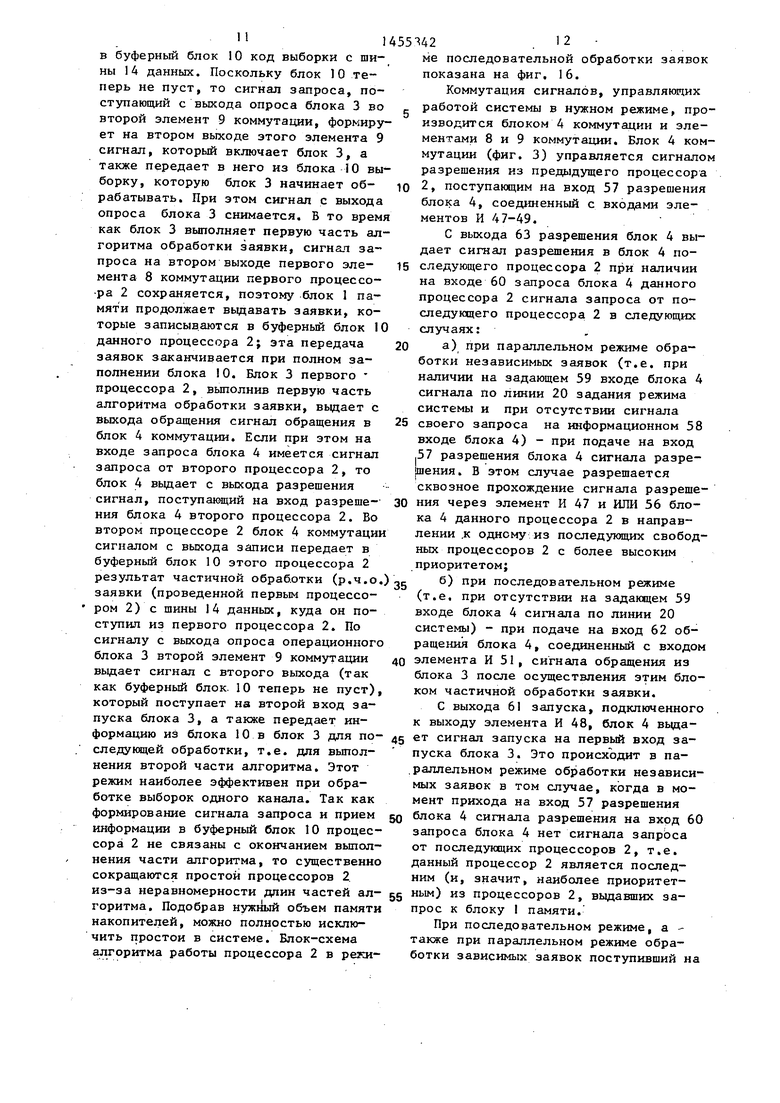

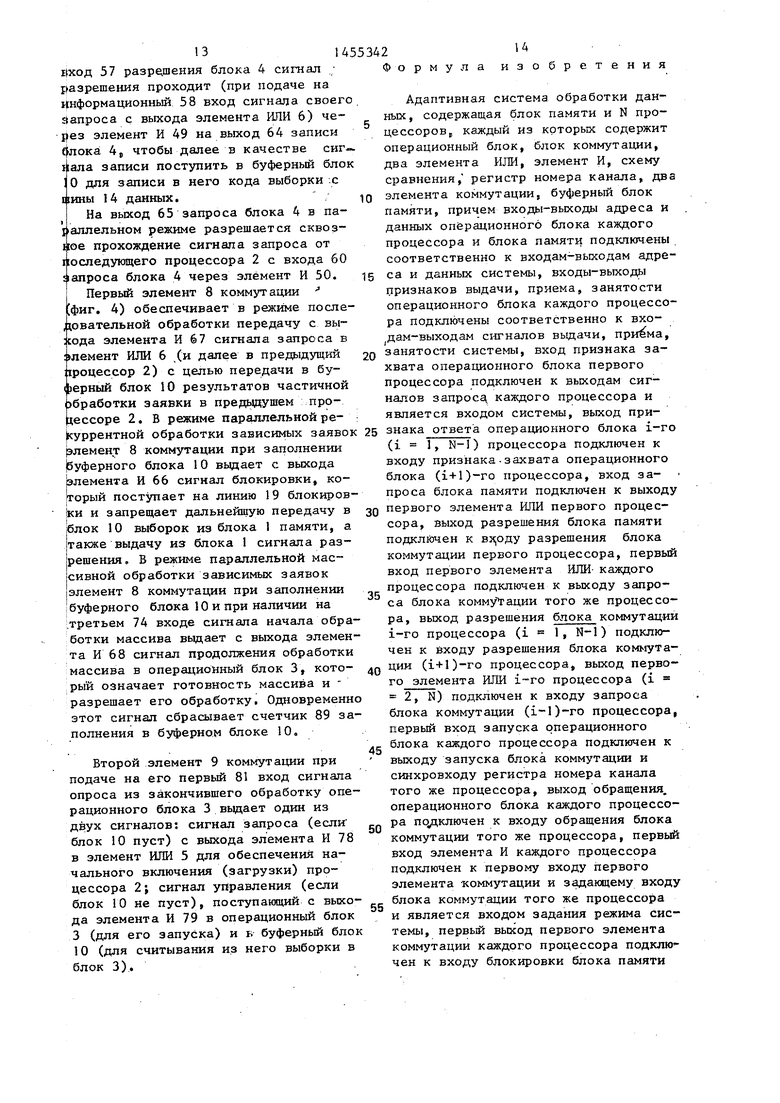

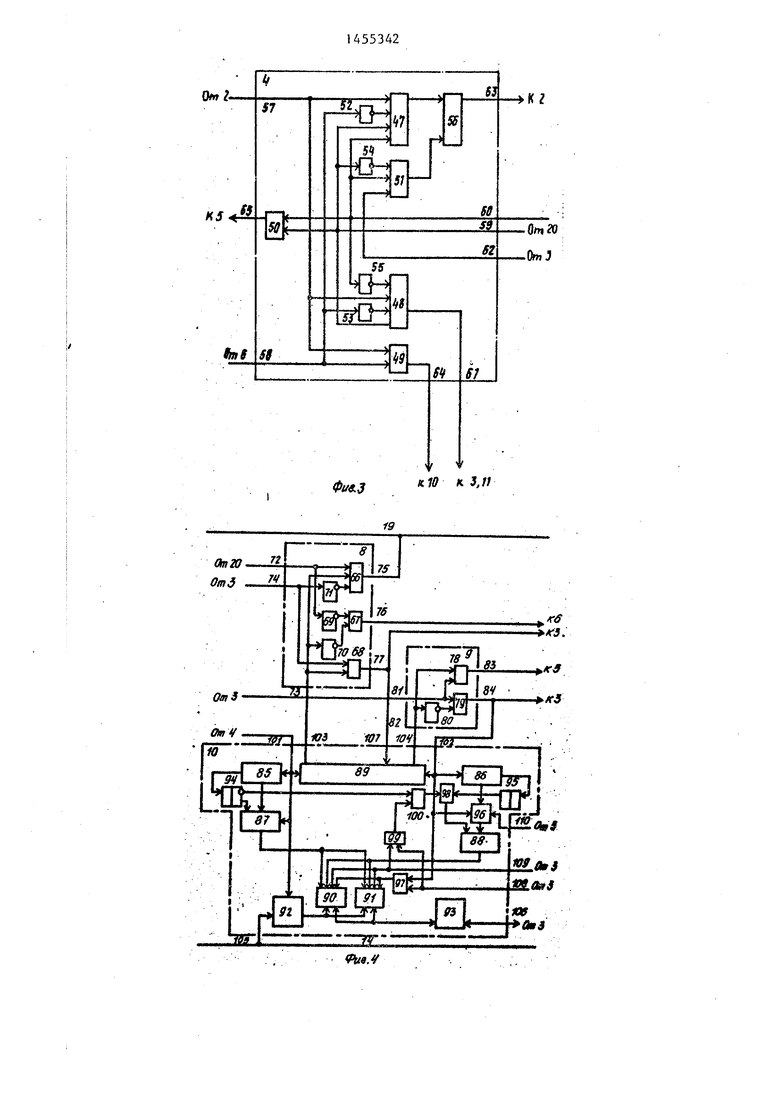

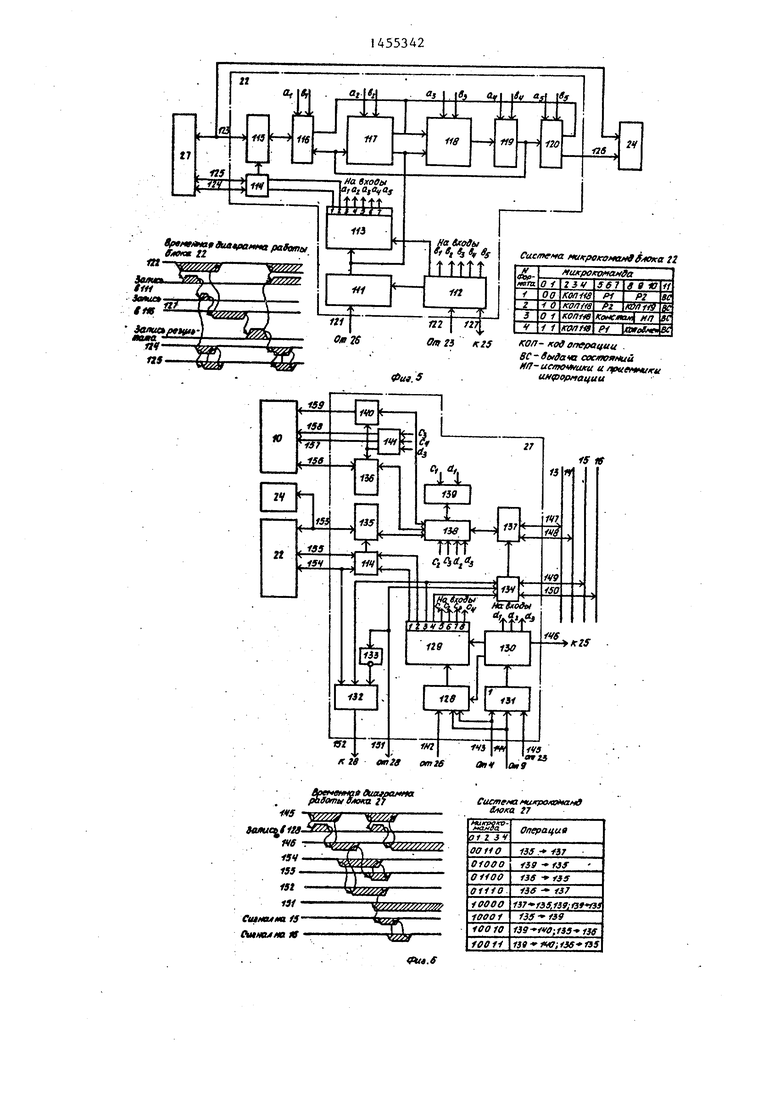

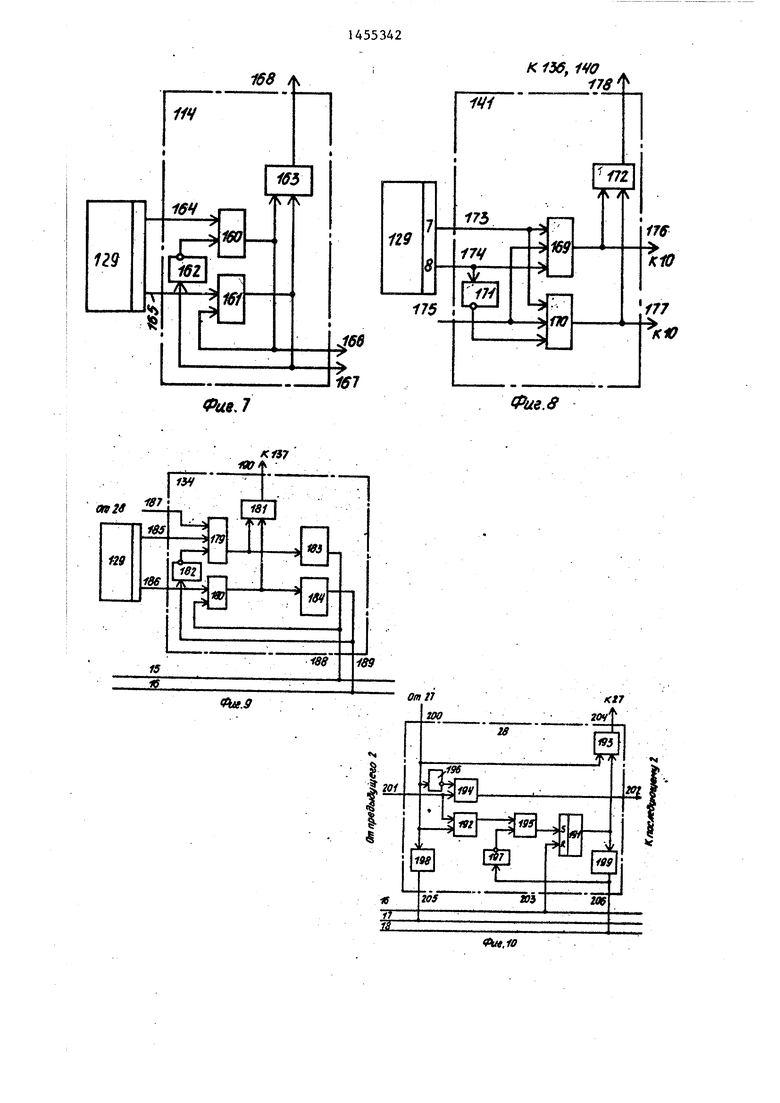

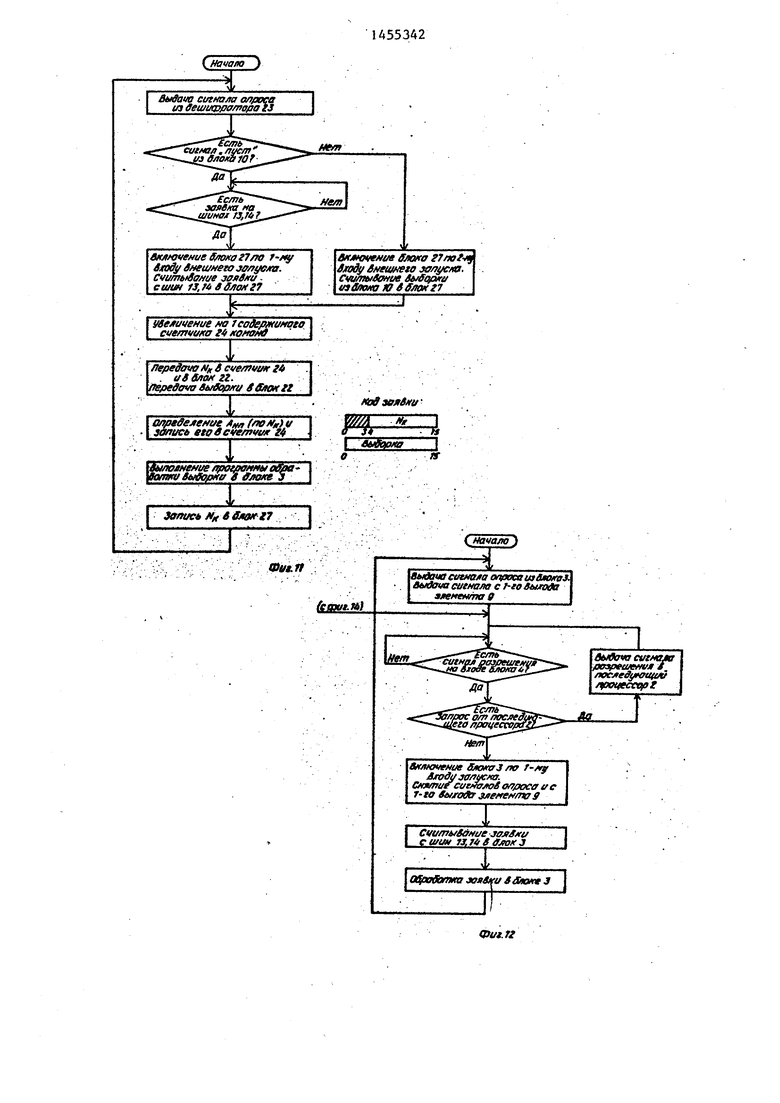

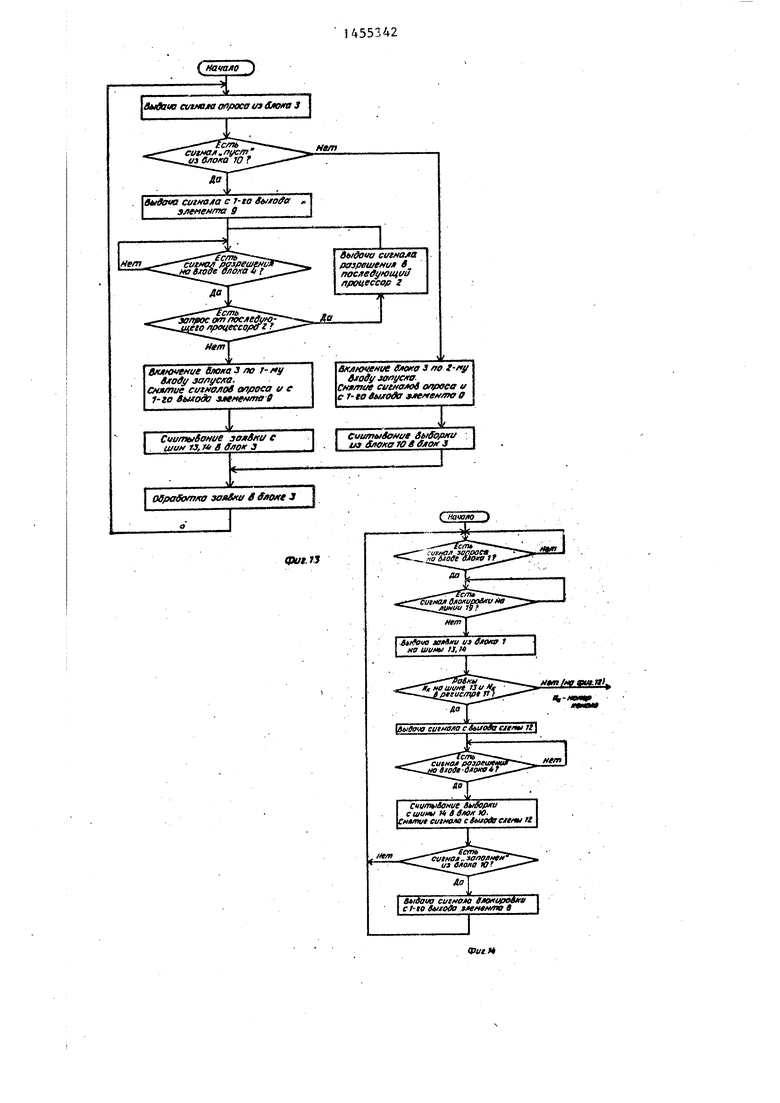

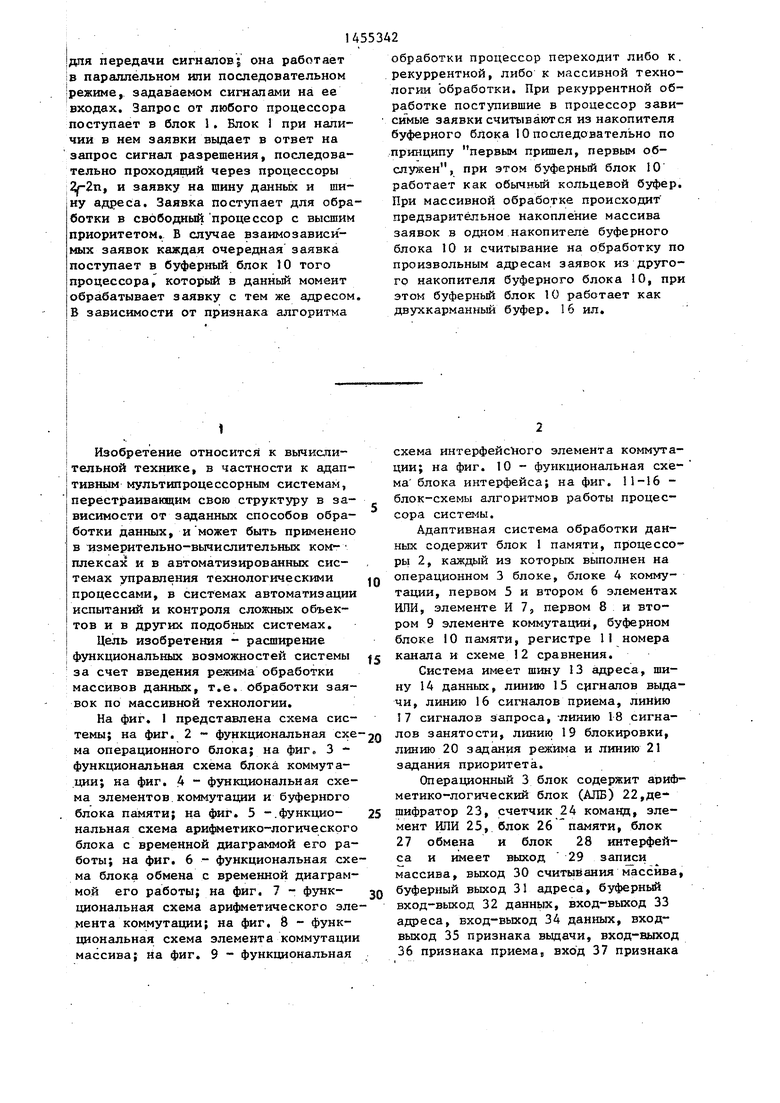

На фиг, 1 представлена схема системы; на фиг. 2 функциональная cxe ма операционного блока; на фиг. 3 - функциональная схема блока коммутации; на фиг. 4 - функциональная схема элементов.коммутации и буферного блока памяти; на фиг, 5 -.функцио- нальная схема арифметико-логического блока с временной диаграммой его работы; на фиг, 6 - функциональная схема блока обмена с временной диаграммой его работы; на фиг. 7 - функ- циональная схема арифметического элемента коммутации; на фиг. 8 - функциональная схема элемента коммутации массива; на фиг, 9 - функциональная

схема интерфейсного элемента коммутации; на фиг, 10 - функциональная схема блока интерфейса; на фиг. 11-16 - блок-схемы алгоритмов работы процессора системы.

Адаптивная система обработки данных содержит блок 1 памяти, процессо- ры 2, каждый из которых выполнен на операционном 3 блоке, блоке 4 коммутации, первом 5 и втором 6 элементах ИЛИ, элементе И 7, первом 8 и втором 9 элементе коммутации, буферном блоке 10 памяти, регистре 11 номера канала и схеме 12 сравнения.

Система имеет шину 13 адреса, шину 14 данных, линию 15 сигналов вьща- чи, линию 16 сигналов приема, линИю 17 сигналов запроса, -линию 18 сигналов занятости, линию 19 блокировки, линию 20 задания режима и линию 21 задания приоритета.

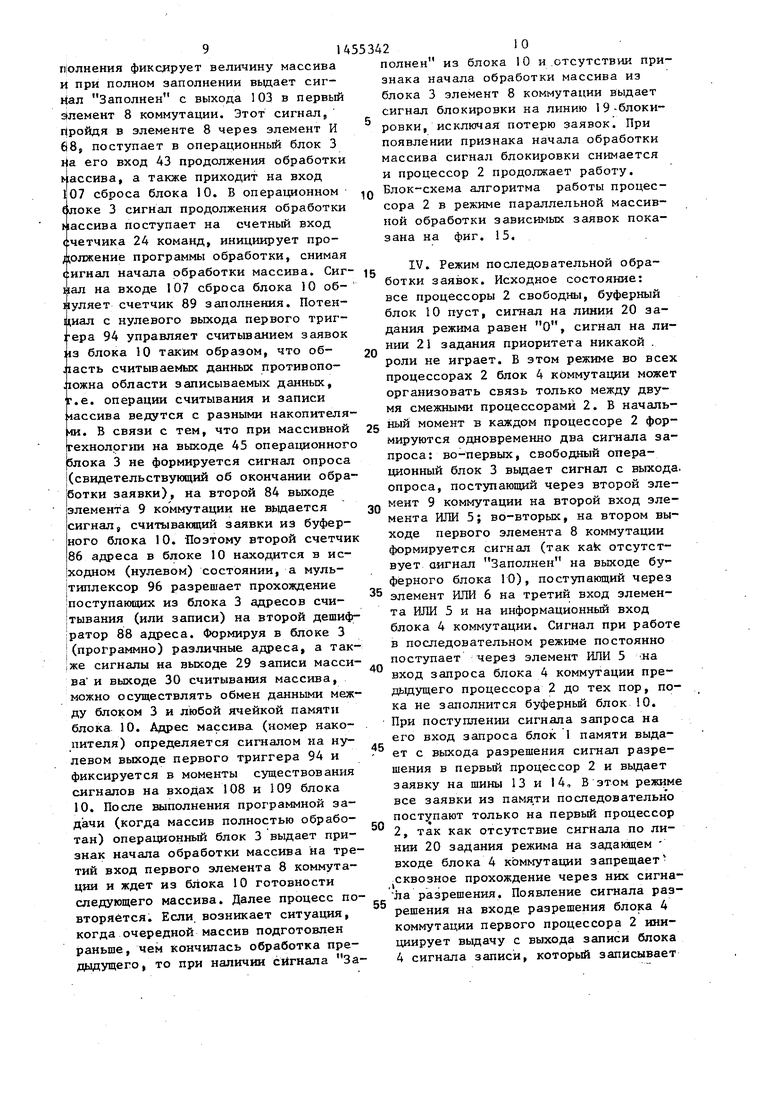

Операционный 3 блок содержит арифметико-логический блок (АЛБ) 22,дешифратор 23, счетчик 24 команд, элемент ИЛИ 25, блок 26 памяти, блок 27 обмена и блок 28 интерфейса и имеет выход 29 записи массива, выход 30 считывания массива, буферный выход 31 адреса, буферный вход-выход 32 данных, вход-выход 33 адреса, вход-выход 34 данных, вход- выход 35 признака выдачи, вход-выход 36 признака приема, вход 37 признака

захвата, выход 38 признака ответа, выход 39 признака запроса, вход-выход 40 признака занятости, первьй 4 и второй 42 входы запуска, вход 43 продолжения обработки массива, выхо 44 обращения, выход 45 опроса и вых 46 начала обработки массива.

Блок 4 коммутации содержит пять элементов И 47-51 четыре элемента НЕ 52-55 и элемент ИЛИ 56 и имеет вход 57 разрешения,информационный 58 вход, задающий 59 вход, вход 60 запроса, выход 61 запуска, вход 62 обращения, выход 63 разрешения, выход 64 записи и выход 65 запроса.

Первый элемент 8 коммутации содержит три элемента И 66-68 и три элемента НЕ 69-71 и имеет первый 72 вход, второй 73 и третий 74 входы, первый 75, второй 76 и третий 77 выходы.

Второй элемент 9 коммутации содержит два элемента И 78, 79 и элемент НЕ 80 и имеет первый 81 и второй 82 входы, первый 83 и второй 84 выходы.

Буферный блок ГО памяти содержит два счетчика 85 и 86 адреса,, два дешифратора 87 и 88 адреса, счетчик 89 заполнения, два накопителя 90 и 91, входной 92 и выходной 93 регистры, два триггера 94 и 95, мультиплексор 96, три элемента ИЛИ 97-99 и элемент И 100 и имеет вход 101 записи, вход 102 считывания, выход 103 Заполнен, выход 104 Пуст, информационный 105 вход, информационный 106 вход-выход, вход 107 сброса, вход 108 считывания массива, вход 109 записи массива и вход 110 адреса.

АЛБ 22 содержит регистр 11I микро- комавд, формирователь 112 синхросигналов, дешифратор 113, арифметический элемент 114 коммутации, приемопередатчик 115, регистр 116, регистровую 117 память, сумматор 118, сдвигатель 119 и регистр 120 состояния и имеет вход 121 кода микрокоманды (МК), вход 122 запуска, вход-выход 123 данных, вход-выход 124 признака выдачи, вход- выход 125 признака приема, информационный 126 выход и выход 127 сигнала исполнения.

Блок 27 обмена содержит регистр 128 микрокоманд, дешифратор 129, фор- мирователь 130 синхросигналов, элемент ИЛИ 131, элемент И 132, элемент НЕ 133, арифметический элемент 114 коммутации, интерфейсный элемент 134

1 д

455342

п

10

20

25

коммутации, три приемопередатчика 135-137, коммутатор 138, регистр 139, передатчик 140 и элемент 141 коммутации массива и имеет вход 142 кода микрокоманды, первый 143 и второй 144 входы внешнего запуска, вход 145 внутреннего запуска, выход 146 сигнала исполнения, вход-выход 147 адреса, первые входы-выходы данных 148, признака выдачи 149 и признака приема 150, вход 151 разрешения захвата, выход 152 захвата, вторые входы-выходы данных 153, признака выдачи 154 и 15 признака приема 155, буферный вход- выход 156 данных, выход 157 считывания массива, выход 158 записи массива и буферный выход 159 адреса.

Арифметический элемент 114 коммутации содержит два элемента И 160 и 161, элемент НЕ 162 и элемент ИЛИ 163 и имеет первый 164 и второй 165 входы, первый 166 и второй 167 входы-вы- хода и выход 168.

Элемент 141 коммутации массива содержит два элемента И 169 и 170, элемент НЕ 171 и элемент ИЛИ 172 и имеет первый 173, второй 174 и третий 175 входы, первый 176, второй 177 и третий 178 выходы.

Интерфейсный элемент Г34 коммутации содержит два элемента И I79 и 180, элемент ИЛИ 181,.элемент НЕ 182 и два ключа 183 и 184 и имеет первый g 185, второй 186 и третий 187 входы, первый 188 и второй 189, входы-выходы и выход I90.

Блок 28 интерфейса содержит триггер 191, четыре элемента И 192-195, два элемента НЕ 196 и 197 и два ключа 198 и 199 и имеет вход 200 захвата, вход 201 признака захвата, выход 202 признака ответа, вход 203 признака приема, выход 204 разрешения зах- 5 вата, выход 205 признака запроса и вход-выход 206 признака занятости.

Система работает следующим образом.

Работа системы определяется сигналами на линии 20 задания режима и линии 2 задания приоритета. В зависимости от значений этих сигналов в системе организуется один из режимов работы.

I. Режим параллельной обработки независимых заявок. Исходное состояние: все процессоры 2 свободны, буферный блок 10 пуст, сигнал на линии 20 задания режима равен 1, сигнал

0

0

1455342

(на линии 21 задания приоритета равен О. В этом режиме каждый процессор 2 выдает сигнал запроса. Этот сигнал в процессоре 2 формируется операцион- ;ным блоком 3 перед началом работы Кили после окончания алгоритма обра- ;ботки выборки), С выхода опроса блока 13 этот сигнал проходит на первый вход второго элемента 9 коммутации, далее на его первый выход (так как на его втором входе присутствует сигнал, пришедший с выхода Пуст буферного

30

блока 10) и поступает на второй вход I первого элемента ИЛИ 5. На первый 1вход элемента ИЛИ 5 в параллельном {режиме поступает сигнал от блока 4 коммутаиции, формирующийся из запросов последующих процессоров 2. Объединяясь через элементы ИЛИ 5 процессоров 2, все запросы поступают на I вход запроса блока 1 памяти. По сиг- налу запроса блок 1 выдает с адресно- I го входа-выхода и входа-выхода дан- Iных код номера канала и код выборки ;соответственно. С выхода разрешения блока } памяти выдается сигнал разрешения. Сигнал разрешения в параллельном режиме последовательно проходит через блоки 4 коммутации процессоров 2, анализируя их приоритет, и вклнзчает наиболее приоритетный процессор 2. Приоритет процессоров 2 в данном режиме повышается по мере возрастания их номеров, т.е. по мере удаления их от блока 1 памяти. Поэтому сигнал разрешения, пройдя через блоки 4 коммутации всех процессоров 2, включает в работу последний процессор 2. Включение осуществляется о сигналом, поступающим с выхода блока 4 коммутации на первый, вход запуска блока 3. При этом в блок - 3 считьша- ются из блока 1 памяти кода номера канала и выборки. Одновременно код номера канала записывается вфегистр 11 номера канала, снимается сигнал опроса, поступивший с выхода опроса блока 3 (т.е. исчезает запрос данного процессора 2), что разрешает включение в работу предыдущего процессора 2. Так происходит начальное включение в работу (загрузка) каждого

входе запроса отсутствует запрос от любого последукяцего процессора 2. Тем самым повышается приоритет про- цессоров 2 по мере возрастания их но меров. Записанный в регистр 11 код номера канала поступает на второй информационный вход схемы 12 сравнения. Так как схема 12 сравнения не включе п на (из-за отсутствия на ее входе разрешения сигнала от элемента И 7J,.To в данном режиме регистр 11 никакой роли в работе процессора 2 не играет. По номеру канала, считанному в опера 5 ционный блок 3, определяется программа обработки заявки. Так как длительность обработки является величиной произвольной, то произвольной (случайной) будет и последовательность

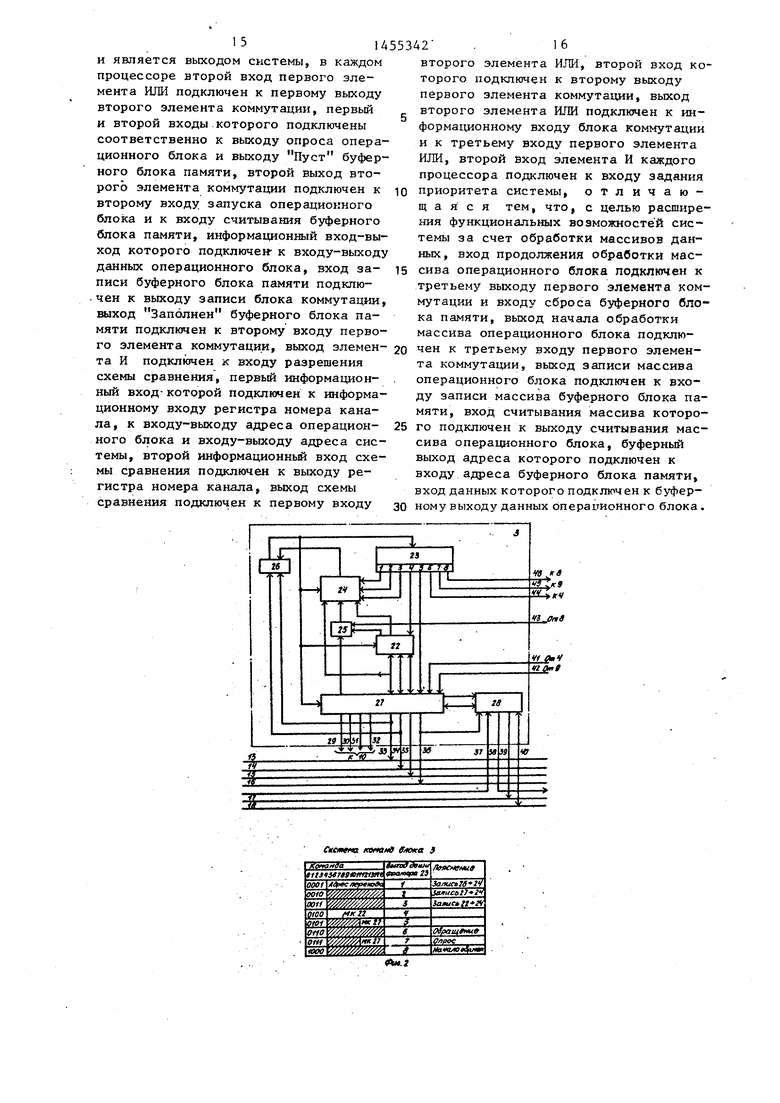

20 включения процессоров 2 в работу по мере их освобождения. Тем самым обеспечиваются непрерывность работы всех процессо)ов 2 и минимальность их простоев . Блок-схема алгоритма вьтолне25,ййя программы блоком 3 представлена на фиг. 11. Блок-схема алгоритма работы процессора 2 в режиме параллельной обработки независимых заявок по- к азана на фиг. 12.

II. Режим параллельной обработки зависимых заявок. Исходное состояние: все процессоры 2 свободны, буферный блок 10 пуст, сигналы на линии 20 задания режима и линии 21 задания приоритета равны 1. В этом режиме система в зависимости от выполняемого алгоритма может работать как в режиме рекуррентной, так и в режиме массивной технологии обработки заявок. В режиме рекуррентной обработки система работает следующим образом. Начальное включение (загрузка) каждого процессора 2 осуществляется, как и в первом режиме, сигналом с выхода опроса операционного блока 3. Отличие

35

45

50

заключается в том, что в каждом процессоре 2 включена схема 12 сравнения сигналом с выхода элемента И 7.

Запись следукяце|1 заявки в Процессор 2, занятый обработкой выборки какого-либо канала, осуществляется сле- дзпощим образом. Этот процессор 2 не выдает своего запроса к блоку 1 памяти. Но запросы к блоку 1 могут прийпроцессора 2. В данном режиме включе- - . - ние процессора 2 в работу производит- gg ти от другого (других) процессора 2. ся только при условии, что на входе При этом блок 1 выдает очередную за- разрешения блока 4 коммутации этого явку. Так как шина 13 адреса соеди- процессора 2 есть сигнал разрешения йена с первыми информационными входа- от предыдущего процессора 2, а на ми схем 12 сравнения всех процессо

30

о

входе запроса отсутствует запрос от любого последукяцего процессора 2. Тем самым повышается приоритет про- цессоров 2 по мере возрастания их номеров. Записанный в регистр 11 код номера канала поступает на второй информационный вход схемы 12 сравнения. Так как схема 12 сравнения не включеп на (из-за отсутствия на ее входе разрешения сигнала от элемента И 7J,.To в данном режиме регистр 11 никакой роли в работе процессора 2 не играет. По номеру канала, считанному в опера5 ционный блок 3, определяется программа обработки заявки. Так как длительность обработки является величиной произвольной, то произвольной (случайной) будет и последовательность

0 включения процессоров 2 в работу по мере их освобождения. Тем самым обеспечиваются непрерывность работы всех процессо)ов 2 и минимальность их простоев . Блок-схема алгоритма вьтолне5,ййя программы блоком 3 представлена на фиг. 11. Блок-схема алгоритма работы процессора 2 в режиме параллельной обработки независимых заявок по- к азана на фиг. 12.

II. Режим параллельной обработки зависимых заявок. Исходное состояние: все процессоры 2 свободны, буферный блок 10 пуст, сигналы на линии 20 задания режима и линии 21 задания приоритета равны 1. В этом режиме система в зависимости от выполняемого алгоритма может работать как в режиме рекуррентной, так и в режиме массивной технологии обработки заявок. В режиме рекуррентной обработки система работает следующим образом. Начальное включение (загрузка) каждого процессора 2 осуществляется, как и в первом режиме, сигналом с выхода опроса операционного блока 3. Отличие

35

45

50

заключается в том, что в каждом процессоре 2 включена схема 12 сравнения сигналом с выхода элемента И 7.

Запись следукяце|1 заявки в Процессор 2, занятый обработкой выборки какого-либо канала, осуществляется сле- дзпощим образом. Этот процессор 2 не выдает своего запроса к блоку 1 памяти. Но запросы к блоку 1 могут прий- . - gg ти от другого (других) процессора 2. При этом блок 1 выдает очередную за- явку. Так как шина 13 адреса соеди- йена с первыми информационными входа- ми схем 12 сравнения всех процессоров 2, то в каждом процессоре 2 вы10

1455342 8

ма обработки предыдущей заяки блок выдает сигнал опроса во второй элемент 9 коммутации. Так как сигнал Пуст теперь отсутствует (в блоке находится выборка), то второй элеме 9 коммутации выдает сигнал, поступа щий на второй ,вход запуска блока 3 для запуска блока 3 и на вход считывания буферного блока 10. При этом выборка передается с информационного выхода блока 10 в блок 3 для обработ ки. В буферном блоке 10 может находиться одновременно до 64 К выборок одного канала. Считывание их из бло ка 10 осуществляется последовательно в порядке их поступления. При полном заполнении блока 10 выдается сигнал с выхода Заполнен. Этот сигнал про ходит через первой элемент 8 коммута ции и поступает с его первого выхода в виде сигнала блокировки на линию 19 блокировки, объединяющую выходы блокировок от всех процессоров 2. По

15

данный на шину 13 адрес кода номера канала сравнивается с кодом номера канала, записанным в регистр 11 номера канала при включении процессора 2 в работу. Если эти коды в данном процессоре 2 совпали (это значит, что поступила выборка этого же канала, который обрабатывается в этом процес- соре 2), то схема 12 сравнения со своего выхода выдает сигнал, который через элемент ИЛИ 6 поступает в элемент ИЛИ 5 и на информационный вход блока 4 коммутации, являясь соответственно сигналом своего запроса от .данного процессора 2 г блоку 1 памяти и признаком режима параллельной обработки зависимых заявок, блокирующим сквозное прохождение через блок 4 сигнала разрешения. Таким образом, этот сигнал превращает данный процессор 2 в процессор с наивысшим приоритетом. Сигнал с выхода разрешения блока 1 памяти (он вьщается с не- 25 явление сигнала блокировки на входе

гг : гГка°оГпТ:г°вГ - -- ™

предыдущие процессоры 2, поступает на вход разрешения блока

20

35

40

4 коммутации

даиного процессора 2 и инициирует зо появление на выходе запис блока 4 сигнала записи, поступающего на вход записи буферного блока 10. Этот сигнал осуществляет запись в блок 10 кода выборки с шины 14 данных. По окончании передачи заявки, по шине I3 адреса и шине 14 данных сигнал на вы- ходе схемы 12 сравнения снимается. Таким образом, в системе осуществляется фиксированное распределение зависимых заявок по процессорам 2, тем самым обеспечивается строгая последовательность обработки выборок одного канала. В системе нет строгой привязки номеров каналов к конкретным процессорам 2, т.е. фиксация распределения заявок существует только при появлении фактора опережения. Во всех остальных случаях распределение остается достаточно произвольным, так как учитывается только приоритетность процессоров 2 (как и в первом режиме). Это значительно повышает живучесть системы и сокращает время и- затраты на оборудование на организацию распределения заявок.

После записи кода выборки в буфер- ньй блок 10 процессор 2 работает следующим образом. По окончании алгорит45

50

считывание заявок из блока I, исключая возможность появления фактора опережения в системе при заполнении буферного блока 10 какого-либо процессора 2. Блок-схема алгоритма работы процессора 2 в режиме параллельной, рекуррентной обработки зависимых заявок показана на фиг. 13; блок- схема алгоритма записи заявки в процессор 2 в этом режиме представлена на фиг. 14.

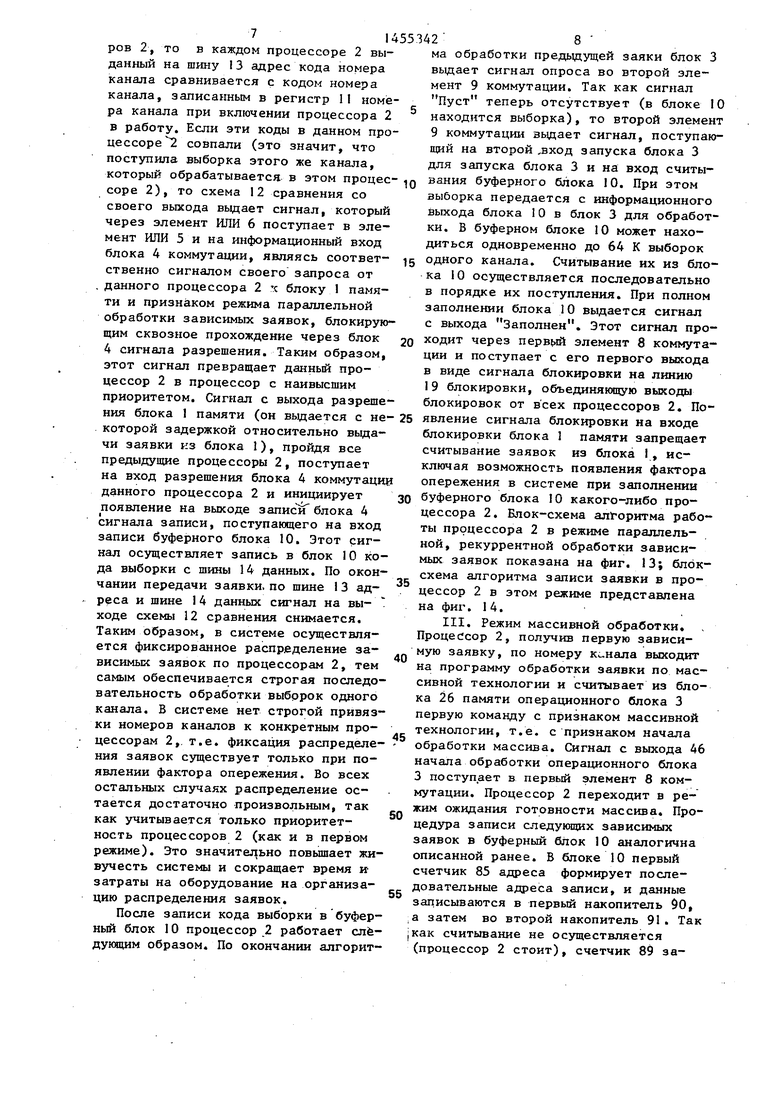

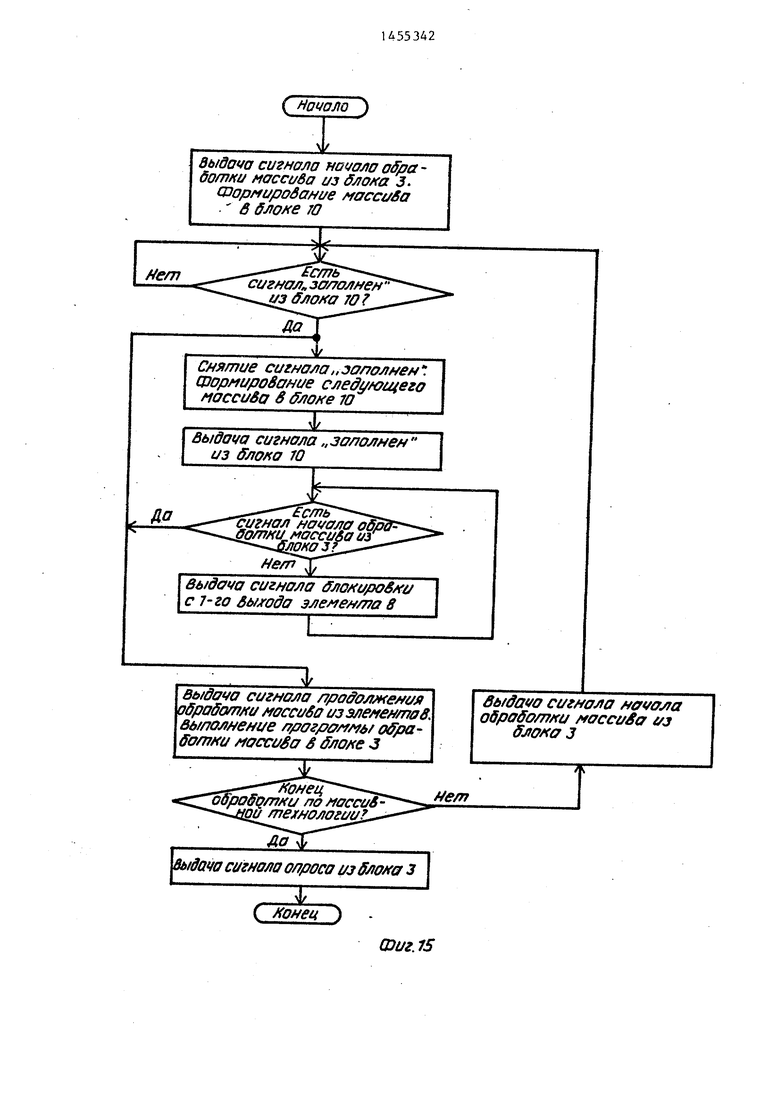

III. Режим массивной обработки. Процессор 2, получив первую зависимую заявку, по номеру KL.Hала выходит на программу обработки заявки по массивной технологии и считывает из блока 26 памяти операционного блока 3 первую команду с признаком массивной технологии, т.е. с признаком начала обработки массива. Сигнал с выхода 46 начала обработки операционного блока 3 поступает в первый элемент 8 коммутации. Процессор 2 переходит в режим ожидания готовности массива. Процедура записи следующих зависимых заявок в буферный блок 10 аналогична описанной ранее. В блоке 10 первый счетчик 85 адреса формирует последовательные адреса записи, и данные записываются в первый накопитель 90, а затем во второй накопитель 91. Так как считывание не осуществляется (процессор 2 стоит), счетчик 89 за10

55342 8

ма обработки предыдущей заяки блок 3 выдает сигнал опроса во второй элемент 9 коммутации. Так как сигнал Пуст теперь отсутствует (в блоке 10 находится выборка), то второй элемент 9 коммутации выдает сигнал, поступающий на второй ,вход запуска блока 3 для запуска блока 3 и на вход считывания буферного блока 10. При этом выборка передается с информационного выхода блока 10 в блок 3 для обработки. В буферном блоке 10 может находиться одновременно до 64 К выборок одного канала. Считывание их из блока 10 осуществляется последовательно в порядке их поступления. При полном заполнении блока 10 выдается сигнал с выхода Заполнен. Этот сигнал проходит через первой элемент 8 коммутации и поступает с его первого выхода в виде сигнала блокировки на линию 19 блокировки, объединяющую выходы блокировок от всех процессоров 2. По15

25 явление сигнала блокировки на входе

20

-- ™

35

40

зо

45

0

считывание заявок из блока I, исключая возможность появления фактора опережения в системе при заполнении буферного блока 10 какого-либо процессора 2. Блок-схема алгоритма работы процессора 2 в режиме параллельной, рекуррентной обработки зависимых заявок показана на фиг. 13; блок- схема алгоритма записи заявки в процессор 2 в этом режиме представлена на фиг. 14.

III. Режим массивной обработки. Процессор 2, получив первую зависимую заявку, по номеру KL.Hала выходит на программу обработки заявки по массивной технологии и считывает из блока 26 памяти операционного блока 3 первую команду с признаком массивной технологии, т.е. с признаком начала обработки массива. Сигнал с выхода 46 начала обработки операционного блока 3 поступает в первый элемент 8 коммутации. Процессор 2 переходит в режим ожидания готовности массива. Процедура записи следующих зависимых заявок в буферный блок 10 аналогична описанной ранее. В блоке 10 первый счетчик 85 адреса формирует последовательные адреса записи, и данные записываются в первый накопитель 90, а затем во второй накопитель 91. Так как считывание не осуществляется (процессор 2 стоит), счетчик 89 за1455342

111олнения фиксирует величину массива И при полном заполнении выдает сиг- Нал Заполнен с выхода 103 в первый элемент 8 коммутации. Этот сигнал, йройдя в элементе 8 через элемент И 68, поступает в операционный блок 3 На его вход 43 продолжения обработки ьассива, а также приходит на вход 107 сброса блока 10. В операционном елоке 3 сигнал продолжения обработки массива поступает на счетный вход (;четчика 24 команд, инициирует продолжение программы обработки, снимая сигнал начала обработки массива. Сиг- нал на входе 107 сброса блока 10 обнуляет счетчик 89 заполнения. Потенциал с нулевого выхода первого триг- ера 94 управляет считьшанием заявок 113 блока 10 таким образом, что об- ласть считываемых данных противоположна области записываемых данных, т.е. операции считывания и записи массива ведутся с разными накопителя- ии. В связи с тем, что при массивной технологии на выходе 45 операционного {блока 3 не формируется сигнал опроса Ксвидетельствукнций об окончании обра- |ботки заявки), на второй 84 выходе |элемента 9 коммутации не выдается сигнал, считывакяций заявки из буферного блока 10. Поэтому второй счетчик 86 адреса в блоке 10 находится в ис- |ходном (нулевом) состоянии, а мультиплексор 96 разрешает прохождение поступающих из блока 3 адресов счи- тывания (или записи) на второй дешиф- |ратор 818 адреса. Формируя в блоке 3 I (программно) различные адреса, а так же сигналы на выходе 29 записи масси ва и выходе 30 считывания массива, можно осуществлять обмен данными между блоком 3 и любой ячейкой памяти блока 10. Адрес массива (номер накопителя) определяется сигналом на ну- левом выходе первого триггера 94 и фиксируется в моменты существования сигналов на входах 108 и 109 блока 10. После выполнения программной задачи (когда массив полностью обрабо- тан) операционный блок 3 вьщает признак начала обработки массива на третий вход первого элемента 8 коммутации и ждет из блока 10 готовности следующего массива. Далее процесс по вторяётся. Если, возникает ситуация, когда очередной массив подготовлен раньше, чем кончилась обработка предыдущего, то при наличии сигнала

За10

5 0 25 ЗО g

полнен из блока 10 и .отсутствии признака начала обработки массива из блока 3 элемент 8 коммутации выдает сигнал блокировки на линию 19-блокировки, исключая потерю заявок. При появлении признака начала обработки массива сигнал блокировки снимается и процессор 2 продолжает работу.

f. Блок-схема алгоритма работы процессора 2 в режиме параллельной массивной обработки зависимых заявок показана на фиг. 15.

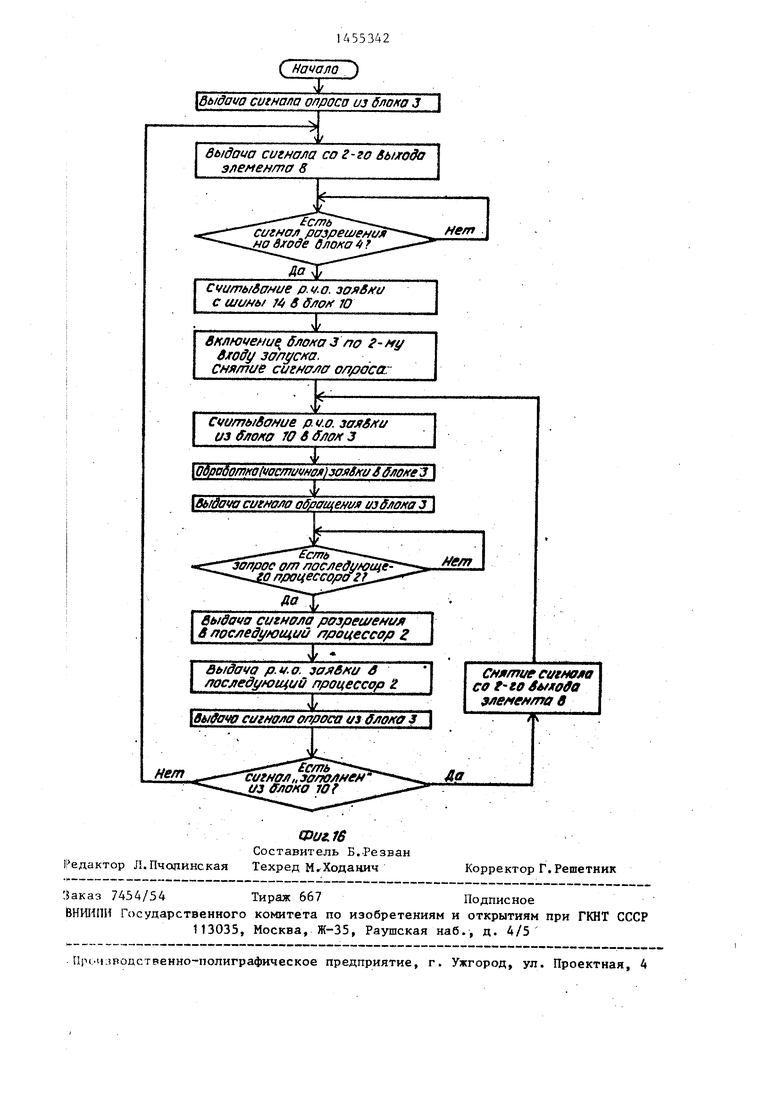

IV. Режим последовательной обработки заявок. Исходное состояние: все процессоры 2 свободны, буферный блок 10 пуст, сигнал на линии 20 задания режима равен О, сигнал на линии 21 задания приоритета никакой . роли не играет. В этом режиме во всех процессорах 2 блок 4 коммутации может организовать связь только между двумя смежными процессорами 2. В начальный момент в каждом процессоре 2 формируются одновременно два сигнала запроса: во-первых, свободный операционный блок 3 выдает сигнал с выхода опроса, поступающий через второй элемент 9 коммутации на второй вход элемента ИЛИ 5; во-вторых, на втором выходе первого элемента 8 коммутации формируется сигнал (так Kak отсутствует сигнал Заполнен на выходе буферного блока 10), поступающий через элемент ИЛИ 6 на третий вход элемента ИЛИ 5 и на информационный вход блока 4 коммутации. Сигнал при работе в последовательном режиме постоянно поступает череЭ элемент ИЛИ 5 :на вход запроса блока 4 коммутации пре- дьщущего процессора 2 до тех пор, пока не заполнится буферный блок 10. При поступлении сигнала запроса на его вход запроса блок 1 памяти выдает с выхода разрешения сигнал разрешения в первый процессор 2 и выдает заявку на щины 13 и 14, В этом реж11ме все заявки из памяти последовательн о поступают только на первый процессор 2, так как отсутствие сигнала по линии 20 задания режима на задаклцем входе блока 4 коммутации запрещает сквозное прохождение через них сигна - ла разрешения. Появление сигнала разрешения на входе разрешения блока 4 коммутации первого процессора 2 инициирует вьщачу с выхода записи блока 4 сигнала записи, который записывает

1455 42. 12

в буферный блок 10 код выборки с ши-ме последовательной обработки заявок

ны 14 данных. Поскольку блок 10 теперь не пуст, то сигнал запроса, поступающий с выхода опроса блока 3 во

,

изводится блоком 4 коммутации и элементами 8 и 9 коммутации. Блок 4 коммутации (фиг. 3) управляется сигналом разрешения из предыдущего процессора 10 2, поступающим на вход 57 разрешения

второй элемент 9 коммутации, формирует на втором выходе этого элемента 9 сигнал, который включает блок 3, а также передает в него из блока 10 выборку, которую блок 3 начинает обпоказана на фиг, 16.

Коммутация сигналов, управляющих g работой системы в нужном режиме, прорабатывать. При этом сигнал с выхода опроса блока 3 снимается. В то время как блок 3 выполняет первую часть алгоритма обработки заявки, сигнал запроса на втором выходе первого элемента 8 коммутации первого процессора 2 сохраняется, поэтому блок 1 па- мят и продолжает вьщавать заявки, которые записываются в буферньй блок 10 данного процессора 2; эта передача заявок заканчивается при полном заполнении блока 10. Блок 3 первого процессора 2, выполнив первую часть алгоритма обработки заявки, вьщает с выхода обращения сигнал обращения в блок 4 коммутации. Если при этом на входе запроса блока 4 имеется сигнал запроса от второго процессора 2, то блок 4 вьщает с вькода разрешения

блока 4, соединенный с входами элементов И 47-49.

С выхода 63 разрешения блок 4 выдает сигнал разрешения в блок 4 по15 следующего процессора 2 при наличии на входе 60 запроса блока 4 данного процессора 2 сигнала запроса от последующего процессора 2 в следующих случаях:

20 а) при параллельном режиме обработки независимых заявок (т.е. при наличии на задающем 59 входе блока 4 сигнала по линии 20 задания режима системы и при отсутствии сигнала

25 своего запроса на информационном 58 входе блока 4) - при подаче на вход ,57 разрешения блока 4 сигнала разре шения. В этом случае разрешается сквозное прохождение сигнала разреше- сигнал, поступакщий на вход разреще- ЗО ния через элемент И 47 и ИЛИ 56 бло- ния блока 4 второго процессора 2. Во ка 4 данного процессора 2 в направлении .к одному из последующих свободных процессоров 2 с более высоким

приоритетом;

втором процессоре 2 блок 4 коммутации сигналом с выхода записи передает в буферный блок 10 этого процессора 2 результат частичной обработки (р.ч.о.) б) при последовательном режиме заявки (проведенной первым процессо- (т.е. при отсутствии на задающем 59 ром 2) с щины 14 данных, куда он поступил из первого процессора 2. По сигналу с выхода опроса операционного блока 3 второй элемент 9 коммутации выдает сигнал с второго выхода (так

как буферный блок. 10 теперь не пуст), который поступает на второй вход запуска блока 3, а также передает инвходе блока 4 сигнала по линии 20 системы) - при подаче на вход 62 обращения блока 4, соединенный с входом 40 элемента И 51, сигнала обращения из блока 3 после осуществления этим блоком частичной обработки заявки.

С выхода 61 запуска, подключенного к выходу элемента И 48, блок 4 вьщаформацию из блока 10 в блок 3 для по- 45 ет сигнал запуска на первый вход заел едукндей обработки, т.е. для вьтол- нения второй части алгоритма. Этот режим наиболее эффективен при обработке выборок одного канала. Так как формирование сигнала запроса и прием информации в буферный блок 10 процессора 2 не связаны с окончанием выполнения части алгоритма, то существенно сокращаются простой процессоров 2

пуска блока 3. Это происходит в па- .раллельиом режиме обработки независимых заявок в том случае, когда в момент прихода на вход 57 разрешения 50 блока 4 сигнала разрешения на вход 60 запроса блока 4 нет сигнала запроса от последующих процессоров 2, т.е. данный процессор 2 является последним (и, значит, наиболее приоритет- 4--j --- w- iA IILIWUL/WI С 1

из-за неравномерности длин частей ал- 55 Ь1м) из процессоров 2, выдавших за- горитма. Подобрав нужный объем памяти прос к блоку I памяти. накопителей, можно полностью исклю- При последовательном режиме, а - чить простои в системе. Блок-схема также при параллельном режиме обра- алгоритма работы процессора 2 в реки- ботки зависимых заявок поступивший на

ме последовательной обработки заявок

,

изводится блоком 4 коммутации и элементами 8 и 9 коммутации. Блок 4 коммутации (фиг. 3) управляется сигналом разрешения из предыдущего процессора 2, поступающим на вход 57 разрешения

показана на фиг, 16.

Коммутация сигналов, управляющих работой системы в нужном режиме, производится блоком 4 коммутации и элементами 8 и 9 коммутации. Блок 4 коммутации (фиг. 3) управляется сигналом разрешения из предыдущего процессора 2, поступающим на вход 57 разрешения

блока 4, соединенный с входами элементов И 47-49.

С выхода 63 разрешения блок 4 выдает сигнал разрешения в блок 4 последующего процессора 2 при наличии на входе 60 запроса блока 4 данного процессора 2 сигнала запроса от последующего процессора 2 в следующих случаях:

а) при параллельном режиме обработки независимых заявок (т.е. при наличии на задающем 59 входе блока 4 сигнала по линии 20 задания режима системы и при отсутствии сигнала

своего запроса на информационном 58 входе блока 4) - при подаче на вход 57 разрешения блока 4 сигнала разрешения. В этом случае разрешается сквозное прохождение сигнала разреше- ния через элемент И 47 и ИЛИ 56 бло- ка 4 данного процессора 2 в направении .к одному из последующих свободных процессоров 2 с более высоким

приоритетом;

б) при пос (т.е. при отс

б) при последовательном режиме (т.е. при отсутствии на задающем 59

входе блока 4 сигнала по линии 20 системы) - при подаче на вход 62 обращения блока 4, соединенный с входом 40 элемента И 51, сигнала обращения из блока 3 после осуществления этим блоком частичной обработки заявки.

С выхода 61 запуска, подключенного к выходу элемента И 48, блок 4 вьща45 ет сигнал запуска на первый вход запуска блока 3. Это происходит в па- .раллельиом режиме обработки независимых заявок в том случае, когда в момент прихода на вход 57 разрешения 0 блока 4 сигнала разрешения на вход 60 запроса блока 4 нет сигнала запроса от последующих процессоров 2, т.е. данный процессор 2 является последним (и, значит, наиболее приоритет 4--j --- w- iA IILIWUL/WI С 1

5 Ь1м) из процессоров 2, выдавших за- прос к блоку I памяти. При последовательном режиме, а - также при параллельном режиме обра- ботки зависимых заявок поступивший на

131455342

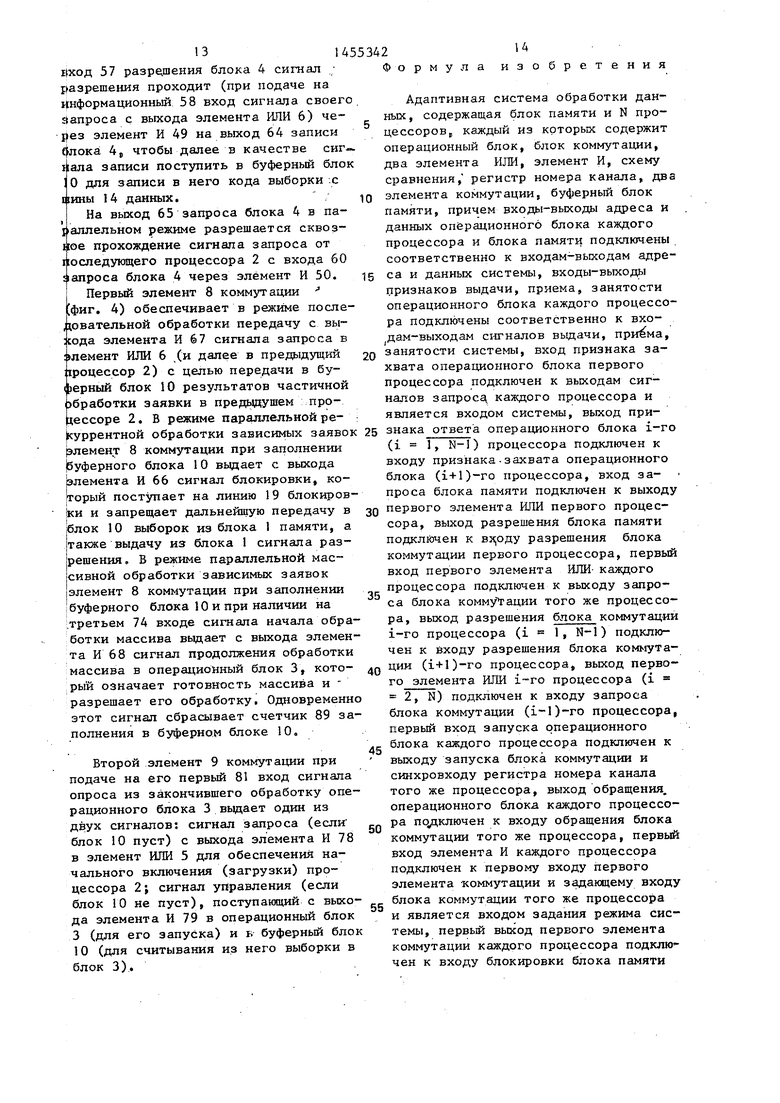

йход 57 разре шения блока 4 сигаал ;Формула изобретения разрешения проходит (при подаче на

«нформационный 58 вход сигнала своего.Адаптивная система обработки дан- Запроса с выхода элемента ИЛИ 6) че-ных, содержащая блок памяти и N прорез элемент И 49 на выход 64 записи дессоров каждый из которых содержит 4лока 4j чтобы далее в качестве сиг-операционный блок, блок коммутации, ikana записи поступить в буферный блокдва элемента ИЛИ, элемент И, схему 10 для записи в него кода выборки .ссравнения, регистр номера канала, два пины 14 данных. / Юэлемента коммутации, буферный блок Т На выход 65 запроса блока 4 в па-памяти, причем входь -выходы адреса и .аллельном режиме разрешается сквоз-данных операционного блока каждого 08 прохождение сигнала запроса отпроцессора и блока памяти подключены юследующего процессора 2 с входа 60соответственно к входам-выходам адре- апроса блока 4 через элемент И 50. 15са и данных системы, входы-выходы

Первый элемент 8 коммутации признаков выдачи, приема, занятости :фиг. 4) обеспечивает в режиме после-операционного блока каждого процессо- J oвaтeльнoй обработки передачу с вы-ра подключены соответственно к вхо- чода элемента И 67 сигнала запроса в дам-выходам сигналов выдачи, приема, Элемент ИЛИ 6 (и далее в предыдущий 20занятости системы, вход признака за- ироцессор 2) с целью передачи в бу-хвата операционного блока первого верный блок 10 результатов частичнойпроцессора подключен к выходам сиг- обработки заявки в предыдущем про-налов запросу каждого процессора и рессоре 2. В режиме параллельной ре- :является входом системы, вькод при- йуррентной обработки зависимых заявок 25знака ответа операционного блока 1-го элемент 8 коммутации при заполнении(i 1, N-1) процессора подключен к буферного блока 10 выдает с выходавходу признака-захвата операционного Элемента И 66 сигнал блокировки, ко-блока (i+l)-ro процессора, вход за- k-орый поступает на линию 19 блокиров-проса блока памяти подключен к выходу ки и запрещает дальнейшую передачу в ЗОпервого элемента ИЛИ первого процес- Ьлок 10 выборок из блока I памяти, асора, выход разрешения блока памяти |также выдачу из блока 1 сигнала раз-подключен к вх,оду разрешения блока 1решения. В режиме параллельной мае-коммутации первого процессора, первый |сивной обработки зависимых заявоквход первого элемента ИЛИ- каждого элемент 8 коммутации при заполнении „процессора подключен к выходу запро- буферного блока 10 и при наличии на са блока коммутации того же процессо- третьем 74 входе сигнала начала обра-ра, выход разрешения блока коммутации ботки массива выдает с выхода элемен-i-ro процессора (i 1, N-1) подклю- та И 68 сигнал продолжения обработкичей к йходу разрешения блока коммута- массива в операционный блок 3, кото- 40 (i+l)-ro процессора, выход перво- рый означает готовность массива и -го элемента ИЛИ процессора (i разрешает его обработку. Одновременно 2, N) подключен к входу запроса этот сигнал сбрасывает счетчик 89 за-блока коммутации (i-l)-ro процессора, полнения в буферном блоке 10.первый вход запуска операционного

... блока каждого процессора подключен к 45

Второй элемент 9 коммутации при выходу запуска блока коммутации и

подаче на его первый 81 вход сигналасинхровходу регистра номера канала

опроса из закончившего обработку one-того же процессора, выход обращения,

рационного блока 3 вьщает один изоперационного блока каждого процессо- двух сигналов: сигнал запроса (если g ра подключен к входу обращения блока

блок 10 пуст) с выхода элемента И 78коммутации того же процессора, первый

в элемент ИЛИ 5 для обеспечения на-вход элемента И каждого процессора

чального включения (загрузки) про-подключен к первому входу первого

цессора 2; сигнал управления (еслиэлемента коммутации и задающему входу

блок 10 не пуст), поступающий с выхо-блока коммутации того же процессора

да элемента И 79 в операционный блоки является входом задания режима сис3 (для его запуска) и к буферный блоктемы, первьй выход первого элемента

10 (для считывания из него выборки вкоммутации каждого процессора подклюблок 3) входу блокировки блока памяти

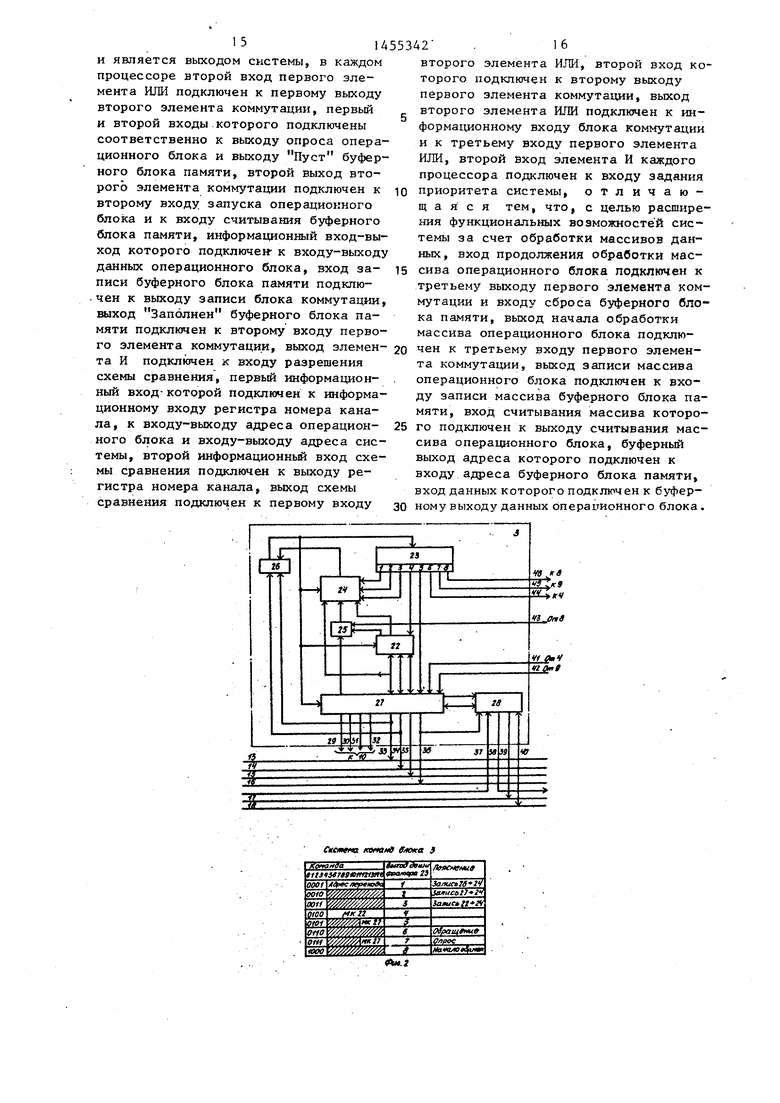

и является выходом системы, в каждом процессоре второй вход первого элемента ИЛИ подключен к первому выходу второго элемента коммутации, первый и второй входы которого подключены соответственно к выходу опроса операционного блока и выходу Пуст буферного блока памяти, второй выход второго элемента коммутации подключен к второму входу запуска операционного блока и к входу считывания буферного блока памяти, информационный вход-выход которого подключен- к входу-выходу данных операционного блока, вход записи буферного блока памяти подключен к выходу записи блока коммутации, илход Заполнен буферного блока памяти подключен к второму входу первого элемента коммутации, выход элемен- 20 чен к третьему входу первого элемента И подключен к входу разрешенията коммутации, выход записи массива

схемы сравнения, первый информацион- . ный вход-которой подключен к информационному входу регистра номера канала, к входу-выходу адреса операцион- 25 ного блока и входу-выходу адреса системы, второй информационньш вход схемы сравнения подключен к выходу регистра номера канала, выход схемы сравнения подключен к первому входу зо

операционного блока подключен к входу записи массива буферного блока памяти, вход считывания массива которого подключен к выходу считывания массива операционного блока, буферный выход адреса которого подключен к входу адреса буферного блока памяти, вход данных которого подключен к буферному выходу данных операиионного блока.

Слскигма кагммв /Кюка }

второго элемента ИЛИ, второй вход которого подключен к второму выходу первого элемента коммутации, выход второго элемента ИЛИ подключен к информационному входу блока коммутации и к третьему входу первого элемента ИЛИ, второй вход элемента И каждого процессора подключен к входу задания

приоритета системы, отличающаяся тем, что, с целью расширения функциональных возможностей системы за счет обработки массивов данных, вход продолжения обработки массива операционного блока подключен к третьему выходу первого элемента коммутации и входу сброса буферного блока памяти, выход начала обработки массива операционного блока подкпюоперационного блока подключен к входу записи массива буферного блока памяти, вход считывания массива которого подключен к выходу считывания массива операционного блока, буферный выход адреса которого подключен к входу адреса буферного блока памяти, вход данных которого подключен к буферному выходу данных операиионного блока.

Фив.

fue.

к 10 к З.П

ns

tlS

Staue fiaСалнвлмл tS Аммм/жМГ

Ctfcmfta гш(н санамвУ т(а 22

к 25

КОП- Koi onfpanuu ВС в1ндача состояний НП-ueami faKu а /«илчни/ги ui popHai4uu

Cucmffta ни1грояо анв Люка 17

Фив,7

iOO

AT 737

ФшМ

(Начаяа

Выдача сигнала ал/юеа из вешифраторо 13

OftjtweMffe ffMfto gJnof-M входу внешнею хлусяв. CvwiwiiMtfe e6ff( taSaoMOJO effM)K27

Увеличение на г edtepmumto. cuemvum г MOftaM

X

Птевача Ng в cve/nvair i

авОямгг. (tepeaava вьНЯуг/га вЛюхП

I ameffejtefft/e (f№Mt,u

записл etff Seve/nimtr 14

I

Запись МквЛтг-г

ФолП

(emut.}

ко9авявтM

M

Выдала catMom опроса швяопз. быдат согнала с 1-го аленемгпаО

выЛгт сагнвлг fleapfo/efw i /юелеЛ/юи(аи /Vmtecccftf

AfOfoveHt/e Smmlfio f-fty

ЛгоЗа x/tycfa. Cfoiffruf cotAr,foS о/уюса if e f-to tu/fo r ieffefffnaS

I Cvum euJHue JOJtfMtf

ftUJM 13.Л1вУлоКЗ

нет

выдвиа си1нала с т-to ft/foffer злемемта Я

..о

бкяючемие ОяомЗ ао r-fty

вяави запуска. Снятие cvMO/ioi wifloca v е 1-ге fbotoSo лммеааа-в

Сиитыбонае звяЛки е I . шин 13, М 8 ffJfOX 3

OSpaSom/fo заяйка в Sewe 3

(pot. П

IauSaua cuiHOM iJmHVoeire с t-to Staoeo tMHenma в

(

Зь/dotfa сигнала начало offoa ботки массива i/з ло(а з. fOopMupoSani/e лгасс1/еа в бло(е 7О

Снятие сигналапзолол /ем-. Формирование следующего на с с ибо effflOffe 7О

Выдала сигнала ..залалнен из 70

выдала сигнала ло/(ировА(е/ с 1-го элемента в

i.

Выдача сигнала лродо/м енил oopa5om/fu occuSo иззле/ еншав, вь/полнение рогра/ / / offpa- ffaf7 f u fiaccuSa S J

ча сигнала олросо з i

t онец j

вб/davo сигнала Havana o6paffom/fu / taccuSa i/j ffjTff ff 3

Фиг. 15

Hai/ojio L

Bbidova сигнала опроса из блока j )

выдочо сигнала со 2-го Sbtjrodo элемента в

Да

Счить/бание p.v.o. с u/uffb/ в G/ioff Ю

блокад по /-лу dJfody 3crnffCf(a. сня/пие сиена а ол/уосаг

CvuminSaHue р. v.o. 3ffjfS/ff/

из ffffO ff 7ff 6 ff/fff 3

OopaoomMlvofyni/wox 3axSf((ej

I ,

6i fda a сиена/ а обращемм 1/з6ломаз

fi7/7d

запрос O/7J последиюще Щп цессораг

да

Выдала сигнала разреи/енил Опосредующий ггроцессар 2

Bb/dava р.v.o. sajfS/fu S лослед(/юи4ий процессор И

е/п

CMffntflf сигнала со f toSA/xoffa 9fleftfft a в

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мультипроцессорная система | 1978 |

|

SU742943A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-30—Публикация

1987-02-02—Подача