1

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе автоматизированного комплекса обработки данных экспериментальных исследований.

Известно устройство для вычисления коэффициентов Фурье, содержащее блок ввода ординат, генератор опор-ной частоты, блок формирования кодов аргументов, реверсивные счетчики, источник эталонного напряжения, два функциональных преобразователя и блок задержки И .

Недостатком этого устройства является низкое быстродействие.

Наиболее близким к предлагаемому по технической сущности является устройство для реализации алгоритма быстрого преобразования Фурье, содержащее основной блок памяти, счетчик адреса и арифметический блок, выход которого соединен с информационным входомосновного блока памяти, выход которого соединен с первым входом арифметического блока, деишфратор адреса, делитель частоты и преобразователь .напряжения в код 2.

Недостатком устройства является то, что оно позволяет вычислять только коэффициенты дискретного преобразования Фурье.

Цель изобретения - расширение функциональных возможностей устройства за счет вычисления коэффициентов обобщенных дискретных функций в области определения N р, где

10 Ь и m - произвольные целые .

поставленная цель достигается тем, что в предложенное устройство для быстрого вычисления коэФФициен15 тов обобщенных дискретных,функций, содержащее основной блок памяти, счетчик адреса и арифметический блок, выход которого соединен с информационным входом основного

20 блока памяти,выход которого соединен с первым входом ариф1 ютического блока, дополнительно введены блок формирования адреса, дополнительный блок памяти, коммутатор и блок вычисления ядра обобщенной функции, содержащий счетчик весовых коэффициентов, умножитель, преобразователь двоичного кода в код по модулю р и память ядра, выход которой

30 iсоединен со VBTOPHM входом арифметичесного устройства, а вход - через преобразователь двоичного кода в код по модулю р подключен к выходу умножителя, первый вход которого подключен к выходу счетчика адреса, а второй - соединен с выходом счетчика весовых коэффициентов, первый вход которого является входом значения р, а второй - соединен с выходом сигнала переполнения счетчика адреса и перв.ым входом коммутатора, второй вход которого

соединен со входом синхронизации устройства, счетным и ходом счетчика адреса и разрешающим входом дополнительного блока памяти, управляющий вход коммутатора подключен к пвому выходу блока формирования адре и входу выбора операции дополнительного блока памяти, адресный вход которого подключен к выходу счетчика адреса, первый вход арифметическго блока подключен к выходу и информационному входу дополнительного блока памяти, выход коммутатора подключен ко входу блока выработки адрса и через линию задержки - к разрешающему входу основного блока памяти, адресный вЯод и вход выбора операции которого соединены соответственно со вторьи-л и третьим выходами блока формирования адреса.

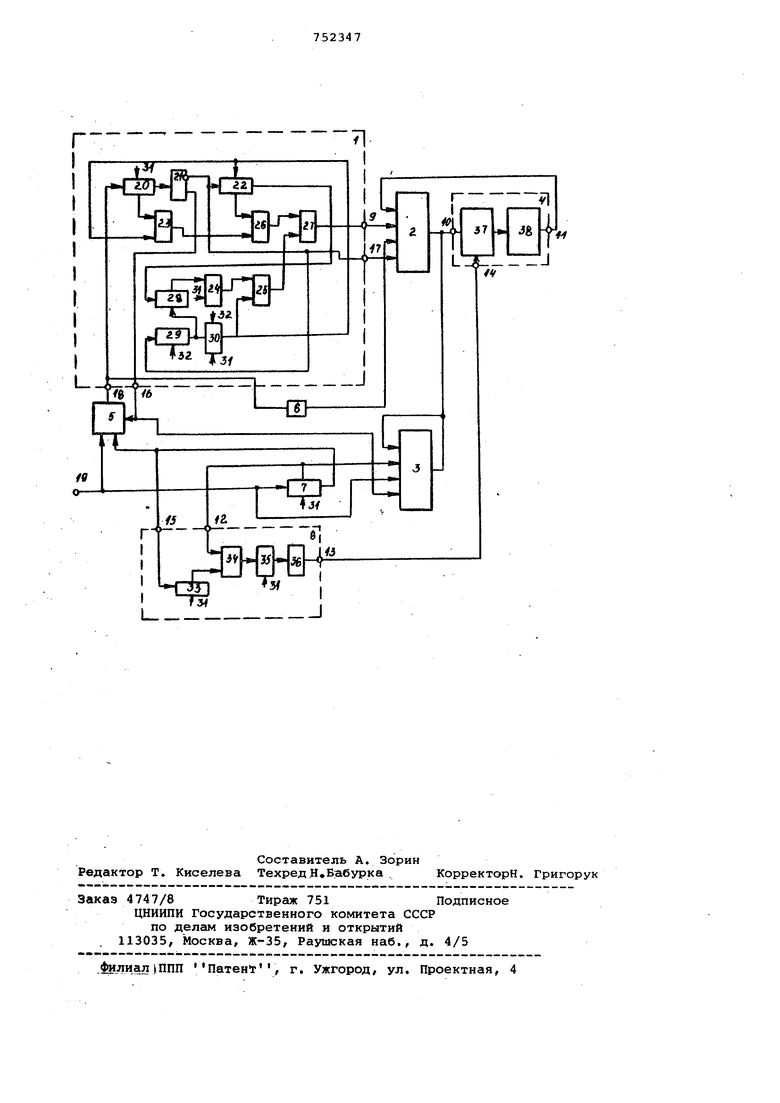

На чертеже представлена блок-схема устройства.

Схема содержит блок 1 формирования адреса, основной блок 2 памяти, дополнительный блок 3 памяти, арифметический блок 4, коммутатор 5, линию 6 задержки, адресный счетчик 7 и блок 8 вычисления ядра обобщенных дискретных функций, выход 9 блока формирования адреса, первый вход 10 арифметического блока, в.ыход 11 арифметического блока, первый вход 12 блока вычисления ядра, его выход 13, второй вход 14 арифметического устройства, второй вход 15 блока вычисления ядра, выходы 16 и 17 блока формирования адреса, вход 18 блока формирования адреса, вход 19 синхронизирующего сигнала устройства.

Блок формирования адреса, в частности, может содержать счетчик 20 по модулю , триггер 21, счетчик 22 по модулю S, блок 23 умножения на модуль S, схему 24 умножения на модуль Р, блок 25 умножения модулей, сумматора 26 и 27, двоичный счетчик 28 микрошагов, счетчик 29 по модулю Q и блок 30 вычисления модуля S, при этом счетный вход счетчика 20 по модулю .р соединен со входом блока формирования адреса, а выход сигналапереполнения счетчика 20 по модулю Р соединен со счетным входом триггера 21, инверсный выход которого соединен со счетным-входом счетчика 29

по модулю Q и со счетным входом счетчика 22 по модулю S, информационный выход которого соединен с одним из входов первого сумматора 26 а выход сигнала переполнения счетчика 22 по модулю S соединен со счётным входом двоичного счетчика 28 микрошагов, информационный выход которого соединен со входом блока 24 умножения на модуль Р, выход которого соединен с первым входом блока 25 умножения модулей. Информационный выход счетчика 20 по модулю Р соединен с первым входом блока 23 умножения на модуль S, выход которой соединен со вторым входом первого сумматора 26, выход которого соединен с первым входом второг сумматора 27, выход которого соединен со вторым выходом блока формирования адреса, выход сигнала переполнения счетчика 29 по модулю Q соединен со входом установки в ноль двоичного счетчика 28 микрошагов и со входом блока 30 вычисления модуля S, выход которого соединен со вторым входом блока 25 умножения модулей, со входом установки счетчика 22 по модулю S и со вторым входом блока 23 умножения на модуль S, входы 31 устройства являются входами в двоичном коде значений модуля Р, вход 32 - значений-.модуля Q.

Блок вычисления ядра обобщенной дискретной функции содержит счетчик 33 весовых коэффициентов, умножитель 34, преобразователь 35 двоичного кода в код по модулю Р, память 36 ядра.

Арифметический блок состоит из последовательно соединенных блоков 3 умножения комплексных чисел и накапливающего сумматора-вычитателя 38

Работа устройства происходит следующим образом.

Предварительно задаются все начальные условия, а именно: на входы 31 всех устройств выполняющих операции по модулю подается в двоичном коде значение модуля Р, через информационный вход в запоминающее устройство 36 блока вычисления ядра заносятся все значения амплитуд, представленные в двоичном коде, которые могут принимать ббобщенные. дискретные функции при данном Р, причем номера ячеек блока 36 совпадают с номерами занесенных в них значений амплитуд. На вход 32 подается значение модуля Q р . В основной блок 2 памяти заносятся ординаты реализации исследуемого процесса, причем адреса ячеек совпадают с номерами занесенных в них ординат реализации.

В исходном состоянии все счетчики устройства установлены в нуль. ТатхэвЦе импульсы со входа 19 поступают через коммутатор 5 на счетный вход 19 счетчика 20 по модулю (Р блока 1 формирования адреса. При поступ лении первых Р - 1 тактовых импульсов на информационном выходе счетчика 20 по модулю Р формируется цифровая последовательность, которая подается на первый вход блока 23 умножения на модуль, на второй вход которого в этот момент с выхода бло .ка 30 вычисления модуля S подается В двоичном коде значение модуля S (для первого шага преобразования Q S) . Тогда в результате перемножения цифровой последовательности, формируемой счетчиком 20 по модулю S на модуль S, на выходе 9 блока 1 формирования адреса формируется соот ветствукяцая цифровая последовательность, в результате чего из основного блока 2 памяти происходит чтение значений ординат реализации, которые последовательно перемножаются в блоке 37 умножения комплексных чисел с нулевой строкой ядра, которую вырабатывает блок 8 и результаты умножения суммируются в сумматоре 38 В это же время значения ординат реализации иэ ячеек основного блока памяти записываются соответственно в ячейки дополнительного блока 3 па мяти, адреса выборки которых выраба тывают счетчик 7 адреса. Следующий Р-ий импульс устанавливает счетчик 20 по модулю Р в ноль, а сигнал переполнения с его выхода перебрасывает триггер 21 в противоположное состояние, в результате чего на вхо выбора операции основного блока 2 памяти устанавливается уровень записи, а на входе выбора операции дополнительного блока памяти устана ливается уровень чтения. В этот момент времени на выходе блока 1 форм рования адреса сформирован адрес выборки и по сигналу выборки, который приходит через линию 6 задержки на вход разрешения выборки основног блока- 2 памяти, происходит запись р зультатов перемножени-я и суммирования в ячейку блока 3, а из ячейки блока 2 памяти происходит считывани ординаты реализации. При поступлени следующих Р-1 тактовых импульсов счетчик 7 адреса вырабатывает соответствующие адреса и происходит опе рация чтения очередных ординат из дополнительного блока 3 памяти. При этом тактовые импульсы со входа 19 на выход коммутатора 5 не проходят, так как на управляющем входе коммутатора 5 данных присутст вует высокий уровень, сформированный триггером 21, в результате чего это уровень дает разрешение на прохо5кде импульсов с выхода сигнала перемножения счетчика 7 адреса и запрет на прохождение тактовых импульсов со входа 19. При поступлении следующего тактового импульса на вход 19 устройства счетчкк 7 адреса устанавливается в ноль и сигнал переполнения с его выхода через коммутатор 5 поступает на счетный вход счетчика 20 по модулю Р и записывает в него единицу и одновременно сигнал переполнения, прошедщий через линию 6 задержки на вход разрешения выборки основного блока 2 памяти, записывает в соответствующую ячейку результат перемножения ординат реализации на первую строку ядра. В дальнейшем работа устройства происходит аналогично до окончания 1-го шага. Первый шаг преобразования оканчивается в тот момент, когда счетчик 29 по модулю Q выработает сигнал переполнения, по переднему фронту которого происходит деление модуля Q на модуль Р в блоке 30 вычисления модуля S, в результате чего на выходе блока 30 вычисления модуля S формируется модуль S. Значение этого модуля поступает соответственно на вход установки модуля счетчика 22 по модулю S и на вход блока 23 умножения на модуль S. При поступлении на вход следующей серии Р импульсов на выходе блока формирования адреса формируются аналогичным образом адреса и происходит требуемый порядок обмена информацией между основным блоком памяти 2 и арифметическим устройством 4, в результате чего происходит вычисление коэффициентов обобщенных дискретных функций. При поступлении импульса счетчик 22 по модулю S вырабатывает импульс переполнения, который записывает в двоичный счетчик 28 микрошагов единицу, которая умножается в блоке 24 умножения на модуль Р и результат перемножается соответственно в блоке 25 умножения на модуль S. Аналогичным образом происходит вычисление на юстальных микрошагах. Когда в счетчик 29 по модулю Q поступит Q-ыи импульс, сигнал переполнения с его выхода установит двоичный счетчик 28 микрошагов в ноль, а по переднему фронту его в блоке 30 вычисления модуля S произойдет следующее деление модуля Q на Р и, если,результат деления меньше единицы, то блок 30 вычисления модуля вырабатывает сигнал окончания вычисления коэффициентов. Работа блока вычисления ядра обобщенных дискретных функций происходит следующим образом. На первом, микрошаге работы устройства счетчик 33 весовых коэффициентов установлен в ноль. Значения кодов с информационного выхода счетчика 7 адреса поступают на второйвход 12 умножителя 34, в результате чего при поступлении на вход устройства первых Р-1 тактовых импульсов умножитель 34 и преобразователь 35 двоичного кода в код по модули Р формируют цифровую последовательность, вследствие чего из блока 36 считывается строка .ядра, которая поступает на второй вход блока 37 умножения комплексных чисел арифметического устройств 4. Следующий Р-ый тактовый импульс устанавливает счетчик 7 адреса в ноль, а сигнал переполнения с его выхода записьшает в счетчик 33 весовых коэффициентов 1, в результате чего на выходе устройства формируется строка ядра обобщенных дискретных функций. Таким образом,предлагаемое устрой ство позволяет вычислять коэффициенты обобщенных дискретных функций с любым Рит. При это будут коэф 1)ициенты преобразования Фурье-Уолша а при - коэффициенты дискретного преобразования Фурье. Предлагаемое устройство позволяет значительно повысить быстродействие вычисления коэффициентов обобщенных дискретных функций. При и выигрыш в 800 быстродействии составит Формула изобретения Устройство для вычисления коэффи циентов обобщенных дискретных функций, содержащее основной блок памят счетчик адреса и арифметический бло выход которого соединен с информаци онным входом основного блока памяти выход которого соединен с первым входом арифметическогоблока, о тличающееся тем, что, с целью расширения функциональных воз можностей за счет вычисления коэффи циентов обобщенных дискретных функций в области определения N Р, где Рит- произвольные целые числ в него введены блок формирования адреса, дополнительный блок памяти, коммутатор и блок вычисления ядра дискретной функции, содержащий счетчик весовых коэффициентов,умножитель, п эеобразователь двоичного кода в код по модулю Р и память ядра, соединенной выходом со вторым входом арифметического блока, а вход - через преобразователь двоичного кода в код по модулю Р подключен к выходу умножителя, первый вход которого подключен к выходу счетчика адреса, а второй - соединен с выходом счетчика весовых коэффициентов, первый вход которого является входом значения Р, а второй - соединен с выходом сигнала переполнения счетчика адреса и первым входом коммутатора, второй вход которого соединен со входом синхронизации устройства, счетным входом счетчика адреса и разрешаняцим входом дополнительного блока памяти, управляющий, вход коммутатора подключен к первому выходу блока формирования адреса и входу выбора операции дополнительного блока памяти, адресный вход которого подключен к выходу счетчика адреса, первый в.ход арифметического блока подключен к выходу и информационному входу дополнительного блока памяти, выход комму т;атора подключен ко входу блока формирования адреса и через линию задepжkи - к разрешающему входу основного блока памяти, адресный вход и вход выбора операции которого соединены соответственно со вторым и третьим выходами блока формирования адреса.. Ниточники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 436358, кл. G 06 F 1/02, 1974. 2.Авторское свидетельство СССР 480079, кл. G 06 F 1/02, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов обобщенных функций Хаара | 1979 |

|

SU942036A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для спектрального анализа | 1981 |

|

SU1013972A1 |

| Генератор обобщенных дискретных функций | 1978 |

|

SU744528A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Генератор функций Уолша | 1985 |

|

SU1262470A1 |

| Устройство для формирования элементов расширенных полей Галуа GF ( @ ) и кодовых последовательностей на их основе | 1987 |

|

SU1441413A1 |

Авторы

Даты

1980-07-30—Публикация

1978-06-07—Подача