Изобретение относится к вычислительной технике и может быть использовано для отображения информации о ходе технологических процессов и при отображении многоплановых изображений.-

Цель изобретения -повышение быстродействия устройства.

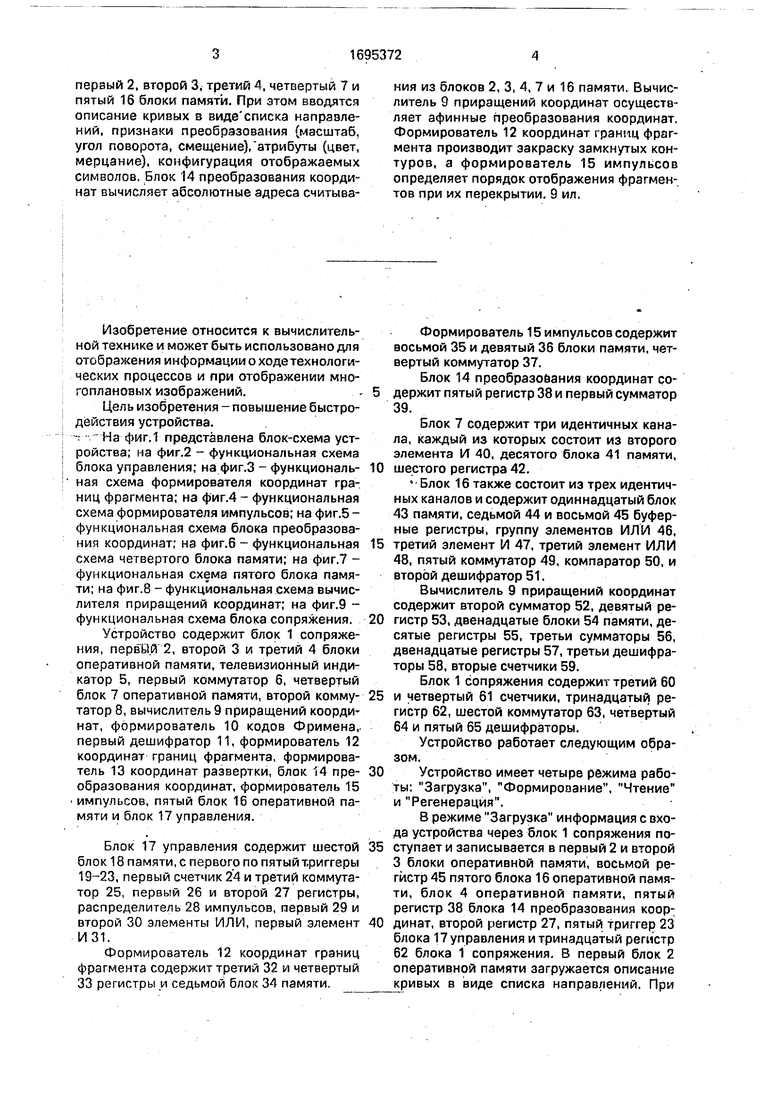

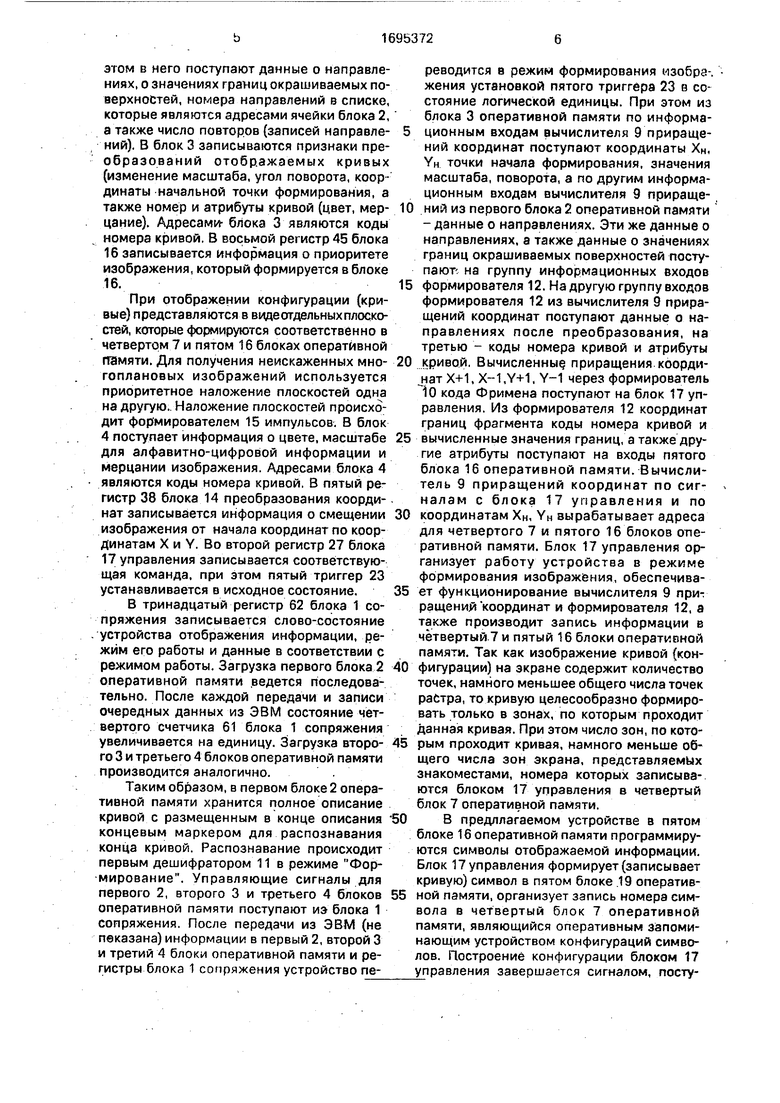

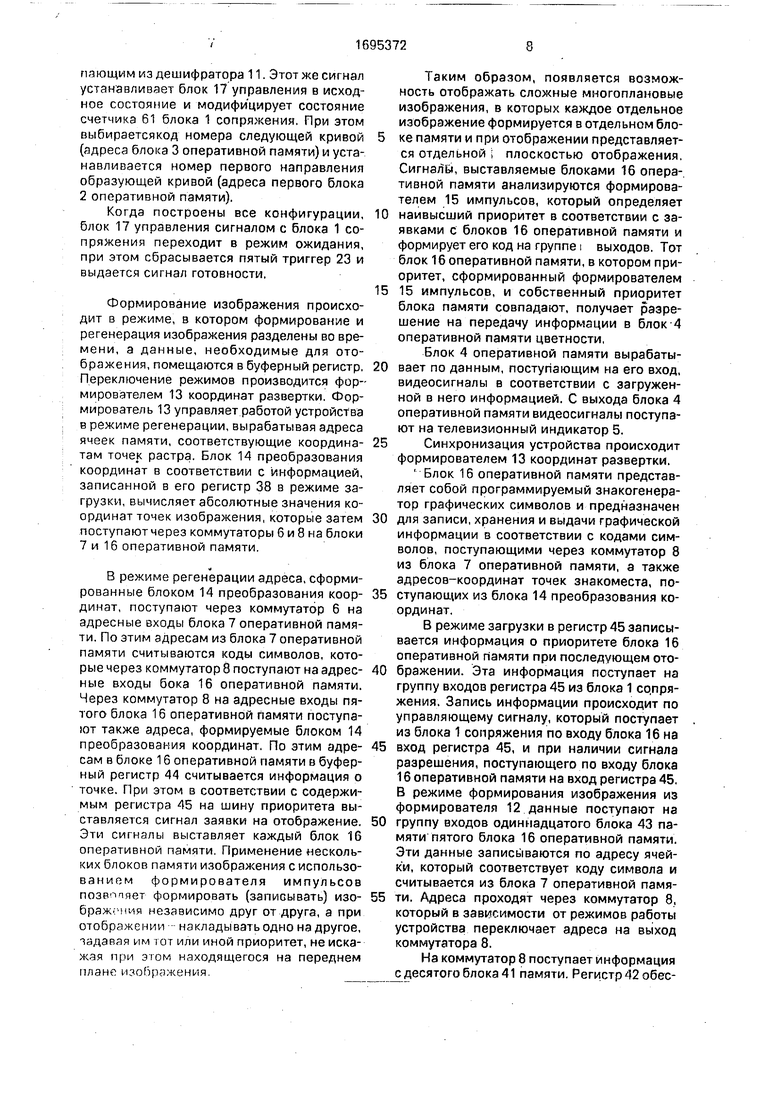

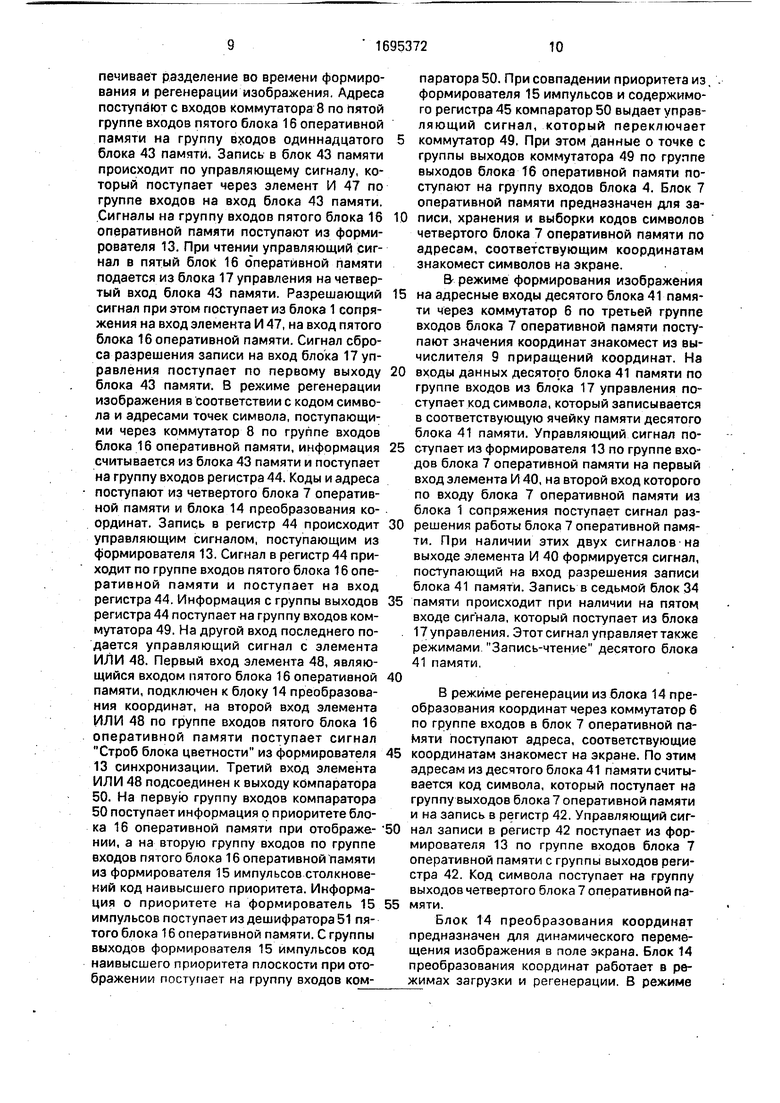

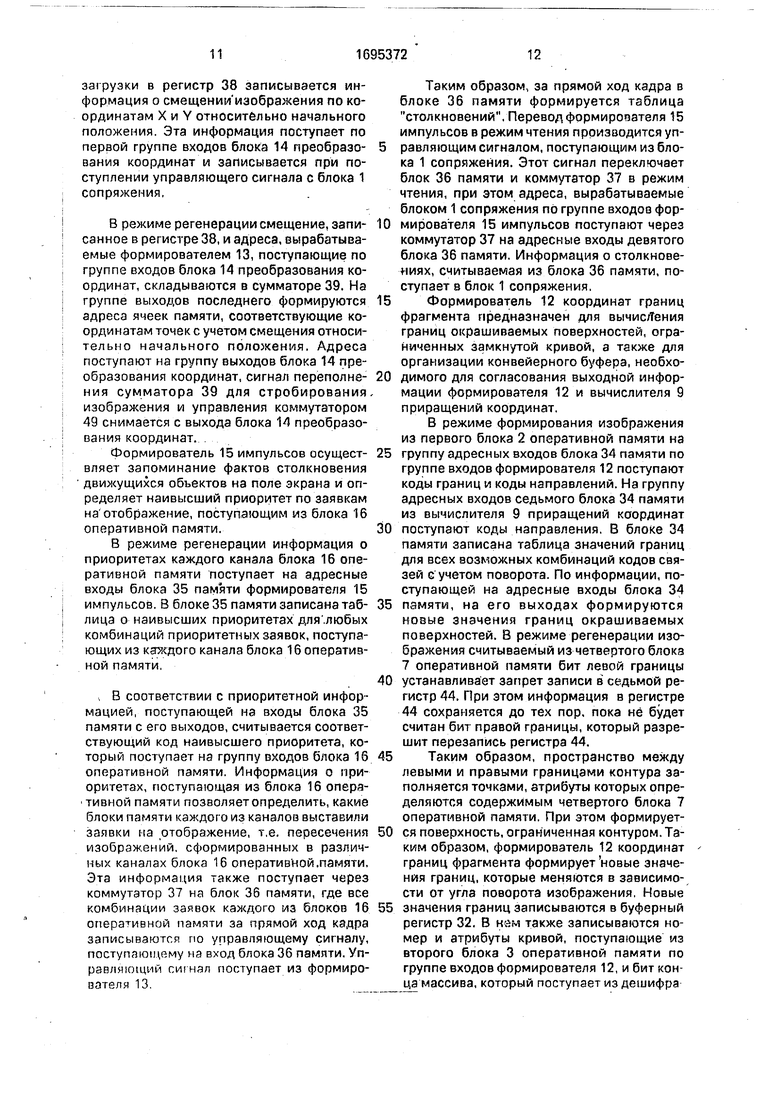

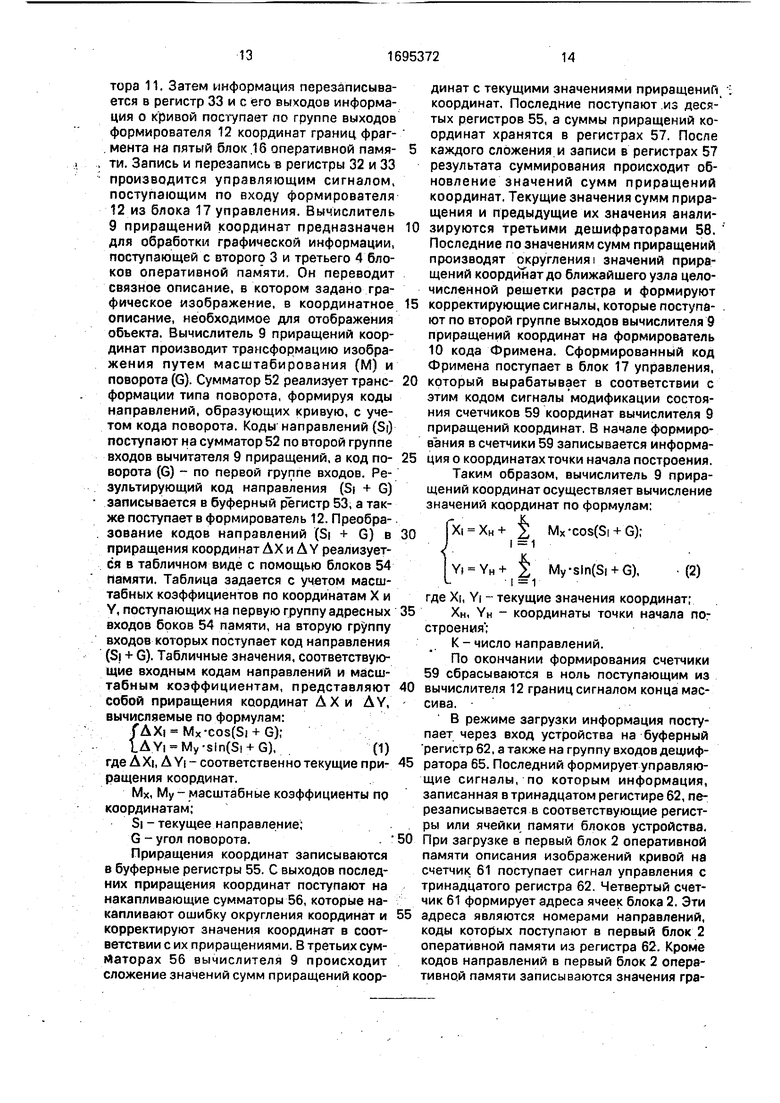

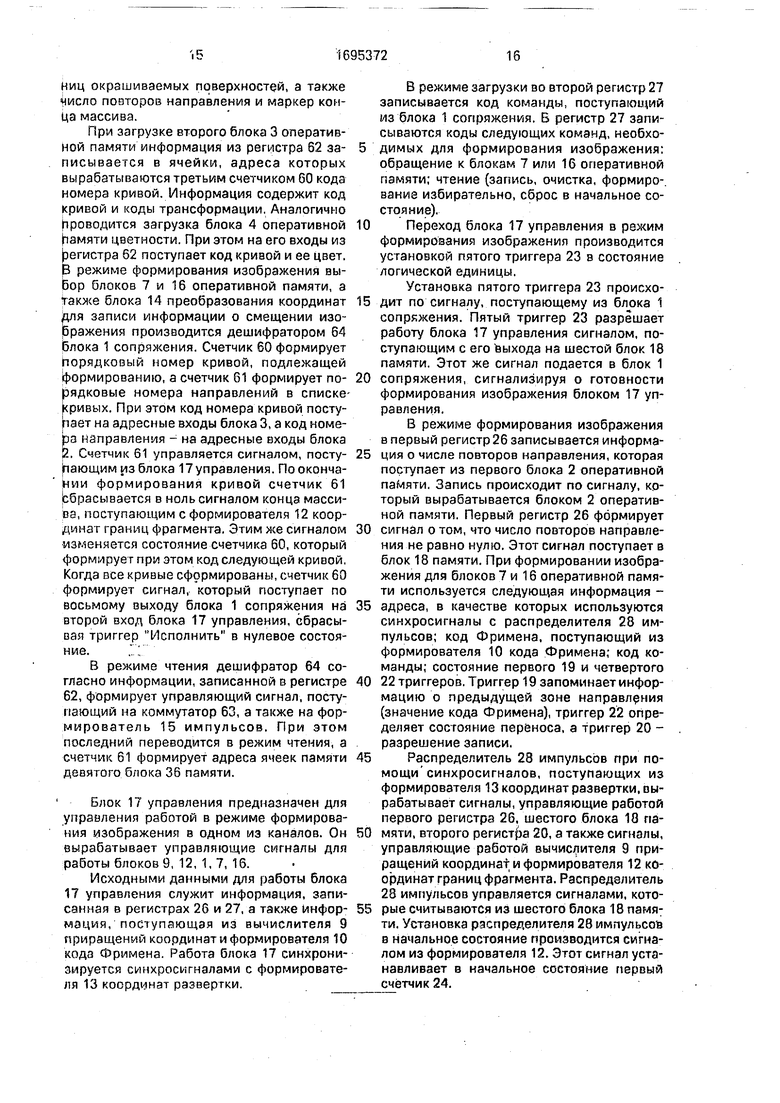

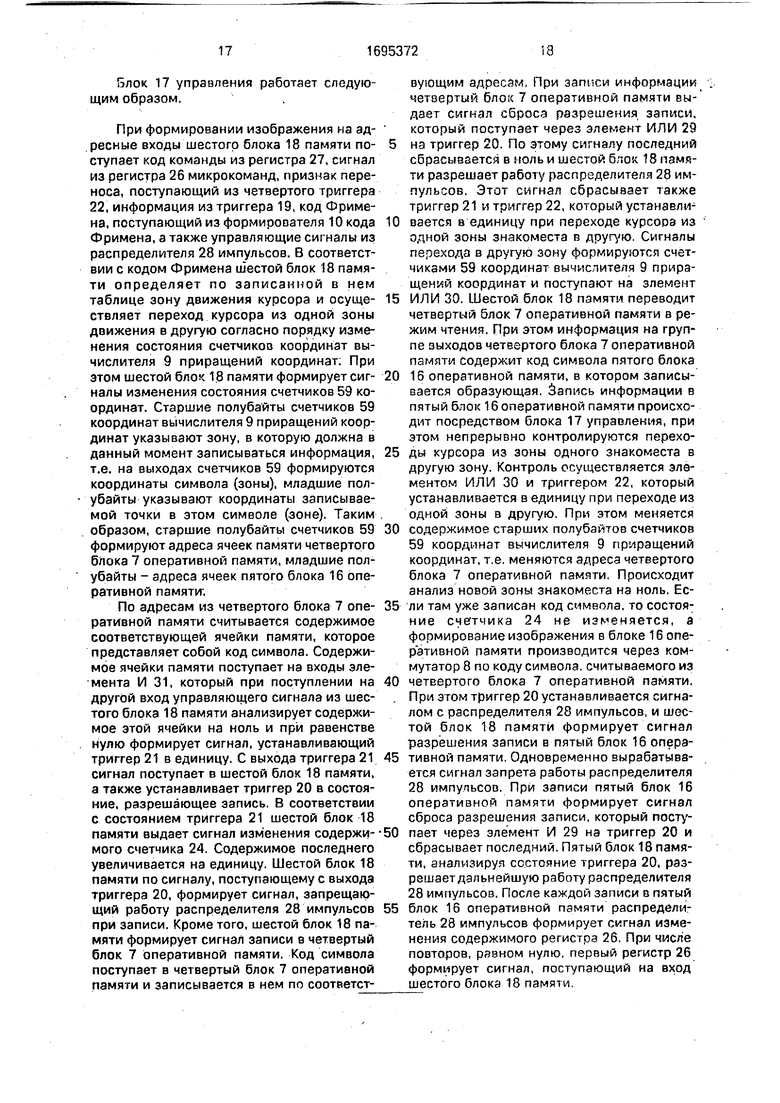

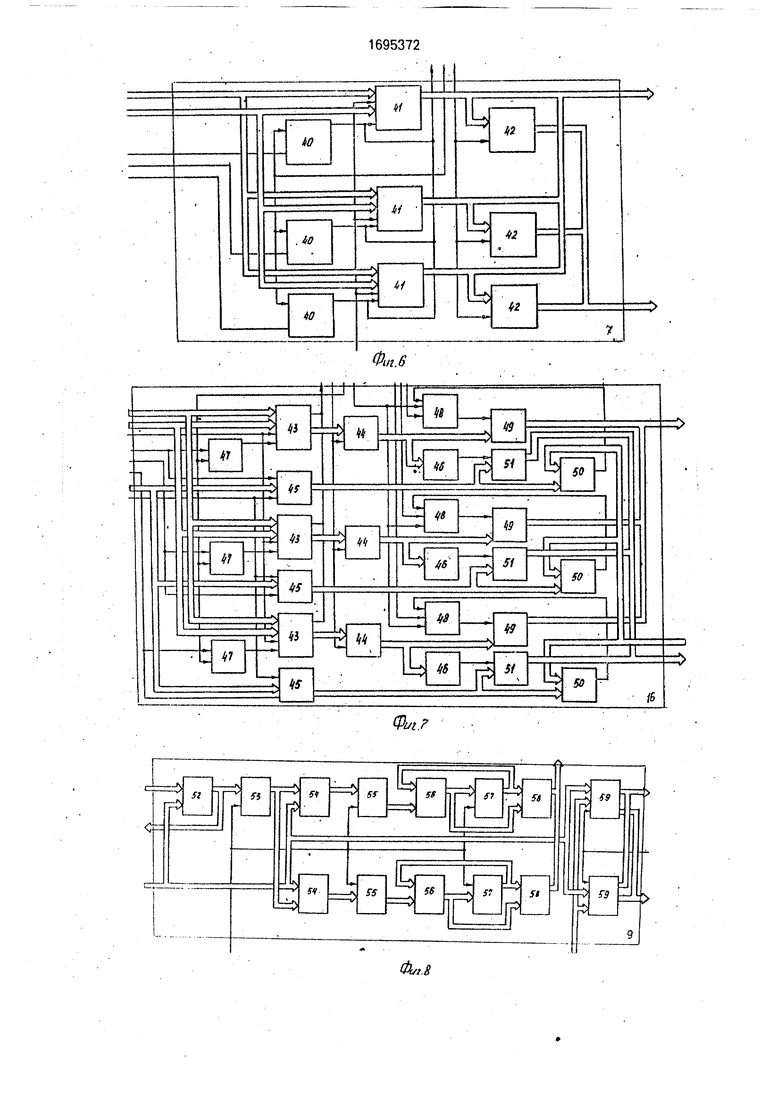

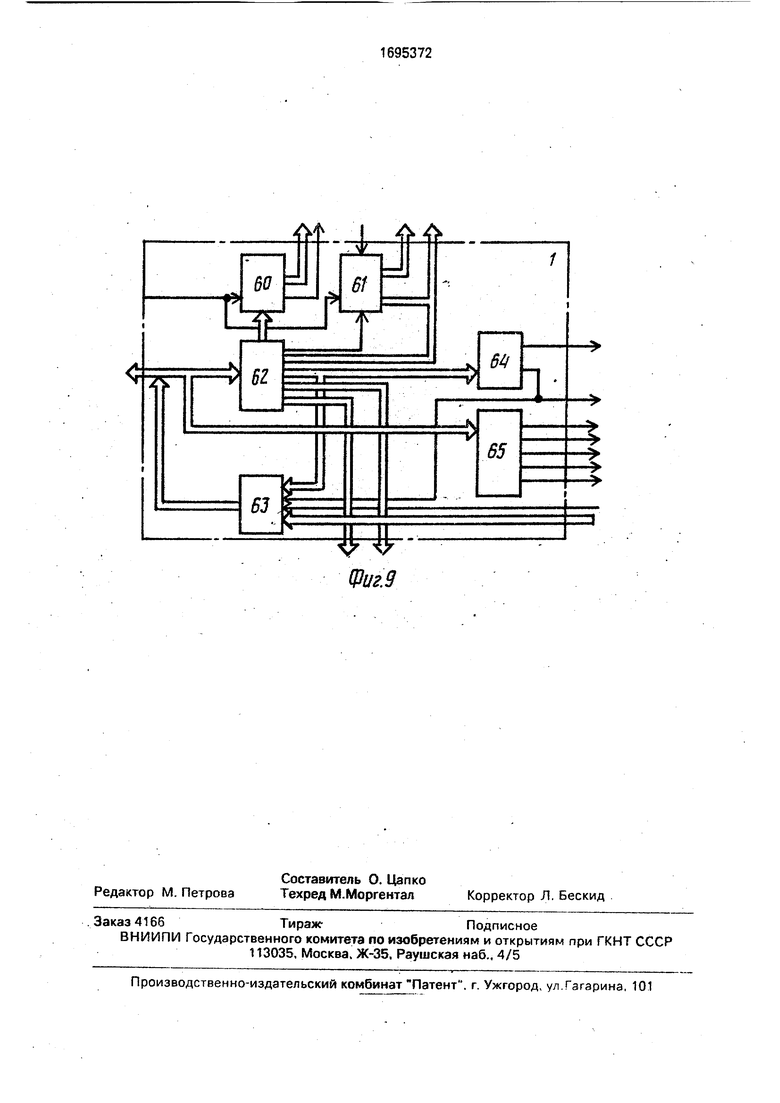

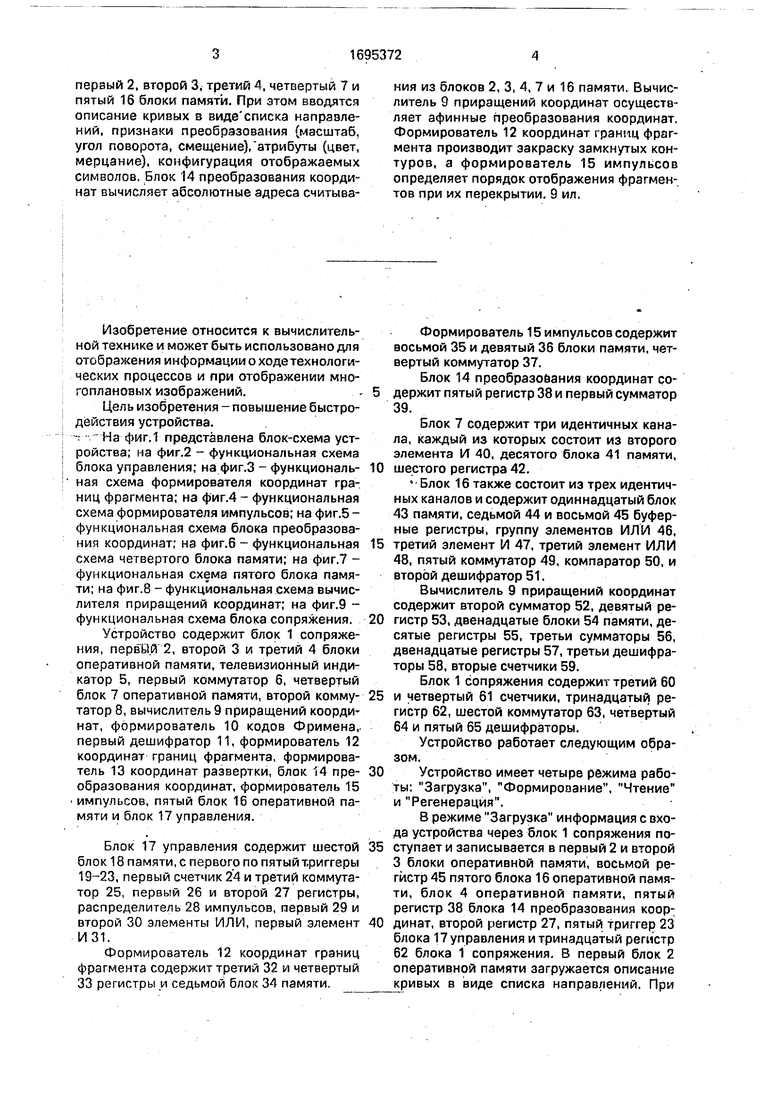

- На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема блока управления; на фиг.З - функциональ- ная схема формирователя координат границ фрагмента; на фиг.4 - функциональная схема формирователя импульсов; на фиг.5- функциональная схема блока преобразования координат; на фиг.6 - функциональная схема четвертого блока памяти; на фиг.7 - функциональная схема пятого блока памяти; на фиг.8 - функциональная схема вычислителя приращений координат; на фиг.9 - функциональная схема блока сопряжения.

Устройство содержит блок 1 сопряжения, первый 2, второй 3 и третий 4 блоки оперативной памяти, телевизионный индикатор 5, первый коммутатор 6, четвертый блок 7 оперативной памяти, второй комму- татор 8, вычислитель 9 приращений коорди- нат, формирователь 10 кодов Фримена, первый дешифратор 11, формирователь 12 координат границ фрагмента, формирователь 13 координат развертки, блок 14 пре- образования координат, формирователь 15 импульсов, пятый блок 16 оперативной памяти и блок 17 управления.

Блок 17 управления содержит шестой блок 18 памяти, с первого по пятый триггеры 19-23, первый счетчик 24 и третий коммутатор 25, первый 26 и второй 27 регистры, распределитель 28 импульсов, первый 29 и второй 30 элементы ИЛИ, первый элемент И31.

Формирователь 12 координат границ фрагмента содержит третий 32 и четвертый 33 регистры .и седьмой блок 34 памяти,

Формирователь 15 импульсов содержит восьмой 35 и девятый 36 блоки памяти, четвертый коммутатор 37.

Блок 14 преобразоёания координат содержит пятый регистр 38 и первый сумматор 39.

Блок 7 содержит три идентичных канала, каждый из которых состоит из второго элемента И 40, десятого блока 41 памяти, шестого регистра 42.

4 Блок 16 также состоит из трех идентичных каналов и содержит одиннадцатый блок 43 памяти, седьмой 44 и восьмой 45 буферные регистры, группу элементов ИЛИ 46, третий элемент И 47, третий элемент ИЛИ 48, пятый коммутатор 49, компаратор 50, и второй дешифратор 51.

Вычислитель 9 приращений координат содержит второй сумматор 52, девятый регистр 53, двенадцатые блоки 54 памяти, десятые регистры 55, третьи сумматоры 56, двенадцатые регистры 57, третьи дешифраторы 58, вторые счетчики 59.

Блок 1 сопряжения содержит третий 60 и четвертый 61 счетчики, тринадцатый регистр 62, шестой коммутатор 63, четвертый 64 и пятый 65 дешифраторы.

Устройство работает следующим образом.

Устройство имеет четыре режима работы: Загрузка, Формироаание, Чтение и Регенерация.

В режиме Загрузка информация с входа устройства через блок 1 сопряжения поступает и записывается в первый 2 и второй 3 блоки оперативной памяти, восьмой регистр 45 пятого блока 16 оперативной памяти, блок 4 оперативной памяти, пятый регистр 38 блока 14 преобразования координат, второй регистр 27, пятый триггер 23 блока 17 управления и тринадцатый регистр 62 блока 1 сопряжения. В первый блок 2 оперативной памяти загружается описание кривых в виде списка направлений. При

этом в него поступают данные о направлениях, о значениях границ окрашиваемых поверхностей, номера направлений в списке, которые являются адресами ячейки блока 2, а также число повторов (записей направлений). В блок 3 записываются признаки преобразований отображаемых кривых (изменение масштаба, угол поворота, координаты начальной точки формирования, а также номер и атрибуты кривой (цвет, мерцание). Адресами- блока 3 являются коды номера кривой. В восьмой регистр 45 блока

16записывается информация о приоритете изображения, который формируется в блоке 16.

При отображении конфигурации (кривые) представляются в виде отдельных плоскостей, которые формируются соответственно в четвертом 7 и пятом 16 блоках оперативной памяти. Для получения неискаженных многоплановых изображений используется приоритетное наложение плоскостей одна на другую. Наложение плоскостей происходит формирователем 15 импульсов. В блок 4 поступает информация о цвете, масштабе для алфавитно-цифровой информации и мерцании изображения. Адресами блока 4 являются коды номера кривой. В пятый регистр 38 блока 14 преобразования координат записывается информация о смещении изображения от начала координат по координатам X и Y. Во второй регистр 27 блока

17управления записывается соответствующая команда, при этом пятый триггер 23 устанавливается в исходное состояние.

В тринадцатый регистр 62 блока 1 сопряжения записывается слово-состояние устройства отображения информации, режим его работы и данные в соответствии с режимом работы. Загрузка первого блока 2 оперативной памяти ведется последовательно. После каждой передачи и записи очередных данных из ЭВМ состояние четвертого счетчика 61 блока 1 сопряжения увеличивается на единицу. Загрузка второго 3 и третьего 4 блоков оперативной памяти производится аналогично.

Таким образом, в первом блоке 2 оперативной памяти хранится полное описание кривой с размещенным в конце описания концевым маркером для распознавания конца кривой. Распознавание происходит первым дешифратором 11 в режиме Формирование. Управляющие сигналы для первого 2, второго 3 и третьего 4 блоков оперативной пзмяти поступают иэ блока 1 сопряжения. После передачи из ЭВМ (не пеказана) информации в первый 2, второй 3 и третий 4 блоки оперативной памяти и регистры блока 1 сопряжения устройство переводится в режим формирования мзобра-. жения установкой пятого триггера 23 в состояние логической единицы. При этом из блока 3 оперативной памяти по информа- 5 ционным входам вычислителя 9 приращений координат поступают координаты Хн, YH точки начала формирования, значения масштаба, поворота, а по другим информационным входам вычислителя 9 прираще10 ний из первого блока 2 оперативной памяти - данные о направлениях. Эти же данные о направлениях, а также данные о значениях границ окрашиваемых поверхностей поступают на группу информационных входов

5 формирователя 12. На другую группу входов формирователя 12 из вычислителя 9 приращений координат поступают данные о направлениях после преобразования, на третью - коды номера кривой и атрибуты

0 кривой. Вычисленные приращения коорди- .нат Х+1, X-1.Y+1. Y-1 через формирователь 10 кода Фримена поступают на блок 17 управления. Из формирователя 12 координат границ фрагмента коды номера кривой и

5 вычисленные значения границ, а также другие атрибуты поступают на входы пятого блока 16 оперативной памяти. Вычислитель 9 приращений координат по сигналам с блока 17 управления и по

0 координатам Хн, YH вырабатывает адреса для четвертого 7 и пятого 16 блоков оперативной памяти. Блок 17 управления организует работу устройства в режиме формирования изображения, обеспечива5 ет функционирование вычислителя 9 прит ращений координат и формирователя 12, а также производит запись информации в четвертый 7 и пятый 16 блоки оперативной памяти. Так как изображение кривой (кон0 фигурации) на экране содержит количество точек, намного меньшее общего числа точек растра, то кривую целесообразно формировать только в зонах, по которым проходит данная кривая. При этом число зон, по кото5 рым проходит кривая, намного меньше общего числа зон экрана, представляемых знакоместами, номера которых записываются блоком 17 управления в четвертый блок 7 оперативной памяти.

0 В предлагаемом устройстве в пятом блоке 16 оперативной памяти программируются символы отображаемой информации. Блок 17 управления формирует (записывает кривую) символ в пятом блоке 19 оператив5 ной памяти, организует запись номера символа в четвертый блок 7 оперативной памяти, являющийся оперативным запоминающим устройством конфигураций символов. Построение конфигурации блоком 17 управления завершается сигналом, поступающим из дешифратора 11. Этот же сигнал устанавливает блок 17 управления в исходное состояние и модифицирует состояние счетчика 61 блока 1 сопряжения, При этом выбираетсякод номера следующей кривой (адреса блока 3 оперативной памяти) и устанавливается номер первого направления образующей кривой (адреса первого блока 2 оперативной памяти).

Когда построены все конфигурации, блок 17 управления сигналом с блока 1 сопряжения переходит в режим ожидания, при этом сбрасывается пятый триггер 23 и выдается сигнал готовности.

Формирование изображения происходит в режиме, в котором формирование и регенерация изображения разделены во времени, а данные, необходимые для отображения, помещаются в буферный регистр, Переключение режимов производится формирователем 13 координат развертки. Формирователь 13 управляет работой устройства в режиме регенерации, вырабатывая адреса ячеек памяти, соответствующие координатам точек растра. Блок 14 преобразования координат в соответствии с информацией, записанной в его регистр 38 в режиме загрузки, вычисляет абсолютные значения координат точек изображения, которые затем поступают через коммутаторы б и 8 на блоки 7 и 16 оперативной памяти.

В режиме регенерации адреса, сформированные блоком 14 преобразования координат, поступают через коммутатор 6 на адресные входы блока 7 оперативной памяти. По этим адресам из блока 7 оперативной памяти считываются коды символов, которые через коммутатор 8 поступают на адресные входы бока 16 оперативной памяти. Через коммутатор 8 на адресные входы пятого блока 16 оперативной памяти поступают также адреса, формируемые блоком 14 преобразования координат. По этим адресам в блоке 16 оперативной памяти в буферный регистр 44 считывается информация о точке. При этом в соответствии с содержимым регистра 45 на шину приоритета выставляется сигнал заявки на отображение. Эти сигналы выставляет каждый блок 16 оперативной памяти Применение нескольких блоков памяти изображения с использо- ванием формирователя импульсов позв тпяет формировать (записывать) изо- браж. ния независимо друг от друга, а при отображении накладывать одно на другое, тадавая им i от или иной приоритет, не искажая при этм находящегося на переднем плане изображения

Таким образом, появляется возможность отображать сложные многоплановые изображения, в которых каждое отдельное изображение формируется в отдельном блоке памяти и при отображении представляется отдельной , плоскостью отображения. Сигналы, выставляемые блоками 16 оперативной памяти анализируются формирователем 15 импульсов, который определяет

0 наивысший приоритет в соответствии с заявками с блоков 16 оперативной памяти и формирует его код на группе i выходов. Тот блок 16 оперативной памяти, в котором приоритет, сформированный формирователем

5 15 импульсов, и собственный приоритет блока памяти совпадают, получает разрешение на передачу информации в блок 4 оперативной памяти цветности,

Блок 4 оперативной памяти вырабаты0 вает по данным, поступающим на его вход, видеосигналы в соответствии с загруженной в него информацией. С выхода блока 4 оперативной памяти видеосигналы поступают на телевизионный индикатор 5.

5Синхронизация устройства происходит

формирователем 13 координат развертки.

Блок 16 оперативной памяти представляет собой программируемый знакогенератор графических символов и предназначен

0 для записи, хранения и выдачи графической информации в соответствии с кодами символов, поступающими через коммутатор 8 из блока 7 оперативной памяти, а также адресов-координат точек знакоместа, по5 ступающих из блока 14 преобразования координат.

В режиме загрузки в регистр 45 записывается информация о приоритете блока 16 оперативной памяти при последующем ото0 бражении. Эта информация поступает на группу входов регистра 45 из блока 1 со.пря- жения. Запись информации происходит по управляющему сигналу, который поступает из блока 1 сопряжения по входу блока 16 на

5 вход регистра 45, и при наличии сигнала разрешения, поступающего по входу блока 16 оперативной памяти на вход регистра 45. В режиме формирования изображения из формирователя 12 данные поступают на

0 группу входов одиннадцатого блока 43 памяти пятого блока 16 оперативной памяти. Эти данные записываются по адресу ячейки, который соответствует коду символа и считывается из блока 7 оперативной памя5 ти. Адреса проходят через коммутатор 8, который в зависимости от режимов работы устройства переключает адреса на выход коммутатора 8.

На коммутатор 8 поступает информация с десятого блока 41 памяти. Регистр 42 обеспечивает разделение во времени формирования и регенерации изображения. Адреса поступают с входов коммутатора 8 по пятой группе входов пятого блока 16 оперативной памяти на группу входов одиннадцатого блока 43 памяти. Запись в блок 43 памяти происходит по управляющему сигналу, который поступает через элемент И 47 по группе входов на вход блока 43 памяти. Сигналы на группу входов пятого блока 16 оперативной памяти поступают из формирователя 13. При чтении управляющий сигнал в пятый блок 16 оперативной памяти подается из блока 17 управления на четвертый вход блока 43 памяти. Разрешающий сигнал при этом поступает из блока 1 сопряжения на вход элемента И 47, на вход пятого блока 16 оперативной памяти. Сигнал сброса разрешения записи на вход блока 17 управления поступает по первому выходу блока 43 памяти. В режиме регенерации изображения в соответствии с кодом символа и адресами точек символа, поступающими через коммутатор 8 по группе входов блока 16 оперативной памяти, информация считывается из блока 43 памяти и поступает на группу входов регистра 44. Коды и адреса поступают из четвертого блока 7 оперативной памяти и блока 14 преобразования координат. Запись в регистр 44 происходит управляющим сигналом, поступающим из формирователя 13. Сигнал в регистр 44 приходит по группе входов пятого блока 16 оперативной памяти и поступает на вход регистра 44. Информация с группы выходов регистра 44 поступает на группу входов коммутатора 49. На другой вход последнего подается управляющий сигнал с элемента ИЛИ 48. Первый вход элемента 48, являющийся входом пятого блока 16 оперативной памяти, подключен к блоку 14 преобразования координат, на второй вход элемента ИЛИ 48 по группе входов пятого блока 16 оперативной памяти поступает сигнал Строб блока цветности из формирователя 13 синхронизации. Третий вход элемента ИЛИ 48 подсоединен к выходу компаратора 50. На первую группу входов компаратора 50 поступает информация о приоритете блока 16 оперативной памяти при отображении, а на вторую группу входов по группе входов пятого блока 16 оперативной памяти из формирователя 15 импульсов столкновений код наивысшего приоритета. Информация о приоритете на формирователь 15 импульсов поступает из дешифратора 51 пятого блока 16 оперативной памяти. С группы выходов формирователя 15 импульсов код наивысшего приоритета плоскости при отображении поступает на группу входов компаратора 50. При совпадении приоритета из, формирователя 15 импульсов и содержимого регистра 45 компаратор 50 выдает управ- ляющий сигнал, который переключает 5 коммутатор 49. При этом данные о точке с группы выходов коммутатора 49 по группе выходов блока 16 оперативной памяти поступают на группу входов блока 4. Блок 7 оперативной памяти предназначен для за10 писи, хранения и выборки кодов символов четвертого блока 7 оперативной памяти по адресам, соответствующим координатам знакомест символов на экране.

В- режиме формирования изображения

15 на адресные входы десятого блока 41 памяти через коммутатор 6 по третьей группе входов блока 7 оперативной памяти поступают значения координат знакомест из вычислителя 9 приращений координат. На

0 входы данных десятого блока 41 памяти по группе входов из блока 17 управления поступает код символа, который записывается в соответствующую ячейку памяти десятого блока 41 памяти. Управляющий сигнал по5 ступает из формирователя 13 по группе входов блока 7 оперативной памяти на первый вход элемента И 40, на второй вход которого по входу блока 7 оперативной памяти из блока 1 сопряжения поступает сигнал раз0 решения работы блока 7 оперативной памяти. При наличии этих двух сигналов на выходе элемента И 40 формируется сигнал, поступающий на вход разрешения записи блока 41 памяти. Запись в седьмой блок 34

5 памяти происходит при наличии на пятом входе сигнала, который поступает из блока 17управления. Этот сигнал управляет также режимами Запись-чтение десятого блока 41 памяти,

0

В режиме регенерации из блока 14 преобразования координат через коммутатор 6 по группе входов в блок 7 оперативной памяти поступают адреса, соответствующие

5 координатам знакомест на экране. По этим адресам из десятого блока 41 памяти считывается код символа, который поступает на группу выходов блока 7 оперативной памяти и на запись в регистр 42. Управляющий сиг0 нал записи в регистр 42 поступает из формирователя 13 по группе входов блока 7 оперативной памяти с группы выходов регистра 42. Код символа поступает на группу выходов четвертого блока 7 оперативной па5 мяти.

Блок 14 преобразования координат предназначен для динамического перемещения изображения в поле экрана. Блок 14 преобразования координат работает в режимах загрузки и регенерации. В режиме

загрузки в регистр 38 записывается информация о смещении изображения по координатам X и Y относительно начального положения. Эта информация поступает по первой группе входов блока 14 преобразования координат и записывается при поступлении управляющего сигнала с блока 1 сопряжения,

В режиме регенерации смещение, записанное в регистре 38, и адреса, вырабатываемые формирователем 13, поступающие по группе входов блока 14 преобразования координат, складываются в сумматоре 39. На группе выходов последнего формируются адреса ячеек памяти, соответствующие координатам точек с учетом смещения относм- тельно начального положения, Адреса поступают на группу выходов блока 14 преобразования координат, сигнал переполнения сумматора 39 для стробирования. изображения и управления коммутатором 49 снимается с выхода блока 14 преобразования координат.

Формирователь 15 импульсов осуществляет запоминание фактов столкновения движущихся объектов на поле экрана и определяет наивысший приоритет по заявкам на отображение, поступающим из блока 16 оперативной памяти.

В режиме регенерации информация о приоритетах каждого канала блока 16 оперативной памяти поступает на адресные входы блока 35 памяти формирователя 15 импульсов. В блоке 35 памяти записана таблица о наивысших приоритетах для .любых комбинаций приоритетных заявок, поступающих из каждого канала блока 16 оперативной памяти,

v В соответствии с приоритетной информацией, поступающей на входы блока 35 памяти с его выходов, считывается соответствующий код наивысшего приоритета, который поступает на группу входов блока 16 оперативной памяти. Информация о приоритетах, поступающая из блока 16 оперативной памяти позволяет определить, какие блоки памяти каждого из каналов выставили заявки на отображение, т.е. пересечения изображений, сформированных в различных каналах блока 16 оперативной.памяти, Эта информация также поступает через коммутатор 37 на блок 36 памяти, где все комбинации заявок каждого из блоков 16 оперативной памяти за прямой ход кадра записываются по управляющему сигналу, поступающему на вход блока 36 памяти. Управляющий сигнал поступает из формирователя 13

Таким образом, за прямой ход кадра в блоке 36 памяти формируется таблица столкновений. Перевод формирователя 15 импульсов в режим чтения производится управляющим сигналом, поступающим из блока 1 сопряжения. Этот сигнал переключает блок 36 памяти и коммутатор 37 в режим чтения, при этом адреса, вырабатываемые блоком 1 сопряжения по группе входов фор0 мирователя 15 импульсов поступают через коммутатор 37 на адресные входы девятого блока 36 памяти. Информация о столкновениях, считываемая из блока 36 памяти, поступает в блок 1 сопряжения.

5 Формирователь 12 координат границ фрагмента предназначен для вычис/Тения границ окрашиваемых поверхностей, ограниченных замкнутой кривой, а также для организации конвейерного буфера, необхо0 димого для согласования выходной информации формирователя 12 и вычислителя 9 приращений координат.

В режиме формирования изображения из первого блока 2 оперативной памяти на

5 группу адресных входов блока 34 памяти по группе входов формирователя 12 поступают коды границ и коды направлений. На группу адресных входов седьмого блока 34 памяти из вычислителя 9 приращений координат

0 поступают коды направления. В блоке 34 памяти записана таблица значений границ для всех возможных комбинаций кодов связей с учетом поворота. По информации, поступающей на адресные входы блока 34

5 памяти, на его выходах формируются новые значения границ окрашиваемых поверхностей. В режиме регенерации изображения считываемый из четвертого блока 7 оперативной памяти бит левой границы

0 устанавливает запрет записи в седьмой регистр 44. При этом информация в регистре 44 сохраняется до тех пор. пока не будет считан бит правой границы, который разрешит перезапись регистра 44.

5 Таким образом, пространство между левыми и правыми границами контура заполняется точками, атрибуты которых определяются содержимым четвертого блока 7 оперативной памяти. При этом формирует0 ся поверхность, ограниченная контуром. Таким образом, формирователь 12 координат границ фрагмента формирует новые значения границ, которые меняются в зависимости от угла поворота изображения, Новые

5 значения границ записываются в буферный регистр 32. В нам также записываются номер и атрибуты кривой, поступающие из второго блока 3 оперативной памяти по группе входов формирователя 12, и бит конца массива, который поступает из дешифра

тора 11. Затем информация перезаписывается в регистр 33 и с его выходов информация о кривой поступает по группе выходов формирователя 12 координат границ фраг- мента на пятый блок .16 оперативной памя- ти. Запись и перезапись в регистры 32 и 33 производится управляющим сигналом, поступающим по входу формирователя 12 из блока 17 управления. Вычислитель 9 приращений координат предназначен для обработки графической информации, поступающей с второго 3 и третьего 4 блоков оперативной пам яти. Он переводит связное описание, в котором задано графическое изображение, в координатное описание, необходимое для отображения объекта. Вычислитель 9 приращений координат производит трансформацию изображения путем масштабирования (М) и поворота (G). Сумматор 52 реализует транс- формации типа поворота, формируя коды направлений, образующих кривую, с учетом кода поворота. Коды направлений (Si) поступают на сумматор 52 по второй группе входов вычитателя 9 приращений, а код по- ворота (G) - по первой группе входов. Результирующий код направления (Si + G) записывается в буферный регистр 53, а также поступает в формирователь 12. Преобразование кодов направлений (Si + G) в приращения координат АХи AY реализуется в табличном виде с помощью блоков 54 памяти. Таблица задается с учетом масштабных коэффициентов по координатам X и Y, поступающих на первую группу адресных входов боков 54 памяти, на вторую группу входов которых поступает код направления {Si + G). Табличные значения, соответствующие входным кодам направлений и масштабным коэффициентам, представляют собой приращения координат ДХи ДУ, вычисляемые по формулам:

/AXi Mx-cos(Si + G);

LAYi My-sln(Si + G),(1)

где Д Xi, Д Yi - соответственно текущие при- ращения координат.

Мх, Му- масштабные коэффициенты по координатам;

Si - текущее направление;

G - угол поворота.

Приращения координат записываются в буферные регистры 55. С выходов последних приращения координат поступают на накапливающие сумматоры 56, которые накапливают ошибку округления координат и корректируют значения координат в соответствии с их приращениями. В третьих сумматорах 56 вычислителя 9 происходит сложение значений сумм приращений координат с текущими значениями приращений координат. Последние поступают из десятых регистров 55, а суммы приращений координат хранятся в регистрах 57. После каждого сложения и записи в регистрах 57 результата суммирования происходит обновление значений сумм приращений координат. Текущие значения сумм приращения и предыдущие их значения анализируются третьими дешифраторами 58. Последние по значениям сумм приращений производят округления: значений приращений координат до ближайшего узла целочисленной решетки растра и формируют корректирующие сигналы, которые поступают по второй группе выходов вычислителя 9 приращений координат на формирователь 10 кода Фримена. Сформированный код Фримена поступает в блок 17 управления, который вырабатывает в соответствии с этим кодом сигналы модификации состояния счетчиков 59 координат вычислителя 9 приращений координат. В начале формирования в счетчики 59 записывается информация о координатах точки начала построения. Таким образом, вычислитель 9 приращений координат осуществляет вычисление значений координат по формулам:

ГХ( Хн + Ј Mx-cos(Si + G);

1

н+ i

My-sln(Si + G),

(2)

где Xi, YI - текущие значения координат;

Хн, YH - координаты точки начала по: строения ;

К - число направлений.

По окончании формирования счетчики 59 сбрасываются в ноль поступающим из вычислителя 12 границ сигналом конца массива.

В режиме загрузки информация поступает через вход устройства на буферный регистр 62, а также на группу входов дешифратора 65. Последний формирует управляющие сигналы, по которым информация, записанная в тринадцатом регистире 62, перезаписывается в соответствующие регистры или ячейки памяти блоков устройства. При загрузке в первый блок 2 оперативной памяти описания изображений кривой на счетчик 61 поступает сигнал управления с тринадцатого регистра 62. Четвертый счетчик 61 формирует адреса ячеек блока 2, Эти адреса являются номерами направлений, коды которых поступают в первый блок 2 оперативной памяти из регистра 62. Кроме кодов направлений в первый блок 2 оперативной памяти записываются значения граНиц окрашиваемых поверхностей, а также число повторов направления и маркер конца массива.

При загрузке второго блока 3 оперативной памяти информация из регистра 62 записывается в ячейки, адреса которых вырабатываются третьим счетчиком 60 кода номера кривой. Информация содержит код кривой и коды трансформации, Аналогично Проводится загрузка блока 4 оперативной Памяти цветности. При этом на его входы из регистра 62 поступает код кривой и ее цвет. В режиме формирования изображения выбор блоков 7 и 16 оперативной памяти, а также блока 14 преобразования координат для записи информации о смещении изображения производится дешифратором 64 блока 1 сопряжения. Счетчик 60 формирует порядковый номер кривой, подлежащей формированию, а счетчик 61 формирует порядковые номера направлений в списке- Кривых. При этом код номера кривой поступает на адресные входы блока 3, а код номера направления - на адресные входы блока 2. Счетчик 61 управляется сигналом, посту- Иающим из блока 17 управления. По окончании формирования кривой счетчик 61 сбрасывается в ноль сигналом конца массива, поступающим с формирователя 12 координат границ фрагмента. Этим же сигналом изменяется состояние счетчика 60, который формирует при этом код следующей кривой, Когда псе кривые сформированы, счетчик 60 формирует сигнал, который поступает по восьмому выходу блока 1 сопряжения на второй вход блока 17 управления, сбрасывая триггер Исполнить в нулевое состояние., 1

В режиме чтения дешифратор 64 согласно информации, записанной в регистре 62, формирует управляющий сигнал, поступающий на коммутатор 63, а также на фор- мирователь 15 импульсов. При этом последний переводится в режим чтения, а счетчик 61 формирует адреса ячеек памяти девятого блока 36 памяти.

Блок 17 управления предназначен для управления работой в режиме формирования изображения в одном из каналов. Он вырабатывает управляющие сигналы для работы блоков 9, 12, 1, 7, 16.

Исходными данными для работы блока 17 управления служит информация, записанная в регистрах 26 и 27, а также Информация, поступающая из вычислителя 9 приращений координат и формирователя 10 кода Фримена. Работа блока 17 синхронизируется синхросигналами с формирователя 13 координат развертки.

В режиме загрузки во второй регистр 27 записывается код команды, поступающий мз блока 1 сопряжения. Б регистр 27 записываются коды следующих команд, необходимых для формирования изображения; обращение к блокам 7 или 16 оперативной памяти; чтение (запись, очистка, формиро-. вание избирательно, сброс в начальное состояние).

0 Переход блока 17 управления в режим формирования изображения производится установкой пятого триггера 23 в состояние логической единицы.

Установка пятого триггера 23 происхо5 дит по сигналу, поступающему из блока 1 сопряжения. Пятый триггер 23 разрешает работу блока 17 управления сигналом, поступающим с его выхода на шестой блок 18 памяти. Этот же сигнал подается в блок 1

0 сопряжения, сигнализируя о готовности формирования изображения блоком 17 управления.

В режиме формирования изображения в первый регистр 26 записывается информа5 ция о числе повторов направления, которая поступает из первого блока 2 оперативной памяти. Запись происходит по сигналу, который вырабатывается блоком 2 оперативной памяти. Первый регистр 26 формирует

0 сигнал о том, что число повторов направления не равно нулю. Этот сигнал поступает в блок 18 памяти. При формировании изображения для блоков 7 и 16 оперативной памяти используется следующая информация 5 адреса, в качестве которых используются синхросигналы с распределителя 28 импульсов; код Фримена, поступающий из формирователя 10 кода Фримена; код команды; состояние первого 19 и четвертого

0 22 триггеров. Триггер 19 запоминает информацию о предыдущей зоне направления (значение кода Фримена), триггер 22 определяет состояние переноса, а триггер 20 - разрешение записи.

5 Распределитель 28 импульсов при помощи синхросигналов, поступающих из формирователя 13 координат развертки, вырабатывает сигналы, управляющие работой первого регистра 26, шестого блока 18 па0 мяти, второго регистра 20, а также сигналы, управляющие работой вычислителя 9 приращений координат и формирователя 12 координат границ фрагмента. Распределитель 28 импульсов управляется сигналами, кото5 рые считываются из шестого блока 18 памя: ти. Установка распределителя 28 импульсой в начальное состояние производится сигналом из формирователя 12. Этот сигнал устанавливает в начальное состояние первый счетчик 24.

Блок 17 управления работает следующим образом.

При формировании изображения на адресные входы шестого блока 18 памяти поступает код команды из регистра 27, сигнал из регистра 26 микрокоманд, признак переноса, поступающий из четвертого триггера 22, информация из триггера 19, код Фриме- на, поступающий из формирователя 10 кода Фримена, а также управляющие сигналы из распределителя 28 импульсов. В соответствии с кодом Фримена шестой блок 18 памяти определяет по записанной в нем таблице зону движения курсора и осуществляет переход курсора из одной зоны движения в другую согласно порядку изменения состояния счетчиков координат вычислителя 9 приращений координат. При этом шестой блок 18 памяти формирует сигналы изменения состояния счетчиков 59 координат. Старшие полубайты счетчиков 59 координат вычислителя 9 приращений координат указывают зону, в которую должна в данный момент записываться информация, т.е. на выходах счетчиков 59 формируются координаты символа (зоны), младшие полубайты указывают координаты записываемой точки в этом символе (зоне). Таким образом, старшие полубайты счетчиков 59 формируют адреса ячеек памяти четвертого блока 7 оперативной памяти, младшие полубайты - адреса ячеек пятого блока 16 оперативной памяти;

По адресам из четвертого блока 7 оперативной памяти считывается содержимое соответствующей ячейки памяти, которое представляет собой код символа. Содержимое ячейки памяти поступает на входы элемента И 31, который при поступлении на другой вход управляющего сигнала из шестого блока 18 памяти анализирует содержимое этой ячейки на ноль и при равенстве нулю формирует сигнал, устанавливающий триггер 21 в единицу. С выхода триггера 21 сигнал поступает в шестой блок 18 памяти, а также устанавливает триггер 20 в состояние, разрешающее запись. В соответствии с состоянием триггера 21 шестой блок 18 памяти выдает сигнал изменения содержи- мого счетчика 24. Содержимое последнего увеличивается на единицу. Шестой блок 18 памяти по сигналу, поступающему с выхода триггера 20, формирует сигнал, запрещающий работу распределителя 28 импульсов при записи. Кроме того, шестой блок 18 памяти формирует сигнал записи в четвертый блок 7 оперативной памяти. Код символа поступает в четвертый блок 7 оперативной памяти и записывается в нем по соответствующим адресам, При записи информации четвертый блок 7 оперативной памяти выдает сигнал сброса разрешения записи, который поступает через элемент ИЛИ 29 5 на триггер 20. По этому сигналу последний сбрасывается в ноль и шестой блок 18 памяти разрешает работу распределителя 28 импульсов. Этот сигнал сбрасывает также триггер 21 и триггер 22, который устанавли0 вается в единицу при переходе курсора из одной зоны знакоместа в другую. Сигналы перехода в другую зону формируются счетчиками 59 координат вычислителя 9 приращений координат и поступают на элемент

5 ИЛИ 30. Шестой блок 18 памяти переводит четвертый блок 7 оперативной памяти в режим чтения. При этом информация на группе выходов четвертого блока 7 оперативной памяти содержит код символа пятого блока

0 16 оперативной памяти, в котором записывается образующая, Запись информации в пятый блок 16 оперативной памяти происходит посредством блока 17 управления, при этом непрерывно контролируются перехо5 ды курсора из зоны одного знакоместа в другую зону. Контроль осуществляется элементом ИЛИ 30 и триггером 22, который устанавливается в единицу при переходе из одной зоны в другую. При этом меняется

0 содержимое старших полубайтов счетчиков 59 координат вычислителя 9 приращений координат, т.е. меняются адреса четвертого блока 7 оперативной памяти, Происходит анализ новой зоны знакоместа на ноль. Ес5 ли там уже записан код символа, то состояние счетчика 24 не изменяется, а формирование изображения в блоке 16 оперативной памяти производится через коммутатор 8 по коду символа, считываемого из

0 четвертого блока 7 оперативной памяти. При этом триггер 20 устанавливается сигналом с распределителя 28 импульсов, и шестой блок 18 памяти формирует сигнал разрешения записи в пятый блок 16 опера5 тивной памяти. Одновременно вырабатывается сигнал запрета работы распределителя 28 импупьсов. При записи пятый блок 16 оперативной памяти формирует сигнал сброса разрешения записи, который посту0 пает через элемент И 29 на триггер 20 и сбрасывает последний. Пятый блок 18 памяти, анализируя состояние триггера 20, разрешает дальнейшую работу распределителя 28 импульсов. После каждой записи в пятый

5 блок 16 оперативной памяти распределитель 28 импульсов формирует сигнал изменения содержимого регистра 26. При числе повторов, равном нулю, первый регистр 26 формирует сигнал, поступающий на вход шестого блока 18 памяти

Шестой блок 18 памяти вырабатывает сигналы, на основе которых распределитель 28 импульсов формирует сигнал управления вычислителем 9 приращений координат и формирователем 12 координат границ фраг- мента, а также сигнал изменения состояния счетчика 61 блока 1 сопряжения. Счетчик 61 формирует адреса первого блока 2 оперативной памяти, в котором записаны направления, описывающие кривую. После этого происходит считывание следующего направления.

В режиме регенерации распределитель 28 импульсов в соответствии с синхросигналами из формирователя 13 координат раз- вертки переключает блок 17 управления в режим регенерации, при,котором блок 17 управления запоминает свое состояние, не формируя никаких управляющих сигналов.

По окончании формирования кривой первый дешифратор 11 вырабатывает сигнал конца массива, поступающий через буферные регистры, формирователя 12 на вычислитель 9 приращений координат v, блок 17 управления, устанавливая их в на- чальное состояние, и в блок 1 сопряжения, изменяя содержимое счетчика 60, который формирует при этом номер следующей кривой, являющийся адресом второго блока 3 оперативной памяти.

После построения всех кривых блок 1 сопряжения вырабатывает сигнал, который сбрасывает триггер 23 в ноль. Триггер 23 формирует на своем выходе сигнал, запрещающий работу блока 17 управления и сиг- нализирующий о готовности устройства к формированию нового изображения. Этот сигнал поступает в блок 1 сопряжения. Таким образом, в четвертом блоке 7 оперативной памяти записывается конфигу рация из символов, информация о которых сформирована в пятом блоке 16 оперативной памяти.

Таким образом, изобретение обеспечивает повышение быстродействия за счет того, что по сравнению с известным устройством операция смещения фрагментов 1 изображения осуществляется не перепрограммированием конфигураций, а вычислением координат с учетом смещения в режиме регенерации.

Формула изобретения

Устройство для отображения информации на экране телевизионного индикатора, содержащее блок сопряжения, первый, вто рой, третий и четвертый блоки оперативной памяти, первый и второй коммутаторы, вычислитель приращений координат формирователь кодов Фримена, первый дешифратор, первый и второй выходы блока

сопряжения подключены соответственно к управляющему и информационному входам первого блока оперативной памяти, адресный вход которого соединен с первым выходом второго блока оперативной памяти, управляющий и информационный входы которого подключены соответственно к третьему и четвертому выходам блока сопряжения, первый выход первого блока оперативной памяти соединен с информационным входом первого дешифратора и с первым информационным входом вычислителя приращений координат, второй информационный вход которого подключен к второму выходу второго блока оперативной памяти, первый выход вычислителя приращений координат соединен с входом формирователя кодов Фримена, второй выход вычислителя приращений координат подключен к первому информационному входу втрого коммутатора, пятый и шестой выходы блока сопряжения соединены соответственно с управляющим и информационным входами третьего блока оперативной памяти, выход которого подключен к видеовходам телевизионного индикатора, вход-выход блока сопряжения является входом-выходом устройства, отличающееся тем, что. с целью повышения быстродействия устройства, оно содержит блок управления, формирователь координат границ фрагмента, пятый блок оперативной памяти, формирователь импульсов, блок преобразования координат, формирователь координат развертки, выход которого соединен с управляющим входом первого коммутатора, первым информационным входом блока преобразования координат, первым информационным входом блока управления, первым адресным входом четвертого блока оперативной памяти, управляющим входом второго коммутатора, синхровходом телевизионного .индикатора, синхровходом формирователя импульсов и первым адресным входом пято- гго блока оперативной памяти, второй адресный вход которого подключен к выходу второго коммутатора, второй информационный вход которого и второй информационный вход блока управления соединены с первым выходом четвертого блока оперативной памяти, второй выход которого подключен к третьему информационному входу второго коммутатора, четвертый информационный вход которого и первый информационный вход пе рвого коммутатора подключены к первому выходу блока преобразования координат, второй выход которого соединен с третьим адресным входом пятого блока оперативной памяти, четвертый адресный вход которого, второй адресный вход четвертого блока оперативной памяти и бторой информационный вход блока преобразования координат подключены к седьмому выходу блока сопряжения, вось- мой выход которого соединен с управляющим входом блока преобразования координат, третий информационный вход которого, информационный вход пятого блока оперативной памяти и третий ин- формационный вход блока управления подключены к девятому выходу блока сопряжения, десятый выход которого соединен с входом запуска блока управления, первый выход которого подключен к входу управлению записью блока сопряжения, вход управления чтением которого и вход управления чтением блока управления и первый управляющий вход вычислителя приращений координат подключены к пер- вому выходу формирователя координат границ фрагментов, второй выход которого соединен с пятым адресным входом пятого блока оперативной памяти, первый управляющий вход которого подключен к второму выходу блока управления, тактовый вход которого соединен с первым выходом пятого блока оперативной памяти, второй выход которого соединен с адресным входом третьего блока оперативной памяти, пер- вый выход формирователя импульсов подключен к шестому адресному входу пятого блока оперативной памяти, третий выход которого соединен с первым информационным входом формирователя импульсов, вто- рые информационный и управляющий входы которого подключены соответственно к одиннадцатому и двенадцатому выходам блока сопряжения, тринадцатый выход которого соединен с вторым управляющим

входом пятого блока оперативной памяти,, первый информационный вход блока сопряжения подключен к второму аыходу формирователя импульсов, тактовый вход блока сопряжения соединен с третьим выходом блока управления, четвертый и пятый выходы которого подключены соответственно к информационному и управляющему входам четвертого блока оперативной памяти, третий адресный вход которого соединен с выходом первого коммутатора, второй информационный вход которого подключен к второму выходу вычислителя приращений координат, третий выход которого соединен с четвертым информационным входом блока управления, шестой выход которого соединен с третьим информационным входом вычислителя приращений координат, четвертый выход которого подключен к первому информационному, входу формирователя координат границ фрагмента, второй информационный вход которого соединен с третьим выходом второго блока оперативной памяти, выход первого дешифратора со- единен с входом управления чтением формирователя координат границ фрагмента, третий информационный вход которого подключен к первому выходу первого блока оперативной памяти, второй и третий выходы которого соединены соответственно с пятым информационным входом и синхров- ходом блока управления, седьмой выход которого подключен к второму управляющему входу вычислителя приращений координат и тактовому входу формирователя коордит нат границ фрагмента, третий аыход четвертого блока оперативной памяти соединен с входом сброса блока управления, шестой информационный вход которого подключен к выходу формирователя кодов Фримена,

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1983 |

|

SU1193722A1 |

| Устройство для отображения информации | 1985 |

|

SU1354183A1 |

| Устройство для отображения информации | 1987 |

|

SU1513439A1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1990 |

|

SU1718265A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| Генератор символов | 1987 |

|

SU1550572A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1539825A1 |

| Устройство для формирования изображения | 1988 |

|

SU1575230A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Устройство для формирования информации на телевизионном индикаторе | 1981 |

|

SU1075298A1 |

Изобретение относится к вычислительной технике и может быть использовано для отображения информации о ходе технологических процессов и при отображении многоплановых изображений. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок 1 сопряжения, первый 2, второй 3, третий 4, четвертый 7 и пятый 16 блоки оперативной памяти, телевизионный индикатор 5, первый б и второй 8 коммутаторы, вычислитель 9приращений координат, формирователь 10кодов Фримена, первый дешифратор 11, формирователь 12 координат границ фрагмента, формирователь 13 координат развертки, блок 14 преобразования координат, формирователь 15 импульсов, блок 17 управления с соответствующими связями . Информация об изображении через бл-о-к 1 сопряжения записывается в

Фиг f

Авторы

Даты

1991-11-30—Публикация

1986-12-11—Подача