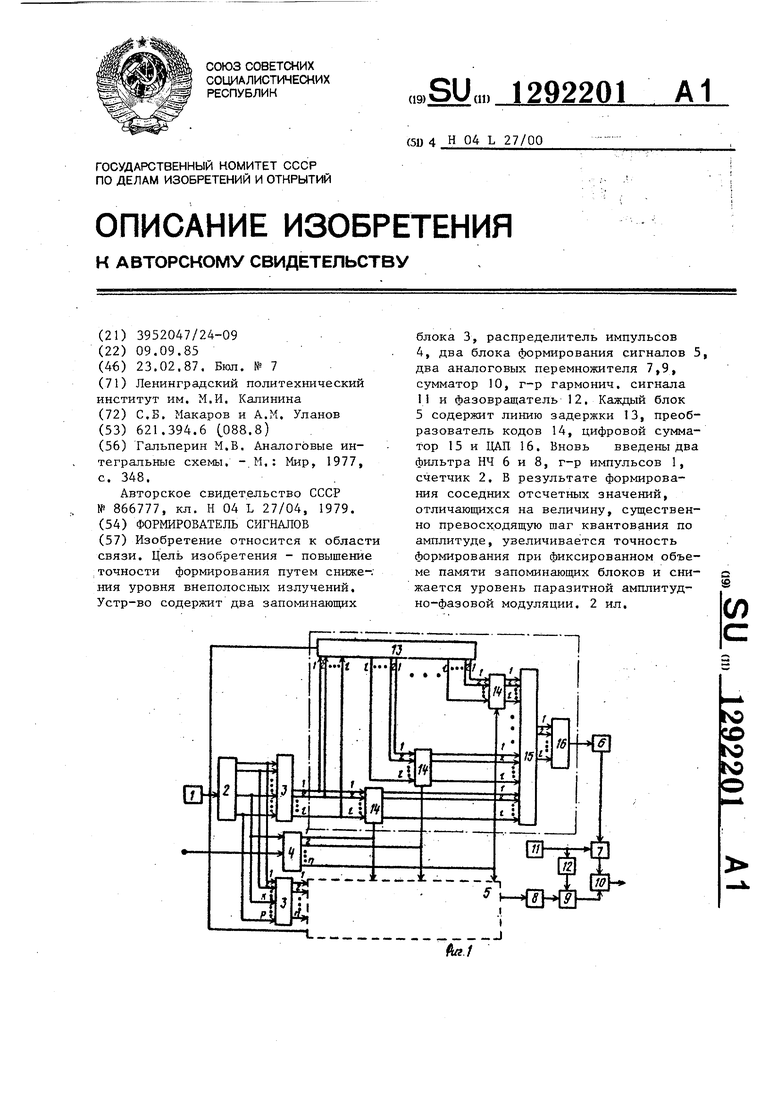

Изобретение относится к области связи и может найти применение в высокоскоростных системах связи для формирования сигналов, перекрывающихся во времени, имейщих ограниченный спектр частот и малые уровни внеполосных излучений.

Целью изобретения является повышение точности формирования путем снижения уровня внеполосных излучений.

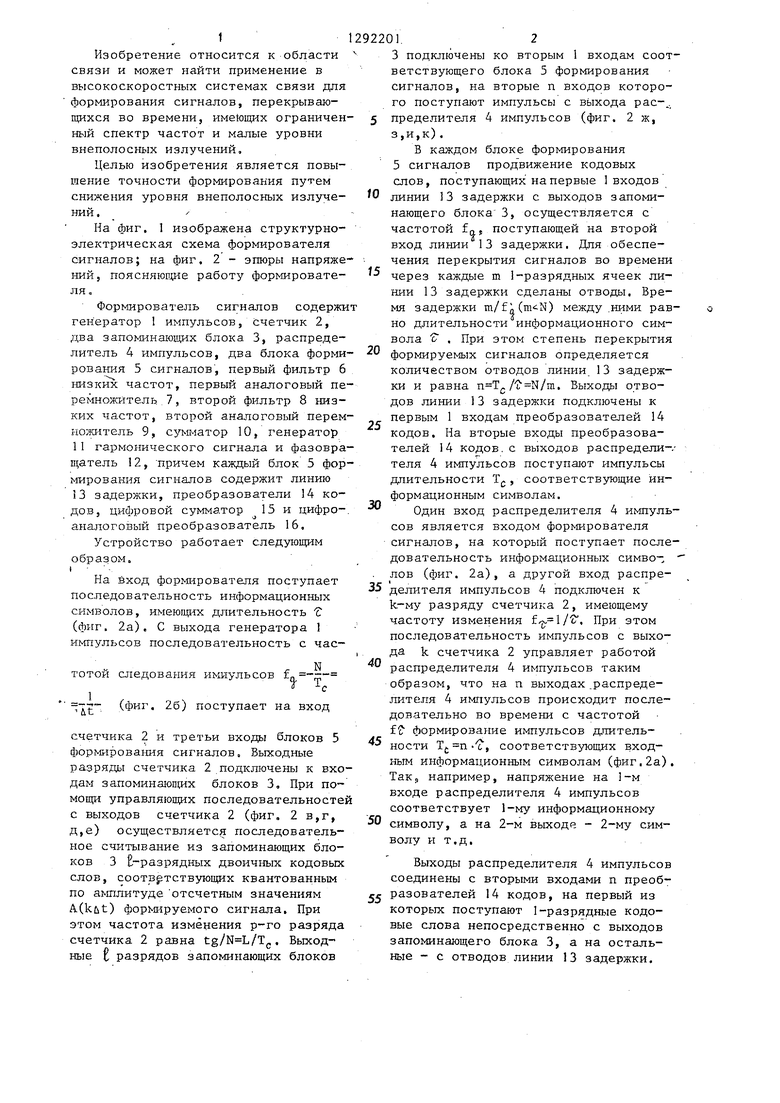

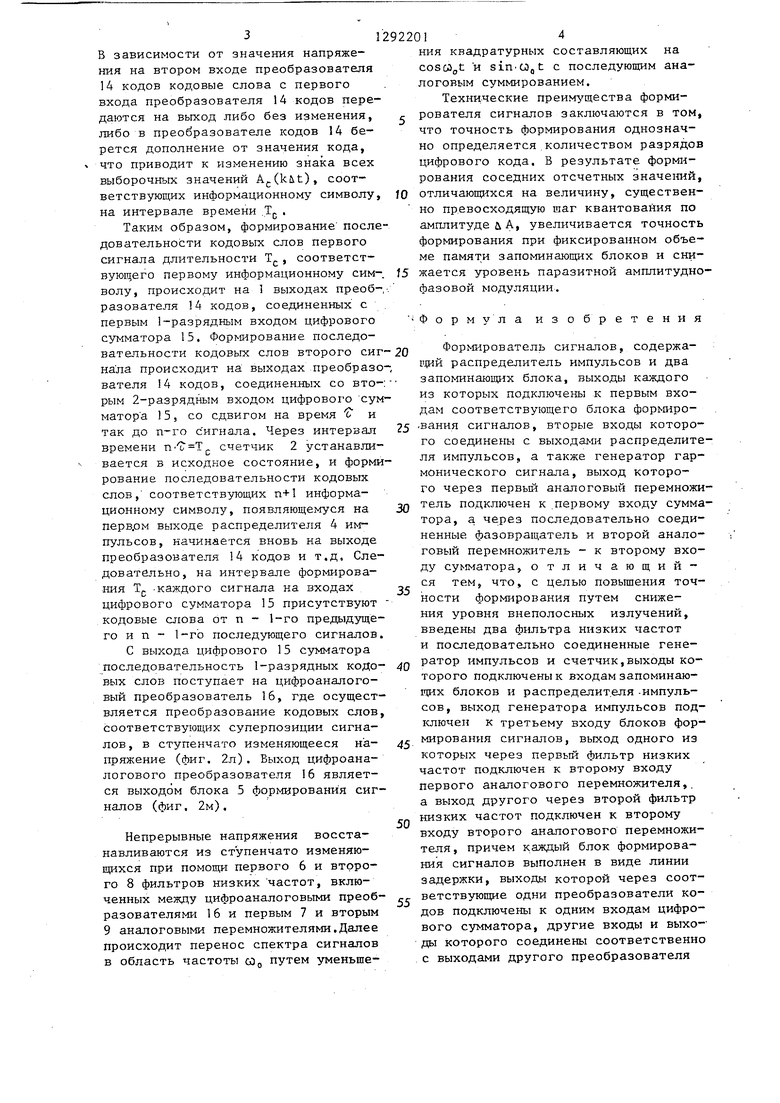

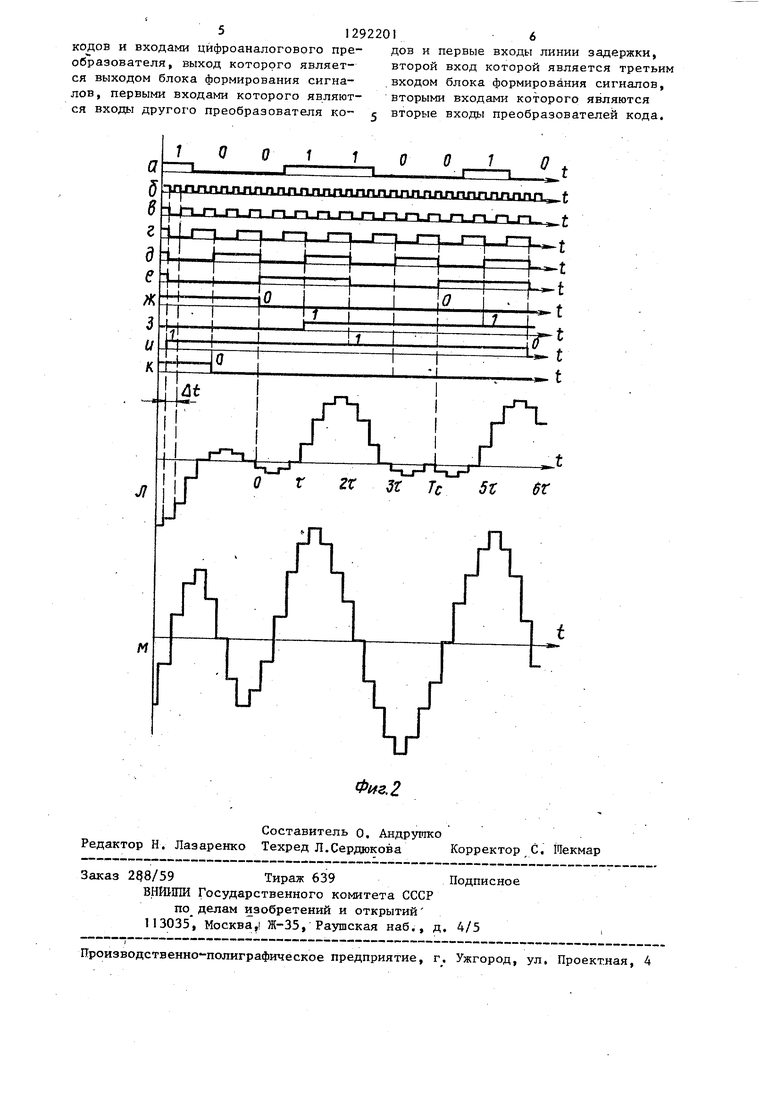

На фиг. 1 изображена структурно- электрическая схема формирователя сигналов; на фиг. 2 - эпюры напряже- НИИ, поясняющие работу формировате- ля,

Формирователь сигналов содержи ген ератор 1 импульсов, счетчик 2, два запоминающих блока 3, распределитель 4 импульсов, два блока формирования 5 сигналов, первый фильтр 6 низких частот, первый аналоговый пе- ремножйтель.7, второй фильтр 8 низких частот, второй аналоговый перем- нолштель 9, сумматор 10, генератор 11 гармонического сигнала и фазовращатель 12, Причем каждый блок 5 формирования сигналов содержит линию 13 задержки, преобразователи 14 кодов, цифровой сумматор 15 и цифро-. аналоговый преобразователь 16.

Устройство работает следующим

образом. I - .

На вход форм11рователя поступает последовательность информационных символов, длительность Т (фиг. 2а), С выхода генератора 1 импульсов последовательность с час-

N

тотой следования имиульсов „- Т с

f7 (фиг, 26) поступает на вход

счетчика 2 и третьи входы блоков 5 формирования сигналов, Выходные разряды счетчика 2 подключены к входам запоминающих блоков 3, При помощи управляющих последовательносте с выходов счетчика 2 (фиг, 2 в,г, д,е) осуществляется последовательное считывание из запоминающих блоков 3 Е-разрядных двоичных кодовых слов, соответствующих квантованным по a mлитyдe отсчетным значениям A() формируемого сигнала. При этом частота изменения р-го разряда счетчика 2 равна , Выходные разрядов запоминающих блоков

0

0

5

0

5

0

5

0

5

3 подключены ко вторым 1 входам соответствующего блока 5 формирования сигналов, на вторые п входов которого поступают импульсы с выхода рас-. пределителя 4 импульсов (фиг. 2 ж, з,и,к).

В каждом блоке формирования 5 сигналов продвижение кодовых слов, поступающих на первые 1 входов линии 13 задержки с выходов запоминающего блока 3, осуществляется с частотой fns поступающей на второй вход линии 13 задержки. Для обеспечения перекрытия сигналов во времени через каждые m 1-разрядных ячеек линии 13 задержки сделаны отводы. Время задержки m/fo(nKN) между .ними равно длительности информационного символа о , При этом степень перекрытия формируемых сигналов определяется количеством отводов линии 13 задержки и равна (N/m. Выходы отводов линии 13 задержки подключены к первым 1 входам преобразователей 14 кодов. На вторые входы преобразователей 14 кодов, с выходов распредели-. теля 4 импульсов поступают импульсы длительности Т., соответствующие информационным символам.

Один вход распределителя 4 импульсов является входом формирователя сигналов, на который поступает последовательность информационных симво-, лов (фиг. 2а), а другой вход распределителя импульсов 4 подключен к k-му разряду счетчика 2, имеющему частоту изменения f l/ C . При этом последовательность импульсов с выхода k счетчика 2 управляет работой распределителя 4 импульсов таким образом, что на п выходах .распределителя 4 импульсов происходит последовательно во времени с частотой f формирование импульсов длительности Т(,П б , соответствующих входным информационным символам (фиг.2а). Так5 например, напряжение на 1-м входе распределителя 4 импульсов соответствует 1-му информационному символу, а на 2-м выходе - 2-му символу и т.д..

Выходы распределителя 4 импульсов соединены с вторыми входами п преобразователей 14 кодов, на первый из которых поступают 1-разрядные кодовые слова непосредственно с выходов запоминающего блока 3, а на остальные - с отводов линии 13 задержки.

в зависимости от значения напряжения на втором входе преобразователя 14 кодов кодовые слова с первого входа преобразователя 14 кодов передаются на выход либо без изменения, либо в преобразователе кодов 14 берется дополнение от значения кода, что приводит к изменению знака всех выборочных значений A.(ktit}, соответствующих информационному символу, на интервале времени .Т(. .

Таким образом, формирование последовательности кодовых слов первого сигнала длительности Т. , соответствуюпдего первому информационному сим-, волу, происходит на 1 выходах преоб-,-. разователя 14 кодов, соединенных с первым 1-разрядным входом цифрового сумматора 15. Формирование последовательности кодовых слов второго сиг- 20 нала происходит на выходах преобразо-, вателя 14 кодов, соединенных со вто-: рым 2-разряднь1м входом цифрового сумматора 15, со сдвигом на время о и так до с игнала. Через интервал

f5

25

времени П о Т, счетчик 2 устанавливается в исходное состояние, и формирование последовательности кодовых слов, соответствующих п+1 информационному символу, появляющемуся на перв.ом выходе распределителя 4 импульсов, начинается вновь на выходе преобразователя 14 кодов и т.д. Следовательно, на интервале формирования Tj. -каждого сигнала на входах цифрового сумматора 15 присутствуют кодовые слова от п - 1-го предыдущего и п - 1-гЬ последующего сигналов

С выхода цифрового 15 сумматора последовательность 1-разрядных кодовых слов поступает на цифроаналого- вый преобразователь 16, где осуществляется преобразование кодовых слов соответствующих суперпозиции сигналов , в ступенчато изменяющееся напряжение (фиг. 2л). Выход цифроана- логового преобразователя 16 является выходом блока 5 формирования сигналов (фиг. 2м).

Непрерывные напряжения восстанавливаются из ступенчато изменяющихся при помощи первого 6 и второго 8 фильтров низких частот, включенных между цифроаналоговыми преоб- разователями 16 и первым 7 и вторым 9 аналоговыми перемножителямн.Далее происходит перенос спектра сигналов в область частоты сОп путем уменьше

20 922014

ния квадратурных составляющих на cosWgt и sin Qjt с последующим аналоговым суммированием.

Технические преим щества формирователя сигналов заключаются в том, что точность формирования однозначно определяется количеством разрядов цифрового кода. В результате формирования соседних отсчетных значе1шй, отличающихся на величину, существенно превосходящую шаг квантования по амплитудеUА, увеличивается точность формирования при фиксированном объеме памят и запоминающих блоков и снижается уровень паразитной амплитудно- фазовой модуляции.

10

f5

Форм у л а изобретения

0

0

5

0

0

5

Формирователь сигналов, содержа- ид2й распределитель импульсов и два запоминающих блока, выходы каждого из которых подключены к первым входам соответствующего блока формиро- 5 -вания сигналов, вторые входы которого соединены с выходами распределителя импульсов, а также генератор гармонического сигнала, выход которого через первый аналоговый перемножитель подключен к .первому входу сумматора, а через последовательно соединенные фазовращатель и второй аналоговый перемножитель - к второму входу сумматора, отличающий- ся тем, что, с целью повыщения точности формирования путем снижения уровня внеполосных излучений, введены два фильтра низких частот и последовательно соединенные генератор импульсов и счетчик,выходы которого подключены к входам запоминающих блоков и распределит.еля -импульсов, выход генератора импульсов подключен к третьему входу блоков формирования сигналов, выход одного из которых через первый фильтр низких частот подключен к второму входу первого аналогового перемножителя,, а выход другого через второй фильтр низких частот подключен к второму входу второго аналогового перемножителя , причем к;аждый блок формирования сигналов выполнен в виде линии задержки, выходы которой через соответствующие одни преобразователи кодов подключены к одним входам цифрового сумматора, другие входы и выходы которого соединены соответственно с выходами другого преобразователя

кодов и входами цйфроаналогового преобразователя, выход которого является выходом блока формирования сигналов , первыми входами которого являются входы другого преобразователя кодов и первые входы линии задержки, второй вход которой является третьим входом блока формирования сигналов, вторыми входами которого являются вторые входы преобразователей кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов | 1988 |

|

SU1598198A2 |

| Способ формирования сигналов с расширенным спектром | 2018 |

|

RU2699817C1 |

| Способ формирования сигналов с расширенным спектром | 2018 |

|

RU2699818C1 |

| Способ расширения спектра сигналов | 2018 |

|

RU2699816C1 |

| Способ расширения спектра сигналов | 2019 |

|

RU2714300C1 |

| Способ формирования сигналов с расширенным спектром | 2018 |

|

RU2699819C1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396721C1 |

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

Изобретение относится к области связи. Цель изобретения - повышение точности формирования путем сниже-: ния уровня внеполосных излучений. Устр-во содержит два запоминающих блока 3, распределитель импульсов 4, два блока формирования сигналов 5, два аналоговых перемножителя 7,9, сумматор 10, I-р гармонич. сигнала П и фазовращатель 12. Каждый блок 5 содержит линию задержки 13, преобразователь кодов 14, цифровой сумматор 15 и ЦАП 16. Вновь введены два фильтра НЧ 6 и 8, г-р импульсов 1, счетчик 2. В результате формирования соседних отсчетных значений, отличающихся на величину, существенно превосходящую шаг квантования по амплитуде, увеличивается точность формирования при фиксированном объеме памяти запоминающих блоков и снижается уровень паразитной амплитудно-фазовой модуляции. 2 ил. (Л

Составитель 0. Андрутко Редактор Н. Лаэаренко Техред Л.Сердюкова Корректор С. Шекмар

Заказ 238/59 Тираж 639Подписное

ВНЙИПЙ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5i

.

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Ф14г,2

| Гальперин М.В | |||

| Аналоговые интегральные схемы | |||

| -.М.: Мир, 1977, с | |||

| Телефонная трансляция с местной цепью для уничтожения обратного действия микрофона | 1924 |

|

SU348A1 |

| Устройство для цифроаналогового формирования однополосных сигналов с амплитудно-фазовой модуляцией | 1979 |

|

SU866777A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-02-23—Публикация

1985-09-09—Подача