112

Изобретение относится к вычислительной технике и может быть использовано для контроля пакетных t кодов.

Цель изобретения повышение дос- товерности контроля.

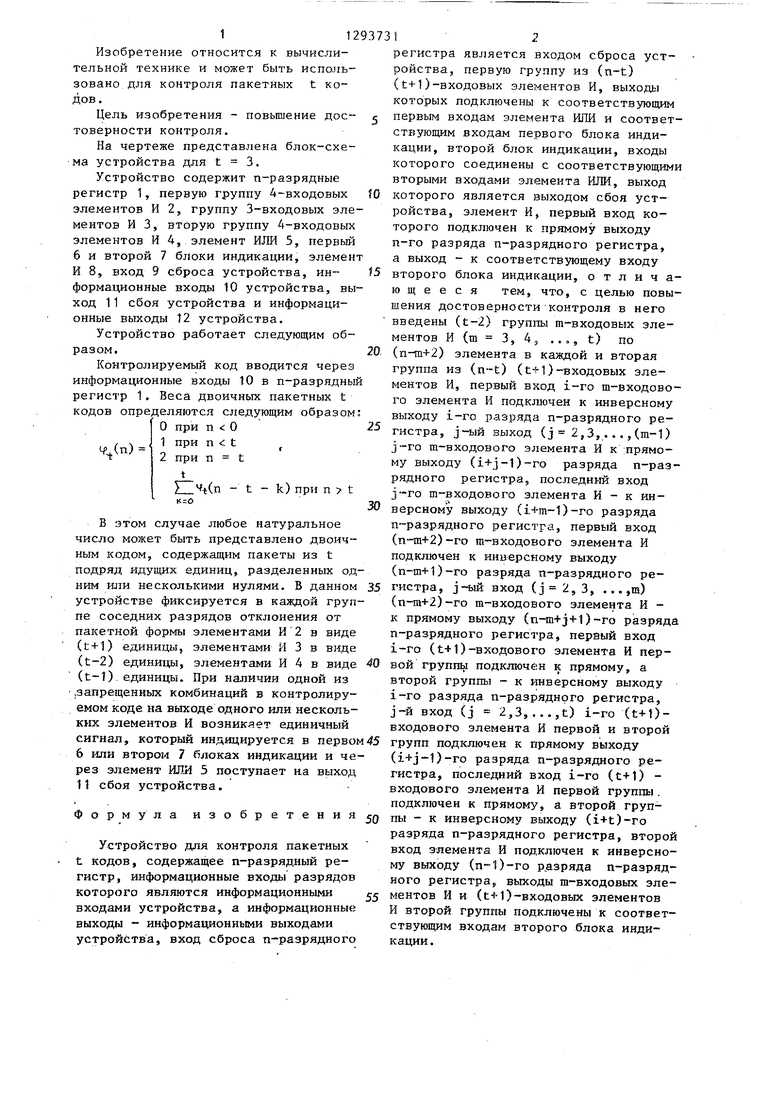

На чертеже представлена блок-схема устройства для t 3,

Устройство содержит п-разрядные регистр 1, первую группу 4-входовых элементов И 2, группу 3-входовых элементов И 3, вторую группу 4-входовых элементов И 4, элемент ИЛИ 5, первый 6 и второй 7 блоки индикации, элемент И 8, вход 9 сброса устройства, ин- формационные входы 10 устройства, выход 11 сбоя устройства и информационные выходы 12 устройства.

Устройство работает следующим образом.

Контролируемый код вводится через информационные входы 10 в п-разрядный регистр 1. Веса двоичных пакетных t кодов определяются следующим образом

0при п О

1при п t

2при п t

t - t - k) при п t

Ч (п)

В этом случае любое натуральное число может быть представлено двоичным кодом, содержащим пакеты из t подряд идущих единиц, разделенных одним или несколькими нулями. В данном устройстве фиксируется в каждой группе соседних разрядов отклонения от пакетной формы элементами И 2 в виде (t+1) единицы, элементами И 3 в виде (t-2) единицы, элементами И 4 в виде (t-t). единицы. При наличии одной из Запрещенных комбинаций в контролируемом коде на выходе одного или нескольких элементов И возникает единичный сигнал, который индицируется в первом 6 или втором 7 блоках индикации и через элемент ИЛИ 5 поступает на выход 11 сбоя устройства.

Формула изобретения

Устройство для контроля пакетных t кодов, содержащее п-разрядный регистр, информационные входы разрядов которого являются информационными входами устройства, а информационные выходы - информационными выходами устройства, вход сброса п-разрядного

0 5

0

5

0

5 О 5

0

55

12

регистра является входом сброса устройства, первую группу из (n-t) (t+1)-вxoдoвыx элементов И, выходы которых подключены к соответствующим первым входам элемента ИЛИ и соответствующим входам первого блока индикации, второй блок индикации, входы которого соединены с соответствующими вторыми входами элемента ИЛИ, выход которого является выходом сбоя устройства, элемент И, первый вход которого подключен к прямому выходу п-го разряда п-разрядного регистра, а выход - к соответствующему входу второго блока индикации, отличающееся тем, что, с целью повышения достоверности контроля в него введены (t-2) группы ш-входовых элементов И (т 3, 4, ..., t) по (n-m-J-2) элемента в каждой и вторая группа из (n-t) (t-«1)-вxoдoвыx элементов И, первый вход i-ro m-входово- го элемента И подключен к инверсному выходу i-ro разряда п-разрядного регистра, j-ый выход (J 2,3,..,,(т-1) j-ro m-входового элемента И к :прямо- му выходу (i+j-1)-ro разряда п-разрядного регистра, последний вход J-го т-входового элемента И - к инверсному выходу (i+m-1)-ro разряда П разрядного регистра, первый вход ()-го т-входового элемента И подключен к инверсному выходу (п-т+1)-го разряда п-разрядного регистра, -ы& вход (,3, .., ,m) (n-m+2)-ro m-входового элемента И - к прямому выходу (n-m+j+1)-ro разряда п-разрядного регистра, первый вход i-ro (t+1)-входового элемента И первой группь: подключен к прямому, а второй группы - к инверсному выходу i-ro разряда п-разряднрго регистра, j-й вход (j 2,3,...,t) i-ro (t+1)- входового элемента И первой и второй групп подключен к прямому выходу (i+j-1)-ro разряда п-разрядного регистра, последний вход i-ro (t+1) - входового элемента И первой группы . подключен к прямому, а второй группы - к инверсному выходу (i+t)-ro разряда п-разрядного регистра, второй вход элемента И подключен к инверсному выходу ()-го разряда п-разрядного регистра,, выходы т-входовых элементов И и (ь+1)-входовых элементов И второй группы подключены к соответствующим входам второго блока индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля пакетно-оптимальных @ - кодов | 1985 |

|

SU1337899A1 |

| Устройство для сравнения мN-разрядных чисел | 1980 |

|

SU920702A1 |

| Устройство для контроля оптимальных @ -кодов Фибоначчи | 1983 |

|

SU1149261A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Устройство для выделения экстремального из -разрядных двоичных чисел | 1978 |

|

SU752326A1 |

| Устройство для определения максимального из т двоичных чисел | 1980 |

|

SU875376A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2012 |

|

RU2480823C1 |

| Устройство для выделения экстремального из @ чисел | 1981 |

|

SU1005030A1 |

Изобретение относится к вычислительной технике. Изобретение позволяет повысить достоверность пакетных t кодов. Устройство содержит п-раз- рядный регистр 1, злементы И 2, 3, 4, 8, элемент ИЛИ 5, блоки 6 и 7 индикации. 1 ил. 11 S (Л &0 vi 00

| Устройство для контроля р-кодовфибОНАччи | 1979 |

|

SU817718A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля оптимальных @ -кодов Фибоначчи | 1983 |

|

SU1149261A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-28—Публикация

1985-02-28—Подача