. Г Изобретение относится к вычислительной технике и может быть использовано для котроля р кодов Фибоначчи.

Наиболее близким к предлагаемому является устройство для контроля р-го кода Фибоначчи,содержащее п-раарядлный регистр, первый элемент ИЛИ, (п-р).блоков фиксации сбоев, каждый ИЗ которых содержит первый злемент И, злемент ИЛИ, выход которого соединен с первым входом первого элемента И, первый вход блока фиксации сбоев соединен со вторым входом первого элемента И, выход которого соединен с первым вьЬсодсм блока фиксации сбоев, второй и третий входы блока фиксации сбоев соединены соответственно с первым и вторым входеат элемента ИЛИ, первые выходы всех блоков фиксации сбоев - с соответству,щими входами первого элемента ИЛИ, выход которого является выход ж устройства, выход каждого i-го триггера соединен с первым входом соответствующего (i-p)-ro блока фиксации сбоев, совторым входом (l-p+D-ro блока фиксации сбоев и с третьим входом (i-p+2)-ro блока фиксации сбоев, установочный вход устройства с первым входом всех триггеров п-разрядного регистра, информационный вход триггера старшего разряда регистра со входом устройства fl.

Недостаток известного устройства невозможность обнаружения ошибок, вызывающих переход триггера из едииичного состояния в нулевое (типа

1 в 0).

o

изобретения - увеличение эффективности контроля путем фиксации ошибок типа переходов 1 в О. Поставленная цель достигается тем, что устройство для контроля р кояов Фибоиаччи, содержащее п разрядный триггерный регистр, злемент ИЛИ, (п-р) блоков фиксации сбоев, каждый из которых содержит первый элемент И, элемент ИЛИ, выход кото6рого соединен с первьм входом первого элемента И, первый вход блока фиксации сбоев соединен со вторь входом первого элемента И, выход которого соединен с первым выходом блока фиксации сбоев, второй и третий входи блока фиксации сбоев соединены соответственно с первым и вторым входами элемента ИЛИ, первые выходы всех блоков фиксации сбоев - с соответствуювщми входами элемента ИЛИ, выход

которого является выходом устройства/ выход каждого i-ro триггера регистра соединен с первым входом соответствующего (i -р)-го блока фиксации сбоев со вторымвходом {i-p+l)-ro блока фиксации сбоев и с третьим входом (i -р4-2)-го блока фиксации сбоев, установочный вход устройства - .с первым входом всех триггеров регистра, информационный вход триггера старшего разряда регистра - со входом устройства, дополнительно содержит группу из Чп-р+1) элементов ИЛИ, первый вход каждого элемента ИЛИ группы является соответствующим информационным входом устройства,вто рой выход каждого i-ro блока фиксации сбоев соединен со вторым входом {|-1)-го и третьим входом (i-2)-ro элементов ИЛИ группы, выход каждого элемента ИЛИ группы - с информационным входом соответствующего триггера регистра, управлякядий вход устройства - с управляющим входом каждого блока фиксации сбоев, выходы младших разрядов регистра - с соответствующими входами элемента ИЛИ, а каждый блок фиксации сбоев дополнительно содержит формирователь импульсов и дополнительный элемент И, выход которого является вторым выходом блока фиксации сбоев, первый вход блока фисации сбоев соединен со входом формирователя импульсов, выход которого соединен с первым входом дополнительного элемента И, второй вход которого соединен с управляющим входом блока фиксации сбоев.

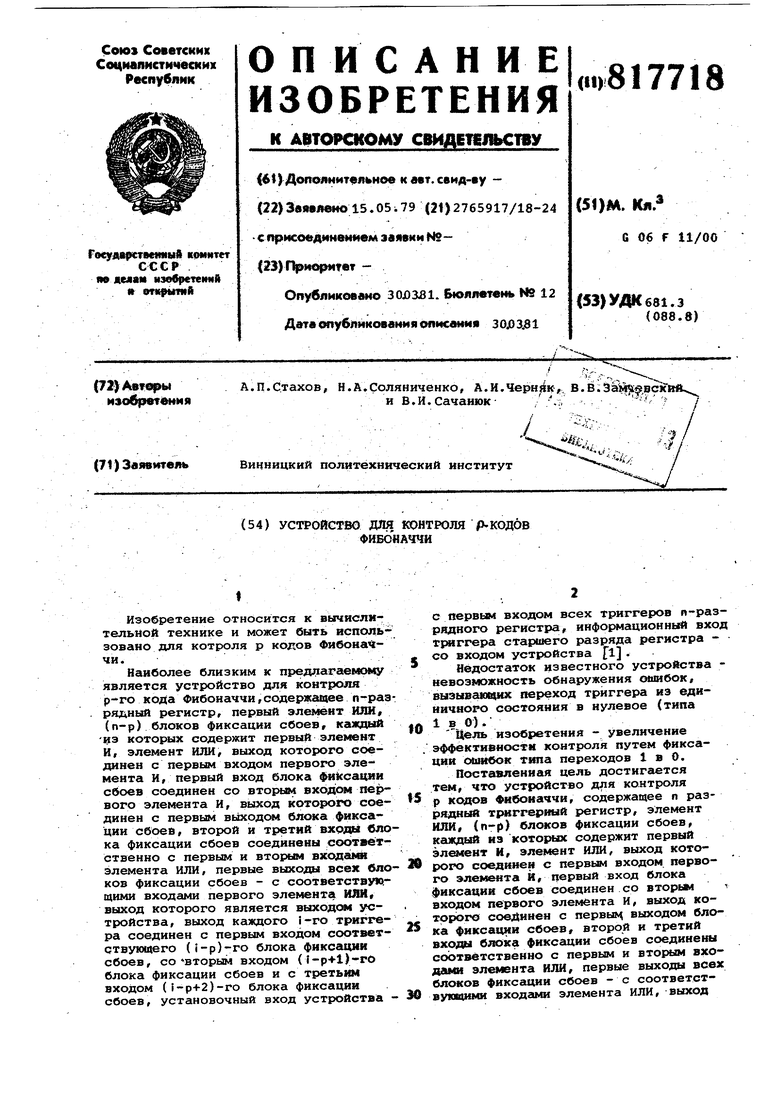

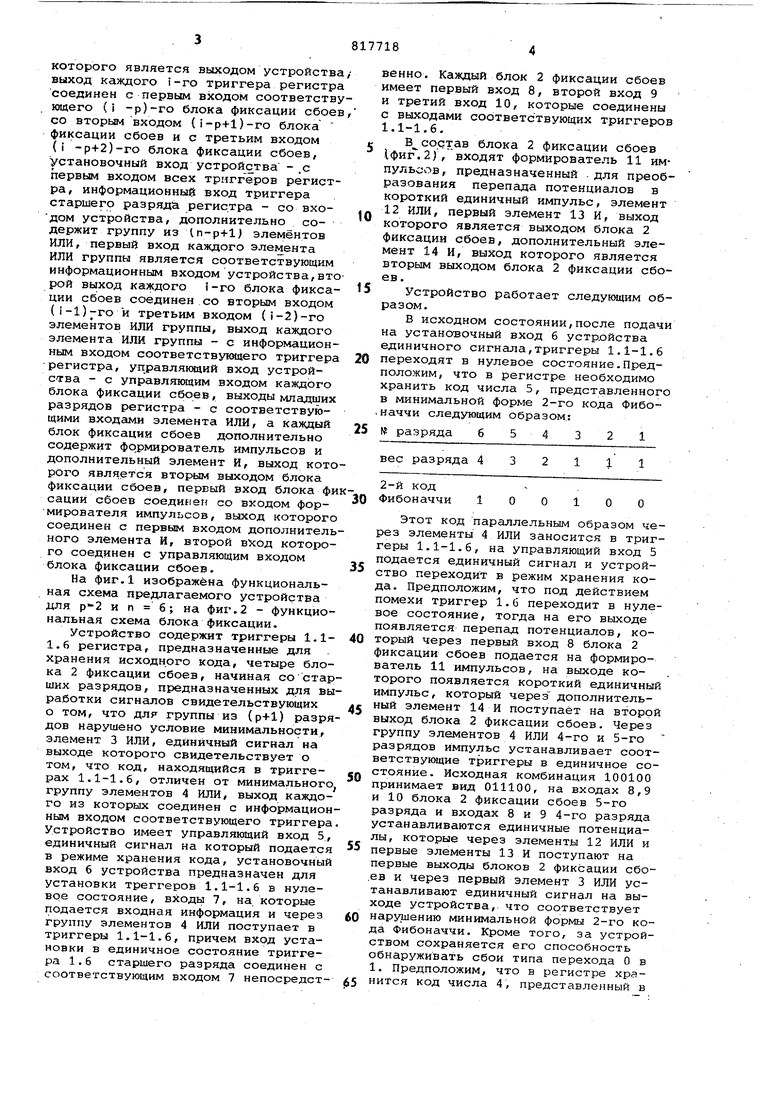

На фиг.1 изображена функциональная схема предлагаемого устройства для р-2 и п 6; на фиг.2 - функциональная схема блока фиксации.

Устройство содержит триггеры 1.11.6 регистра, предназначенные для хранения исходного кода, четыре блока 2 фиксации сбоев, начиная со старших разрядов, предназначенных для выработки сигналов свидетельствующих о том, что для группы из (р+1) разрядов нарушено условие минимальности, элемент 3 ИЛИ, единичный сигнал на выходе которого свидетельствует о том, что код, находящийся в триггерах 1.1-1.6, отличен от минимального группу элементов 4 ИЛИ, выход каждого из которых соединен с информационным входом соответствующего триггера Устройство имеет управлякиций вход 5, единичный сигнал на который подается в режиме хранения кода, установочный вход 6 устройства предназначен для установки треггеров 1.1-1.6 в нулевое состояние, входы 7, на которые подается входная информация и через группу элементов 4 ИЛИ поступает в триггеры 1.1-1.6, причем вход установки в единичное состояние триггера 1.6 старшего разряда соединен с соответствующим входом 7 непосредственно. Каждый блок 2 фиксации сбоев имеет первый вход 8, второй вход 9 и третий вход 10, которые соединены с выходами соответствующих триггеров 1.1-1.6.

t В состав блока 2 фиксации сбоев 1ФИГ.2У, входят формирователь 11 импульсов, предназначенный -для преобразования перепада потенциалов в короткий единичный импульс, элемент 12 ИЛИ, первый элемент 13 И, выход которого является выходом блока 2 фиксации сбоев, дополнительный элемент 14 И, выход которого является вторым выходом блока 2 фиксации сбоев.

5 Устройство работает следующим образом.

В исходном состоянии,после подачи на установочный вход 6 устройства единичного сигнала,триггеры 1.1-1.6 0 переходят в нулевое состояние.Предположим, что в регистре необходимо хранить код числа 5, представленного в минимальной форме 2-го кода Фибо.наччи следующим образом:

5 № разряда 6 54 3 2 1

вес разряда 4

2-й код

О О 30 Фибоначчи 1

О О

Этот код параллельным образом через элементы 4 ИЛИ заносится в триггеры 1.1-1.6, на управляющий вход 5 подается единичный сигнал и устройство переходит в режим хранения кода. Предположим, что под действием помехи триггер 1.б переходит в нулевое состояние, тогда на его выходе появляется перепад потенциалов, который через первый вход 8 блока 2 фиксации сбоев подается на формирователь 11 импульсов, на выходе которого появляется короткий единичный импульс, который через дополнительf ный элемент 14 И поступает на второй выход блока 2 фиксации сбоев. Через группу элементов 4 ИЛИ 4-го и 5-го разрядов импульс устанавливает соответствукнцие триггеры в единичное состояние. Исходная комбинация 100100

принимает вид 011100, на входах 8,9 и 10 блока 2 фиксации сбоев 5-го разряда и входах 8 и 9 4-го разряда устанавливаются единичные потенциалы, которые через элементы 12 ИЛИ и

первые элементы 13 И поступают на первые выходы блоков 2 фиксации сбоев и через первый элемент 3 ИЛИ устанавливают единичный сигнал на выходе устройства, что соответствует

нарушению минимальной формы 2-го кода Фибоначчи. Кроме того, за устройством сохраняется его способность обнаруживать сбои типа перехода О в 1. Предположим, что в регистре хранится код числа 4, представленный в минимальной форме 2-го кода Фибона чи следующим образом: разряда 65 4 3 2 1 Если под действием помехи триггер 1.5 переходит в единичное сост яние и код принимает вид 110000, тогда на его выходе появляется пол жительный потенциал, который через вход 9 блока 2 фиксации сбоев шест го разряда поступает на вкод элеме та 12 ИЛИ. Вместе с единичным поте циалом, поступившим с триггера 1.6 на первый вход 8 блока 2 фиксации сбоев этого разряда, они вызывают появление единичного потенциала на выходе первого элемента И 13. Этот потенциал через первый элемент 3 .И появляется на контрольном выходе устройства, что свидетельствует о нарушении минимальной формы предст ления хранимого числа. Однако если под действием помех в единичное состояние переходит не триггер l.Sj а триггер 1.3 и храни мый в регистре код принимает вид чТо единичный потенциал с прямого ин формационного выхода триггера 1.3 поступает на входы 8,9 и 10 соответ ствующих блоков 2 фиксации сбоев. Это не вызывает появления единичного сигнала на выходе первого элемен та 13 И блоков 2 фиксации сбоев, та как на одном из входов первого элемента 13 И блоков 2 фиксации сбоев всех разрядов присутствует нулевой потенциал. Это свидетельствует р не нарушении минимальной формы 2-го ко Фибоначчи. Таким образом, предлагаемое устройство позволяет обнаружить часть сбоев типа переход О в 1, а также все сбои типа переход 1 в 0. При п 8 коэффициент обнаружения ошибок в известном устройстве составля ,ет 5д5н 33% - для однократной ошибк двухкратной ошибки, %н трехкратной ошибки и т.д. Общий коэффициент обнаружени ошибок составляет приблизительно 91%. В предлагаемом устройстве , м 76% - для однократной ошибки, 88% - для двухкратной ошибки, 96% - для трехкратной ошибки. Общий коэффициент обнаружения ошибо составляет приблизительно 99%. Следовательно, увеличение коэффициента обнаружения ошибок, особенно в случае однократных и двухкратных ошибок, и определяет положительный эффект. Формула изобретения Устройство, для контро;1я р кодов Фибоначчи, содержащее п разрядный триггерный регистр, элемент ИЛИ, (п-р) блоков фиксации сбоев, каждый из которых содержит первый элемент И, элемент ИЛИ,выход которого соединен с первым входом nepBoio элемента И, первый вход блока фиксации сбоев соединен со вторым входом первого элемента И, выход которого соединен с первым выходом блока фиксации сбоев, второй и третий входы блоке: фиксации сбоев соединены соответственно . с пе|)вым и вторым входами элемента ИЛИ, первые выходы всех блоков фиксации сбоев соединены с соответствующими входами элемента ИЛИ, выход которого является выходом устройства, выход каждого i-ro триггера регистра соединен с первым входом соответствующегв (i-p)-ro блока фиксации сбоев, со вторым входом (Г-р+1)-го блока фиксации сбоев и с третьим входом ()-ro блока фиксации сбоев, установочный вход устройства соединен с первых входом всех триггеров регистра, информационный вход триггера старшего разряда регистра соединен со входом устройства, отличающееся тем, что, с целью увеличения эффективности контроля путем фиксации ошибок типа переходов 1 в О, устройство дополнительно содержит группу из (п-р+1) элементов .ИЛИ, первый вход каждого элемента ИЛИ группы.является соответствующим информационным входом устройства, второй выход -каждого i-ro блока фиксации сбоев соединен со вторым входом (i-l)-ro и третьим входом (i-2)го элементов ИЛИ группы, выход каждого элемента ИЛИ группы соединен с информационньвл входом соответствующего, триггер;: регистра, управляющий вход устройства соединен с управляющим входом каждого блока фиксации сбоев, выходы младших разрядов региСтра соединены с соответствующими входами элемента ИЛИ, а каждый блок фиксации сбоев дополнительно содержит формирователь импульсов и дополнительный элемент И выход которого является вторым выходом блока фиксации сбоев., первый вход блока фиксации сбоев соединен со входом формирователя импульсов, выход которого соединен с первым входом дополнительного элемента И, второй вход которого соединен с управляющим входом блока фиксации сбоев. Источники информации, принятые во внимание при экспертизе 1. Стахов А.П. Введение в алгоритмическую теорию измерений. М., Советское радио, 1977, с.148, ис.38 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля @ -кодов Фибоначчи | 1983 |

|

SU1149262A1 |

| Устройство для контроля оптимальных @ -кодов Фибоначчи | 1983 |

|

SU1149261A1 |

| Устройство для обнаружения и исправления ошибок | 1987 |

|

SU1578811A1 |

| Устройство для контроля оптимальных Р-кодов Фибоначчи | 1987 |

|

SU1471193A1 |

| Устройство для обнаружения и исправления однократных ошибок оптимальных р-кодов Фибоначчи | 1987 |

|

SU1479932A1 |

| Устройство для контроля 3-кода Фибоначчи | 1987 |

|

SU1478217A1 |

| Устройство для обнаружения ошибок в пакетном @ -коде | 1987 |

|

SU1483645A1 |

| Устройство для приведения р-кодов Фибоначчи к минимальной форме | 1982 |

|

SU1019434A1 |

| Устройство для обнаружения и исправления ошибок в @ -кодах Фибоначчи | 1986 |

|

SU1441400A1 |

| Устройство для приведения @ -кодов Фибоначчи к минимальной форме | 1982 |

|

SU1092489A1 |

Авторы

Даты

1981-03-30—Публикация

1979-05-15—Подача