Изобретение относится к вычислительной технике и может быть использовано для организации обмена информа- цией ресурсов (процессоров, блоков памяти и т.д.) вычислительной системы Целью изобретения является расширение функциональных возможностей устройства за счет реализации децентра- лизованного и приоритетного способа настройки на требуемые соединения.

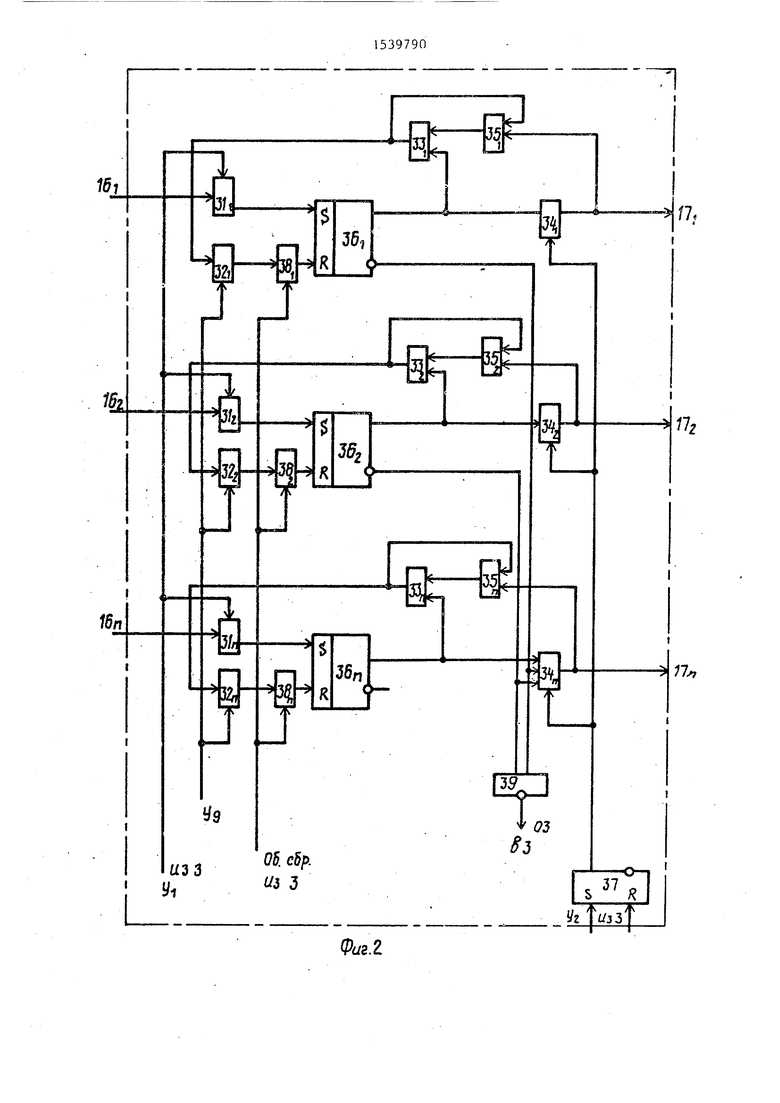

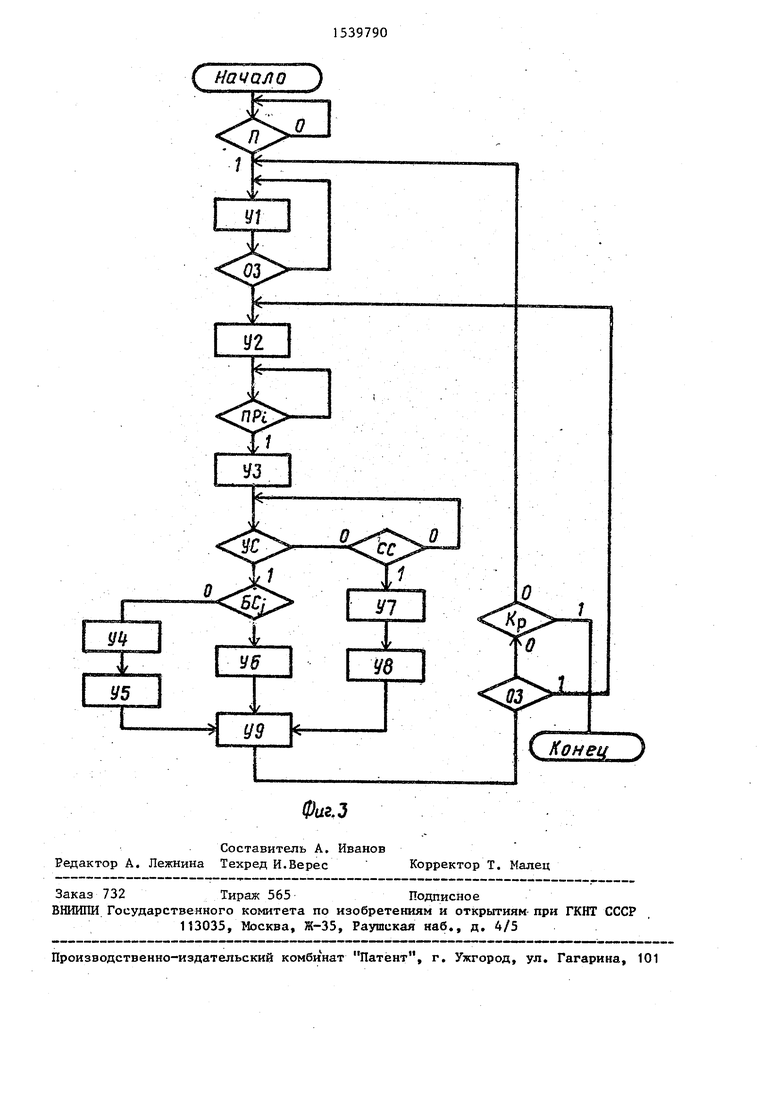

На фиг.1 представлена структурная коммутационного устройства; на фиг.2 - функциональная схема бло- ка приоритета; на фиг.З - граф-схема микропрограммы блока управления.

Коммутационное устройство (фиг.1) содержит два дешифратора 1 и 2, блок 3 управления, первый управляющий вход которого является входом 4 пуска устройства, три первых регистра 5, 6 и 7, матричный коммутатор 8, информационные входы 9 и выходы 10 устройства, первые 11 и вторые 12 наст- роечные входы матричного коммутатора, первые адресные входы 13 матричного коммутатора, настроечные входы 14 устройства, блок 15 приоритета, первые управляющие входы устрой- ства, управляющие выходы 17,,-17п устройства, шифратор 18 адреса, четвертый и пятый регистры 19 и 20, второй адресный вход 21 матричного коммутатора, блок 22 состояния, содержащий демультиплексор 23, регистр 24 состояния и мультиплексор 25, синхронизирующий вход 26 устройства, управляющий выход 27 Занято-свободно1 вторые управляющие входы устройства, выход 29 и элементы 30 коммутации матричного коммутатора.

Блок 15 приоритета (фиг.2) содержит первую группу элементов И ,

вторую группу элементов И 32{-32h, третью группу элементов И и четвертую группу элементов И 34,-34nj группу элементов ИЛИ и, триггеры , триггер 37 разрешения опроса, группу элементов ИЛИ и элемент И-НЕ 39. Шифратор 18 адреса является стандартным блоком устройства, содержит элементы ИЛИ и преобразует унитарный код в двоичный.

Блок 3 управления при наличии граф схемы микропрограммы (фиг.З) синтезируется по известным методам как автомат Мура или Мили.

Принцип функционирования устройства заключается в следующем.

Граф-схема микропрограммы, приведенная на фиг.З, описывает работу.устройства. По управляющему входу 4 в блок 3 управления поступает сигнал Пуск (П). Блок 3 управления начинает работу и формирует сигнал У1, который осуществляет прием сигналов- запросов в блоке 15 приоритета, пос-t тупающих от ресурсов (абонентов) по управляющим входам 28 -28У1. Единичный уровень сигнала-запроса указывает на необходимость обслуживания коммутационным устройством 1-го ресурса. Сигналы-запросы запоминаются в триггерах 364-36h блока 15 приоритета. При наличии одного или нескольких единичных уровней сигналов-запросов блок 15 приоритета формирует сигнал Общий запрос (03) в блок 3 управления. Есл сигнал 03 1, то блок 3 управления вырабатывает сигнал Y2 в блок 15 приоритета, по которому в блоке 15 приоритета устанавливается триггер 37 и на выходе 17; (i l,n) последнего образуется сигнал Разрешение на обслуживание 1-го ресурса (РО;).

Кроме того, по сигналу РО с помощью шифратора 18 формируется код адреса 1-го ресурса-передатчика, содержащий адрес Ау соответствующего столбца элементов 30 матричного коммутатора 8 и адрес М х для выбора соответствующей строки элементов 30. Код адреса АХМ х определяет двоичный номер ресурса-передатчика (адрес 1-го входа матричного коммутатора 8, к которому подключен i-й ресурс-передатчик). После этого блок 3 управления находится в ожидании поступления сигнала Прием (ПР , 1) отЧ-ресурса, сообщающего о наличии на настроечных входах 14 адреса приемника (ресурса), с которым хочет установить связь i-й ресурс-передатчик. При блок 3 управления формирует сигнал Y3, разрешающий прием адреса с настроечных входив 14 в регистр 7.

Формат log m-разрядного адреса j-ro приемника содержит признаковую и адресную части. Признаковая часть (Пр) определяет режимы установления соединения (УС) или стирания соединения (СС), а адресная часть содержит адрес Ау соответствующего выхода элемента матричного коммутатора 8 и адрес My для выбора соответствующего столбца элементов 30. Таким образом, код адреса АуМц определяет j-гй выход матричного коммутатора 8, к которому подключен j-й приемник.

Кроме того, код адреса АуМц поступает на адресные входы блока 22 состояния -и адресует с помощью мультиплексора 25 j-й бит состояния регистра

Формирует сигнал Y5, стробирую- 1 щий выходы дешифраторов J и 2 f установление заданного соединения соо ветствующего входа и выхода), сооб щающий ресурсу-передатчику о том, что j-й ресурс-приемник свободен (сигнал С на выходе 27, необходимый для определения момента передачи

Q данных ресурсом-передатчиком через матричный коммутатор 8 после того, как в нем установлена связь), и сбра сывающий триггер 37 разрешения опроса в блоке 15 приоритета (фиг.2). В

15 блоке IS приоритета каждый триггер 36j (i 1,п) содержитjкроме того, несимметричный триггер, выполненный на элементах И 33; и ИЛИ 35;, необходимый для запоминания сигнала оп20 роса и организации последующего сбро са триггера 36 по сигналу блока 3 управления с целью перехода к обслуживанию следующего по порядку запроса, хранимого в триггере 36 ().

25

30

35

В том случае, если осведомительные сигналы , блок управления на выходе 27 вырабатывает сигнал Занято, поступающий к ресурсу- передатчику.

Другая комбинация осведомительных сигналов и определяет ситу ацию, когда ресурс закончил передачу данных через матричный коммутатор 8, и осуществляет сброс ранее заданного им соединения (разборка соед нительного пути). При этом блок управления формирует сигнал Y7, осуществляющий запись кода из ре24. Единичное значение j-ro бита сое- ДО гистРа 7 соответственно в регистры 6 тояния (БС) свидетельствует о том, что j-й ресурс-приемник занят, а нулевое значение - j-й ресурс-приемник свободен.

После записи кода в регистр блок 3 управления анализирует признав ковую часть (Пр) адреса приемника. Если и в регистре 24 блока 22 состояния j-й бит состояния , то блоком управления формируется сигнал Y4, по которому содержимое регистра 7 (код А ц и код Мц) переписывается соответственно в регистры 6 и 5, j-й бит состояния регистра 24 устанавливается в единичное состояние и код АХМУ с выходов шифратора 18 заносится соответственно в ре-, гистр 1 - 20 (Ах) и регистр 19 (М). В следующем такте блок 3 управления

(Ац) и 5 (Мц) и сброс j-ro бита состояния в регистре 24 блока 22 состоя ния. Затем в следующем такте блок 3 управления выдает сигнал Y8, строби45 РУ°щий выходы дешифратора 2 (выполняющий сброс соединительного пути). Режим сбирания соединения осуществляется подачей кода , выбирающего j-й выход матричного коммутатора 8,

50 в соответствии с которым на j-м выходе дешифратора 2 формируется единичный уровень сигнала, выбирающий столбец элементов 30, ив этом столбце реализуется сброс установленного сое55 дкнения, если сигналы на выходах дешифратора 1 имеют нулевые уровни.

После формирования блоком 3 управления сигналов Y5, Y6 или Ye в следующем такте времени он вырабатывает

Формирует сигнал Y5, стробирую- 1 щий выходы дешифраторов J и 2 f установление заданного соединения соответствующего входа и выхода), сообщающий ресурсу-передатчику о том, что j-й ресурс-приемник свободен (сигнал С на выходе 27, необходимый для определения момента передачи

данных ресурсом-передатчиком через матричный коммутатор 8 после того, как в нем установлена связь), и сбрасывающий триггер 37 разрешения опроса в блоке 15 приоритета (фиг.2). В

блоке IS приоритета каждый триггер 36j (i 1,п) содержитjкроме того, несимметричный триггер, выполненный на элементах И 33; и ИЛИ 35;, необходимый для запоминания сигнала опроса и организации последующего сброса триггера 36 по сигналу блока 3 управления с целью перехода к обслуживанию следующего по порядку запроса, хранимого в триггере 36 ().

В том случае, если осведомительные сигналы , блок управления на выходе 27 вырабатывает сигнал Занято, поступающий к ресурсу- передатчику.

Другая комбинация осведомительных ; сигналов и определяет ситуацию, когда ресурс закончил передачу данных через матричный коммутатор 8, и осуществляет сброс ранее заданного им соединения (разборка соединительного пути). При этом блок управления формирует сигнал Y7, осуществляющий запись кода из регистРа 7 соответственно в регистры 6

гистРа 7 соответственно в регистры 6

(Ац) и 5 (Мц) и сброс j-ro бита состояния в регистре 24 блока 22 состояния. Затем в следующем такте блок 3 управления выдает сигнал Y8, стробиРУ°щий выходы дешифратора 2 (выполняющий сброс соединительного пути). Режим сбирания соединения осуществляется подачей кода , выбирающего j-й выход матричного коммутатора 8,

в соответствии с которым на j-м выходе дешифратора 2 формируется единичный уровень сигнала, выбирающий столбец элементов 30, ив этом столбце реализуется сброс установленного соедкнения, если сигналы на выходах дешифратора 1 имеют нулевые уровни.

После формирования блоком 3 управления сигналов Y5, Y6 или Ye в следующем такте времени он вырабатывает

сигнал Y, поступающий в блок 15 приоритета и осуществляющий сброс 1-го запроса (сброс триггера 36J). В результате установления триггера 36j в с нулевое состояние на его инверсном выходе появляется единичный уровень сигнала, который разрешает формирова- ние сигнала на выходах элементов И в блоке 15 приоритета, JQ

Блок 3 управления анализирует осведомительный сигнал 03, приходящий с выхода 29 блока 15 приоритета, и если , то надиндется обслуживание следующего запроса (вновь формиру|5 ется сигнал Y2). При и входном сигнале Конец работы , поступающем по входу 26, блок 3 управления заканчивает свою работу,, а при наличии повторяет цикл выполнения микро- 20 программы.

Формула изобретения

Коммутационное устройство, содер- 25 жащее два дешифратора, блок управления, три регистра и матричный коммутатор, информационные входы и выходы которого соединены соответственно с информационными входами и выходами 30 устройства, вход пуска которого соединен с первым управляющим входом блока управления, информационные входы первого и второго регистров соединены с выходами соответствующих ас разрядов третьего регистра, выход старшего разряда которого соединен с вторым управляющим входом блока управления, первый управляющий выход которого соединен с входами записи пер- 40 вого и второго регистров, выходы первого дешифратора соединены с первыми настроечными входами матричного коммутатора, вторые настроечные входы которого соединены с выходами второго дешиф 4 ратора, вход адреса которого соединен с информационным выходом первого регистра, информационные выходы второго регистра соединены с первыми адресными входами матричного коммута- J тора, второй управляющий выход блока управления соединен с входом записи

третьего регистра, информационные входы которого соединены с настроечными входами устройства, первый вход управления которого соединен с третьим управляющим входом блока управления, третий управляющий выход которого соединен с выходом Занято - свободно устройства, вход синхронизации которого соединен с четвертым управляющим входом блока управления, четвертый и пятый управляющие выходы которого соединены с управляющими входами первого и второго дешифраторов соответственно, отличающееся тем, что, с целью расширения функциональных возможностей за счет реализации децентрализованного и приоритетного способа настройки на требуемые соединения, в устройство введены блок приоритета, шифратор адреса, четвертый и пятый регистры и блок состояния, причем информационный вход блока приоритета соединен с вторым входом управления устройства, управляющий вход которого соединен с информационным выходом блока приоритета и входом шифратора адреса, первая группа выходов которого соединена с информационным входом четвертого регистра, а вторая группа выходов - с информационным входом пятого регистра, информационный выход которого соединен с вторым адресным входом матричного коммутатора, информационный выход четвертого регистра соединен с адресным входом первого дешифратора, входы записи четвертого и пятого регистров соединены с шестым управляющим выходом блока управления, управляющие пятый вход и седьмой выход которого соединены соответственно с управляющими выходом и входом блока приоритета, восьмой управляющий выход блока управления соединен с одноименным входом блока состояния, адресный вход которого соединен с информационными входами первого и второго регистров, информационный выход блока состояния соединен с- шестым управляющим входом блока управления.

M-и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Многоканальное устройство управления вводом информации в микроЭВМ | 1984 |

|

SU1234844A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для сопряжения управляющей и управляемых вычислительных машин | 1988 |

|

SU1517033A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Микропрограммное устройство управления | 1980 |

|

SU955055A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649506A1 |

Изобретение относится к вычислительной технике и может быть использовано для организации обмена информацией ресурсов (процессоров, блоков памяти и т.д.) вычислительной системы. Целью изобретения является расширение функциональных возможностей устройства за счет реализации децентрализованного и приоритетного способа настройки на требуемые соединения. Структурная схема коммутационного устройства содержит два дешифратора 1 и 2, блок управления 3, вход 4 пуска устройства, три первых регистра 5, 6 и 7 и матричный коммутатор 8, информационные входы 9 и выходы 10 устройства, первые 11 и вторые 12 настроечные входы матричного коммутатора, его адресные входы 13, настроечные входы 14 устройства, блок приоритета 15, первый управляющий вход 161-16N устройства, управляющий выход 171-17N устройства, шифратор адреса 18, четвертый и пятый регистры 19 и 20, второй адресный вход 21 матричного коммутатора, блок состояния 22, содержащий демультиплексор 23, регистр состояния 24 и мультиплексор 25, синхронизирующий вход 26 устройства, управляющий выход 27 "Занято-свободно" устройства, второй управляющий вход 281-28N устройства, элементы коммутации 30 матричного коммутатора 8. 3 ил.

Фаг2

„УЦиЩ.

( Начало j

UiJ

QO

У5

У9

С Конец J

| Устройство для сопряжения | 1976 |

|

SU651335A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коммутационное устройство для вычислительной системы | 1978 |

|

SU746492A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО для ВЫПУСКА СЫПУЧИХ МАТЕРИАЛОВ | 0 |

|

SU246109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1988-03-29—Подача