Изоб .Л ;;тение относится к импульсной технике и автоматике и может быть использовано в приемопередатчиках многоимпульсных сигналов, например, в линиях связи ВИМ - ИВК.

Цель изобретения - расширение функциональных возможностей преобразователя за счет возможности работы в режимах шифрации и дешифрации.

На фиг.1 представлена структурная W ИВК, поступает на вход 11 устройства

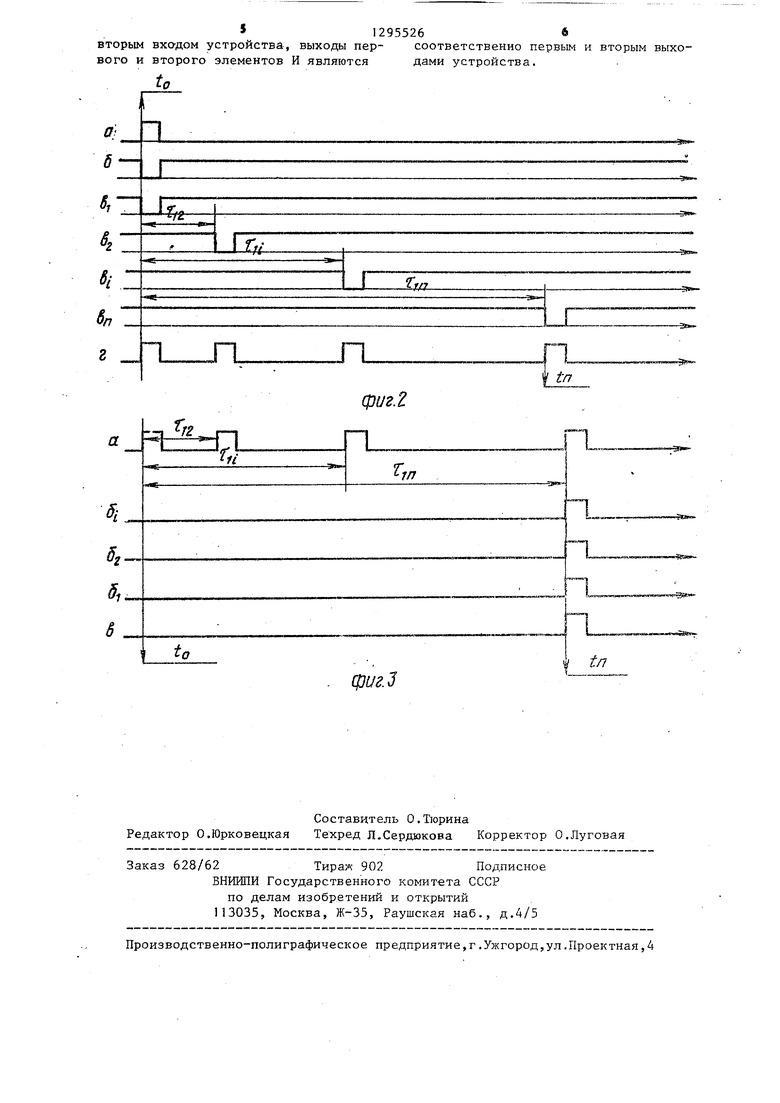

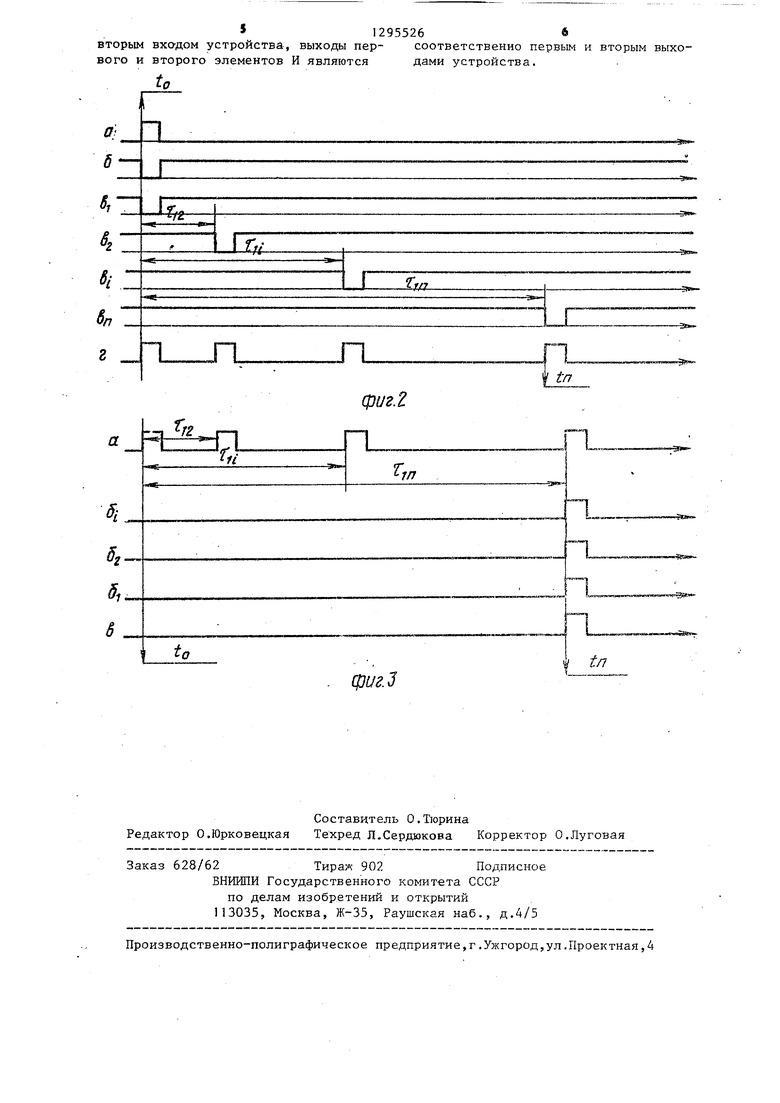

схема предлагаемого преобразователя; на фиг.2 и 3 - временные диаграммы работы преобразователя в режимах кодирования и декодирования.

Преобразователь содержит элемент И-НЕ 1, регистр 2 сдвига, многовхо- довый элемент И-НЕ или ИЛИ-НЕ 3,триггер 4, первый, второй и третий элементы И , элемент 8 задержки,блок 9 выделения фронта, генератор 10 импульсов, первый и второй входы 11 и 12, первый и второй выходы 13 и 14.

Элемент 3 представляет собой базовый элемент цифровой техники, выполняющий логические функции И или ИЛИ в зависимости от логического уровня сигналов.

Блок 9 выделения фронта выполнен, например, в виде аналогового или цифрового дифференцирующего устройства.

На фиг.2 обозначены: а - импульс на входе 11 устройства; б - импульс на входе регистра 2 сдвига; в; - импульс на i-M выходе регистра 2 сдвига (,2,...,п); г - сформированный ИВК на инверсном выходе элемента 3 и на выходе 13 устройства (, Y в v... ... V Bj). На фнг;3 обозначены: а - дешифрируемый ИВК на входе 12 устройства и входе регистра 2 сдвига; б- - i-й импульс дешифрируемого ИВК на i-M регистра 2 сдвига в момент t появления п-го импульса на п-м выходе; в - дешифрированный ИВК (импульс совпадения) на прямом выходе элемента 3 и на выходе 14 устройства (в-б,- б,г ...-б,).

Уровни сигналов на фиг.2 и 3 пока- з.аны в предположении, что высокому уровню сигнала соответствует логический символ , а низкому уровню - символ О, и что заявленное устройство и сопрягаемые с ним по входу и выходу блоки выполнены в логической системе элементов Шеффера, которая характеризуется соотношениями OYO 0. Если предлагаемое устройство и сопрягаемые блоки выполнены в

системе элементов Пирса, характеризующейся логическими функциями О х 1V1 1, то уровни всех сигналов должны быть заменены на -противоположные .

Преобразователь работает следующим образом.

Одиночньй импульс, подлежащий шифрированию, т.е. приборазованию в

5

и далее идет на вход элемента И-НЕ 1 и вход триггера 4. Триггер устанавливается в состояние S, что соответствует режиму работы устройства в

5 качестве шифратора ИВК.

Импульс с первого входа 11 устройства одновременно с установкой триггера 4 в состоянии S устанавливает в такое же состояние регистр 2 сдвига, т.е. записывает во все его ячейки символ 1. Одновременно сигнал с З-выхода триггера 4 переводит регистр 2 сдвига в режим сдвига слева направо () и удерживает регистр 2 в этом режиме в течение всего времени пребывания устройства в режиме шифратора.

Сигналом с выхода триггера 4 открываются элементы И-НЕ 1 и И 5, а эле менты № 6 и 7 закрываются. Через открытый элемент И-НЕ i входной сигнал в виде импульсов низкого уровня (смена уровня обеспечивается инверсией на выходе элемента 1) поступает на

5 первый информсщионный вход D1 регист

ра 2 сдвига и продвигается по нему (слева направо) с помощью импульсов сдвига от генератора 10,

Элемент 3 для импульсов низкого уровня работает как элемент ИЛИ-НЕ. Поэтому на его первом инверсном выходе, по мере продвижения входного импульса в регистре 2 сдвига, образуется серия импульсов высокого уровня с междуимпульсными интервалами, - задаваемыми подключением входов элемента 3 к выходам регистра 2 сдвига, т.е. требующийся ИВК Через первый элемент И 5 эта серия импульсов проходит на первый выход 13 устройства. В этом время импульс низкого уровня с последнего выхода регистра 2 сдвига через последовательно включенные блок,9 выделения фронта и элемент 8 задержки поступает на второй,инверс- ньй вход триггера 4 и переводит его в состояние R. Задержка импульса сброса в элементе 8 на время bta o ,

0

5

0

5

где ч; - длительность выходных импульсов элемента 3, необходима для того, чтобы элемент. И 5 не закрылся до полного прохождения через него последнего импульса сформированного ИВК.

После перевода триггера 4 в состояние R преобразователь переключается в режим дешифратора.

Импульс низкого уровня с последнего выхода регистра 2 сдбига, пройдя через блок 9 выделения фронта в элемент 8 задержки, одновременно с переводом триггера 4 в состояние R устанавливает в такое же состояние регистр 2 сдвига, т.е. записывает во все его ячейки символ О, а сигнал с R-выхода триггера 4 переводит регистр 2 сдвига в режим сдвига справа налево () и удерживает его в этом режиме в течение всего времени пребывания устройства в режиме дешифратора. Импульсы высокого уровня с выхода элемента И 7 поступают на второй информационный вход D2 регистра 2 сдвига и продвигаются по нему в виде символов 1. В режиме дешифратора элементы И-НЕ 1 и И 5 закрываются, а третий и четвертый элементы И 6 и 7 открываются сигналом с другого выхода триггера 4. На второй вход 12 устройства поступает серия импульсов высокого уровня, представляющая собой ИВК, подлежащий дешифрированию. Через элемент И 7 этот ИВК поступает на вход регистра 2 сдвига и продвигается по нему справа налево. Для импульсов высокого уровня элемент 3 работает как элемент И-НЕ. Поэтому,

когда все импульсы дешифрируемого ИВК 40 сдвига через последовательно соеди- поступят в регистр 2 сдвига, на вто- ненные блок выделения фронта и элером прямом выходе элемента 3 образуется импульс совпадения высокого уровня, представляющий собой дешифрированный ИВК, ранее поступивший на второй вход устройства. Через элемент И 6 этот импульс идет на второй выход 14 устройства.

В режиме дешифратора (состояние R триггера 4) устройство находится до поступления на его первый вход очередного импульса, подлежащего шифри- рованию, после чего устройство вновь переходит в режим шифратора (состояние S триггера 4), и процесс повторяется. Такое чередование режимов работы устройства полностью соответствует, например, режиму работы ли

95526

НИИ связи ВИМ-ИВК, в которой после одного сеанса передачи могут проходить несколько сеансов приема.

В процессе перехода из режима дешифратора в режим шифратора блок 9 выделения фронта, срабатьгаающий только от переднего фронта тямпульса, снимаемого с последнего выхода регистра 2 сдвига, препятствует удержанию триг- 4 в состоянии R (в момент.

10

гера

когда он должен переключиться в сое- S)

тояние Ъ ) низким логическим уровнем на последнем выходе регистра 2 сдвига при отсутствии на этом выходе им- пульсов дешифрируемого ИВК.

Ф ормула изобретения

Преобразователь импульсно-времен- ных кодов, содержащий генера.тор импульсов, выход которого подключен к тактовому входу регистра сдвига и блок выделения фронта, отличающийся тем, что, с целью расширения функциональных возможностей преобразователя за счет возможности работы в режимах шифрации и дешифрации, в него введены многовходовый элемент И-НЕ или ШШ-НЕ, триггер, элемент задержки, элементы И и элемент И-НЕ, выход которого соединен с первым информационным входом регистра сдвига, выходы которого подключены к соответствующим входам многовходового элемента И-НЕ или ИЛИ-НЕ, инверсный выход которого соединен с первым входом первого элемента И, прямой выход соединен с первым входом второго элемента И, инверсный выход регистра

мент задержки соединен с входами обнуления регистра сдвига и триггера, прямой выход которого подключен к первому входу элемента И-НЕ, первому управляющему входу регистра сдвига и второму входу первого элемента И, инверсный выход триггера соединен с вторым входом второго элемента И,вторым управляющим входом регистра сдвига и первым входом третьего элемента- И, выход которого подключен к второп му информационному входу регистра сдвига, второй вход элемента И-НЕ

объединен с установочными входами триггера и регистра сдвига и является первым входом устройства, второй . вход третьего элемента И является

12955266

вторым входом устройства, выходы пер- соответственно первым и вторым выхо- вого и второго элементов И являются дами устройства.

и

1

.Itnn

П

5 Иtf7

фиг2

Чг

п

Si

s,.

б,.

6.

in

фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор импульсно-временных кодов | 1981 |

|

SU999152A1 |

| Устройство для приема команд | 1982 |

|

SU1084856A1 |

| Дешифратор импульсно-временных кодов | 1986 |

|

SU1474851A1 |

| Стартстопный демодулятор | 1982 |

|

SU1062876A1 |

| Счетчик с контролем | 1983 |

|

SU1123106A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| Устройство для контроля длительности импульсов | 1980 |

|

SU901949A1 |

| Устройство для моделирования дискретного канала связи | 1977 |

|

SU720774A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| Способ фазовой синхронизации тактовых импульсов внешним импульсом запуска | 2024 |

|

RU2824042C1 |

Изобретение относится к импульсной технике и автоматике и может быть использовано в приемопередатчиках многоимпульсных сигналов, например, в линиях связи ВИМ-ИВК. Цель изобретения - расширение функциональных возможностей преобразователя за счет возможности работы в режимах шифра- ции и дешифрации. Преобразователь содержит элемент И-НЕ 1, регистр 2 сдвига, многовходовый элемент И-НЕ или ИЛИ-НЕ 3,триггер 4,элементы И 5, 6 и 7, элемент 8 задержки, блок 9 вьщеле- ния фронта, генератор 10 импульсов, входы 11 и 12 и выходы 13 и 14. 3 ил. /4 :Jbui. «. ф(/г.

Составитель О.Тюрина Редактор О.Юрковецкая Техред Л.Сердюкова Корректор 0.Луговая

Заказ 628/62Тираж 902Подписное

ВНШШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул,Проектная,4

| Глобус М.А | |||

| Двоичное кодирование в асинхронных системах | |||

| - М.: Связь, 1972, с.70, рйс.Юа, с.74, рис.14а | |||

| Ланцов А.Л | |||

| и др | |||

| Цифровые устройства на комплементарных МДП интегральных микросхемах | |||

| - М.: Радио и связь, с.24-25, рис.1.15 | |||

| Дешифратор импульсно-временных кодов | 1981 |

|

SU999152A1 |

Авторы

Даты

1987-03-07—Публикация

1985-06-27—Подача