1129

Изобретение относится к электро- радиоизмерительной технике и может быть использовано для получения двух гармонических сигналов с заданными фазовыми соотношениями в широком диапазоне частот.

Цель изобретения - повьшение точности задания дискретных значений фазовых сдвигов в широком диапазоне частот.

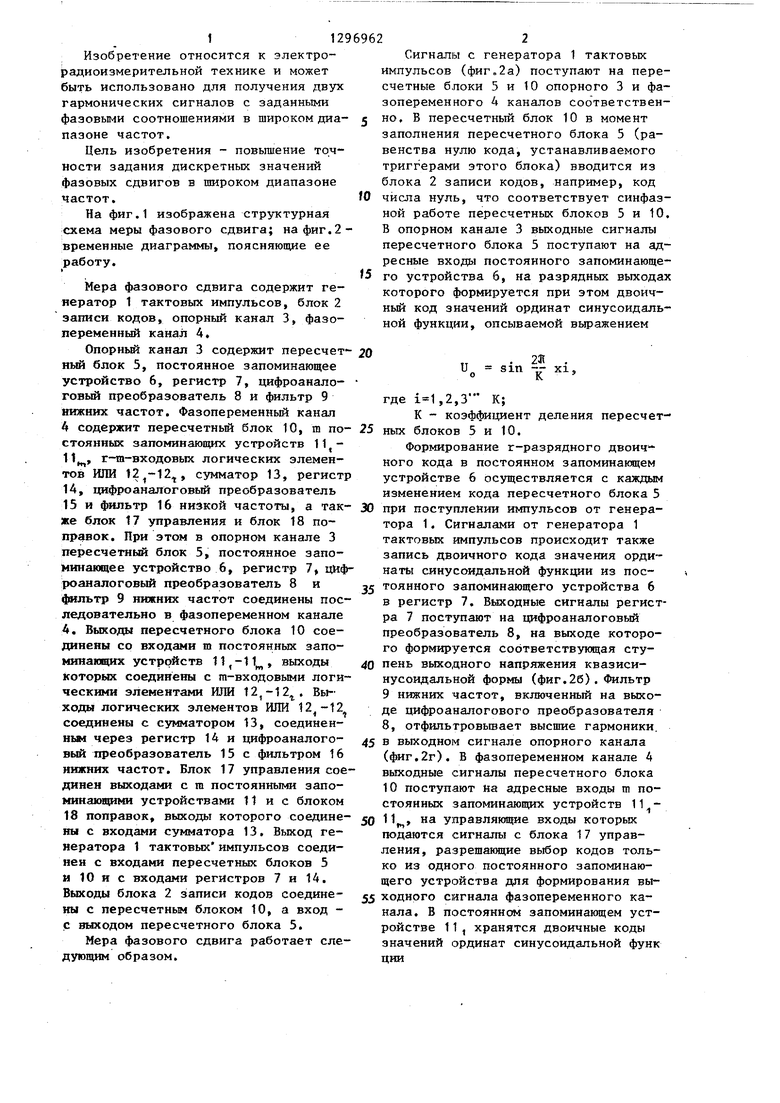

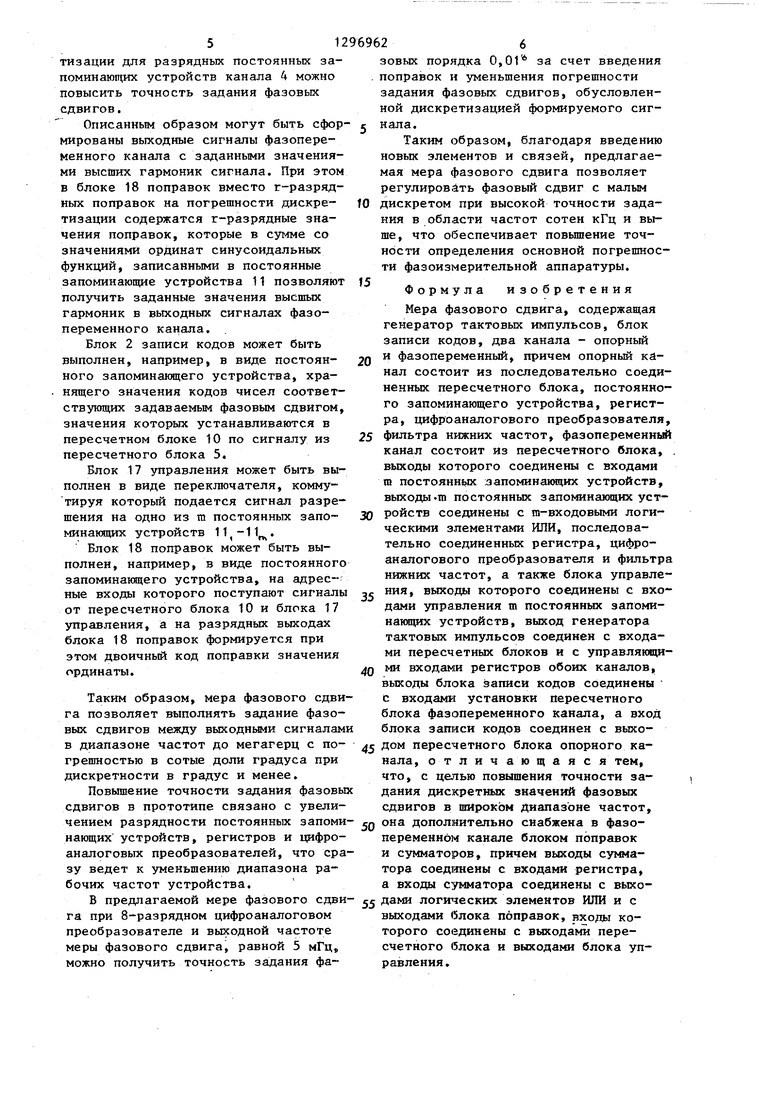

На фиг.1 изображена структурная чгхема меры фазового сдвига; на фиг.2- временные диаграммы, поясняющие ее работу.

Сигналы с генератора 1 тактовых импульсов (фиг„2а) поступают на пересчетные блоки 5 и 10 опорного 3 и фа- зопеременного 4 каналов соответственно, В пересчетный блок 10 в момент заполнения пересчетного блока 5 (равенства нулю кода, устанавливаемого тригг ерам:и этого блока) вводится из блока 2 записи кодов, например, код числа нуль, что соответствует синфазной работе пересчетных блоков 5 и 10 В опорном канале 3 выходные сигналы пересчетного блока 5 поступают на ад ресные входы постоянного запоминающе 15 го устройства 6, на разрядных выхода которого формируется при этом двоичный код значений ординат синусоидаль ной функции, опсываемой выражением

и

, 23 ,

sin XI,

К.

Мера фазового сдвига содержит генератор 1 тактовых импульсов, блок 2 записи кодов, опорный канал 3, фазо- переменный канал 4.

Опорный канал 3 содержит пересчет- 20 ный блок 5, постоянное запоминающее устройство 6, регистр 7, цифроанало- говый преобразователь 8 и фильтр 9 нижних частот. Фазопеременный канал

4 содержит пересчетный блок 10, m по- 25 ных блоков 5 и 10. стоянных запоминающих устройств Формирование г-разрядного двоич- 11, r-m-входовых логических элементов ИЛИ , сумматор 13, регистр 14, цифроаналоговый преобразователь

15 и фильтр 16 низкой частоты, а так- 30 при поступлении импульсов от генера- Же блок 17 управления и блок 18 по- тора 1. Сигнал-ши от генератора 1

где ,2,3 К;

К - коэффи1 иент деления пересчетного кода в постоянном запоминакяцем устройстве 6 осуществляется с каждым изменением кода пересчетного блока 5

правок. При этом в опорном канале 3 пересчетиый блок 5, постоянное запоминающее устройство 6, регистр 7, цйф- роаналоговый преобразователь 8 и фильтр 9 нижних частот соединены последовательно в фазопеременном канале 4, Выходы пересчетного блока 10 соединены со входами т постоянных запоминающих устройств 11,-11„, выходы которых соединены с т-входовыми логическими элементами ИЛИ . Выходы логических элементов ИЛИ соединены с сумматором 13, соединенным через регистр 14 и цифроаналого- вый преобразователь 15с фильтром 16 нижних частот. Блок 17 управления соединен выходами с га постоянными запо- минакнцини устройствами 11 и с блоком

тактовых импульсов происходит также запись двоичного кода значения ординаты синусоидальной функции из пос35 тоянного запоминающего устройства 6 в регистр 7. Выходные сигналы регистра 7 поступают на цифроаналоговый преобразователь 8, на выходе которого формируется соответствующая сту40 пень выходного напряжения квазисинусоидальной формы (фиг.26) . Фильтр

9нижних частот, включенный на выходе цифроаналогового преобразователя 8, отфильтровьшает высшие гармоники.

45 в выходном сигнале опорного канала (фиг,2г). В фазопеременном канале 4 выходные сигналы пересчетного блока

10поступают на адресные входы m постоянных запоминающих устройств 11 10поступают на адресные входы m стоянных запоминающих устройств 1

18 поправок, выходы которого соедине- 50 1 управляющие входы которых

вы с входами сумматора 13, Выход генератора 1 тактовых импульсов соединен с входами пересчетных блоков 5 и 1О и с входами регистров 7 и 14. Выходы блока 2 записи кодов соединены с пересчетным блоком 10, а вход - с выходом пересчетного блока 5.

Мера фазового сдвига работает следующим образом.

подаются сигналы с блока 17 управления, разрешающие выбор кодов тол ко из одного постоянного запоминаю щего устройства дпя формирования 55 ходного сигнала фазопеременного к нала. В постоянном запоминающем у ройстве 11, хранятся двоичные коды значений ординат синусоидальной фу ции

Сигналы с генератора 1 тактовых импульсов (фиг„2а) поступают на пересчетные блоки 5 и 10 опорного 3 и фа- зопеременного 4 каналов соответственно, В пересчетный блок 10 в момент заполнения пересчетного блока 5 (равенства нулю кода, устанавливаемого тригг ерам:и этого блока) вводится из блока 2 записи кодов, например, код числа нуль, что соответствует синфазной работе пересчетных блоков 5 и 10. В опорном канале 3 выходные сигналы пересчетного блока 5 поступают на адресные входы постоянного запоминающе- го устройства 6, на разрядных выходах которого формируется при этом двоичный код значений ординат синусоидальной функции, опсываемой выражением

и

, 23 ,

sin XI,

К.

ных блоков 5 и 10. Формирование г-разрядного двоич-

где ,2,3 К;

К - коэффи1 иент деления пересчетных блоков 5 и 10. Формирование г-разрядного двоич-

при поступлении импульсов от генера- тора 1. Сигнал-ши от генератора 1

ного кода в постоянном запоминакяцем устройстве 6 осуществляется с каждым изменением кода пересчетного блока 5

тактовых импульсов происходит также запись двоичного кода значения ординаты синусоидальной функции из пос35 тоянного запоминающего устройства 6 в регистр 7. Выходные сигналы регистра 7 поступают на цифроаналоговый преобразователь 8, на выходе которого формируется соответствующая сту40 пень выходного напряжения квазисинусоидальной формы (фиг.26) . Фильтр

9нижних частот, включенный на выходе цифроаналогового преобразователя 8, отфильтровьшает высшие гармоники.

45 в выходном сигнале опорного канала (фиг,2г). В фазопеременном канале 4 выходные сигналы пересчетного блока

10поступают на адресные входы m постоянных запоминающих устройств 1 управляющие входы которых

подаются сигналы с блока 17 управления, разрешающие выбор кодов только из одного постоянного запоминающего устройства дпя формирования вы- 55 ходного сигнала фазопеременного канала. В постоянном запоминающем устройстве 11, хранятся двоичные коды значений ординат синусоидальной функ ции

.

sin -2fi .

1

В постоянном запоминающем устройстве 11 хранятся коды функции

sin

(2 К

2) К-т

где m - число постоянных запоминающих устройств в фазопеременном канале, характеризующее уменьшение дискрета фазового сдвига,

В постоянном запоминающем устройстве 11 хранятся коды функции

и,

т.д.

2Jf

2Ir,

f fl f- .i - -.X ()J

В постоянном запоминающем устройстве 11 хранятся двоичные коды функции

. е2:Л , т - 1)

и sin ( ;г 1 ,

f К тпх К

Пусть с блока 17 управления разрешается выбор, например, из постоянного запоминающего устройства 11, , двоичных г-разрядных кодов значений ординат синусоидальной функции

2П .

Sin

которые через логические элементы ИЛИ , сумматор 13 и регистр 14 подаются на цифроаналоговый преобразователь 15. При этом выходной гармонический сигнал на выходе фазо- перемен гого канала (фиг.2д) отфильтрованный из выходного сигнала квазисинусоидальной формы (фиг.2в) цифро- аналогового преобразователя 15, совпадает по фазе с выходным гармоническим сигналом опорного канала (фиг.2г) с точностью до погрешности формирования. Использование постоянсостояния пересчетного блока 10. С блока IS поправок код поправки посту пает на входы сумматора 13, на другие входы которого подается двоичный код значений ординаты синусоидальной функции с разрядных выходов выбранного постоянного запоминающего устройства 11 для данного состояния пересчетного блока 10. С выхода сумматора 13 г-разрядный двоичный код, равный сумме кодов из постоянного запоминающего устройства и блока 18 поправок, записьшается сигналом от генератора 1 тактовых импульсов в регистр 14. Таким образом, цифро- аналоговый преобразователь 15 вклюного запоминакяцего устройства 11 дпя

формирования выходного сигнала фазо- ченный на выходе регистра 14, формипеременного канала (фиг.2е;ж) позволяет установить выходные сигналы меры фазового сдвига с дискретом

л Ч-.

211

А icTm и т.д.

Фазовый сдвиг между выходными сигналами устройства можно изменять также с дискретом, равным

2Л

/1 -К-,

путем записи в пересчетный блок 10 канала 4, в момент заполнения пере969624

счетного блока 5 канала 3, из блока 2 записи кодов, кода числа соответ- ствукицего задаваемому фазовому сдвигу (фиг.2з,и).

Формирование выходных сигналов меры фазового сдвига описанным образом с дискретом

23Г

4Ч,

К X m

имеет погрешность, вызванную дискретизацией значений ординат аппроксимируемой синусоидальной функции.

С целью повышения точности задания дискретных значений фазовых сдвигов в широком диапазоне частот используется г-разрядный сумматор 13 и г-разрядный блок 18 поправок.

Блок 18 поправок содержит Кхт значений ДВОИЧНЕЛХ кодов поправок для К двоичных кодов значений ординат синусоидальных функций, записанных в m постоянных запоминающих устройствах 11 11у. фазопеременного канала. Выбор необходимого значения поправки осуществляется по сигналам от блока 17 управления и пересчетного блока 10 для соответствукицего постоянного запоминающего устройства 11 и данного

состояния пересчетного блока 10. С блока IS поправок код поправки поступает на входы сумматора 13, на другие входы которого подается двоичный код значений ординаты синусоидальной функции с разрядных выходов выбранного постоянного запоминающего устройства 11 для данного состояния пересчетного блока 10. С выхода сумматора 13 г-разрядный двоичный код, равный сумме кодов из постоянного запоминающего устройства и блока 18 поправок, записьшается сигналом от генератора 1 тактовых импульсов в регистр 14. Таким образом, цифро- аналоговый преобразователь 15 вклю0

5

рует ступень выходного напряжения квазисинусоидальной формы с учетом поправки за счет погрешности дискре- тизащш значений ординат для данного числа разрядов цифроаналогового преобразователя 15. Формирование г-разрядных двоичных кодов в выбранном постоянном запоминакнцем устройстве 11 и в блоке 18 поправок осуществляется с каядым изменением кода пересчетного блока 10 при поступлении .импульсов от генератора 1. Корректируя значения ординат синусоидальных функций с учетом погрешности дискреto

тизации для разрядных постоянных запоминающих устройств канала 4 можно повысить точность задания фазовых сдвигов.

Описанным образом могут быть сфор- г мированы выходные сигналы фазопере- менного канала с заданными значениями выс1аих гармоник сигнала. При этом в блоке 18 поправок вместо г-разряд- Ных поправок на погрешности дискретизации содержатся г-разрядные значения поправок, которые в сумме со значениями ординат синусоидальных функций, записанными в постоянные запоминающие устройства 11 позволяют }5 получить заданные значения высшых гармоник в выходных сигналах фазо- переменного канала.

Блок 2 записи кодов может быть выполнен, например, в виде постоянного запоминающего устройства, хранящего значения кодов чисел соответствующих задаваемым фазовым сдвигом, значения которых устанавливаются в пересчетном блоке 10 по сигналу из пересчетного блока 5.

Блок 17 управления может быть выполнен в виде переключателя, коммутируя который подается сигнал разрешения на одно из m постоянных запоминающих устройств 11, 11f

Блок 18 поправок может быть вы12969626

зовых порядка 0,01 за счет введения поправок и уменьшения погрешности задания фазовых сдвигов, обусловленной дискретизацией формируемого сигнала.

Таким образом, благодаря введению новых элементов и связей, предлагаемая мера фазового сдвига позволяет регулировать фазовый сдвиг с малым дискретом при высокой точности задания в области частот сотен кГц и выше, что обеспечивает повышение точности определения основной погрешности фазоизмерит«шьной аппаратуры.

20

30

Формула изобретения

Мера фазового сдвига, содержащая генератор тактовых импульсов, блок записи кодов, два канала - опорный и фазопеременный, причем опорный канал состоит из последовательно соединенных пересчетного блока, постоянного запоминающего устройства, регистра, цифроаналогового преобразователя,

25 фильтра нижних частот, фазопеременный канал состоит из пересчетного блока, . выходы которого соединены с входами га постоянньк запоминающих устройств, выходы.щ постоянных запоминающих устройств соединены с тп-входовыми логическими элементами ИЛИ, последовательно соединенных регистра, цифро- аналогового преобразователя и фильтра нижних частот, а также блока управления, выходы которого соединены с входами управления m постоянных запоми- нанщих устройств, выход генератора тактовых импульсов соединен с входами пересчетных блоков и с управляющими входами регистров обоих каналов, выходы блока записи кодов соединены с входами установки пересчетного блока фазопеременного канала, а вход блока записи кодов соединен с выхополней, например, в виде постоянного запоминаннцего устройства, на адресные входы которого поступают сигналы от пересчетного блока 10 и блока 17 управления, а на разрядных выходах блока 18 поправок формируется при этом двоичный код поправки значения ординаты.

25 фильтра нижних частот, фазопеременн канал состоит из пересчетного блока выходы которого соединены с входами га постоянньк запоминающих устройств выходы.щ постоянных запоминающих ус ройств соединены с тп-входовыми логи ческими элементами ИЛИ, последовательно соединенных регистра, цифро- аналогового преобразователя и фильт нижних частот, а также блока управл ния, выходы которого соединены с вх дами управления m постоянных запоми нанщих устройств, выход генератора тактовых импульсов соединен с входа ми пересчетных блоков и с управляющ ми входами регистров обоих каналов, выходы блока записи кодов соединены с входами установки пересчетного блока фазопеременного канала, а вхо блока записи кодов соединен с выхо45 дом пересчетного блока опорного канала, отличающаяся тем, что, с целью повышения точности задания дискретных значений фазовых сдвигов в широком диапазоне частот.

Таким образом, мера фазового сдвига позволяет выполнять задание фазовых сдвигов между выходными сигналами в диапазоне частот до мегагерц с погрешностью в сотые доли градуса при дискретности в градус и менее.

Повышение точности задания фазовых сдвигов в прототипе связано с увеличением разрядности постоянных запоми- Q она дополнительно снабжена в фазо- нающих устройств, регистров и цифро- переменном кангше блоком поправок аналоговых преобразователей, что ера- и сумматоров, причем выходы сумма- зу ведет к уменьшению диапазона ра- тора соед11гаены с входами регистра, бочих частот устройства. а входы с: гмматора соединены с выхоВ предлагаемой мере фазового сдви- дами логи еских элементов ИЛИ и с га при 8-разрядном цифроаналоговом выходами блока поправок, входы ко- преобразователе и выходной частоте торого соединены с выходами перемеры фазового сдвига, равной 5 мГц, счетного блока и выходами блока уп- можно получить точность задания фа- равления.

Формула изобретения

Мера фазового сдвига, содержащая генератор тактовых импульсов, блок записи кодов, два канала - опорный и фазопеременный, причем опорный канал состоит из последовательно соединенных пересчетного блока, постоянного запоминающего устройства, регистра, цифроаналогового преобразователя,

фильтра нижних частот, фазопеременный канал состоит из пересчетного блока, . выходы которого соединены с входами га постоянньк запоминающих устройств, выходы.щ постоянных запоминающих устройств соединены с тп-входовыми логическими элементами ИЛИ, последовательно соединенных регистра, цифро- аналогового преобразователя и фильтра нижних частот, а также блока управления, выходы которого соединены с входами управления m постоянных запоми- нанщих устройств, выход генератора тактовых импульсов соединен с входами пересчетных блоков и с управляющими входами регистров обоих каналов, выходы блока записи кодов соединены с входами установки пересчетного блока фазопеременного канала, а вход блока записи кодов соединен с выходом пересчетного блока опорного канала, отличающаяся тем, что, с целью повышения точности задания дискретных значений фазовых сдвигов в широком диапазоне частот.

она дополнительно снабжена в фазо- переменном кангше блоком поправок и сумматоров, причем выходы сумма- тора соед11гаены с входами регистра, а входы с: гмматора соединены с выхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Калибратор фазы | 1983 |

|

SU1138761A1 |

| Устройство для поверки фазометров | 1982 |

|

SU1057877A1 |

| Регулируемая мера фазовых сдвигов | 1985 |

|

SU1257562A1 |

| Широкодиапазонный калибратор фазовых сдвигов | 1987 |

|

SU1525614A1 |

| Регулируемая мера фазовых сдвигов | 1986 |

|

SU1352401A2 |

| Широкодиапазонный калибратор фазовых сигналов | 1984 |

|

SU1226339A1 |

| Калибратор фазы | 1982 |

|

SU1048424A1 |

| Регулируемая мера фазовых сдвигов | 1983 |

|

SU1129552A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

Изобретение относится к электроизмерительной технике. Может быть использовано для получения двух гармонических сигналов с заданными фазовыми соотношениями в широком диапазоне частот. Цель изобретения - повышение точности задания дискретных значений фазовых сдвигов в широком диапазоне частот. Устройство содерЛля ЯГОГ жит генератор 1 тактовых импульсов, блок 2 записи кодов, каналы 3, 4 - опорный и фазопеременный соответственно. Канал 3 содержит пересчетный блок 5, постоянное запоминающее устройство 6, регистр 7, цифроаналого- вый преобразователь 8, фильтр 9 нижних частот (НЧ). Канал 4 содержит пересчетный блок 10, m постоянных запоминающих устройств 11.1-11.т, r-m - входовых логических элементов ИЛИ 12.1-12.г, регистр 14, цифроана- логовый преобразователь 15, фильтр 16 НЧ, блок 17 управления. Для достижения поставленной цели в канал 4 введены блок 16 поправок, сумматор 13, образованы новые функциональные связи. Устройство позволяет регулировать фазовый сдвиг с малым дискретом при высокой точности задания в области частот сотен кГц и выше, что обеспечивает повьппение точности определения основной погрешности фазо- измерительной аппаратуры. 2 ил. (Л с to со О5 СО О5 ю Suatm fiat/

| Мера фазового сдвига | 1983 |

|

SU1103156A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Научное приборостроение и автоматизация научного эксперимента | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-29—Подача