дов которых соединены с входами соответственно первого и второго преобразователей кода данных, выходы Wk8lt2t4 соответственно первого и второго цифро-аналоговых преобразователей. . разрядов которых соединены с входами

| название | год | авторы | номер документа |

|---|---|---|---|

| Калибратор фазы | 1983 |

|

SU1138761A1 |

| Устройство для поверки фазометров | 1982 |

|

SU1057877A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Калибратор параметров качества трехфазной цепи | 1980 |

|

SU957184A1 |

| Программный генератор | 1983 |

|

SU1251292A2 |

| Скважинный инклинометр | 1990 |

|

SU1721225A1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов при исследовании сердечно-сосудистой системы | 1982 |

|

SU1157547A1 |

| Калибратор фазы | 1988 |

|

SU1647449A1 |

| Преобразователь кодов | 1974 |

|

SU548857A1 |

КАЛИБРАТОР ФАЗЫ, содержащий задающий генератор, два постоянных запоминающих элемента, два фильтра нижних частот, первый и второй цифро-аналоговые преобразователи, выходы которых соединены соответственно с входами первого и второго фильтров нижних частот, выходы которых подключены соответственно к первому и второму выходам калибратора фазы, отличающийся тем, что, с целью повышения быстродействия, в него введены четыре .сумматора, регистр, два многоразрядных -элемента И, два элемента сравнения кодов, два преобразователя кода адреса и два преобразователя кода данных, причем первые входы первого сумматора подключены к шине кода М калибратора фазы, вторые входы первого сумматора соединены с выходами второго сумматора, а выходы первого сумматора подключены к входам регистра и первым входам первого элемента сравнения кодов, вторые входы которого соединены с шиной кода N калибратора фазы, а выход первого элемента сравнения кодов подключен к управляющему входу первого многоразрядного элемента И, информационные входы которого подключены к шине дополнительного кода Ник информационным входам второго многоразрядного элемента И, а выходы первого многоразрядного элемента. И соединены с первыми входами второго сумматрра, вторые входы которого подключены ко вхо дам первого преобразователя кода ад-. реса, к первым входам третьего сумматора и к выходам региЪтра, вход записи которого подключен к выходу задающего генератора и к первым упi 1равляющим входам первого и второго пр ёобразователей кода данных, вторые (Л входы третьего сумматора соединены с шиной кода Ntf калибратора фазы, а выходы третьего сумматора подключены к первым входам четвертого сумматора и второго элемента сравнения кодов, вторые входы которого соединены с шиной кода N калибратора {)азы, а выход второго элемента сравнения кодов подключен к управля4 ющему входу второго многоразрядного 00 элемента И, выходы которогоподклюUib чены к вторым входам четвертого сум1чЭ матора, выходы которого соединены с 4 , входами второго преобразователя кода адреса,-управляющие выходы первого и второго преобразователей кода адреса соединены с вторыми управляющими входами соответственно первого |И второго преобразователей кода данных, а выходы разрядов первого и второго преобразователей кода адреса подключены к адресным входам соответственно первого и второго постоянных запоминающих элементов, выходы разря-.

1

Изобретение относится к импульсной и радиоизмерительной технике и может быть использовано для построения калибраторов фазы низкочастотного и инфранизкочастотного диапазона.

Известен измерительный двухфазный генератор (калибратор фазы), содержащий два канала - опорный и фазопеременны, включающие последовательно соединенные первый и второй счетчики-делители частоты, реверсивный распределитель импульсов, ПЗУ, вычислительное устройство, ЦАП, ФНЧ, усилитель и аттеннюато.р, а также бло управления, сое/синенный с вторым счечиком-делителем частоты, ПЗУ, вычислительным устройством и ЦАП, обгцие для обоих каналов блок сравнения кодов с подключенным к нему блоком задания кода фазового сдвига, последовательно соединенные блок управления частотой, генератор сетки частот и распределитель импульсов, который первым выходом подключен ко входу первого счетчйка делителя частоты и блока управления опорного канала, а другими выходами через переключатель соединен с соответствующими элементами фазопеременного канала и входом блока сравнения кодов, который также соединен с выходами счетчиков-делителей частоты опорного канала и входами устамовки нуля счетчиков-делителей частоты фазопе ременного канала l.

Данное устройство требует.большого объема ПЗУ для хранения всех отсчете гармонического сигнала, соответствующих его периоду, имеет большое время установления фазы выходного сигнала (не менее одного периода), что в диапазоне инфраниэких частот может составлять единицы сотни секунд. Кроме того, количество считываемых точед гармонического сигнала здесь постоянно в диапазоне рабочих частот и выбирается исходя

из необходимого дискрета изменения фазы на верхней частоте диапазона. Этим ограничивается возможность улучшения формы сигнала на низких частотах путем увеличения числа считываемых точек по мере понижения частоты сигнала, -а также возможность расширения частотного диапазона в область верхних частот путем уменьшения числа считываемых точек сигнала по мере повышения частоты сигнала.

Наиболее близким по технической сущности к изобретению является цифровое устройство для воспроизведения фазовых сдвигов (калибратор фазы), содержащее два канала, включающих последовательно соединенные делитель частоты, реверсивный счетчик, постоянный запоминающий элемент, преобразователь код - напряжение, Re-цепь, общий для обоих каналов задающий генератор, соединенный выходом с делителями частоты и реверсивными счетчиками обоих каналов, выход Установка нуля первого делителя частоты соединен со входом Запись второго делитдля частоты, управляющие входы которого соединены с шиной кода фйзы, выходь Знак и, и Знак U2 первого и второго дилетелей частоты подключены к управляющим входам соответствующих преобразователей -код - напряжение. (Преобразователь код напряжениё и RC-цепь в дальнейшем целесообразнее называть как цифро-аналоговый преобразователь и фильтр нижних частот) zj.

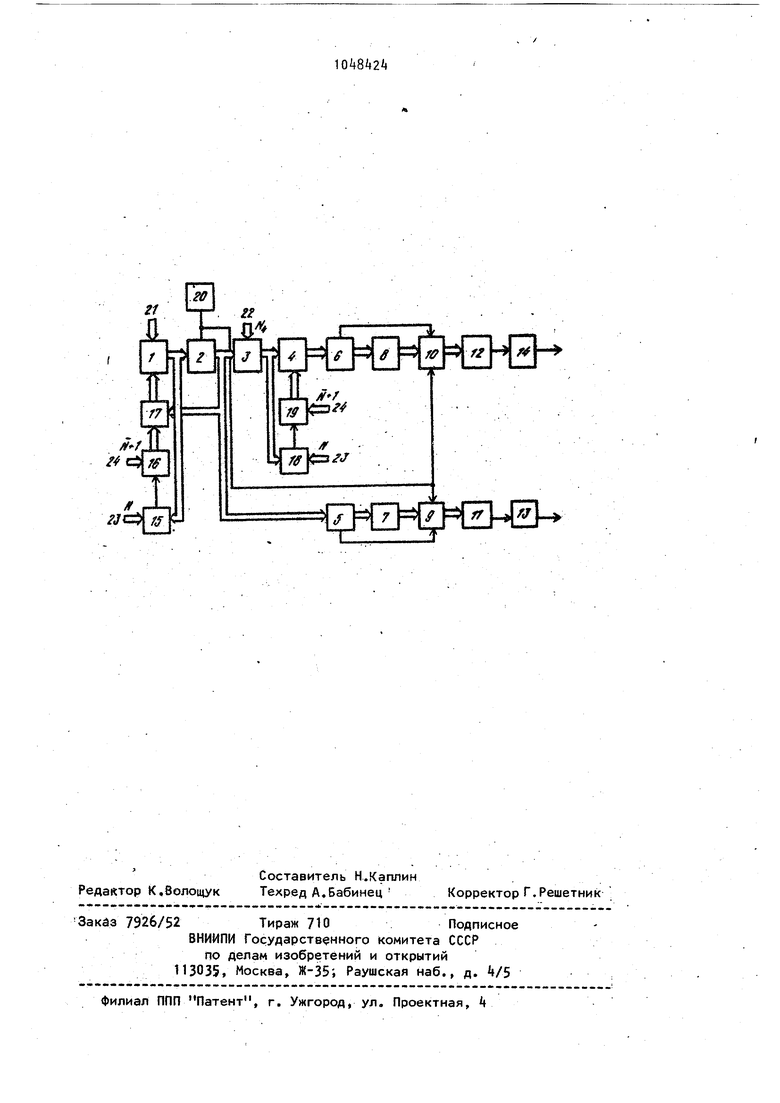

В известном устройстве в ПЗУ хранятся значения синусоидальной функции для одного квадранта, а код фазы задается путем предустановки второго делителя часготы в момент времени, когда текущий код первого делителя частоты равен йулю. При этом время установления фазы велико, а постоян:ство числа счить1вае|«)1х точек ограниЫивает возможности расширения частотНОГО диапазона. Указанные недостатк снижают быстродействие устройства. Цель изобретения - повышение быс родействия.. Поставленная цель достигается те что в калибратор фазы, содержащий задающий генератор, два постоянных запоминающих элемента, два фильтра нижних частот, первый и вто рой цифро-аналоговые преобразовател выходы которых соединены соответственно с входами первого и второго фильтров нижних частот, выходы кото рых подключены соответственно к пер вому и второму выходам калибратора фазы, введены четыре сумматора, регистр, два многоразрядных элемента И, два элемента сравнения кодов, два преобразователя кода адреса и два преобразователя кода данных,пр чем первые входы первого сумматора подключены к шине кода М калибратор .фазы, вторые входы первого сумматор соединены с выходами второго сумматора, а вь(ходы первого сумматора подключены к входам регистра и первым входа; 1 первого элемента сравнения кодов, вторые, входы которого соединены с шиной кода N калибратора фазы, а выход первого элемента сравнения кодов подключен к управляющему входу первого многоразрядного элемента И, информационные входы которого подключены к шине до полнительного кода N и к информационным входам второго многоразрядного элемента И, а выходы первого многоразрядного элемента И соединены с первыми входами второго сумматора, вторые входы которого подключены ко входам первого преобразователя кода адреса, к первым вход третьего сумматора и к выходап регистра, вход записи которого подключен к выходузадающего генератора и к первым управляющим входам пер вого и второго преобразователей кода данных, вторые входы третьего сумматора соединены с шиной кода N калибратора фазы, а выходы третье го сумматора подключены к перрым входам четвертого сумматора и второго элемента сравнения кодов, вторые входы которого соединены с шиной кода N калибратора фазы, а выход второго элемента сравнения кодов под ключен к управляющему входу второго многоразрядного элемента И, выходы которого подключены к вторым входам четвертого сумматора, выходы которого соединены с входами второго пре- , обраэователя кода адреса, управляющие выходы первого и второго преобразователей кода, адреса соединены с вторыми управляющими входами соответственно первого и второго преобразователей кода данных, а выходы разрядов первого и второго преобразователей кода адреса подключены к адресным входам соответственно первого и второго постоянных запоминающих элементов, выходы разрядов которых соединены с входами соответственно первого и второго преобразователей кода данных, выходы разрядов которых соединены с входами соответственно первого и второго цифро-аналоговых преобразователей. На чертеже приведена блок-схема калибратора. Калибратор фазы содержит последовательно соединенные первый сумматор , 1, регистр 2, третий сумматор 3, четвертый сумматор 4, последовательно соединенные в обоих каналах первый и второй преобразователи 5 и 6 .кода адреса, первые и вторые постоянные запоминающие элементы 7 И 8, первый и второй преобразователи 9 и 10 кода данных, первый и второй цифро-аналоговые преобразователи 11 и 12 и первый и второй фильтры.нижних частот 13 и Н, последовательно соединенные первый элемент 15 сравнения кодов, первый многоразрядный элемент 16 И и второй сумматор 17, последовательно соединенные второй элемент 18 сравнения кодов и второй многоразрядный, элемент 19 И, а также .задающий генератор 20, .соединенный с регистром 2, который связан выходами с вторыми входами второго сумматора 17 и первого преобразователя 5 кода адреса, входы второго преобразователя 6 кода адреса соединены с выходами четвертого сумматора 4, вторые входы которого подключены к выходам второго.многоразрядного элемента 19 И, выходы разрядов первого и третьего сумматоров 1 и 3 соединены с 1Входами соответственно первого 15 и второго 18 элементов сравнения кодов, первый и второй входы соответственно первого и третьего сумматоров 1 и 3 соединены соответственно с шиной 21 кода М и шиной 22 кода Щ, вторые входы первого и второго элементов

15 и 18 сравнения кодов соединены с иной 23 кода N, а информационные ходы первого и второго многоразрядых элементов 16 и 19 И соединены с шиой дополнительного кода уисла N. 5

Устройство работает следующим обазом.

Допустим, на первые входы первого сумматора 1 с шины 21 подан код , а регистр 2 находится в нулевом на- О чальном состоянии. Так как входной код первого сумматора 1 при этом еньше N, где N - максимальное число считываемых точекзаданной (синусоидальной) функции сигнала за период, 15 то на выходе первого элемента 15 сравненйя кодовбудет логический нуль, которому соответствуют нулевые уровни на выходах разрядов первого многоразрядного элемента 1б И и вто 20 рого сумматора 17 а на выходах разрядов первого сумматора 1 будет двоичный код единицы. Выходы разрядов регистра 2 соединены с входами первого преобразователя 5 кода адреса не- 25 посредственно и с входами второго преобразователя 6 кода адреса через третий и четвертый сумматоры 3 и j. С помощью этих сумматоров и связанных с ними второго элемента 18 сравне- 30 ния кодов и второго многоразрядного элемента 19 И задается фазовый сдвиг. . между выходными сигналами первого и второго каналов, определяемый двоичным кодом Ny, подаваемым с шины 22 35 на вторые входы третьего сумматора 3. Этот код суммируется с выходным кодом регистра 2 и поступает на первые входы четвертого сумматора 4 и второго элемента 18 сравнения кодов. 40 Если суммарный код меньше N, то на вторые входы четвертого сумматора 4 с выходов разрядов второго многоразрядного элемента 19 И подается нулевой код и таким образом выходной код 45 третьего сумматора 3 без изменения поступает на входы второго преобразователя 5 кода адреса, .

С помощью первого и второго преобразователей 5 и 6 кода адреса определяется номер квадранта синусоидальной функции и преобразование кодов адресов считываемых ячеек первого и второго постоянных запоминакш)их элементов 7 и 8, где записаны N/A зна- 55 чений синусоидальной функции в пер- , вом квадранте (0-90°). При этом впервом и третьем квадрантах выходные

коды первого и второго преобразователей 5 и 6 линейно возрастают от нуля до () в соответствии с выходными кодами регистра 2 и четвертого сумматора , а во втором и четвертом квадрантах - линейно убывают от () до нуля. Первый и второй-преобразователи 5 и 6 кода адреса управляют также соответствующими первыми и вторыми преобразователями кода данных, с помощьк} которых преобразуются выходные коды первого и второго постоянных запоминающих элементов 7 и 8. При этом в первом и втором квадрантах к выходным кодам первого и второго постоянных запоминающих элементов 8 и 7 прибавляется единица, а в третьей и четвертом квадрантах эти коды преобразуются в обратн код. В результате на входы первого и второго цифро-аналоговых преобразователей 11 и 12 поступают коды значений синусоидальной функции

U|(nT)sin((),)+1, и(пТ|) )+1,

где Tg - период дискретизации, определяемый частотой задающего генератора; ,1.,.; . F - частота сигнала. Амплитуда сигналов на выходах первого и второго цифро-аналоговых преобразователей 11 и12 определяются уровнем эталонного напряжения U,p а исключение постоянной составляющей из выходного сигнала осуществляется с помощью операционного усилителя, подключаемого к выходам первого и. второго цифро-аналоговых преобразователей (на чертеже не показаны, так как они входят в состав цифроаналоговых пйобразователей). Отсутствие коммутации полярности эталонного напряжения первого и второго цифро-аналоговых преобразователей 11 и 12 по сравнению с прототипом повысит точность преобразования и

быстродействие устройства,

I ., .

Выходные сигналы цифро-аналоговых преобразователей ступенчатой формы отфильтровываются от высших гармоник С помощью перврго и второго фильтров 13 и Н нижних частот и поступают на выходы устройства (практически к выходам ФНЧ подключаются также усилитель и управляемый аттенюатор, которые обеспечивают усйление мощности сигналов и-заданное ослабление их уровней). Считывание очередного отсчета вы ходного сигнала с выходов первого и второго постоянных запоминающих элементов 7 и 8 и занесение его в . регистры памяти первого и второго преобразователей 9 и ТО производится с частотой задающего генератора 20. Под действием импульсов этого генератора осуществляется запись вы ходного кода первого сумматора 1 в регистр 2, в результате чего выходные коды второго 17 и первого 1 сум маторов увеличиваются на единицу (при ). Также на единицу увеличиваются и выходные коды третьего 3 и четвертого k сумматоров,- в результате чего адрес считываемой яче ки первого и второго постоянных запоминающих элементов 7 и 8 изменя ется на единицу (увеличивается или уменьшается в зависимости от номера квадранта) ,, а ее .содержимое поступает в первый и второй преобразователи 9 и 10 кода данных для формирования отсчета выходного сигнала. В следующем такте процессы повторяются. При достижении выходным кодом первого или третьего сумматоров 1 и 3 з начения N срабатывают первый и второй элементы 15 и 18 ср нения кодов и открывают первый и вт рой многоразрядные элементы 16 и 19 И, на выходах разрядов которых появляется дополнительный код числа -равней N+1, задаваемый с шины 2, где М - обратный код числа N. Этот КОД складывается в четвертом суммато ре 17 с выходным кодом регистра 2 или третьего сумматора 3, в результате чего На выходах второго и четве того сумматоров 17 и k код уменьшит ся на величину N. Таким образом, на выходах регистра 2 и четвертого сумматора k формируется текущий код, изменяющийся в пределах (0-N-1), используемый для формирования кода адреса, принимающего значения ( на выходах разрядов первого и второ го преобразователей 5 и 6 кода адреса. При этом за период сигнала считываются все N значений синусоидальной функции, N/ значений которой для первого квадранта записаны в пер- вом и втором постоянных запоминающих элементах 7 и 8. Частота выходного 2k8 сигнала в этом случае определяется ; как F fjj/N. Ее верхнее значение ог.раничивается быстродействием постоянных запоминающих устройств и цифро.аналоговых преобразователей, имеющих по сравнению с другими элементами устройства наименьшее бь1стродействие. Для расширения вверх частотного диапазона и повышения тем самым быcтpoдeйctвия устройства можно уменьшить число считываемых точек сигнала путем задания кода М, подаваемого с шины 21 на вторые входы первого сумматора 1. При этом выходной код этого сумматора и регистра 2, а также код четвертого сумматора уве- личивается в каждом такте на число М и соответственно на эту же величину изменяется адрес очередной ячейки первого и второго постоянного запоминающего элемента и 8, с которой считывается значение синусоидальной функции. В результате количество считываемых точек уменьша- . ется в М раз, а частота выходного сигнала возрастает в М раз и становится равной F -jff4. Очевидно, что рас-./ ширение частотного диапазона достигается без уменьшения дискрета и изменения фазы, когорые определяются какйС 360/N. Минимальное число считываемых точек и соответственно максимальное значение М ограничивается погрешностью задания фазового сдвига и уровнем искажений выходного сигнала. Предложенное устройство имеет малое время установления фазы сигнала, поскольку выходной сигнал с : заданным фазовым сдвигом формируется сразу после установки кода фазового сдвига. В прототипе для этого требуется время в пределах периода сигнала, составляющее на инфранизких частотах до десятков-сотен секунд. При автоматическом управлении кодом фазы необходимое для ее изменения время в предлагаемом устройстве мойсет составлять единицы микросекунд. Быстродействие устройства повышается также за счет повышения верхней граничной частоты в 10-20 раз без. увеличения дискрета задаваемого фазового сдвига. Предлагаемый калибратор фазы не имеет методических oi- раничений на нижнюю рабочую частоту.

//

-:№

Л/с:$ р.

Авторы

Даты

1983-10-15—Публикация

1982-05-28—Подача