Изобретение относится к робототехнике и может быть применено для регулирования скорости электроприводов промышленных роботов, а также для управления любыми другими инерционными объектами.

Известен интегральный регулятор, содержащий измеритель рассогласования, соединенный выходом через пропорциональный блок и дифференциатор с входами сумматора, подключенного выходом к входу интегратора(книга Оппельта. Малый справочник технических процессов регулирования. Берлин: Техника, 1964, с. 529).

Недостатком такого регулятора является низкое качество регулирования из-за постоянного присутствия интегральной составляющей в законе регулирования.

Известен также интегральный регулятор, содержащий измеритель рассогласования, соединенный выходом через пропорциональньш блок и управляемый интегратор с ключом с входами сумматора, причем выход измерителя рассогласования подключен через пороговый блок к управляющему входу ключа управляемого интегратора отключающего интегральную составляющую закона регулирования (заявка ФРГ № 2354916, кл. G 05 В П/12, 1980).

Недостатком этого регулятора является низкое качество регулирования при наличии помех, которые приводят к нестабильности цепей регулирования регулятора.

Из известных регуляторов наиболее близким по технической сзгщности явля10

f5

Поставленная цель достигается теичто в интегральном регуляторе, содержащем последовательно соединенные измеритель рассогласования и управляемый интегратор с ключом, дополнительно установлены первый и второй одно- тактные детекторы, последовательно соединенные переключатель, первый однотактный детектор с зоной нечувствительности, первый сумматор, первый интегратор, первый пороговый блок и элемент ИЛИ и последовательно соединенные второй однотактный детектор с зоной нечувствительности, второй сумматор, второй интегратор и второй пороговый блок, подключенный выходом к второму входу элемента ИЛИ соединенного выходом с управляющими входами ключа управляемого интегратора и переключателя, подключенного информационным входом к выходу измерителя рассогласования, первым выходом - к входу второго однотактного детектора.с зоной нечувствительности а вторым выходом - к входам первого и второго однотактных детекторов, соединенных выходами с вторыми входами соответственно первого и второго сумматоров,, подключеннь1х выходами к входам сброса соответственно второго и первого интеграторов.

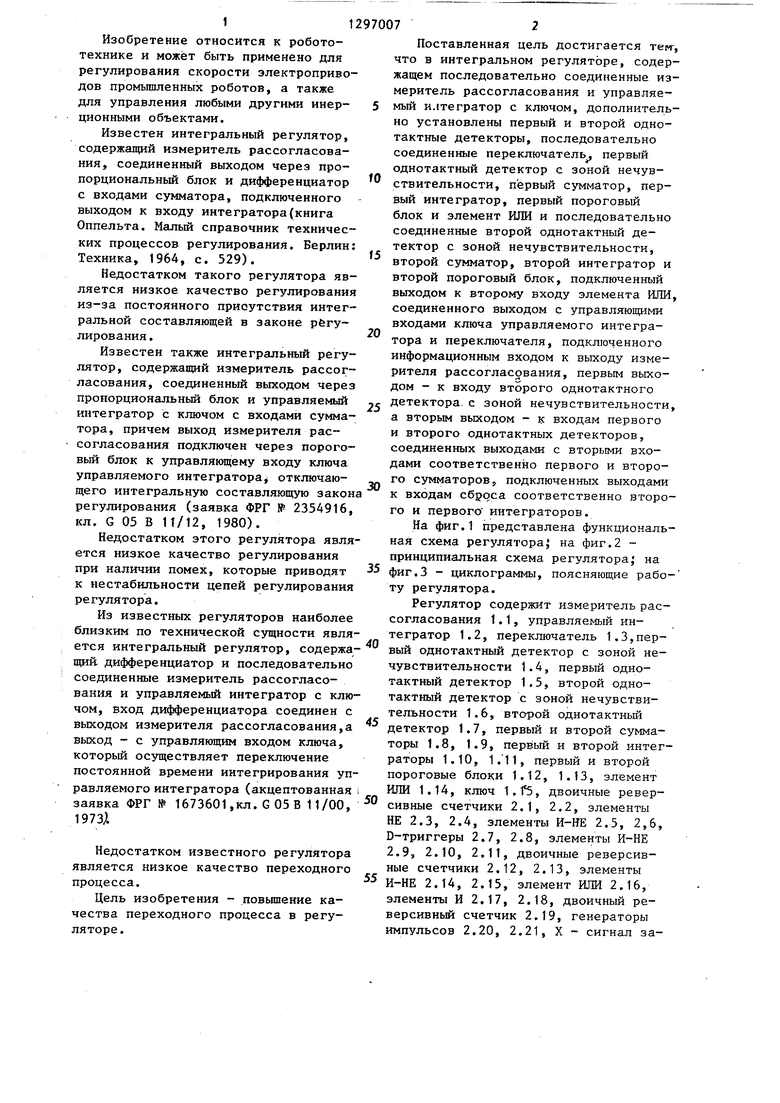

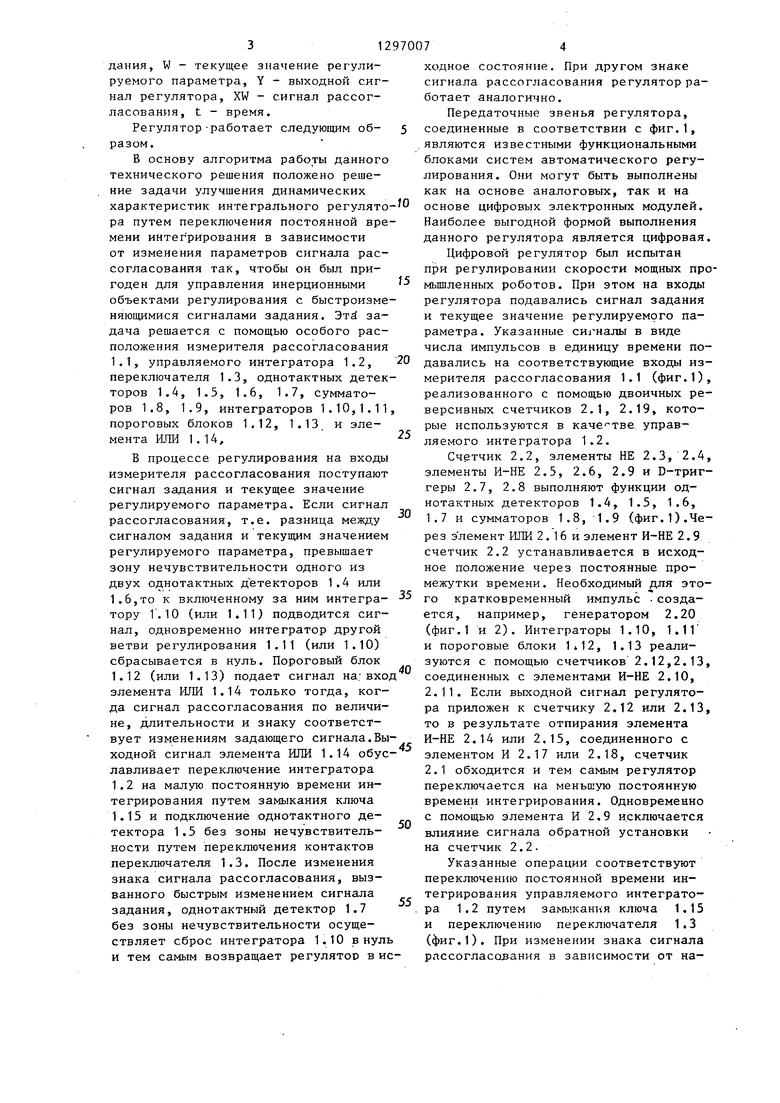

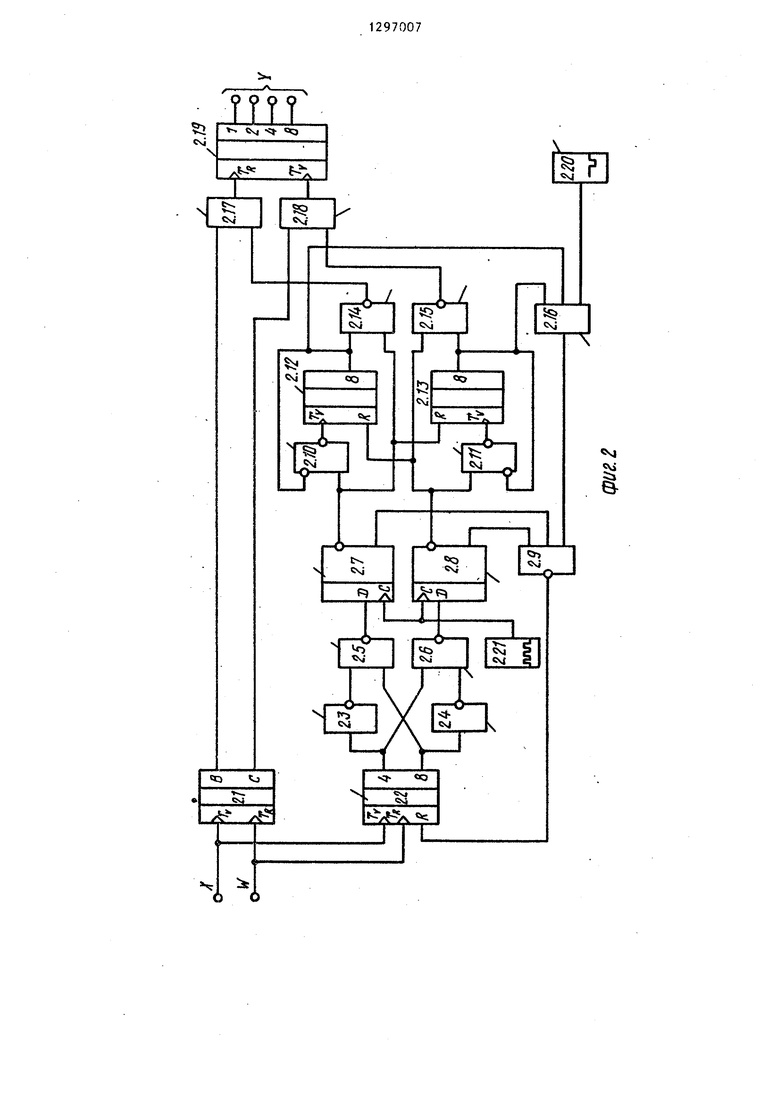

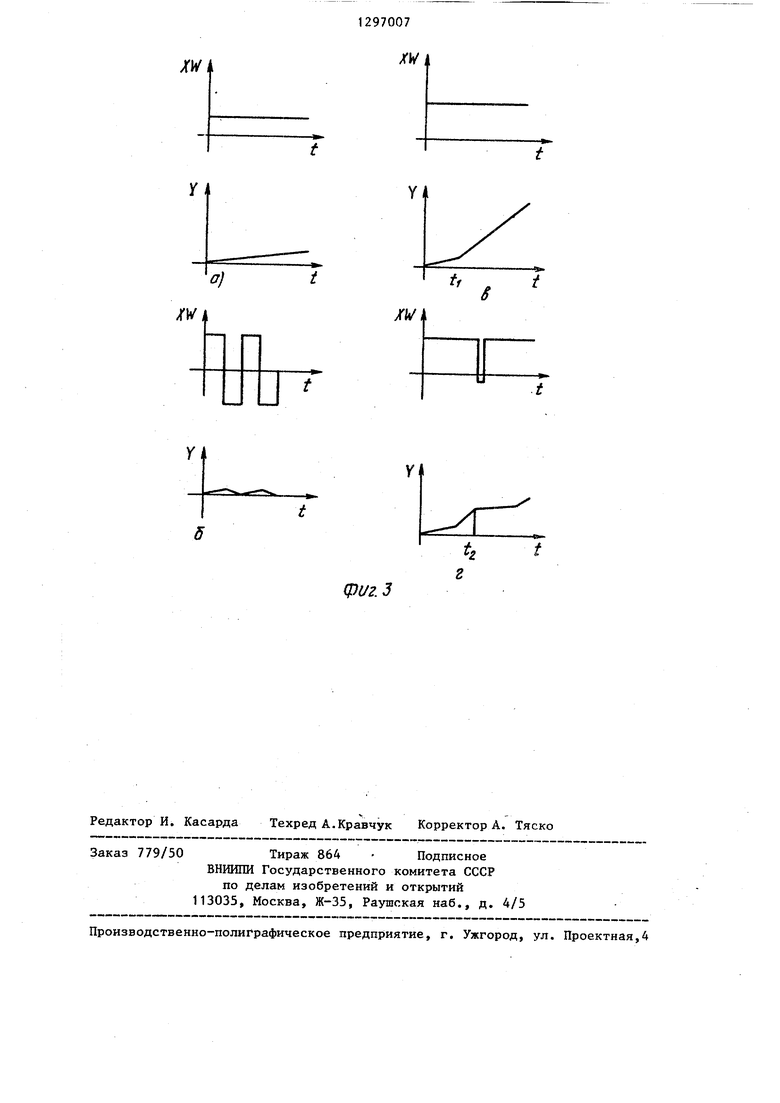

На фиг.1 представлена функциональная схема регулятора; на фиг.2 - принципиальная схема регулятора, на фиг.З - циклограммы, поясняющие работу регулятора.

Регулятор содержит измеритель рассогласования 1.1, управляемый интегратор 1.2, переключатель 1.3,пер20

25

30

ется интегральный регулятор, содержа- вый однотактный детектор с зоной не- щий. дифференциатор и последовательно чувствительности 1.4, первый одно- соединенные измеритель рассогласования и управляемый интегратор с клютактный детектор 1.5, второй однотактный детектор с зоной нечувствительности 1.6, второй однотактный детектор 1.7, первый и второй сумматоры 1.8, 1.9, первый и второй интеграторы 1.10, 1. 11, первый и второй пороговые блоки 1.12, 1.13, элемент ИЛИ 1.14, ключ 1., двоичные реверчом, вход дифференциатора соединен с выходом измерителя рассогласования,а выход - с управляющим входом ключа, которьй осуществляет переключение постоянной времени интегрирования управляемого интегратора (акцептованная

45

тактный детектор 1.5, второй однотактный детектор с зоной нечувствительности 1.6, второй однотактный детектор 1.7, первый и второй сумма торы 1.8, 1.9, первый и второй инте раторы 1.10, 1. 11, первый и второй пороговые блоки 1.12, 1.13, элемент ИЛИ 1.14, ключ 1., двоичные ревер

заявка ФРГ № 1673601,кл.G05 В 11/00, сивные счетчики 2.1, 2.2, элементы

1973А

Недостатком известного регулятора является низкое качество переходного процесса.

Цель изобретения - повьш1ение качества переходного процесса в регуляторе.

НЕ 2.3, 2.4, элементы И-НЕ 2.5, 2, D-триггеры 2.7, 2.8, элементы И-НЕ 2.9я 2.10, 2.11, двоичные реверсивные счетчики 2.12, 2.13, элементы И-НЕ 2.14, 2.15, элемент ИЖ 2.16, элементы И 2.17, 2.18, двоичный реверсивный счетчик 2.19, генераторы импульсов 2.20, 2.21, X - сигнал за

5

Поставленная цель достигается теи, что в интегральном регуляторе, содержащем последовательно соединенные измеритель рассогласования и управляемый интегратор с ключом, дополнительно установлены первый и второй одно- тактные детекторы, последовательно соединенные переключатель, первый однотактный детектор с зоной нечувствительности, первый сумматор, первый интегратор, первый пороговый блок и элемент ИЛИ и последовательно соединенные второй однотактный детектор с зоной нечувствительности, второй сумматор, второй интегратор и второй пороговый блок, подключенный выходом к второму входу элемента ИЛИ, соединенного выходом с управляющими входами ключа управляемого интегратора и переключателя, подключенного информационным входом к выходу измерителя рассогласования, первым выходом - к входу второго однотактного детектора.с зоной нечувствительности, а вторым выходом - к входам первого и второго однотактных детекторов, соединенных выходами с вторыми входами соответственно первого и второго сумматоров,, подключеннь1х выходами к входам сброса соответственно второго и первого интеграторов.

На фиг.1 представлена функциональная схема регулятора; на фиг.2 - принципиальная схема регулятора, на фиг.З - циклограммы, поясняющие рабо ту регулятора.

Регулятор содержит измеритель рассогласования 1.1, управляемый интегратор 1.2, переключатель 1.3,пер0

5

0

вый однотактный детектор с зоной не- чувствительности 1.4, первый одно-

тактный детектор 1.5, второй однотактный детектор с зоной нечувствительности 1.6, второй однотактный детектор 1.7, первый и второй сумматоры 1.8, 1.9, первый и второй интеграторы 1.10, 1. 11, первый и второй пороговые блоки 1.12, 1.13, элемент ИЛИ 1.14, ключ 1., двоичные реверсивные счетчики 2.1, 2.2, элементы

НЕ 2.3, 2.4, элементы И-НЕ 2.5, 2,6, D-триггеры 2.7, 2.8, элементы И-НЕ 2.9я 2.10, 2.11, двоичные реверсивные счетчики 2.12, 2.13, элементы И-НЕ 2.14, 2.15, элемент ИЖ 2.16, элементы И 2.17, 2.18, двоичный реверсивный счетчик 2.19, генераторы импульсов 2.20, 2.21, X - сигнал за312

Дания, W - текущее значение регулируемого параметра, Y - выходной сигнал регулятора, XW - сигнал рассогласования, t - время.

Регулятор-работает следующим об- разом.

В основу алгоритма работы данного технического решения положено решение задачи улучшения динамических характеристик интегрального регулято ра путем переключения постоянной времени интег рирования в зависимости от изменения параметров сигнала рассогласования так, чтобы он был пригоден для управления инерционными объектами регулирования с быстроизме няющимися сигналами задания. Эти задача решается с помощью особого расположения измерителя рассогласования 1.1, управляемого интегратора 1.2, переключателя 1.3, однотактных детекторов 1.4, 1.5, 1.6, 1.7, сумматоров 1.8, 1.9, интеграторов 1.10,1.11 пороговых блоков 1.12, 1.13 и элемента ИЛИ 1.14,

В процессе регулирования на входы измерителя рассогласования поступают сигнал задания и текущее значение регулируемого параметра. Если сигнал рассогласования, т.е. разница между сигналом задания и текущим значением регулируемого параметра, превышает зону нечувствительности одного из двух однотактных детекторов 1.4 или 1.6,то к включенному за ним интегра- тору 1. 10 (или 1.11) подводится сиг

нал, одновременно интегратор другой ветви регулирования 1.11 (или 1.10) сбрасывается в нуль. Пороговый блок 1.12 (или 1.13) подает сигнал на; вход элемента ИЛИ 1.14 только тогда, когда сигнал рассогласования по величине, длительности и знаку соответствует изменениям задающего сигнала.Выходной сигнал элемента ИЛИ 1.14 обуславливает переключение интегратора 1.2 на малую постоянную времени интегрирования путем замыкания ключа 1.15 и подключение однотактного детектора 1.5 без зоны нечувствительности путем переключения контактов переключателя 1.3. После изменения знака сигнала рассогласования, вызванного быстрым изменением сигнала задания, однотактный детектор 1.7 без зонь нечувствительности осуществляет сброс интегратора 1.10 в нуль и тем самым возвращает регулятор в ис

0

5

0

ходкое состояние. При другом знаке сигнала рассогласования регулятор работает аналогично.

Передаточные звенья регулятора, соединенные в соответствии с фиг.1, являются известными функциональными блоками систем автоматического регулирования. Они могут быть выполнены как на основе аналоговых, так и на основе цифровых электронных модулей. Наиболее выгодной формой выполнения данного регулятора является цифровая.

Цифровой регулятор был испытан при регулировании скорости мощных промышленных роботов. При этом на входы регулятора подавались сигнал задания и текущее значение регулируемого параметра. Указанные сигналы в виде числа импульсов в единицу времени подавались на соответствующие входы измерителя рассогласования 1.1 (фиг.1), реализованного с помощью двоичных реверсивных счетчиков 2.1, 2.19, которые используются в каче тве управляемого интегратора 1.2.

Счетчик 2.2, элементы НЕ 2.3, 2.4, элементы И-НЕ 2.5, 2.6, 2.9 и D-триг- геры 2.7, 2.8 выполняют функции однотактных детекторов 1.4, 1.5, 1.6, 1.7 и сумматоров 1.8, 1.9 (фиг.1).Через э лемент ИЛИ 2. 16 и элемент И-НЕ 2.9 счетчик 2.2 устанавливается в исходное положение через постоянные промежутки времени. Необходимый для этого кратковременный импульс - созда

0

0

5

ется, например, генератором 2.20 (фиг.1 и 2). Интеграторы 1.10, 1.1 Г и пороговые блоки , 1.13 реализуются с помощью счетчиков 2.12,2.13, соединенных с элементами И-НЕ 2.10, 2.11. Если выходной сигнал регулятора приложен к счетчику 2.12 или 2.13, то в результате отпирания элемента И-НЕ 2.14 или 2.15, соединенного с элементом И 2.17 или 2.18, счетчик 2.1 обходится и тем самым регулятор переключается на меньшую постоянную времени интегрирования. Одновременно с помощью элемента И 2.9 исключается влияние сигнала обратной установки на счетчик 2.2.

Указанные операции соответствуют переключению постоянной времени интегрирования управляемого интегратора 1.2 путем зa a кaния ключа 1,15 и переключению переключателя 1.3 (фиг.1). При изменении знака сигнала рассогласования в зависимости от на-

правления изменения сигнала рассогласования устанавливается в исходное состояние интегратор 1.10 или 1.11, которые реализованы с помощью счетчиков 2.12 и 2.13 (фиг.2).Тем самым происходит переключение регулятора на большую постоянную времени интегрирования.

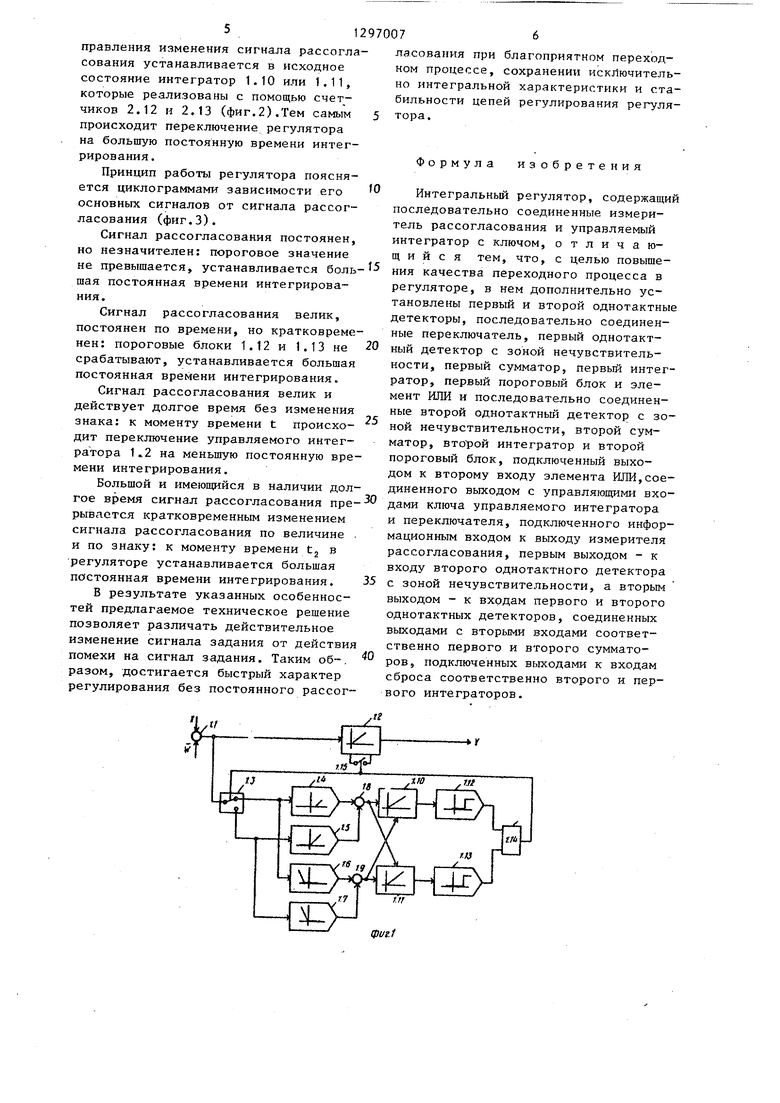

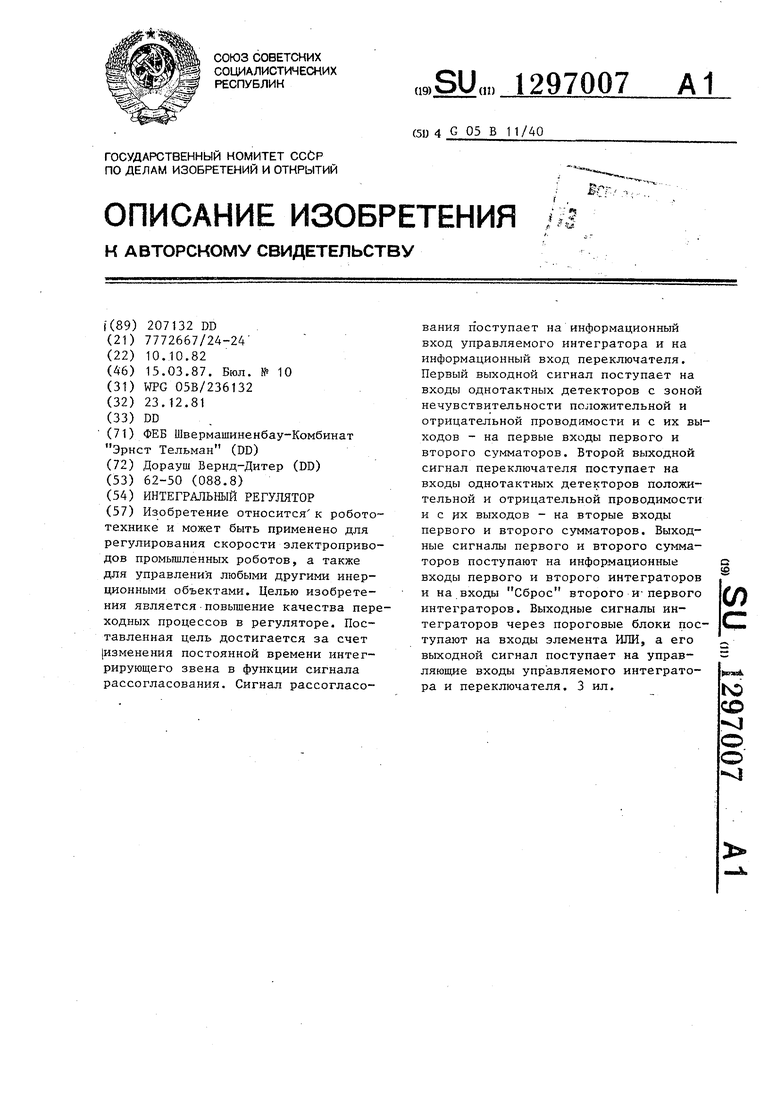

Принцип работы регулятора поясняется циклограммами зависимости его основных сигналов от сигнала рассогласования (фиг.З).

Сигнал рассогласования постоянен, но незначителен: пороговое значение

fO

ласования при благоприятном переходном процессе, сохранении исключитель но интегральной характеристики и ста бильности цепей регулирования регуля тора.

Формула изобретения

Интегральный регулятор, содержани последовательно соединенные измеритель рассогласования и управляемый интегратор с ключом, отличающийся тем, что, с целью повышене превышается, устанавливается боль- ния качества переходного процесса в

шая постоянная времени интегрирования.

Сигнал рассогласования велик, постоянен по времени, но кратковреме- нен: пороговые блоки 1.12 и 1.13 не срабатывают, устанавливается большая постоянная времени интегрирования.

Сигнал рассогласования велик и действует долгое время без изменения знака; к моменту времени t происходит переключение управляемого интегратора 1..2 на меньшую постоянную времени интегрирования.

Большой и имеющийся в наличии долгое время сигнал рассогласования пре рываотся кратковременным изменением сигнала рассогласования по величине и по знаку: к моменту времени t2 в регуляторе устанавливается большая постоянная времени интегрирования.

В результате указанных особенностей предлагаемое техническое решение позволяет различать действительное изменение сигнала задания от действия помехи на сигнал задания. Таким об-, разом, достигается быстрый характер регулирования без постоянного рассог

ласования при благоприятном переходном процессе, сохранении исключительно интегральной характеристики и стабильности цепей регулирования регулятора.

Формула изобретения

Интегральный регулятор, содержаний последовательно соединенные измеритель рассогласования и управляемый интегратор с ключом, отличающийся тем, что, с целью повышения качества переходного процесса в

20

25

35

30

регуляторе, в нем дополнительно установлены первый и второй однотактные детекторы, последовательно соединенные переключатель, первый однотакт- ный детектор с зоной нечувствительности, первый сумматор, первый интегратор, первый пороговый блок и элемент ИЛИ и последовательно соединенные второй однотактный детектор с зоной нечувствительности, второй сумматор, вто рой интегратор и второй пороговый блок, подключенный выходом к второму входу элемента ИЛИ,соединенного выходом с управляющими входами ключа управляемого интегратора и переключателя, подключенного информационным входом к выходу измерителя рассогласования, первым выходом - к входу второго однотактного детектора с зоной нечувствительности, а вторым выходом - к входам первого и второго однотактных детекторов, соединенных выходами с вторыми входами соответственно первого и второго сумматоров, подключенных выходами к входам сброса соответственно второго и первого интеграторов.

фиг.1

/I/

1297007 XW

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный регулятор | 1987 |

|

SU1532895A1 |

| Нелинейное корректирующее устройство | 1987 |

|

SU1536351A1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| УСТРОЙСТВО ЕМКОСТНОГО ТИПА ДЛЯ ОБНАРУЖЕНИЯ НАРУШИТЕЛЯ | 2015 |

|

RU2613759C1 |

| УСТРОЙСТВО ИМИТОЗАЩИТЫ ГРУППЫ КОНТРОЛИРУЕМЫХ ОБЪЕКТОВ | 2015 |

|

RU2595991C1 |

| СПОСОБ СЛИЧЕНИЯ ШКАЛ ВРЕМЕНИ | 2012 |

|

RU2507555C2 |

| Устройство для регулирования температуры | 1980 |

|

SU907514A2 |

| ИЗМЕРИТЕЛЬНЫЙ ПРИБОР | 1992 |

|

RU2067290C1 |

| Импульсный регулятор | 1984 |

|

SU1238025A1 |

| Регулятор относительного обжатия прокатываемой полосы | 1981 |

|

SU944696A1 |

Изобретение относится к робототехнике и может быть применено для регулирования скорости электроприводов промышленных роботов, а также для управления любыми другими инерционными объектами. Целью изобретения является повышение качества переходных процессов в регуляторе. Поставленная цель достигается за счет |изменения постоянной времени интегрирующего звена в функции сигнала рассогласования. Сигнал рассогласования поступает на информационный вход управляемого интегратора и на информационный вход переключателя. Первый выходной сигнал поступает на входы однотактных детекторов с зоной нечувствительности положительной и отрицательной проводимости и с их выходов - на первые входы первого и второго сумматоров. Второй выходной сигнал переключателя поступает на входы однотактных детекторов положительной и отрицательной проводимости и с их выходов - на вторые входы первого и второго сумматоров. Выходные сигналы первого и второго сумматоров поступают на информационные входы первого и второго интеграторов и на входы Сброс второго и-первого интеграторов. Выходные сигналы интеграторов через пороговые блоки поступают на входы элемента ИЛИ, а его выходной сигнал поступает на управляющие входы управляемого интегратора и переключателя. 3 ил. I (Л го со

ff/

Wt

Редактор И. Касарда Заказ 779/50

Техред А.Кравчук Корректор А. Тяско

Тираж 864 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

xw

Фи2.3

Авторы

Даты

1987-03-15—Публикация

1982-10-10—Подача