Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностирования интегральных логических микросхем и устройств, построенных на их основе.

Целью изобретения является повышение быстродействия.

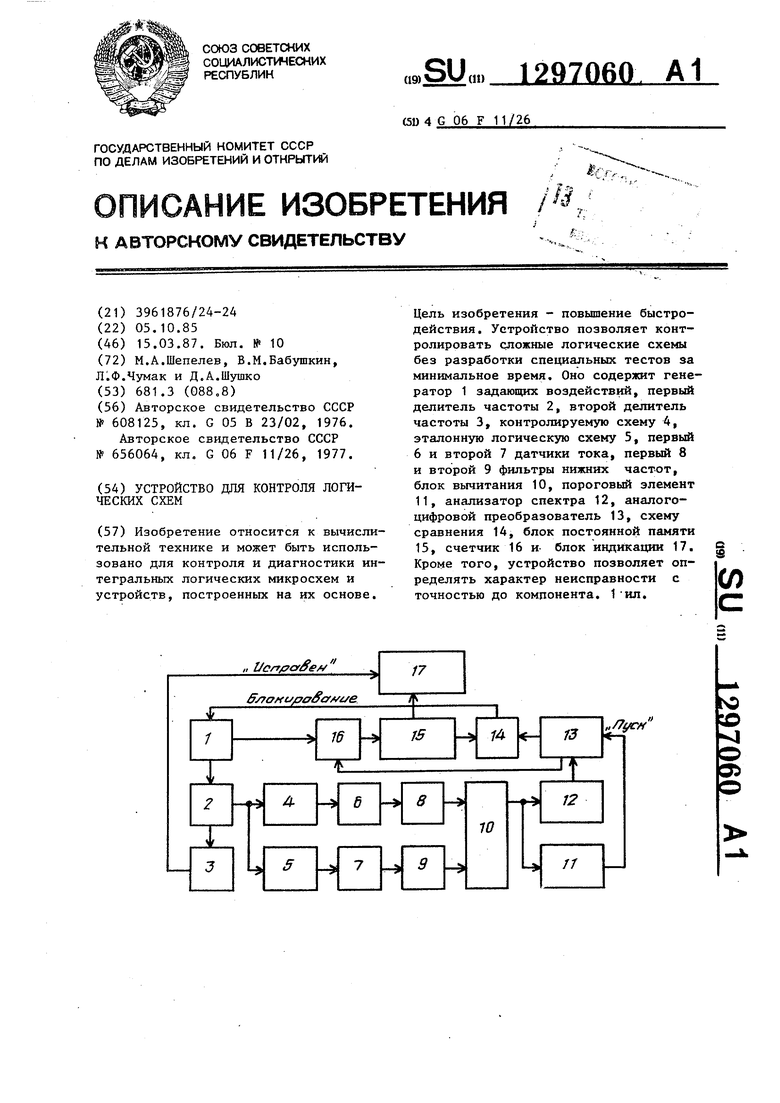

На чертеже показана структурная схема устройства.

Устройство содержит генератор 1 задающих воздействий, первый делитель частоты 2, второй делитель частоты 3, контролируемую схему 4, эталонную схему 5, первый 6 и второй 7 датчики тока, первый 8 и второй 9 фильтры нижних частот, блок вычитания 10, пороговый элемент 11, анализатор спектра 12, аналого-цифровой

10

сигнал, разрешающий работу счетчика 16, второй вход которого соединен с генератором 1 задающих воздействий. При этом счетчик начинает преобразовывать импульсный сигнал в двоичную последовательность, поступающую на адресные входы блока 15. Из блока 15 извлекается информация о возможных неисправностях контролируемой схемы, причем длина слова такова, что в первой половине его записана информация о возможной неисправности, а во второй - код неисправности.

необходимый для индикации результа- 5 тов в блоке индикации 17. При совпадении данных;, хранящихся в блоке 15, с данными, снимаемыми с АЦП 13, схема 14 сравнения вырабатьшает сигнал, блокирующий работу генератора 1 запреобразователь (АЦП) 13, схему срав- дающих воздействий. При этом блок нения 14, блок 15 постоянной памяти, 17 индикации индицирует характер несчетчик 16 и блок 17 индикации.

Устройство работает следующим образом.

Генератор 1 вырабатывает высокочастотный импульсный сигнал, который с помощью первого делителя частоты преобразуется в множество сигналов некратных частот. Каждый из этих сигналов поступает на соответствующий вход контролируемой схемы 4 и эталонной схемы 5. Первый 6 и второй 7 датчики тока вырабатывают сигналы, закон изменения которых соответствует изменениям тока в цепях контролируемой и эталонной логичес- ких схем соответственно. Первый 8 и второй 9 фильтры нижних частот производят фильтрацию сигналов с целью исключения высокочастотных импульсных помех. Блок вычитания 10 определяет разность между сигналами, снимаемыми с датчиков тока. Полученная разность значений сигналов поступает на входы порогового элемента 11 и анализатора спектра 12, При значении рассогласования, превышающем определенную величину, установленную заранее в виде порога срабатывания порогового элемента, на выходе последнего появляется логический сигнал, характеризующий наличие неисправности в схеме 4. Данный сигнал порогового элемента 11 является сигналом пуска для АЦП 13, входы которого соединены с выходами анализатора спектра 12. По окончании преобразования АЦП 13 вырабатьгоает

сигнал, разрешающий работу счетчика 16, второй вход которого соединен с генератором 1 задающих воздействий. При этом счетчик начинает преобразовывать импульсный сигнал в двоичную последовательность, поступающую на адресные входы блока 15. Из блока 15 извлекается информация о возможных неисправностях контролируемой схемы, причем длина слова такова, что в первой половине его записана информация о возможной неисправности, а во второй - код неисправности.

25

30

исправности. Если же.за время цикла, устанавливаемого в виде коэффициента деления делителя 3 частоты,в блок индикации не. поступают данные о характере неисправности, т.е, не срабатывает пороговый элемент, АЦП, счетчик и блок 15,то второй делитель 3 частоты формирует сигнал Испра- подаваемый в блок 17,

вен.

ормула изобретения

40

45

Устройство для контроля логических схем, содержащее генератор за35 дающих воздействий, первьй делитель частоты, анализатор спектра, схему сравнения, эталонную схему, блок ин- дикахщи, причем первый выход генератора задающих воздействий соединен с входом первого делителя частоты,первый выход которого подключен к входу эталонной схемы и является информационным выходом устройства для подключения к входу контролируемой схемы, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй делитель частоты, счетчик, два датчика тока, два фильтра нижних частот, блок вычитания, пороговый элемент, аналого-цифровой преобразователь и блок постоянной памяти, причем входы первого и второго датчиков тока подключены соответственно к ходу эталонной схемы и информационному входу устройства для подключени к выходу контролируемой схемы, выходы первого и второго датчиков тока

50

312970604

через соответствующие фильтры нижнихкода неисправности которого подклю- частот подключены к соответствующимчен к первому входу блока индикации, входам блока вычитания, выход разнос-второй вход которого подключен к вы- ти которого соединен с входами поро-ходу второго делителя частоты,вход гового элемента и анализатора спект- которого подключен к второму выходу ра, выход которого подключен к инфор-первого делителя частоты, выход ра- мационному входу аналого-цифровоговенства схемы сравнения соединен с преобразователя, вход запуска кото-входом блокировки генератора задаю- - рого подключен к выходу пороговогощих воздействий, второй выход кото- элемента, информационный выход ана- )0рого соединен с счетным входом счет- лого-цифрового преобразователя соеда -чика, вход разрешения которого соединен с первым входом схемы сравнения,нен с выходом конца преобразования второй вход которой соединен с выхо-аналого-цифрового преобразователя, дом информации о возможной неисправ-выход счетчика подключен к адресно- ностй блока постоянной памяти, выход 15му входу блока постоянной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1988 |

|

SU1624458A1 |

| Устройство для контроля логических схем | 1990 |

|

SU1718222A1 |

| Устройство для контроля группы логических узлов | 1985 |

|

SU1327109A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| Устройство для программного регулирования | 1979 |

|

SU930263A2 |

| Устройство для метрологической поверки цифровых вольтметров | 1982 |

|

SU1049847A1 |

| Устройство для программного регулирования | 1977 |

|

SU732814A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ ШТАНГОВЫХ НАСОСНЫХ УСТАНОВОК | 2009 |

|

RU2400647C1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики интегральных логических микросхем и устройств, построенных на их основе. Цель изобретения - повышение быстродействия . Устройство позволяет контролировать сложные логические схемы без разработки специальных тестов за минимальное время. Оно содержит генератор 1 задающих воздействий, первый делитель частоты 2, второй делитель частоты 3, контролируемую схему 4, эталонную логическую схему 5, первый 6 и второй 7 датчики тока, первый 8 и второй 9 фильтры нижних частот, блок вычитания 10, пороговый элемент 11, анализатор спектра 12, аналого- цифровой преобразователь 13, схему сравнения 14, блок постоянной памяти 15, счетчик 16 и блок индикации 17. Кроме того, устройство позволяет определять характер неисправности с точностью до компонента. 1 ил. О) /7 Э :о

| Устройство для контроля параметров | 1976 |

|

SU608125A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля логических схем | 1977 |

|

SU656064A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-05—Подача