Изобретение относится к автоматическому контролю логических узлов и может быть использовано в автоматизированных системах контроля логических узлов цифровых схем.

Целью изобретения является повышение точности контроля.

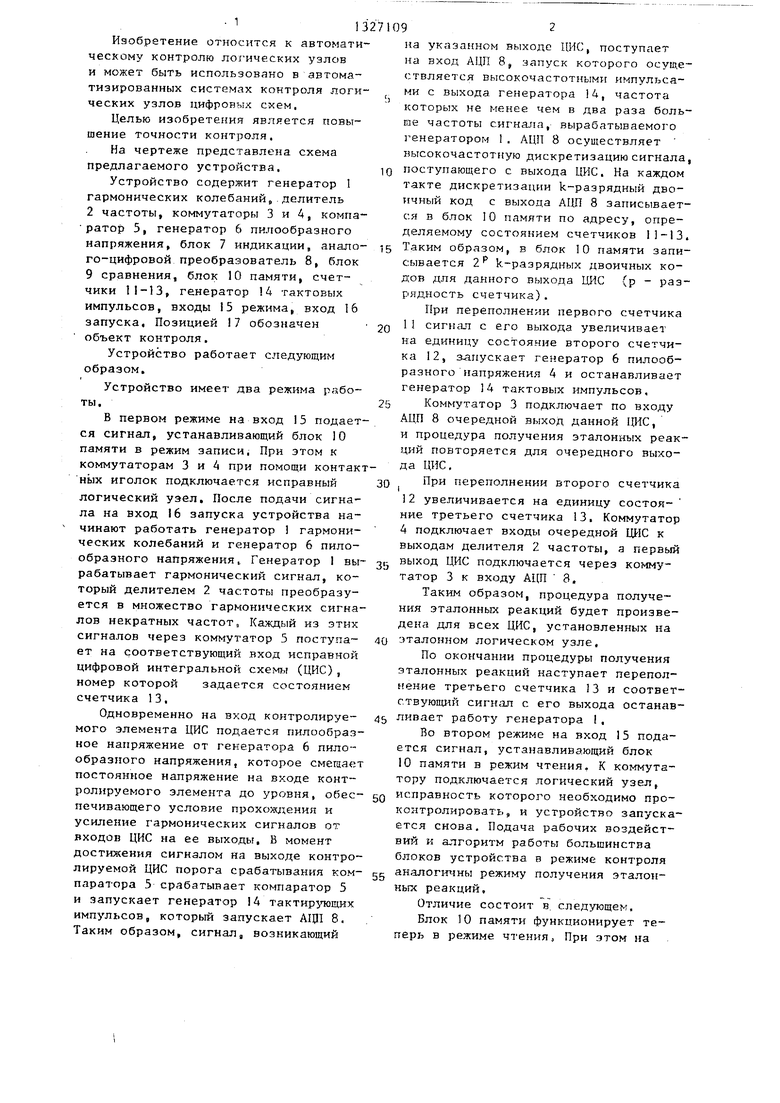

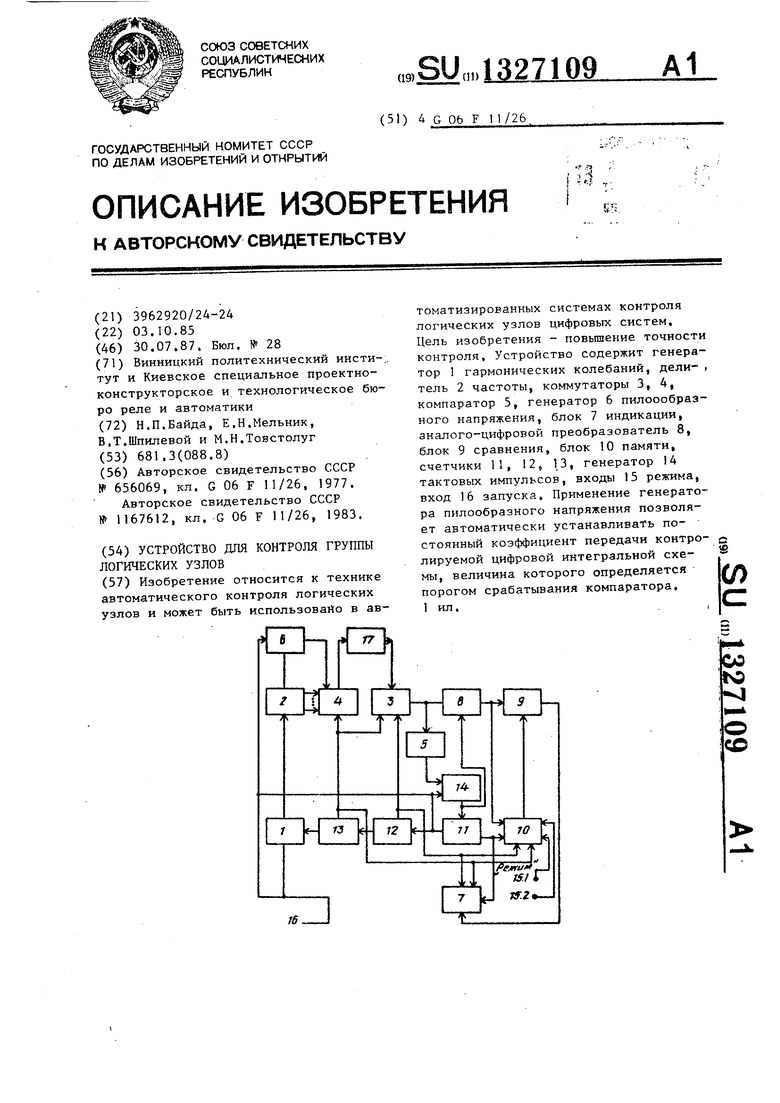

На чертеже представлена схема предлагаемого устройства.

Устройство содержит генератор I гармонических колебаний„ делитель 2 частоты, коммутаторы 3 и А, компаратор 5, генератор 6 пилообразного

напряжения, блок 7 индикации, анало- ig Таким образом, в блок 10 памяти записывается 2 k-раэрядных двоичных кодов для данного выхода ЦИС (р - разрядность счетчика).

го-цифровой преобразователь 8, блок 9 сравнения, блок 10 памяти, счетчики 11-13, генератор 14 тактовых импульсов, входы 15 режима, вход 16 запуска. Позицией 17 обозначен объект контроля.

Устройство работает следующим образом.

Устройство имеет два режима работы,

В первом режиме на вход 15 подается сигнал, устанавливающий блок 10 памяти в режим записи. При этом к коммутаторам 3 и 4 при помощи контакных иголок подключается исправный логический узел. После подачи сигна ла на вход 16 запуска устройства начинают работать генератор 1 гармони

12увеличивается на единицу состоя- ние третьего счетчика 13. Коммутатор 4 подключает входы очередной ЦИС к выходам делителя 2 частоты, а первый

ческих колебаний и генератор 6 пилообразного напряжения. Генератор 1 вы 35 Ь1ход ЦИС подключается через комму- рабатывает гармонический сигнал, ко- татор 3 к входу АЦП 3,

Таким образом, процедура получения эталонных реакций будет произведена для всех ЦИС, установленных на 40 эталонном логическом узле.

По окончании процедуры получения эталонных реакций наступает перепол- иение третьего счетчика 13 и соответ- ствуюпдай сигнал с его выхода останав- 45 ливает работу генератора ,

Во втором режиме на вход 15 подается сигнал, устанавливающий блок 10 памяти в режим чтения, К коммутатору подключается логический узел, ролируемого элемента до уровня, обес- 50 исправность которого необходимо про- печивающего условие прохождения и контролировать, и устройство запуска- усиление гармонических сигналов от ется снова. Подача рабочих воздейст- яходов ЦИС на ее выходы, В момент вий и алгоритм работы большинства

торый делителем 2 частоты преобразу ется в множество гармонических сигналов некратных частот, Каждый из этих сигналов через коммутатор 5 поступает на соответствующий вход исправной цифровой интегральной схемы (ЦИС), номер которой задается состоянием счетчика 13.

Одновременно на вход контролируемого элемента ЦИС подается пилообразное напряжение от генератора 6 пилообразного напряжения, которое смещает постоянное напряжение на входе контдостижения сигналом на выходе контролируемой ЦИС порога срабатывания компаратора 5 срабатывает компаратор 5 и запускает генератор 14 тактируюпщх импульсов, который запускает АЦП 8. Таким образом, сигнал, возникающий

на указанном выходе ЦИС, поступает на вход АЦП 8 запуск которого осуществляется высокочастотными импульсами с выхода генератора 14, частота которых не менее чем в два раза боль- те частоты сигнала, вырабатываемого 1 енератором 1 . АЦП 8 осуществляет высокочастотную дискретизацию сигнала, поступающего с выхода ЦИС, На каждом такте дискретизации k-разрядный двоичный код с выхода АЦП 8 записывается в блок 10 памяти по адресу, определяемому состоянием счетчиков М-13.

сывается 2 k-раэрядных двоичных кодов для данного выхода ЦИС (р - разрядность счетчика).

При переполнении первого счетчика

11сигнал с его выхода увеличивает на единицу состояние второго счетчика 12, аапускает генератор 6 пилообразного напряжения 4 и останавливает генератор 14 тактовых импульсов.

Коммутатор 3 подключает по входу АЦП 8 очередной выход данной ЦИС, и процедура получения эталонных реакций повторяется для очередного выхода ЦИС.

При переполнении второго счетчика

12увеличивается на единицу состоя- ние третьего счетчика 13. Коммутатор 4 подключает входы очередной ЦИС к выходам делителя 2 частоты, а первый

Ь1ход ЦИС подключается через комму- татор 3 к входу АЦП 3,

блоков устройства в режиме контроля ан;1погш ны режиму получения эталон- ньг реакций.

Отличие состоит в, следующем.

Блок 10 памяти функционирует теперь в режиме чтения. При этом на

1

каждом такте с выхода блока 10 памяти на входы блока 9 сравнения поступает код эталонной реакции. На вторые входы блока 9 сравнения поступает соответствующий двоичный код результата измерений. Равенство указанных кодов свидетельствует об исправности контролируемого выхода на данном такте сравнения,

Если на каком-либо такте происходит несравнение результата измерения с эталонной реакцией, то на выходе блока 9 сравнения формируется сигнал по которому в блоке 7 индикации фик- сируется точное место найденной неисправности: номер контролируемой в данный момент ЦИС, номер выхода и номер такта, на котором произошло несравнение,

Формула изобретения

Устройство для контроля группы логических узлов, содержащее блок памяти, первый, второй и третий счетчики, генератор гармонических колебаний, генератор тактовых импульсов, блок сравнения, аналого-цифровой преобразователь, первый и второй ком мутаторы, делитель частоты, причем выход переноса первого счетчика соединен с тактовым входом второго счетчика, вход запуска генератора гармонических колебаний является входом запуска устройства, первый и второй входы режима которого соединены соответственно с входами записи и чтения блока памяти, первая группа адресных входов которого сое- динена с первой группой управляющих входов первого коммутатора и с группой информационных выходов второго счетчика, выход переноса которого соединен с тактовым входом третьего счетчика, выход переноса которого соединен с входом останова генерато

Редактор Л.Веселовская

Составитель И,Иваныкин

Техред И.Попович Корректор Т.Колб

Заказ 3391/46Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Прои:зродственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

5 о

5 о „

5

09

ра гармонических колебаний, выход которого соединен с входом делителя частоты, группа выходов которого соединена с первой группой информационных входов второго коммутатора, группа управляющих входов которого соединена с второй группой управляющих входов первого коммутатора, с группой выходов третьего счетчика, с второй группой адресных входов блока памяти, информационные выходы которого соединены с первыми входами блока сравнения, третья группа адресных входов блока памяти соединена с группой выходов первого счетчика, тактовый -вход которого соединен с выходом генератора тактовых импульсов и с тактовым входом аналого-цифрового преобразователя, вход которого соединен с выходом первого коммутатора, группа информационных входов которого является группой информационных входов устройства для подключения к группе, выходов контролируемых логических узлов, группа выходов второго коммутатора является группой информационных выходов устройства для подключения к входам контролируемых логических узлов группы, группа выходов аналого-цифрового преобразователя соединена с второй группой входов блока сравнения и с группой информационных входов блока памяти, отличающееся тем, что, с целью повьщ1ения точности контроля, в него введены генератор пилообразного напряжения и компаратор, причем вькод первого коммутатора соединен с входом компаратора, выход которого соединен с входом пуска генератора тактовых импульсов, вход останова которого соединен с выходом переноса счетчика, с входом запуска генератора пилообразного напряжения, выход которого подключен к входу второго коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля группы логических схем | 1983 |

|

SU1167612A1 |

| Устройство контроля аналого-цифровых преобразователей | 1990 |

|

SU1757100A2 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Многоканальное измерительное устройство | 1988 |

|

SU1617430A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВАНИЯ ТЕЛЕВИЗИОННОЙ АППАРАТУРЫ | 1989 |

|

RU2050700C1 |

| Устройство для цифрового измерения мгновенной частоты | 1987 |

|

SU1415195A2 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

Изобретение относится к технике автоматического контроля логических узлов и может быть использовайо в автоматизированных системах контроля логических узлов цифровых систем. Цель изобретения - повышение точности контроля. Устройство содержит генератор 1 гармонических колебаний, дели- , тель 2 частоты, коммутаторы 3, 4, компаратор 5, генератор 6 пилоообраз- ного напряжения, блок 7 индикации, аналого-цифровой преобразователь 8, блок 9 сравнения, блок 10 памяти, счетчики 11, 12, 13, генератор 14 тактовых импульсов, входы 15 режима, вход 16 запуска. Применение генератора пилообразного напряжения позволяет автоматически устанавливать постоянный коэффициент передачи контро- с лируемой цифровой интегральной схемы, величина которого определяется порогом срабатывания компаратора. 1 ил., $ (Л б ф

| Устройство для преобразования систем координат | 1976 |

|

SU656069A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля группы логических схем | 1983 |

|

SU1167612A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1985-10-03—Подача