Изобретение относится к радиотехнике и может быть использовано в системах передачи частотно-модулировай- ных сигналов.

Цель изобретения - повышение точности умножения частоты.

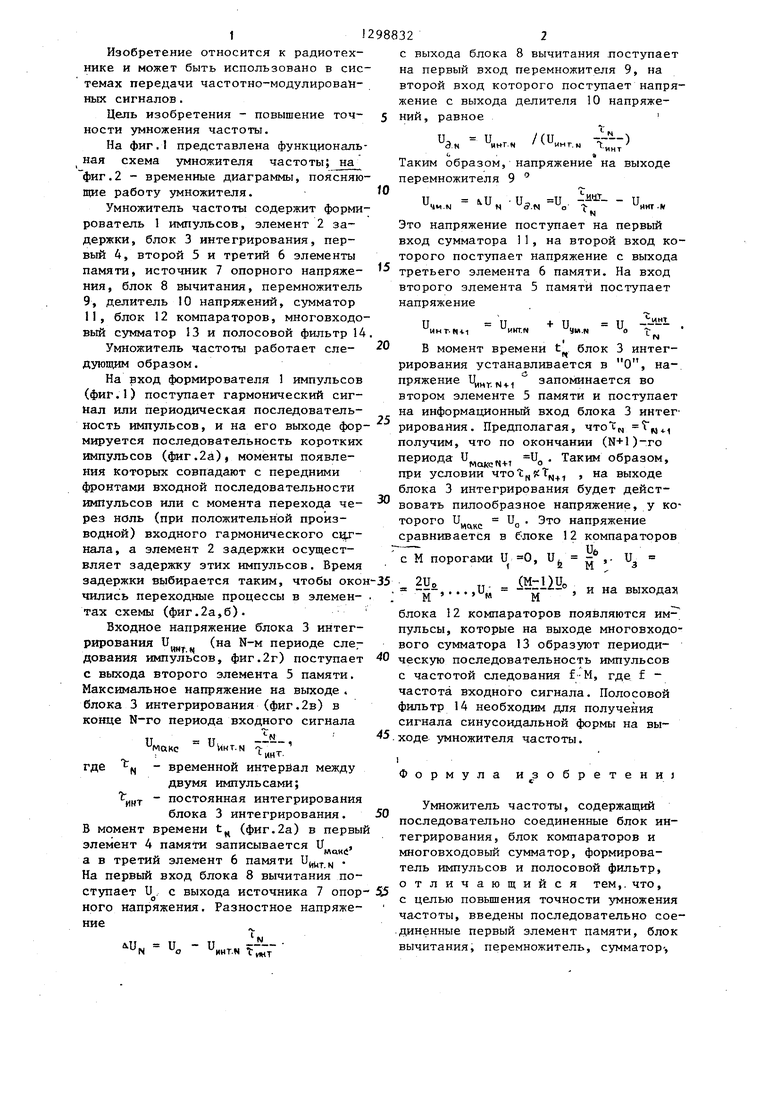

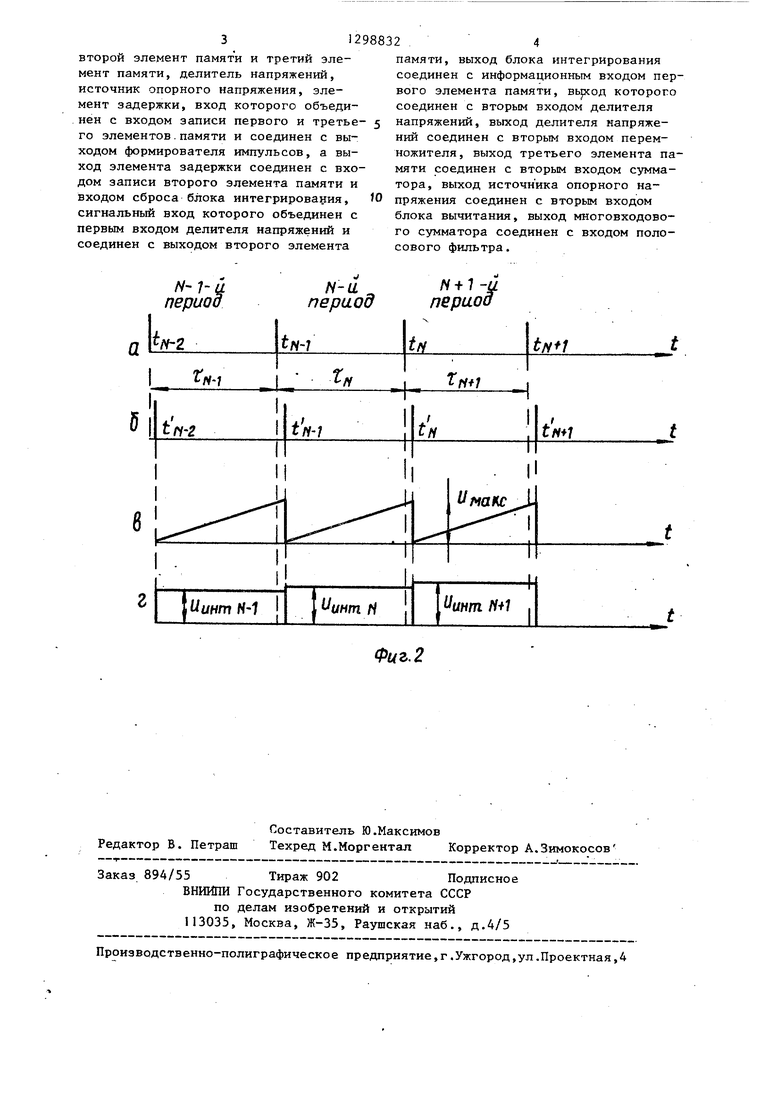

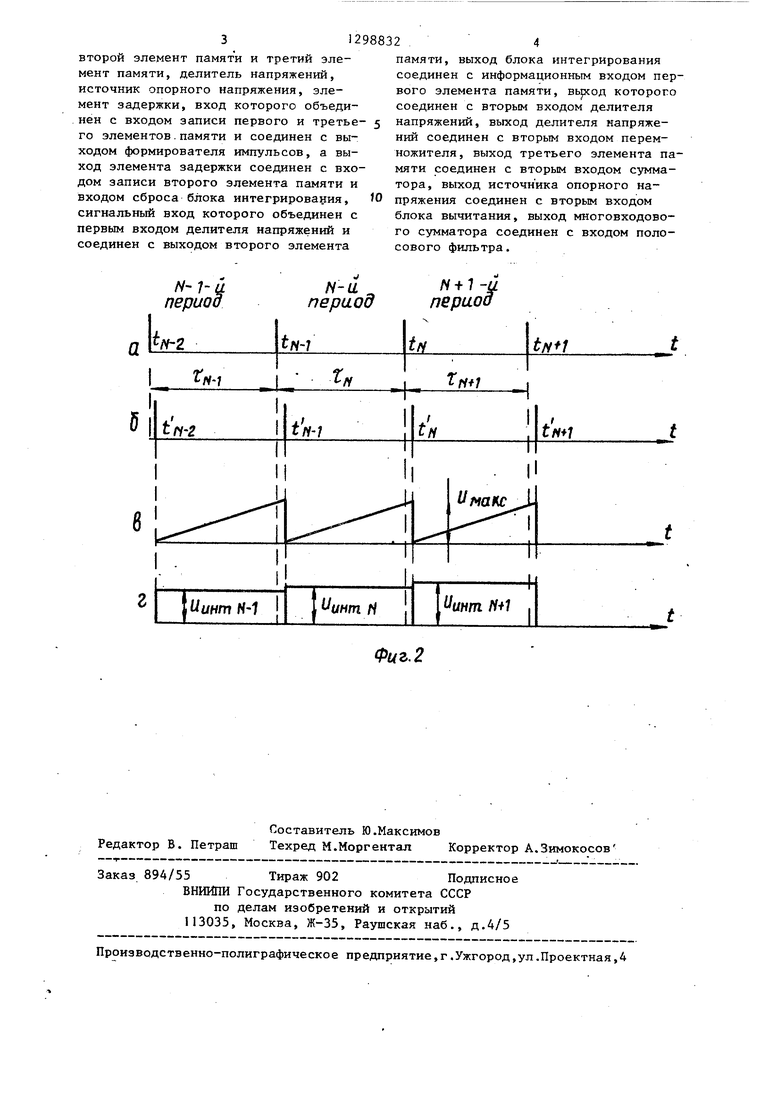

На фиг. представлена функциональная схема умножителя частоты; на фиг.2 - временные диаграммы, поясняющие работу умножителя.

Умножитель частоты содержит формирователь 1 импульсов, элемент 2 задержки, блок 3 интегрирования, первый 4, второй 5 и третий 6 элементы памяти, источник 7 опорного напряжения, блок 8 вычитания, перемножитель 9, делитель 10 напряжений, сумматор 11, блок 12 компараторов, многовходо вый сумматор 13 и полосовой фильтр 14

Умножитель частоты работает следующим образом.

На вход формирователя 1 импульсов (фиг.1) поступает гармонический сиг- йал или периодическая последовательность импульсов, и на его выходе фор мируется последовательность коротких импульсов (фиг.2а), моменты появления которых совпадают с передними фронтами входной последовательности импульсов или с момента перехода через ноль (при положительной производной) входного гармонического сцг- нала, а элемент 2 задержки осуществляет задержку этих импульсов. Время задержки выбирается таким, чтобы око чились переходные процессы в элемен- так схемы (фиг.2а,б).

Входное напряжение блока 3 интегрирования и (на N-M периоде слег

ИН г. 9J

.

дования импульсов, фиг.2г) поступает с выхода второго элемента 5 памяти. Максимальное напряжение на выходе . блока 3 интегрирования (фиг.2в) в конце К-го периода входного сигнала

м

UMOKC .N

где

N

ИНТ

-временной интерйал между двумя импульсами;

-постоянная интегрирования блока 3 интегрирования.

В момент времени t (фиг.2а) в первы элемент 4 памяти записывается а в третий элемент 6 памяти Uj . На первый вход блока 8 вычитания поступает и , с выхода источника 7 опор ного напряжения. Разностное напряжение

-UN и. - ии„г,« flT

С выхода блока 8 вычитания поступает на первый вход перемножителя 9, на второй вход которого поступает напряжение с выхода делителя 10 напряжений, равное

и

э.«

N

HHT.N (инг.м Т

перемножителя

Таким образом, напряжение на выходе 9

и, U.. U;, и.. - и.,

N

Чм.М 5.N о Г, ИНТ.К

Это напряжение поступает на первый вход сумматора 11, на второй вход которого поступает напряжение с выхода третьего элемента 6 памяти. На вход второго элемента 5 памяти поступает напряжение

.

-35 .

и,

и,.

+ и,

20

25

инТ-N+i

В момент времени t

)u.N

блок

и.

ИН1

3 интег- на0

30

40

45

рирования устанавливается в пряжение Ц,„|.. i запоминается во втором элементе 5 памяти и поступает на информационный вход блока 3 интег рирования. Предполагая, что Ср, f N4-i получим, что по окончании (N+l)-ro периода и„о,„., о Таким образом, при условии 4Tot|, , на выходе блока 3 интегрирования будет действовать пилообразное напряжение, у которого - UQ Это напряжение сравнивается в блоке 12 компараторов

с М порогами и 0, з °

2у,

М

блока 12 компараторов появляются им- пульсы, которые на выходе многовходо- вого сумматора 13 образуют периодическую последовательность импульсов с частотой следования f-M, где f частота входного сигнала. Полосовой фильтр 14 необходим для получения сигнала синусоидальной формы на выходе умножителя частоты.

(м-12и„ М

и на выхода5(

Формула

и,з

обретени

Умножитель частоты, содержащий последовательно соединенные блок интегрирования, блок компараторов и многовходовый сумматор, формирователь импульсов и полосовой фильтр, отличающийся тем,, что, с целью повьшения точности умножения частоты, введены последовательно соединенные первый элемент памяти, блок вычитания, перемножитель, сумматор-.

второй элемент памяти и третий элемент памяти, делитель напряжений, источник опорного напряжения, элемент задержки, вход которого объединен с входом записи первого и третье- го элементов.памяти и соединен с выходом формирователя импульсов, а выход элемента задержки соединен с входом записи второго элемента памяти и входом сброса блока интегрирования, сигнальный вход которого объединен с первым входом делителя напряжений и соединен с выходом второго элемента

Гуу.

N1

N

памяти, выход блока интегрирования соединен с информационным входом первого элемента памяти, вьрод которого соединен с вторым входом делителя напряжений, выход делителя напряжений соединен с вторым входом перемножителя, выход третьего элемента памяти соединен с вторым входом сумматора, выход источника опорного напряжения соединен с вторым входом блока вычитания, выход многовходово- го сумматора соединен с входом полосового фильтра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

| Устройство для измерения защищенности сигнала от помех | 1989 |

|

SU1658400A2 |

| Устройство для определения отношения сигнал-шум сигналов с фазовой модуляцией | 1986 |

|

SU1374154A2 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

| Устройство для когерентной обработки фазоманипулированных сигналов | 1983 |

|

SU1131037A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2003 |

|

RU2253183C1 |

| Устройство для измерения защищенности сигнала от помех | 1986 |

|

SU1376249A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

Изобретение м.б. использовано в системах передачи ЧМ-сигналов. Цель изобретения - повышение точности умножения частоты. Устр-во содержит формирователь импульсов 1, блок 3 интегрирования, блок 12 компараторов, многовходовый сумматор 13, полосовой фильтр 14. Вновь введены эл-т задержки 2, эл-ты памяти 4-6, источник- опорного напряжения 7, блок вычитания 8, перемножитель 9, делитель 10 напряжений, сумматор 11. 2 ил. / 1 ю со оо с 00 ГС

Редактор В. Петраш

Составитель Ю.Максимов

Техред М.Моргентал Корректор А.Зкмокосов

Заказ 894/55 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

Фиг.2

| Умножитель частоты | 1983 |

|

SU1190458A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синтезатор частот | 1974 |

|

SU559358A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-23—Публикация

1985-11-11—Подача