1

Изобретение относится к импульсной технике и может быть использовано в устройствах распределения им- гульсов, системах синхронизации и управления .

Цель изобретения - повышение надежности и расширение функциональных возможностей.

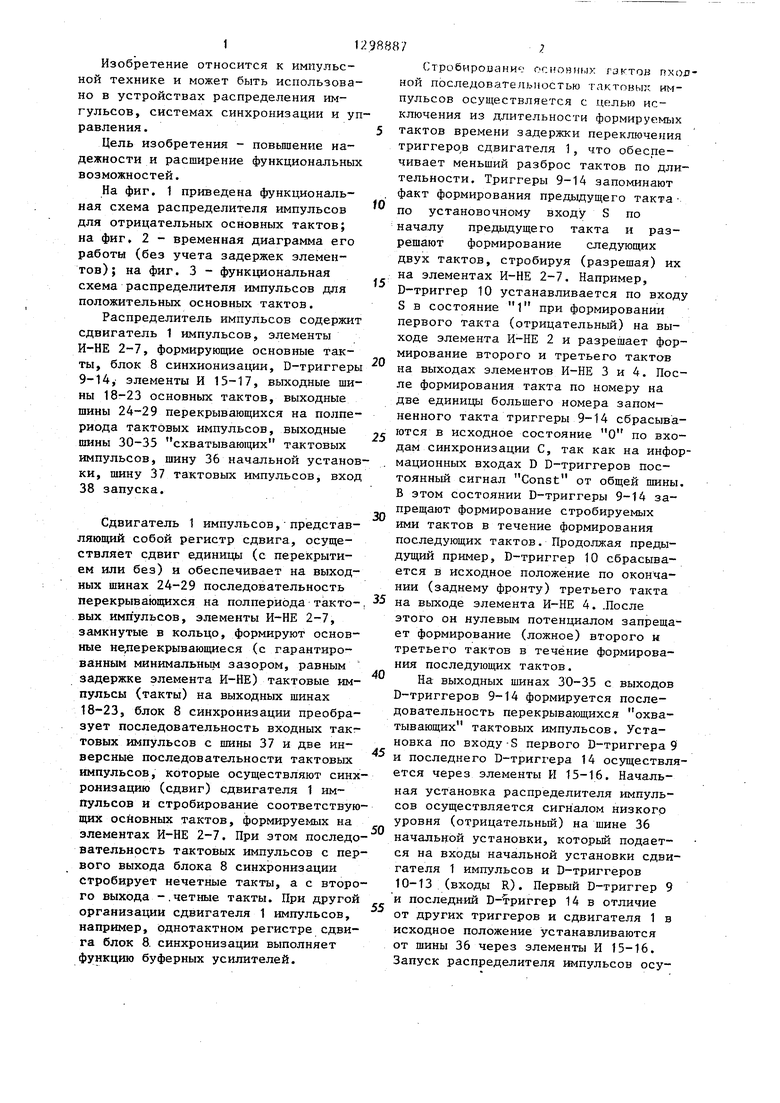

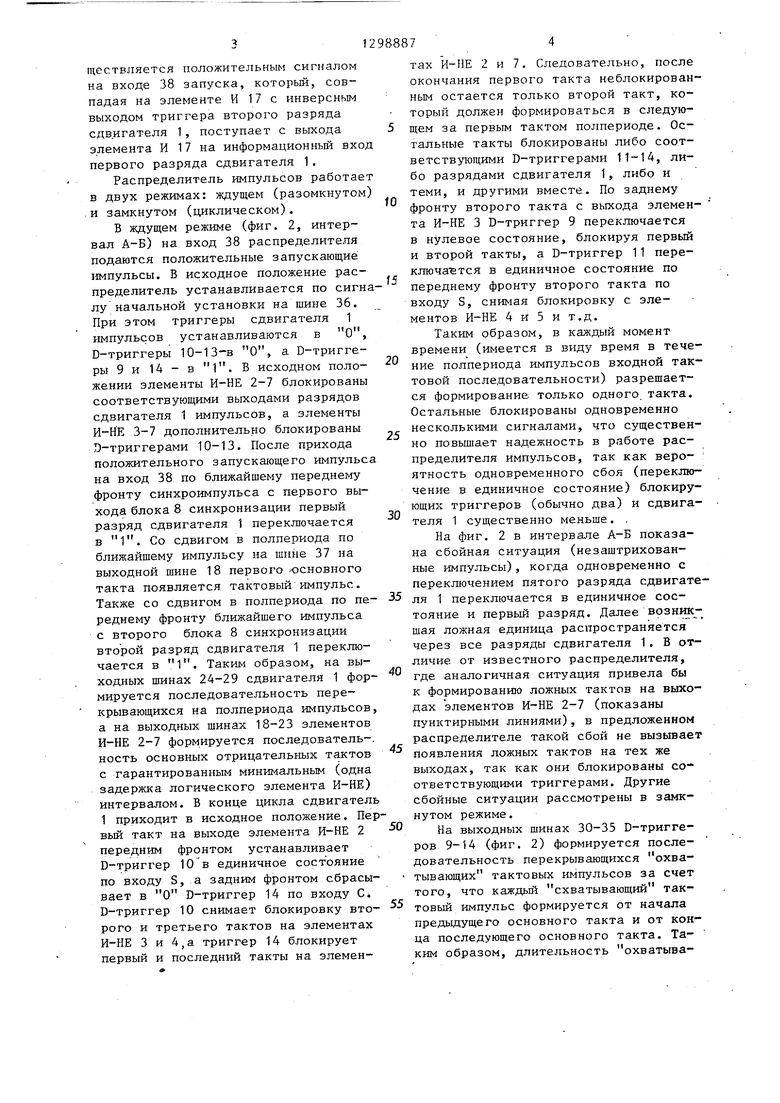

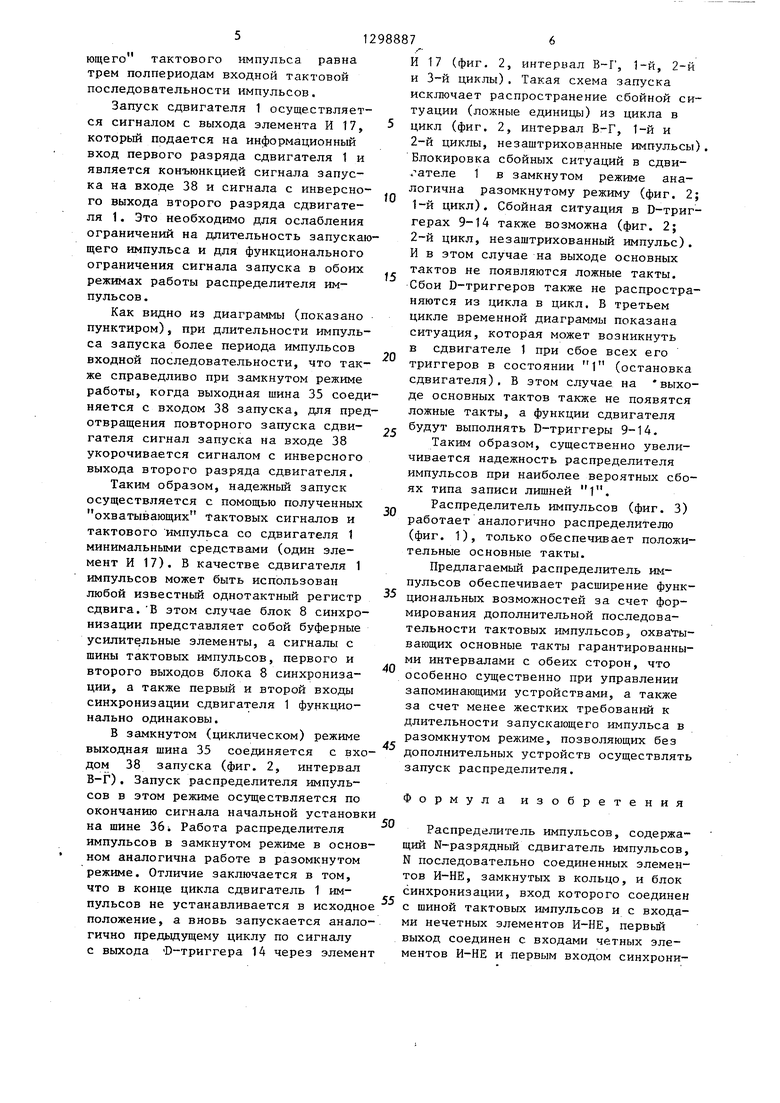

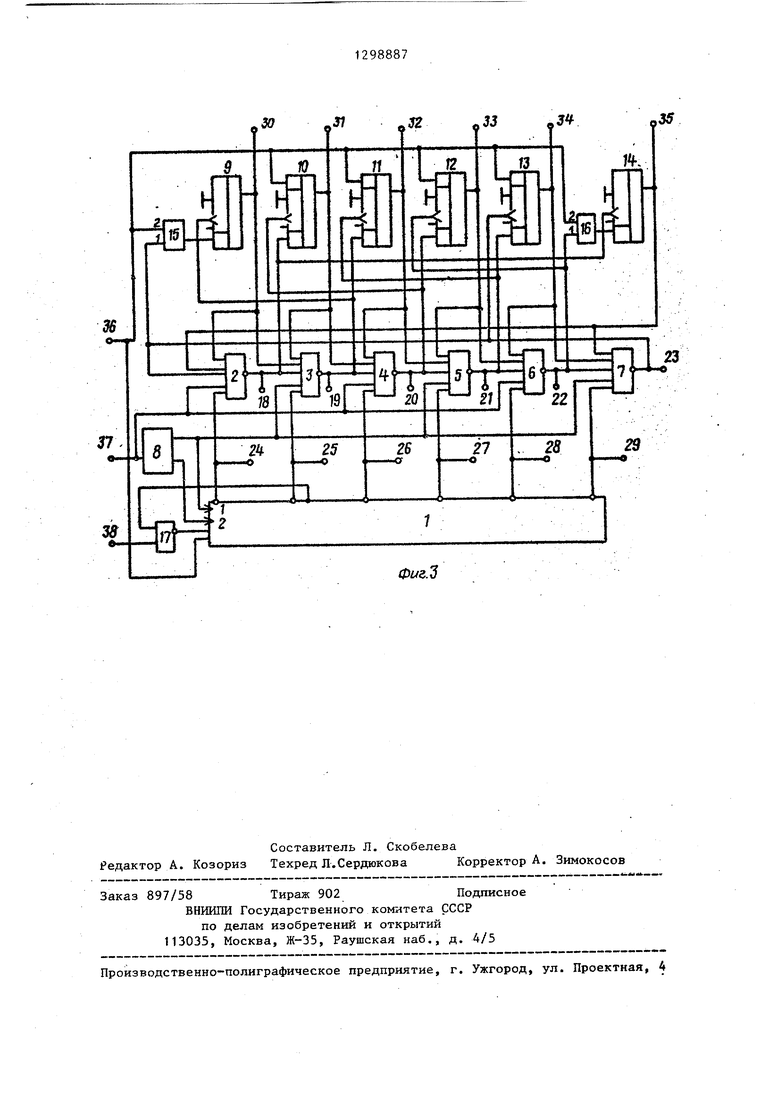

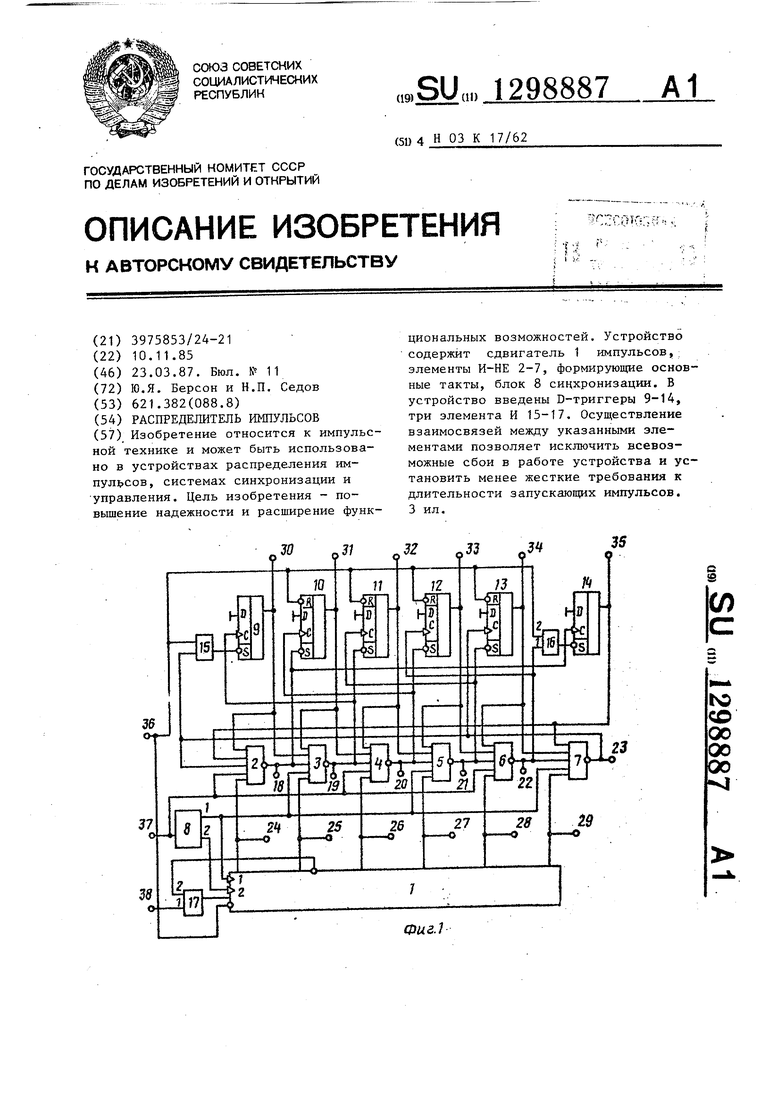

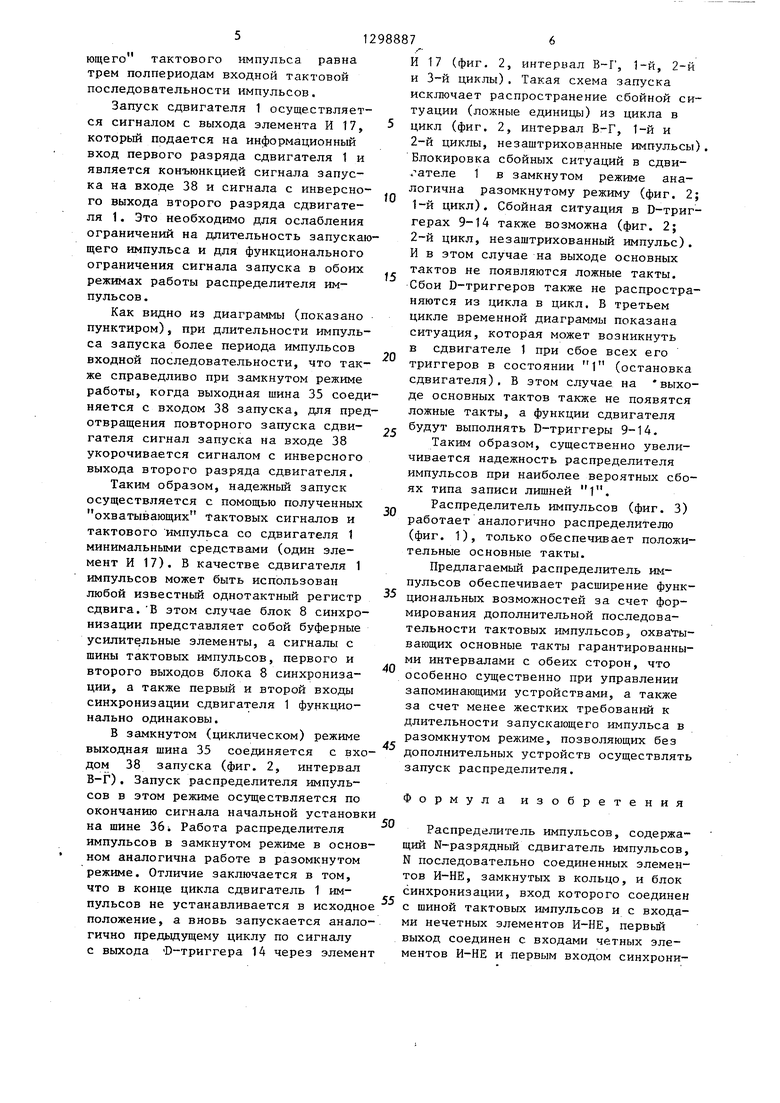

На фиг. 1 приведена функциональная схема распределителя импульсов для отрицательных основных тактов; на фиг, 2 - временная диаграмма его работы (без учета задержек элементов); на фиг. 3 - функциональная схема распределителя импульсов для положительных основных тактов.

Распределитель импульсов содержит сдвигатель 1 импульсов, элементы И-НЕ 2-7, формирующие основные такты, блок 8 синхионизации, D-триггеры 9-14, элементы И 15-17, выходные шины 18-23 основных тактов, выходные шины 24-29 перекрывающихся на полпериода тактовых импульсов, выходные шины 30-35 схватывающих тактовых импульсов, шину 36 начальной установки, шину 37 тактовых импульсов, вход 38 запуска.

Сдвигатель 1 импульсов,представляющий собой регистр сдвига, осуществляет сдвиг единицы (с перекрытием или без) и обеспечивает на выходных шинах 24-29 последовательность перекрывающихся на полпериода тактовых импульсов, элементы И-НЕ 2-7, замкнутые в кольцо, формируют основные не,перекрываю1циеся (с гарантированным минимальным зазором, равным задержке элемента И-НЕ) тактовые импульсы (такты) на выходных шинах 18-23, блок 8 синхронизации преобразует последовательность входных тактовых импульсов с шины 37 и две инверсные последовательности тактовых импульсов, которые осуществляют синхронизацию (сдвиг) сдвигателя 1 импульсов и стробирование соответствующих основных тактов, формируемых на элементах И-НЕ 2-7. При этом последовательность тактовых импульсов с первого выхода блока 8 синхронизации стробирует нечетные такты, а с второго выхода -.четные такты. При другой организации сдвигателя 1 импульсов, например, однотактном регистре сдвига блок 8. синхронизации выполняет функцию буферных усилителей.

12

, fO

f5

20

25

98887;

Стробироиани : основных гактов nxofj- ной последовательностью тактовых m-t- пульсов осуществляется с целью исключения из длительности формируемых тактов времени задержки переключения триггеров сдвигателя 1, что обеспечивает меньший разброс тактов по длительности. Триггеры 9-14 запоминают факт формирования предьщущего такта по установочному входу S по началу предыдущего такта и разрешают формирование следующих двух тактов, стробируя (разрешая) их на элементах И-НЕ 2-7. Например, D-триггер 10 устанавливается по входу S в состояние 1 при формировании первого такта (отрицательный) на выходе элемента И-НЕ 2 и разрешает формирование второго и третьего тактов на выходах элементов И-НЕ 3 и 4. После формирования такта по номеру на две единицы большего номера запомненного такта триггеры 9-14 сбрасываются в исходное состояние О по входам синхронизации С, так как на информационных входах D D-триггеров постоянный сигнал Const от общей шины. В этом состоянии D-триггеры 9-14 запрещают формирование стробируемых ими тактов в течение формирования последующих тактов. Продолжая предыдущий пример, D-триггер 10 сбрасывается в исходное положение по окончании (заднему фронту) третьего такта 35 на выходе элемента И-НЕ 4. .После

этого он нулевьпу потенциалом запрещает формирование (ложное) второго и третьего тактов в течение формирования последующих тактов. На выходных шинах 30-35 с выходов D-триггеров 9-14 формируется последовательность перекрывающихся охватывающих тактовых импульсов. Установка по входу-S первого D-триггера9 и последнего D-триггера 14 осуществляется через элементы И 15-16. Начальная установка распределителя импульсов осуществляется сигналом низкого уровня (отрицательный) на шине 36 начальной установки, которьш подается на входы начальной установки сдвигателя 1 импульсов и D-триггеров 10-13 (входы R). Первый D-триггер 9 и последний D- риггер 14 в отличие от других триггеров и сдвигателя 1 в исходное положение устанавливаются от шины 36 через элементы И 15-16. Запуск распределителя импульсов осу30

50

55

3

щсс.твляется положительным сигналом на входе 38 запуска, который, совпадая на элементе И 17 с инверсным выходом триггера второго разряда сдвигателя 1, поступает с выхода элемента И 17 на информационный вхо первого разряда сдвигателя 1.

Распределитель импульсов работае в двух режимах: ждущем (разомкнутом ,и замкнутом (циклическом),

В ждущем режиме (фиг. 2, интервал А-Б) на вход 38 распределителя подаются положительные запускающие импульсы. В исходное положение распределитель устанавливается по сигнлу начальной установки на шине 36. При этом триггеры сдвигателя 1 импульсов устанавливаются в О, D-триггеры 10-13-в О, а D-тригге- ры 9 и 14 - в 1. В исходном положении элементы И-НЕ 2-7 блокированы соответствующими выходами разрядов сдвигателя 1 импульсов, а элементы И-НЕ 3-7 дополнительно блокированы D-триггерами 10-13. После прихода положительного запускающего импульс на вход 38 по ближайшему переднему фронту синхроимпульса с первого выхода блока 8 синхронизации первый разряд сдвигателя 1 переключается в 1. Со сдвигом в полпериода по ближайшему импульсу на шине 37 на выходной шине 18 первого юсновного такта появляется тактовый импульс, Также со сдвигом в полпериода по переднему фронту ближайшего импульса с второго блока В синхронизации второй разряд сдвигателя 1 переключается в 1. Таким образом, на выходных шинах 24-29 сдвигателя 1 формируется последовательность перекрывающихся на полпериода импульсов а на выходных шинах 18-23 элементов И-НЕ 2-7 формируется последовательность основных отрицательных тактов с гарантированным минимальным (одна задержка логического элемента И-НЕ) интервалом. В конце цикла сдвигатель 1 приходит в исходное положение. Пер вьй такт на выходе элемента И-НЕ 2 передним фронтом устанавливает D-триггер 10 в единичное состояние по входу S, а задним фронтом сбрасывает в О D-триггер 14 по входу С. D-триггер 10 снимает блокировку второго и третьего тактов на элементах И-НЕ 3 и 4,а триггер 14 блокирует первый и последний такты на элеменO

5

0

5

88874

тах И-НЕ 2 и 7. Следовательно, после окончания первого такта неблокирован- ным остается только второй такт, который должен формироваться в следую- 5 щем за первым тактом полпериоде. Остальные такты блокированы либо соответствующими Б-триггерами 11-14, либо разрядами сдвигателя 1, либо и теми, и другими вместе. По заднему фронту второго такта с выхода элемента 3 D-триггер 9 переключается в нулевое состояние, блокируя первый и второй такты, а D-триггер 11 переключается в единичное состояние по переднему фронту второго такта по входу S, снимая блокировку с элементов И-НЕ 4 и 5 и т.д.

Таким образом, в каждый момент времени (имеется в виду время в течение полпериода импульсов входной тактовой последовательности) разрешается формирование только одного такта. Остальные блокированы одновременно несколькими сигналами, что существенно повышает надежность в работе распределителя импульсов, так как веро- ятность одновременного сбоя (переключение в единичное состояние) блокирующих триггеров (обычно два) и сдвигателя 1 существенно меньше. .

На фиг. 2 в интервапе А-Б показана сбойная ситуация (незаштрихованные импульсы), когда одновременно с переключением пятого разряда сдвигате- 5 ля 1 переключается в единичное состояние и первый разряд. Далее возник- шая ложная единица распространяется через все разряды сдвигателя 1. В отличие от известного распределителя, где аналогичная ситуация привела бы к формированию ложных тактов на выходах элементов И-НЕ 2-7 (показаны пунктирными линиями), в предложенном распределителе такой сбой не вызывает появления ложных тактов на тех же выходах, так как они блокированы соответствующими триггерами. Другие сбойные ситуации рассмотрены в замкнутом режиме.

На выходных шинах 30-35 D-тригге- ров 9-14 (фиг. 2) формируется последовательность перекрывающихся охватывающих тактовых импульсов за счет

0

0

5

0

того, что каждый схватывающий тактовый импульс формируется от начала предыдущего основного такта и от конца последующего основного такта. Таким образом, длительность охватыва

ющего тактового импульса равна трем полпериодам входной тактовой последовательности импульсов.

Запуск сдвигателя 1 осуществляется сигналом с выхода элемента И 17, который подается на информационный вход первого разряда сдвигателя 1 и является конъюнкцией сигнала запуска на входе 38 и сигнала с инверсного выхода второго разряда сдвигателя 1. Это необходимо для ослабления ограничений на длительность запускающего импульса и для функционального ограничения сигнала запуска в обоих режимах работы распределителя импульсов .

Как видно из диаграммы (показано пунктиром), при длительности импульса запуска более периода импульсов входной последовательности, что также справедливо при замкнутом режиме работы, когда выходная шина 35 соединяется с входом 38 запуска, для предотвращения повторного запуска сдви- гателя сигнал запуска на входе 38 укорочивается сигналом с инверсного выхода второго разряда сдвигателя. Таким образом, надежный запуск осуществляется с помощью полученных охватывающих тактовых сигналов и тактового импульса со сдвигателя 1 минимальными средствами (один элемент И 17). В качестве сдвигателя 1 импульсов может быть использован любой известный однотактный регистр сдвига. В этом случае блок 8 синхронизации представляет собой буферные усилительные элементы, а сигналы с шины тактовых импульсов, первого и второго выходов блока 8 синхронизации, а также первый и второй входы синхронизации сдвигателя 1 функционально одинаковы.

В замкнутом (циклическом) режиме выходная шина 35 соединяется с вхдом 38 запуска (фиг. 2, интервал В-Г). Запуск распределителя импульсов в этом режиме осуществляется по окончанию сигнала начальной установ на шине 36i Работа распределителя импульсов в замкнутом режиме в осноном аналогична работе в разомкнутом режиме. Отличие заключается в том, что в конце цикла сдвигатель 1 импульсов не устанавливается в исходн положение, а вновь запускается аналгично предьщущему циклу по сигналу с выхода D-триггера 14 через элеме

5

0

5

у з-.

40

45

50

55

И 17 (фиг. 2, интервал В-Г, 1-й, 2-й и 3-й циклы). Такая схема запуска исключает распространение сбойной ситуации (ложные единицы) из цикла в цикл (фиг. 2, интервал В-Г, 1-й и 2-й циклы, незаштрихованные импульсы). Блокировка сбойных ситуаций в сдви- ателе 1 в замкнутом режиме аналогична разомкнутому режиму (фиг. 2; 1-й цикл). Сбойная ситуация в D-триг- герах 9-14 также возможна (фиг. 2; 2-й цикл, незаштрихованный импульс). И в этом случае на выходе основных тактов не появляются ложные такты. Сбои D-триггеров также не распространяются из цикла в цикл. В третьем цикле временной диаграммы показана ситуация, которая может возникнуть в сдвигателе 1 при сбое всех его триггеров в состоянии 1 (остановка сдвигателя), В этом случае на выходе основных тактов также не появятся ложные такты, а функции сдвигателя будут выполнять D-триггеры 9-14.

Таким образом, существенно увеличивается надежность распределителя импульсов при наиболее вероятных сбоях типа записи лишней 1.

Распределитель импульсов (фиг. 3) работает аналогично распределителю (фиг. 1), только обеспечивает положительные основные такты.

Предлагаемый распределитель импульсов обеспечивает расширение функциональных возможностей за счет формирования дополнительной последовательности тактовых импульсов, охватывающих основные такты гарантированными интервалами с обеих сторон, что особенно существенно при управлении запоминающими устройствами, а также за счет менее жестких требований к длительности запускающего импульса в разомкнутом режиме, позволяющих без дополнительных устройств осуществлять запуск распределителя.

Формула изобретения

Распределитель импульсов, содержащий N-разрядный сдвигатель импульсов, N последовательно соединенных элементов И-НЕ, замкнутых в кольцо, и блок синхронизации, вход которого соединен с шиной тактовых импульсов и с входами нечетных элементов И-НЕ, первьй выход соединен с входами четных элементов И-НЕ и первым входом синхрони

71

зации сдвигателя импульсов, второй выход соединен с вторым входом синхронизации сдвигателя импульсов, а выходы разрядов сдвигателя импульсов соединены с выходными шинами и с входами соответствующих элементов Й-НЕ, выходы которых подключены к соответствующим выходным шинам, при этом вход начальной установки сдвигателя импульсов подключен к шине на чальной установки распределителя, отличающийся тем, что, с целью повышения надежности и расширения функциональных возможностей, в него введены N D-триггеров и три элемента И, причем входы синхронизации D-триггеров, начиная с первого и до (N-l)-ro, соединены с выходами элементов И-НЕ, начиная с второго и до N-ro соответственно, а вход синхронизации N-ro D-триггера соединен с йыходом первого элемента И-НЕ, при этом установочные входы D-триггеров, начиная с второго и до (N-l)-ro соединены с выходами элементов И-НЕ, начиная с первого и до (N-2)-ro ср

ответственно, а входы D всех D-триг

8

геров подключены к общей шине, выходы D-триггеров, начиная с первого и до (N-l)-ro, подключены к соответствующим выходным шинам и к входам двух элементов И-НЕ каждый, начиная с первого и второго, продолжая с вторым и третьим и до (N-l)-ro и N-го соответственно, а выход N-го

10

15

20

25

D-триггера подключен к соответствующей выходной шине и к входам первого и N-ro элементов И-НЕ, вход запуска распределителя импульсов подключен к входу первого элемента И, второй вход - соторого соединен с инверсным выходом второго разряда сдвигателя импульсов, а выход - с информационным входом первого разряда сдвигателя импульсов, установочные входы первого и N-ro D-триггеров соединены с выходами второго и третьего элементов И соответственно, первые входы которых соединены соответственно с выходами N-ro и (N-l)-ro элементов ИНЕ, а вторые входы - с шиной начальной установки и входами начальной установки D-триггеров, начиная с второго и до (N-l)-ro,

37

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1980 |

|

SU919071A1 |

| Распределитель импульсов | 1980 |

|

SU947968A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Фотоэлектрическое считывающее устройство | 1977 |

|

SU714428A1 |

| Процессор быстрого преобразования Фурье | 1987 |

|

SU1425709A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1223248A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Устройство для коррекции сбойных кодов в кольцевом распределителе | 1979 |

|

SU888125A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах распределения им- , системах синхронизации и управления. Цель изобретения - повышение надежности и расширение функциональных возможностей. Устройство содержит сдвигатель 1 импульсов, элементы И-НЕ 2-7, формирующие основные такты, блок 8 синхронизации. В устройство введены D-триггеры 9-14, три элемента И 15-17. Осуществление взаимосвязей между указанными элементами позволяет исключить всевозможные сбои в работе устройства и установить менее жесткие требования к длительности запускающих импульсов. 3 ил. сл ISD оо 00 00 Фиг.1

Авторы

Даты

1987-03-23—Публикация

1985-11-10—Подача