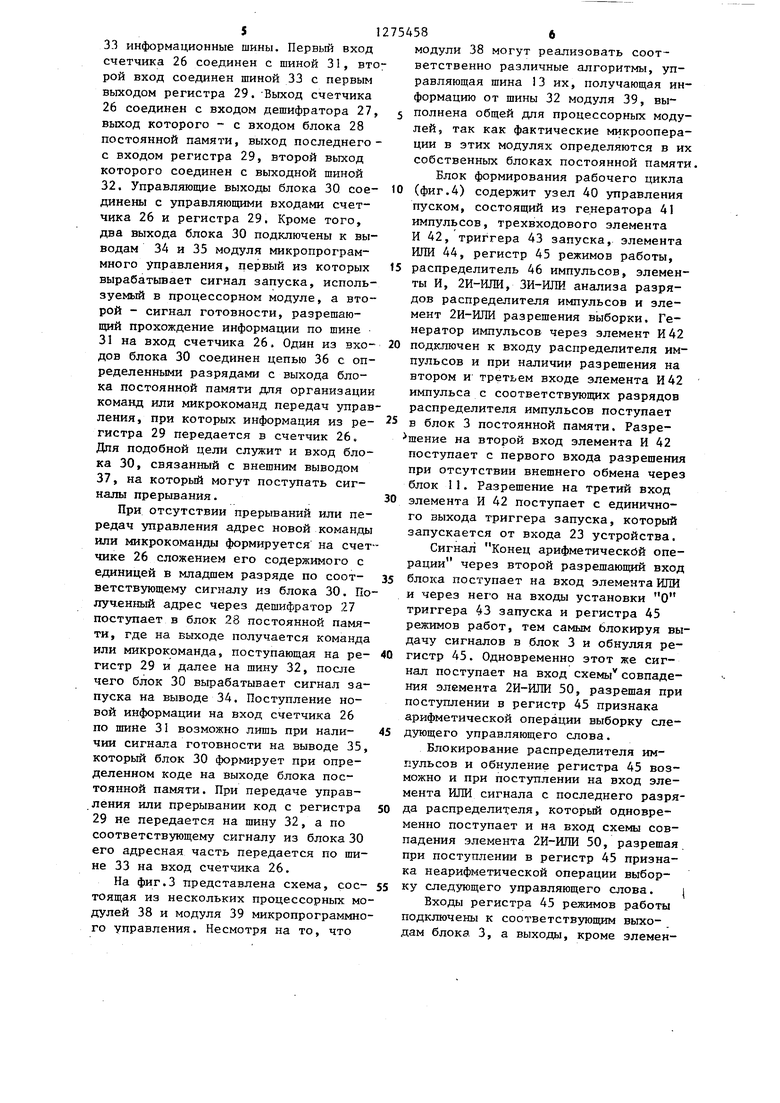

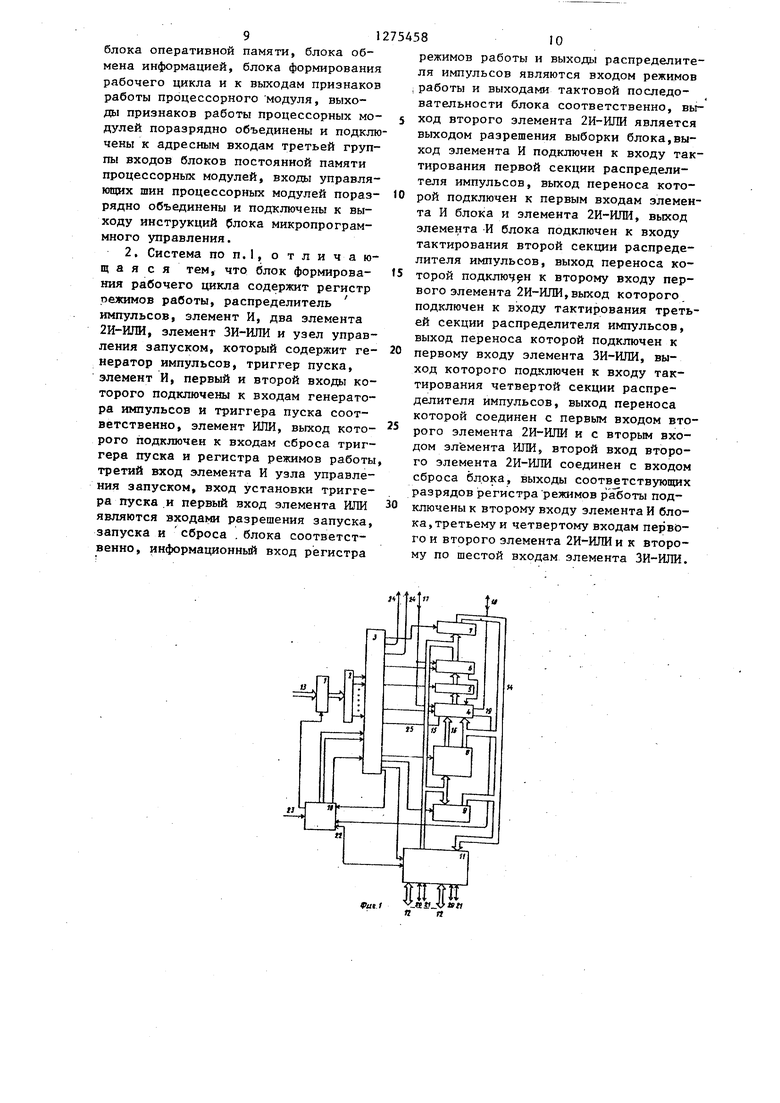

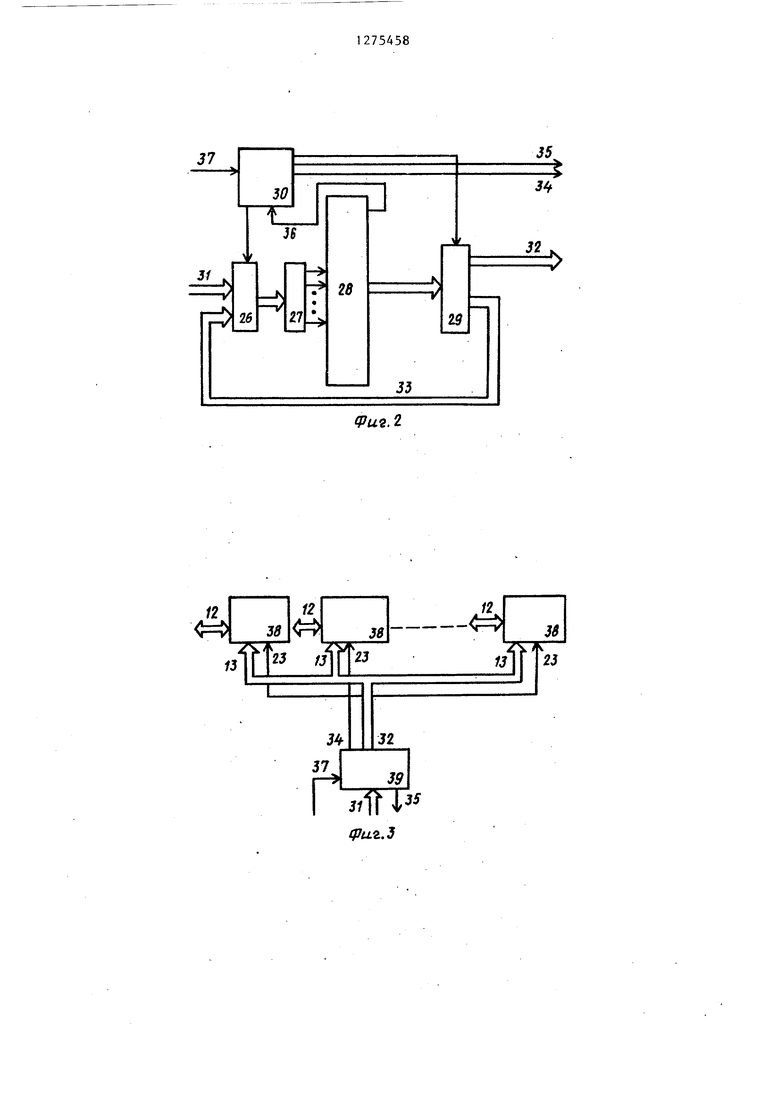

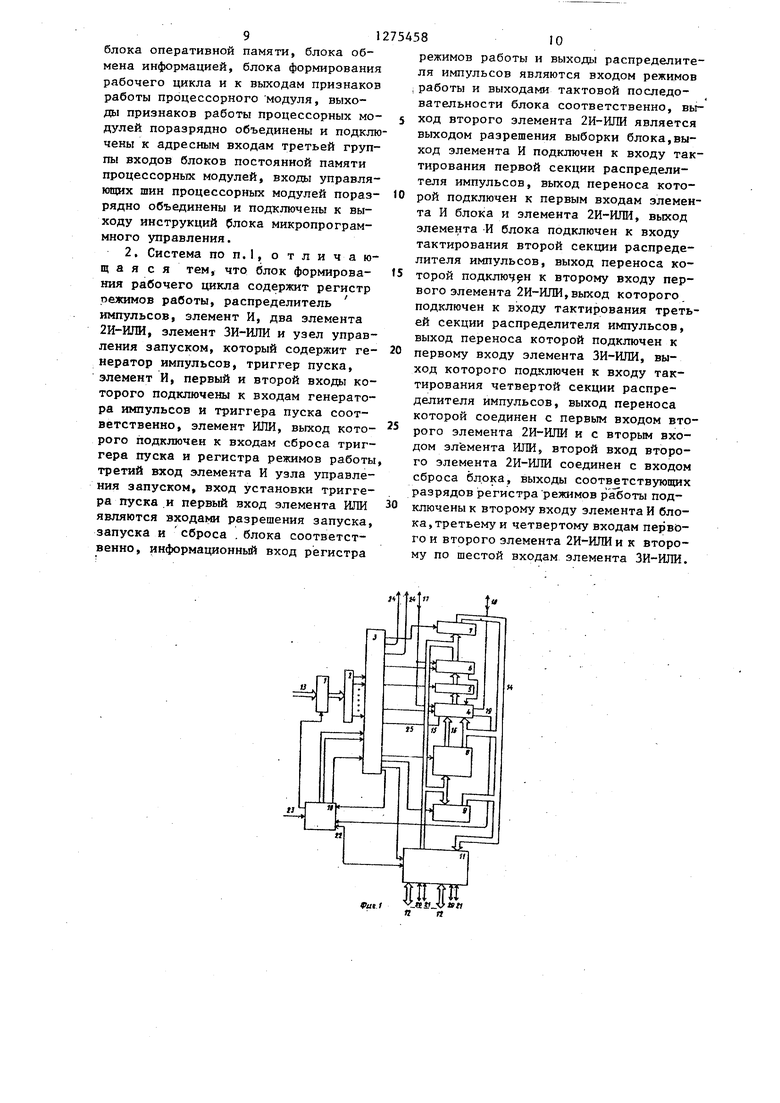

Изобретение относится к вычислительной технике, а именно к микропро цессорным системам,для обработки дан ных по нескольким программам, и может быть использовано при разработке БИС, предназначенных для построения высокопроизводительных вычислительных систем, в частности управляющих систем, работающих в реальном масшта бе времени. Повышение производительности вычислительных систем требует максимального распараллеливания вычислительного процесса, что приводит к созданию микропроцессорных систем с большим числом процессорных элементов. Цель изобретения - повьшение производительности системы за счет децентрализации управления, что обеспечивает организацию большего числа микроопераций, параллелизма их выполнения в процессорных модулях и ре ализации их в любой временной последовательности, а также упрощение структуры микропроцессорной системы На фиг.1 представлена структурная схема процессорного модуля; на фиг.2 структурная схема модуля управления на фиг.З - соединение модулей в системе; на фиг,4 - структурная схема блока формирования рабочего цикла. Процессорный МОДУЛЬ (фиг.) содержит регистр 1 микрокоманды, дешиф ратор 2, блок 3 постоянной памяти, арифметическо-логическое устройство 4, буферный регистр 5 сдвигатель 6 регистр 7 состояшэд, блок 8 оператив ной памяти, регистр 9 результата, блок 10 формирования рабочего цикла устройство 11 обмена информации с двунаправленными информационными шинами 12, управляющую шину 13 и внутренние информационные шины 14 - 16. Вход регистра I соединен с управляющей шиной 13. На регистре 1 в течение выполнения операций хранится соответствующая микрокоманда, выход регистра соединен с входом дещифратора 2, подключенного своим выходом к части входов блока 3 постоянной памяти, остальные входы которого сое динены с выходами блока 10. Соответствующие выходы блока 3 постоянной памяти соединены с управляющими входами арифметико-логического устройства 4, буферного регистра 5, сдвигателя 6, регистра 7 состояний, бло582ка 8 оперативной памяти, регистра 9 результата, устройства 11 обмена информацией и первым управляющим входом блока 10, управляющий выход оторого подключен к управляющему входу регистра 1. Один из выходов блока 8 оперативной памяти и выходы регистров 9 и 7 объединены информационной шиной 14 с входами устройства 11 обмена информацией и арифметическо-логического устройства 4. Вхдды блока 8 и регистров 9 и 7 объединены информационной шиной 15 с Выходами устройства 11 и сдвигателя 6, входы которого через буферньй регистр 5 подключены к выходу устройства 4. Второй вход устройства 4 для поступления второго операнда подключен информационной шиной 16 к второму выходу блока 8 (первый операнд поступает по шине 14). Арифметическо-логическое устройство 4 соединено входами и выходами переноса с двунаправленными выводами 17 и 18 модуля соответственно, причем вход переноса подключен к одному из сдвиговых выводов сдвигателя 6, второй вывод которого соединен с одним из входов устройства 4, где он объединяется с выходом переноса. Цепью 19 устройство 4 соединено с вторым управляющим входом блока 10. Устройство 11 для каждой из двунаправленных шин 12 имеет по два двунаправленных вывода 20 и 21 модуля соответственно. Кроме того, устройство II подключено цепью 22 к третьему управляющему входу блока 10,который соединен с входом 23 модуля. Определенные разряды блока 3 постоянной памяти соединены с двунаправленными выводами 24 модуля. Сигналы на этих выводах используются для взаимной синхронизации процессорных модулей,объединенных с целью расширения разрядности в одий процессорный блок, причем выводы 24 указанных модулей соединяются в одну точку для образования функции Проводное И. Единичный сигнал в этой точке является cтpoбиpyюшJiM импульсом для микроопераций, требующих одновременного выполнения в указанных модулях. В состав арифметическо-логического устройства 4 включены узел асинхронного переноса и узел расширения разрядности. Использование узла асинхронного переноса позволяет фиксиро-вать момент окончания арифметической операции в каждом модуле (прохождение переноса), независимо от о тальных процессорных модулей. Сигнал об окончании операции по цепи 19 передается в блок 10. Узел расширения разрядности предназначен для сопряжения устройств А в различных модулях одной группы, работающих со словами, разрядность которых превосходит разрядность одного процессорного модуля, во время арифметических и сдвиговых операций. Дпя выделения в указанной группе модуля с самыми старшими разрядами используется один из выходов блока постоянной памяти, соединенный цепью 25 с соответствующим входом узла расширения разрядности устройства 4 данного модуля, состояние входов которого устанавливается отличным от состояний входов всех остальных модулей группы и служит идентификатором операций, выполнение которых в старших разрядах отличается от выполнения в оставшихся разрядах. В этом же узле происходит объединение в одну цепь сигналов выхода переноса из старшего разряда каждого модуля и вьщвигаемых разрядов при сдвиге влево, поступающих из сдвигателя 6. Последний кроме операций сдвига, вырабатывает также признаки контролируемых состояний, таких как Переполнение, Знак, Ноль результата и т.д., которые по шине 15 могут быть переданы в регистр 7, а также далее, по шине 14 через устройство 11, на общук для нескольких процессорных модулей магистраль . Поскольку устройство 4 саМО не содержит запоминающих элементов, то для временного хранения полу ченных в нем результатов используется регистр 5. Устройство 11 состоит из одного Ш1И нескольких идентичных блоков обмена информацией, соединенных со сво ими двунаправленными шинами 12, и соответствующих им узлов автономного управления информацией, которые управляют асинхронным приемом и выдачей информации через блоки обмена в соответствии с управляющими сигналами из блока 3 постоянной памяти. Каж дый блок обмена через узел автономного управления обмена подключен к выводам 20 и 21, через первый из которых вводится или выводится признак 584 о наличии информации на соответствующей шине 12, а через второй соответственно вводится или выводится признак окончания обмена информацией. Во время приема информации при наличии соответствующего признака на выводе 20 узел автономного управления обменом вырабатывает сигнал, открывающий вентили передачи информации в блоке обмена из соответствующей шины 12 во внутреннюю шину 15 до момента поступления сигнала окончанкя приема с вывода 21. При выдаче информации узел автономного управления формирует соответствующий признак на вывод 20, открывает вентиль в блоке обмена, пропускающем информацию из.шины 14 в соответствующую шину 12, после чего вырабатывает признак окончания, поступающий на вывод 21. Блок 10 представляет собой распределитель импульсов, работающий от управляемого генератора импульсов, условия генерации которого состоят в прохождении сигнала запуска по входу 23 и отсутствии операций обмена в устройстве 11. Сигнал приема нового управляющего слова в регистр 1 по шине 13 организуется в блоке 10 после прохождения последнего импульса в распределителе импульсов при неарифметических операциях или после прихода сигнала окончания арифметической операции по цепи 19 из устройства 4. Распределитель импульсов имеет управляющий вход, соединенный с выходом определенных разрядов блока 3 по-,) стоянной памяти, который в. зависимости от выполняемой операции может управлять длительностью рабочего цикла и изменить порядок следования импульсов в распределителе. Соединения выходов блока 10 с выходами блока 3 остоянной памяти, состояние остальных входов которого определяется упавляющим словом, дает возможность утем программирования блока постояной памяти организовать реализацию юбых последовательностей наборов мироопераций, которые заложены в труктуру блоков 4 - 9 и 11, и свяанных между ними. Модуль микропрограммного управлеия (фиг.2) содержит счетчик 26 адреа, дешифратор 27, блок 28 постояной памяти, регистр 29 обратной свяи, блок 30 местного управления и ходную 31, выходную 32 и внутреннюю 51 33 информационные шины. Первый вход счетчика 26 соединен с шиной 31, вто рой вход соединен шиной 33 с первым выходом регистра 29. -Выход счетчика 26 соединен с входом дешифратора 27, выход которого с входом блока 28 постоянной памяти, выход последнегос входом регистра 29, второй выход которого соединен с выходной шиной 32. Упpaвляюш e выходы блока 30 соединены с згаравляющими входами счетчика 26 и регистра 29. Кроме того, два выхода блока 30 подключены к выводам 34 и 35 модуля микропрограммного управления, первый из которых вырабатывает сигнал запуска, используемый в процессорном модуле, а второй - сигнал готовности, разрешающий прохождение информации по шине 31 на вход счетчика 26. Один из входов блока 30 соединен цепью 36 с определенными разрядами с выхода блока постоянной памяти для организации команд или микрокоманд передач управ ления, при которых информация из регистра 29 передается в счетчик 26. Для подобной цели служит и вход блока 30, связанный с внешним выводом 37, на который могут поступать сигналы прерывания. При отсутствии прерываний или передач управления адрес новой команды или микрокоманды формируется на счет чике 26 сложением его содержимого с единицей в младшем разряде по соответствуюш ему сигналу из блока 30. По лученный адрес через дешифратор 27 поступает в блок 28 постоянной памяти, где на выходе получается команда или микрокоманда, поступающая на регистр 29 и далее на шину 32, после чего блок 30 вырабатывает сигнал запуска на выводе 34. Поступление новой информации на вход счетчика 26 по шине 31 возможно лишь при наличии сигнала готовности на выводе 35, который блок 30 формирует при определенном коде на выходе блока постоянной памяти. При передаче управления или прерывании код с регистра 29 не передается на шину 32, а по соответствующему сигналу из блока 30 его адресная часть передается по шине 33 на вход счетчика 26. На фиг.З представлена схема, состоящая из нескольких процессорных мо дулей 38 и модуля 39 микропрограммно го управления. Несмотря на то, что 586 модули 38 могут реализовать соответственно различные алгоритмы, управляющая шина 13 их, получающая информацию от шины 32 модуля 39, выполнена общей для процессорных модулей, так как фактические микрооперации в этих модулях определяются в их собственных блоках постоянной памяти, Блок формирования рабочего цикла (фиг.4) содержит узел 40 управления пуском, состоящий из генератора 41 импульсов, трехвходового элемента И 42, триггера 43 запуска, элемента ИЛИ 44, регистр 45 режимов работы, распределитель 46 импульсов, элементы И, 2К-ШШ., ЗИ-ИЛИ анализа разрядов распределителя импульсов и злемент 2И-ИЛИ разрешения выборки. Генератор импульсов через элемент И 42 подключен к входу распределителя импульсов и при наличии разрешения на втором и третьем входе элемента И 42 импульса с соответствующих разрядов распределителя импульсов поступает в блок 3 постоянной памяти. Разрешение на второй вход элемента И 42 поступает с первого входа разрешения при отсутствии внешнего обмена через блок 11. Разрешение на третий вход элемента И 42 поступает с единичного выхода триггера запуска, который запускается от входа 23 устройства. Сигнал Конец арифметической операции через второй разрешающий вход блока поступает на вход элемента ИЛИ и через него на входы установки О триггера 43 запуска и регистра 45 режимов работ, тем самым блокируя выдачу сигналов в блок 3 и обнуляя регистр 45. Одновременно этот же сигнал поступает на вход схемы совпадения элемента 2И-Ш1И 50, разрешая при поступлении в регистр 45 признака арифметической операции выборку следующего управляющего слова. Блокирование распределителя импульсов и обнуление регистра 45 возможно и при поступлении на вход элемента ИЛИ сигнала с последнего разряда распределителя, который одновременно поступает и на вход схемы совпадения элемента 2И-ИЛИ 50, разрешая, при поступлении в регистр 45 признака неарифметической операции выборку следующего управляющего слова. j Входы регистра 45 режимов работы подключены к соответствующим выходам блока 3, а выходы, кроме элемен7та 2И-ИЛИ 50, - к входам схем совпа дения элементов И 47, 2И-ИЛИ 48, ЗИ-ИЛИ 49 анализа разрядов распреде лителя импульсов: безусловной передачи управления, прерываний условной передачи управления, увеличения на 1 счетчика команд. В зависимости от наличия тех или иных признаков на выходах регистра режимов работы распределитель импульсов вырабатывает ту или иную пос ледовательность импульсов с соответствующих разрядов, что позволяет фор мировать рабочий цикл устройства в зависимости от решаемых задач. Формула изобретения 1. Однородная вычислительная система, содержащая N процессорных моду лей и центральный модуль микропрограммного управления, причем каждый процессорный модуль содержит арифметическо-логическое устройство, сдвигатель, буферньш регистр, регистр результата, регистр состояний, блок оперативной памяти, регистр микрокоманды, дешифратор, блок обмена информацией, блок формирования рабочего цикла, причем информационный вход регистра микрокоманд является входом управляющей шины процессорного модуля, выход регистра микрокоманд подключен к входу дешифратора, первый информационный выход блока оперативной памяти, выходрегистра результата и выход регистра состояний подключены через выходную внутреннюю шину данных к информационному входу блока обмена информацией и к входу первого операнда арифметическо-логического устройства, информационные входы блока оперативной памяти, регистр результата и регистр состояний подключены через входную внутреннюю шину данных к информационным выходам блоков обмена информацией и сдвигателя, информационный вход которого, через буферный регистр подключен к выходу результата арифметическо-логического устройства, вход второго операнда арифметическо-логического устройства подключен к второму информационному выходу блока оперативной памяти, информационный вход-выход блока обмена информацией является одноименным входом-выходом процес сорного модуля, входы-выходы призна588ка начала и признака окончания блока обмена информацией являются одноименными входами процессорного модуля, выход признака отсутствия обмена блока обмена информацией подключен к входу разрешения запуска блока формирования рабочего цикла, вход сброса которого подключен к выходу признака окончания операции арифметикб-логического устройства, входы-выходы старших и младших разрядов переноса которого являются одноименными входами-выходами процессорного модуля, вход запуска которого соединен с одпоименным входом блока формирования рабочего цикла, выход разрешения выборки которого подключен к входу синхронизации регистра микрйкоманды, вход переноса и выход переноса сдвигателя подключены к входам-выходам младших и старших разрядов арифметико-логического устройства соответственно, входы запуска процессорных модулей соединены с выходом разрешения центрального блока микропрограммного управления, информационные входы-выходы процессорных модулей образуют шину данных системы, вход-выход переноса старшего разряда i-ro процессорного модуля подключен к входувыходу переноса младшего разряда i+1-го процессорного модуля (,... N), вход-выход переноса старшего разряда N-ro процессорного модуля подключен к входу-выходу переноса младшего из разрядов первого процессорного модуля, входы-выходы признаков начала передачи и окончания передачи процессорных модулей соответственно объединены, вход запуска и вход инструкции центрального блока микропрограммного управления являются одноименными входами системы, отличающаяся тем, что, с целью повышения производительности системы за счет децентрализации управления, в каждый процессорный модуль введен блок постоянной памяти, адресные входы первой и второй групп блока постоянной памяти подключены к выходам дешифратора и выходам такто-, вых последовательностей блока формирования рабочего цикла, соответствующие выходы блока постоянной памяти подключены к входам синхронизации регистров состояний результата, к входам режимов работы сдвигателя, арифметико-логического устройства.

блока оперативной памяти, блока обмена информацией, блока формирования рабочего цикла и к выходам признаков работы процессорного модуля, выходы признаков работы процессорных модулей поразрядно объединены и подключены к адресным входам третьей группы входов блоков постоянной памяти процессорных модулей, входы управляющих шин процессорных модулей поразрядно объединены и подключены к выходу инструкций блока микропрограммного управления.

2. Система по п.I, о т л и ч а ющ а я с я тем, что блок формирования рабочего цикла содержит регистр режимов работы, распределитель импульсов, элемент И, два элемента 2И-ИЛИ, элемент ЗИ-ИЛИ и узел управления запуском, который содержит генератор импульсов, триггер пуска, элемент И, первый и второй входы которого подключены к входам генератора импульсов и триггера пуска соответственно, элемент ИЛИ, выход которого подключен к входам сброса триггера пуска и регистра режимов работы третий вход элемента И узла управления запуском, вход установки триггера пуска .и первый вход элемента ИЛИ являются входами разрешения запуска, запуска и сброса . блока соответственно, информационный вход регистра

режимов работы и выходы распределителя импульсов являются входом режимов , работы и выходами тактовой последовательности блока соответственно, выход второго элемента 2И-ИГШ является выходом разрешения выборки блока,выход элемента И подключен к входу тактирования первой секции распределителя импульсов, выход переноса которой подключен к первым входам элемента И блока и элемента 2И-ИЖ, выход элемента И блока подключен к входу тактирования второй секции распределителя импульсов, выход переноса которой подклю н к второму входу первого элемента 2И-ИЛИ, выход которого подключен к входу тактирования третьей секции распределителя импульсов, выход переноса которой подключен к первому входу элемента ЗИ-ИЛИ, выход которого подключен к входу тактирования четвертой секции распределителя импульсов, выход переноса которой соединен с первым входом второго элемента 2И-ИЛИ и с вторым входом элемента ИЛИ, второй вход второго элемента 2И-ИЛИ соединен с входом сброса блока, выходы соответствующих разрядов регистра режимов работы подключены к второму входу элемента И блока, третьему и четвертому входам первого и второго элемента 2И-ИЛИи к второму по шестой входам элемента ЗИ-ИЛИ.

J7

30

3S

3i

28

n

26

3

32

23

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорная вычислительная система | 1975 |

|

SU674025A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Процессор | 1986 |

|

SU1332328A1 |

| Многоканальный преобразователь угла поворота вала в код | 1983 |

|

SU1144190A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Операционное устройство микропроцессора | 1979 |

|

SU1164719A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

Изобретение относится к вычислительной технике и предназначено для построения высокопроизводительных вычислительных систем, в частности управляющих систем, работающих в реальном масштабе времени.Цель изобретения - расширение функциональных возможностей и упрощение структуры микропроцессорных систем. В состав процессорного модуля системы, состоящей из однотипных процессорных модулей и однотипных модулей управления, вводится постоянное запоминающее устройство (ПЗУ), на выходе которого формируются сигналы микроопераций, поступающие на управляющие входы всех блоков модуля, участвующих в непосредственной передаче и обработке данных. Вход ПЗУ через дещифратор связан с управляющей птной мо дуля, являющейся фактически адресной частью ПЗУ и выходами распределителя импульсов. Разрядность кодов ПЗУ превосходит разрядность управляющей шины, чем достигается возможность увелччения числа микроопераций, обеспечения параллели на их вьшолнения и организации любой последовательности сл их реализации. Несколько процессорных модулей, реализующих одновременно различные алгоритмы, могут объе.циняться своими управляющими щинами с соответствующим выходом одного модуля управления, что приводит к эконою мии числа модулей управления. 1 з.п. сл ф-лы, 4 ил. 1 СП оо

12

38

3lQLjE

JA 32

37

fpus.2

12

JL

Щ

23

tpuz.3

| Евреинов Э.В., Прангишвили И.В | |||

| Цифровые автоматы с настраиваемой структурой | |||

| - М.: Энергия, 974, с.135 - 139 | |||

| Микропроцессорная вычислительная система | 1975 |

|

SU674025A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-07—Публикация

1984-08-20—Подача