Изобретение относится к автоматике и вычислительной технике и может быть использовано, например, в специализированной автоматизированной системе контроля и управления (САСКУ) самостоятельно или в составе блока управления для программного управления процессом контроля и управления в реальнем масштабе времени.

Цель изобретения - повышение коэффициента использования оборудования за счет упорядочения исполнительных адресов по времени начала исполнения, что повышает быстродействие и расширяет область применения.

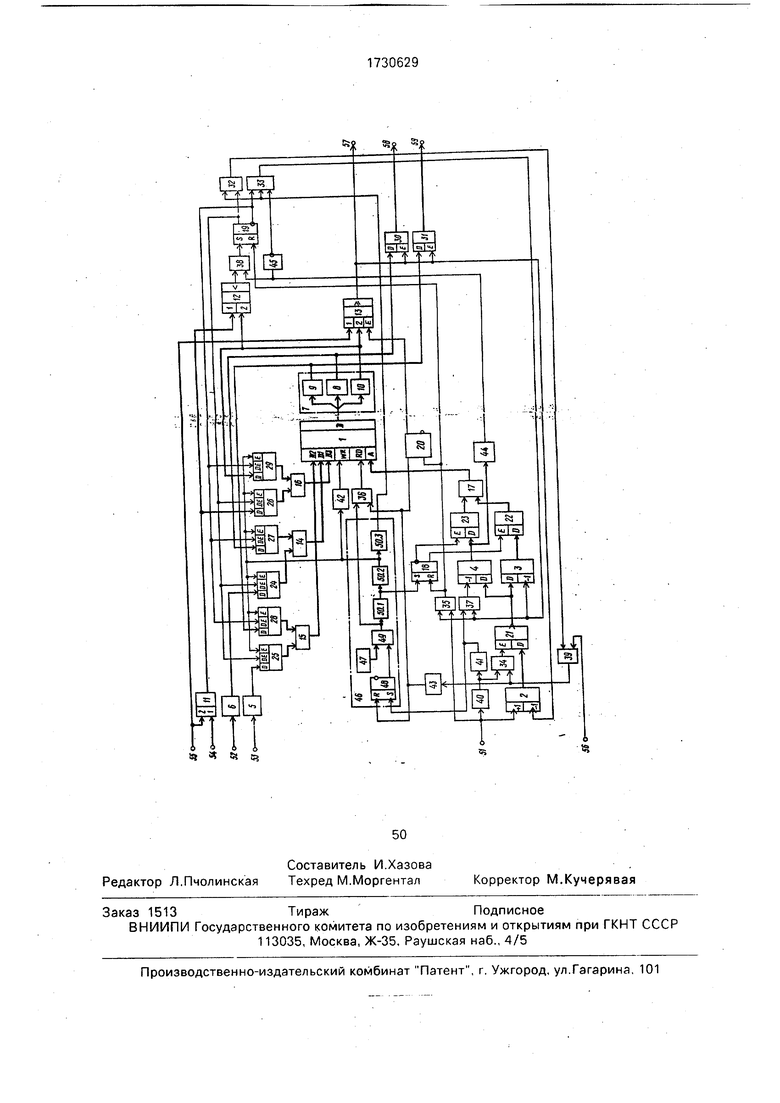

На чертеже представлена структурная схема устройства.

На чертеже обозначено: стековая память 1, первый счетчик 2 вершины стека 2 второй 3 и третий 4 счетчики адреса, выполненные в виде счетчиков-регистров, второй регистр 5 приема кодов исполнительного адреса, первый регистр 6 приема кода номера канала, блок 7 буферных регистров, состоящий из трех частей 8-10 для кодов исполнительного адреса, номера канала и времени ньчала исполнения соответственно, сумматор 11 второй 12 и первый 13 блоки сравнения, второй 14, первый 15. третий 16. четвертый

VJ со

о о го ю

17 блоки элементов ИЛИ, третий 18, первый 19 и второй 20 триггеры, одиннадцатый 21, девятый 22, восьмой 23, третий 24, первый 25, пятый 26, четвертый 27, второй 28, шестой 29, десятый 30 и седьмой 31 коммутаторы, первый 32 и второй 33 элементы И, третий 34, второй 35, пятый 36, первый 37, шестой 38, четвертый 39 элементы ИЛИ, третий 40, первый 41, второй 42, четвертый 43 элементы задержки, дешифратор 44 (нулевого кода), элемент НЕ 45, распределитель 46 импульсов, состоящий из генератора 47 импульсов, триггера 48 управления, элемента И 49 и элементов 50.1- 50.3 задержки, входы управления приемом кода 51, адреса 52, номера канала 53, кода паузы 54, текущего времени 55 и управления продолжением 56, выходы готовности 57, адреса 58 и номера канала 59.

Устройство для управления сопряжением процессора с абонентами работает следующим образом.

Рассмотрим работу устройства с его типичного состояния, когда на входы 51-56 уже неоднократно были поданы сигналы, в памяти 1 хранится информация, упорядоченная по времени начала исполнения и на вход 55 поступают сигналы кода текущего времени, изменяющиеся с определенным постоянным квантом. При этом количество обращений к устройству запоминается в счетчике 2 вершины стека.

Очередное функционирование устройства начинается с поступления сигнала на вход 51. На входе 52 установлены сигналы кода исполнительного адреса, на выходе 53 - кода номера канала, на входе 54 - кода времени паузы. Сигнал с входа 51 проходит на инкрементный вход счетчика 2, изменяя его состояние на единицу, и одновременно через элемент ИЛИ 35 устанавливает триггеры 18 - 20 в исходное состояние, а через элемент 40 задержки и элемент ИЛИ 34 разрешает через коммутатор 21 перезапись содержимого счетчика 2 в счетчики 3 и 4 адреса. Этот же сигнал через элемент 41 задержки запускает распределитель 46 импульсов установкой триггера 48 в состояние 1 и через элемент ИЛИ 37 уменьшает содержимое счетчика 4 на единицу. Содержимое счетчиков 3 и 4 отличается на единицу и указывает адрес вершины стека и предыдущего элемента стека. Состояние 1 триггера 48 открывает элемент И 49.и импульсы с выхода генератора 47 проходят на элементы 50.1-50.3 задержки, появляясь последовательно на четырех выходах распределителя 46 импульсов. Эти сигналы управляют изменением состояний элементов устройства.

По сигналу первого выхода распределителя 46, поступающему через элемент ИЛИ 36, формируется сигнал чтения информации с памяти 1 по адресу со счетчика 4, проходящему через коммутатор 23 по сигналу разрешения с нулевого выхода триггера 18 и блок элементов ИЛИ 17. Считанная информация заносится в блок 7 буферных регистров. Информация регистра 10. являющаяся

0 кодом ВНИ, подается на второй вход блока 12 сравнения, на первый вход которого поступает с сумматора 11 значение очередного (входного) кода ВНИ. Если значение входной информации меньше, чем считан5 ное из памяти 1, то сигналом с выхода блока 12 сравнения через элементы ИЛИ 38, триггер 19 переводится в состояние 1. Состояние 1 триггера 19 свидетельствует о том, что установлено место входной информации

0 в стеке, состояние О - что процедура ранжирования стека должна быть продолжена перемещением информации в памяти 1 до выполнения условия на блоке 12 сравнения. Сигнал с второго выхода распределите5 ля 46 импульсов устанавливает триггер 18 в состояние 1, разрешая прохождение содержимого счетчика 3 через коммутатор 22 и блок элементов ИЛИ 17 на адресный вход памяти 1.

0 Сигнал с третьего выхода распределителя 46 импульсов с элемента 50.3 задержки подается на входы разрешения коммутаторов 24 - 29 и, пройдя элемент 42 задержки, он выполняет запись информации с входов

5 D1 - D3 памяти 1. При состоянии 1 триггера 19, выходы которого заведены на входы блокировок коммутаторов 24 - 29, входной информацией памяти 1 является информация входных регистров 5 и 6 и сумматора 11,

0 пари О - информация регистров 8-10 блока 7 буферных регистров, которая является содержимым предыдущего элемента памяти 1.

Сигнал с четвертого выхода распреде5 лителя 46 импульсов, если процесс ранжирования не закончен и триггер 19 находится в состоянии О, проходит через элемент И 33, на втором входе которого присутствует сигнал 1 с выхода элементе НЕ 45, на

0 декрементные входы счетчика 3 непосредственно и через элемент ИЛИ 37 счетчика 4, а также через элемент ИЛИ 35 устанавливает триггеры 18 - 20 в исходное состояние и на адресном входе памяти 1 устанавливает

5 новое значение счетчика 4.

Распределитель 46 импульсов продолжает работать и под управлением очередных сигналов на его выходах выполняется ранжирование элемента в стеке (перемещение вверх). Это происходит до тех пор, пока

не определится место в стеке для входного ВНИ и на выходе блока сравнения 12 не появится сигнал, либо когда счетчик 4 не укажет на дно стека, т. е. его содержимое станет равным нулю В этом случае на выходе дешифратора 44 формируется сигнал. Этот сигнал и сигнал с выхода блока сравнения 12 через элемент ИЛИ 38 устанавливают триггер 19 в состояние 1. Тогда сигнал с четвертого выхода распределителя 46 проходит через элемент И 32 и элемент ИЛИ 39 и элемент ИЛИ 34 на разрешающий вход коммутатора 21 и содержимое счетчика 2 переписывается в счетчик 3 (устанавливается адрес вершины стека) и затем через коммутатор 22 и блок элементов ИЛИ 17 подается на адресный вход памяти 1. Спустя интервал времени, определяемый элементом 43 задержки, подается сигнал на нулевой вход триггера 48, прекращая работу распределителя 46 импульсов, на единичный вход триггера 20 и через элемент ИЛИ 36 на вход чтения памяти 1 содержимое вершины стека заносится в блок 7 буферных регистров. С регистра 10 значение ВНИ подается на второй вход блока 13 сравнения, на первый вход которого поступают сигналы кода текущего времени с входа 55 устройства, а на разрешающем входе присутствует сигнал с триггера 20. При достижении текущим временем значения, равного или большего ВНИ, появляется сигнал на выходе блока 13 и далев На управляющем выходе 57 готовности устройства. Этот сигнал дает разрешение на появление сигналов кода исполнительного адреса на выходе 58 с коммутатора 30 от регистра 8 и кода номера канала на выходе 59 с коммутатора 31 от регистра 9 и, кроме того, поступает йа де- крементный вход счетчика 2, уменьшая его значение на единицу. Этим действием заканчивается очередной цикл работы устройства.

Рассмотрим работу устройства при самом первом обращении к нему, когда содержимое счетчика 4 всегда равно нулю. В этом случае сигнал с выхода дешифратора 44 через элемент ИЛИ 38 устанавливает триггер 19 в состояние 1 и распределитель 46 импульсов работает всего один цикл, По сигналу с первого выхода происходит холостое чтение по нулевому адресу, сигнал с второго выхода устанавливает на входе памяти 1 адрес, равный единице (вершина стека), по сигналу с третьего выхода информация с входов 52-55 устройства записывается в память 1, сигнал с четвертого выхода управляет теми же функциями устройства, что и при нахождении триггера 19 в состоянии 1.

Очередной цикл работы устройства может быть инициирован управляющими сигналами на входе 51 и на входе 56. При поступлении управляющего сигнала на входе 56 через элементы ИЛИ 39 и 34 на разрешающий вход коммутатора 21 содержимое счетчика 2 переписывается в счетчик 3 и затем поступает на адресный вход памяти 1 через коммутатор 22 и блок элементов ИЛИ

0 17. С выхода элемента ИЛИ 39 через элемент задержки 43 сигнал устанавливает триггер 20 в состояние 1 и через элемент ИЛИ 36 подается на вход чтения памяти 1. Далее считывание информации вершины

5 стека памяти 1, сравнение на блоке 13, появление сигналов на выходах 57-59 устройства и окончание цикла работы происходит аналогично описанному.

Формула изобретения

0 Устройство для управления сопряжением процессора с абонентами, содержащее первый блок сравнения, выход которого соединен с первым счетным входом первого счетчика, второй блок сравнения, второй и

5 третий счетчики, с первого по третий триггеры, первый элемент задержки, выход которого соединен с первым входом первого элемента ИЛИ, второй элемент задержки, выход которого соединен с входом записи

0 памяти, третий и четвертый элементы задержки, первый и второй элемент И, с второго по четвертый элементы ИЛИ, отличающееся тем, что, с целью повышения коэффициента использования оборудова5 ния, в него введены одиннадцать коммутаторов, четыре блока элементов ИЛИ, два регистра, сумматор, дешифратор, распределитель импульсов, блок буферных регистров, два элемента ИЛИ, элемент НЕ. причем

0 вход управления приемом кода устройства соединен с вторым счетным входом первого счетчика, первым входом второго элемента ИЛИ и через третий элемент задержки с первым входом третьего элемента ИЛИ и

5 входом первого элемента задержки, выход которого соединен с входом запуска распределителя импульсов, первый выход которого соединен с входом второго элемента задержки и первыми входами с первого по

0 шестой коммутаторов, выходы первого и второго, третьего и четвертого, пятого и шестого коммутаторов соединены с входами соответственно с первого по третий блоков элементов ИЛИ, выходы .которых соедине5 ны с информационными входами памяти, выход которой соединен с входом блока буферных регистров, первый выход которого соединен с вторым входом второго коммутатора и первым входом седьмого коммутатора, входы адреса и номера канала

устройства через соответственно первый и второй регистры соединены с вторыми входами первого и третьего коммутаторов, третьи входы которых и второй вход пятого коммутатора соединены с первым выходом первого триггера и первым входом первого элемента И, выход которого через четвертый элемент ИЛИ соединен с вторым входом третьего элемента ИЛИ и входом четвертого элемента задержки, выход которого соединен с первыми входами второго триггера и пятого элемента ИЛИ и входом запрета распределителя импульсов, второй выход которого соединен с вторым входом пятого элемента ИЛИ, выход которого соединен с входом чтения памяти, адресный вход которой через четвертый блок элементов ИЛИ соединен с выходами восьмого и девятого коммутаторов, второй выход блока буферных регистров соединен с вторым входом четвертого коммутатора и первым входом десятого коммутатора, третий выход блока буферных регистров соединен с вторым входом шестого коммутатора и первыми входами первого и второго блоков сравнения, вход кода паузы устройства соединен с первым входом сумматора, выход которого соединен с третьим входом пятого коммутатора и вторым входом второго блока сравнения, выход которого соединен с первым входом шестого элемента ИЛИ, выход которого соединен с первым входом первого триггера, второй выход которого соединен с третьими входами второго, четвертого и шестого коммутаторов и первым входом второго элемента И, выход которого

соединен со счетным входом второго счетчика и вторыми входами первого и второго элементов ИЛИ, выход первого элемента ИЛИ соединен со счетным входом третьего

счетчика, выход которого соединен с первым входом восьмого коммутатора и через дешифратор с вторым входом шестого элемента ИЛИ и входом элемента НЕ, третий выход распределителя импульсов соединен

с вторыми входами первого и второго элементов И, выходы первого счетчика и третьего элемента ИЛИ через одиннадцатый коммутатор соединены с входами данных второго и третьего счетчиков, выход второго

счетчика соединен с первым входом девятого коммутатора, четвертый выход распределителя импульсов соединен с первым входом третьего триггера, выходы которого соединены с вторыми входами восьмого и

девятого коммутаторов, вход текущего времени устройства соединен с вторыми входами сумматора и первого блока сравнения, вход управления продолжением устройства соединен с входом четвертого

элемента ИЛИ, выход второго элемента ИЛИ соединен с вторыми входами с первого по третий триггеров, выход второго триггера соединен с третьим входом первого блока сравнения, выход которого соединен с вторыми входами седьмого и десятого коммутаторов, выходы второго блока сравнения, десятого и седьмого коммутаторов соединены соответственно с выходами готовности, адреса и номера канала устройства.

в ss 55

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Многоканальный анализатор электрофизиологических сигналов | 1991 |

|

SU1806603A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство тестового контроля | 1982 |

|

SU1075265A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано, например, в программных устройствах управления специализированных автоматизированных систем контроля для реализации последовательно-параллельных алгоритмов контроля и управления. Целью изобретения является повышение коэффициента использования оборудования. Сущность изобретения состоит в организации такой упорядоченной во времени начала исполнения последовательности исполнительных адресов групп команд, чтобы адрес первой, подлежащей к исполнению, группы команд располагался в вершине последовательности. При этом упорядочение выполняется при входе в устройство, а выход - в момент совпадения значений текущего системного времени и времени начала исполнения. Это достигается тем, что в устройство, содержащее два блока сравнения, три счетчика, три триггера, четыре элемента задержки, память, два элемента И, четыре элемента ИЛИ. введены два блока сравнения, два регистра, одиннадцать коммутаторов, четыре блока элементов ИЛИ, сумматор, дешифратор, распределитель импульсов, два элемента ИЛИ, блок буферных регистров, элемент НЕ и организованы обусловленные ими новые связи, 1 ил. (л

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1495807A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с памятью | 1989 |

|

SU1658161A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1989-10-25—Подача