11

Изобретение относится к области вычислительной техники и может быть использовано при статистической моделировании.

Цель изобретения - повышение точности.

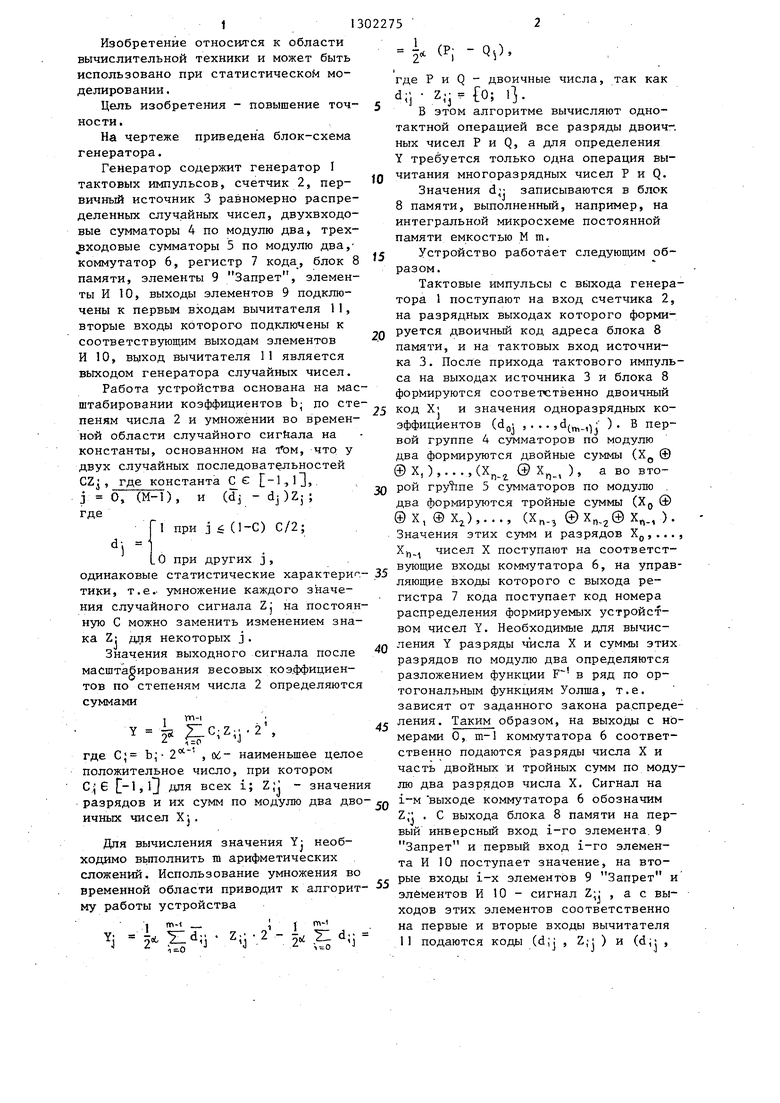

На чертеже приведена блок-схема генератора.

Генератор содержит генератор 1 тактовых импульсов, счетчик 2, пер- вичньй источник 3 равномерно распределенных случайных чисел, двухвкодо- вые сумматоры 4 по модулю два трех- входовые сумматоры 5 по модулю два, коммутатор 6, регистр 7 кода, блок 8 памяти, элементы 9 Запрет, элементы И 10, выходы элементов 9 подключены к первым входам вычитателя 11, вторые входы которого подключены к соответствующим выходам элементов И 10, выход вычитателя 11 является выходом генератора случайных чисел.

Работа устройства основана на масштабировании коэффициентов bj по степеням числа 2 и умножении во временной области случайного сигйала на константы, основанном на т ом, что у двух случайных последовательностей CZ , где константа С€ -l,j, j О, (М-1), и (dj - dj)Zj; где

1 при j с (1-е) с/2;

LO при других J,

одинаковые статистические характерна тики, т.е.. умножение каждого значения случайного сигнала Zj на постоянную С можно заменить изменением знака Z: для некоторых j.

Значения выходного сигнала после масштабирования весовых коэ.ффициен- тов по степеням числа 2 определяются суммами

1 w-i

40

2 & М 2

ГТ Т . о л/ .

где С; Ь, - 2 , наименьшее целое положительное число, при котором

, вующие входы коммутатора 6, на управляющие входы которого с выхода регистра 7 кода поступает код номера распределения формируемых устройством чисел Y. Необходимые для вычисления Y разряды числа X и суммы этих разрядов по модулю два определяются разложением функции в ряд по ортогональным функциям Уолша, т.е. зависят от заданного закона распредеjr ления. Таким образом, на выходы с номерами О, т-1 коммутатора 6 соответственно подаются разряды числа X и часть двойных и тройных сумм по модуС,; 6 -1,0 для всех i; Z;; - значения лю два разрядов числа X. Сигнал на разрядов и их сумм по модулю два дво- JQ i-м выходе коммутатора 6 обозначим ичньпс чисел X; ,Z;: . С выхода блока 8 памяти на пер

вый инверсный вход i-ro элемента. 9 Запрет и первый вход i-ro элемен)

Для вычисления значения У: необходимо вьгполнить m арифметических сложений. Использование умножения во

та И 10 поступает значение, на втоt-c рые входы i-x элементов 9 Запрет и временной области приводит к алгорит- элементов И 10 - сигнал Z;; , а с вы- му работы устройства элементов соответственно

на первые и вторые входы вычитателя 11 подаются коды (dij , Z;: ) и (d;- ,

1

m-1

d:;

1

2 J -.

- 2ei/ °- J

10

|«с (Р; - Q),

I

где Р и Q - двоичные числа, так как d;j Z,.j {0; l.

В этом алгоритме вычисляют одно- тактной операцией все разряды двоичных чисел Р и Q, а для определения Y требуется только одна операция вычитания многоразрядных чисел Р и Q.

Значения d;: записываются в блок 8 памяти, выполненный, например, на интегральной микросхеме постоянной памяти емкостью М т.

Устройство работает следующим образом.

Тактовые импульсы с выхода генератора 1 поступают на вход счетчика 2, на разрядных выходах которого форми- 20 РУется двоичный код адреса блока 8 памяти, и на тактовых вход источника 3. После прихода тактового импульса на выходах источника 3 и блока 8 формируются соответственно двоичный 25 код X и значения одноразрядных коэффициентов (dgj , . .. ,d,: ). В первой группе 4 сумматоров по модулю два формируются двойные суммы (Х ® ®Х, ),..., (Х ® Х, ), а во вто- JO рой группе 5 сумматоров по модулю . два формируются тройные суммы (Хд ®

0х,®х),..., (х„., ©х„.2©х., ).

Значения этих сумм и разрядов Х,..., Ху, чисел X поступают на соответст40

, вующие входы коммутатора 6, на управляющие входы которого с выхода регистра 7 кода поступает код номера распределения формируемых устройством чисел Y. Необходимые для вычисления Y разряды числа X и суммы этих разрядов по модулю два определяются разложением функции в ряд по ортогональным функциям Уолша, т.е. зависят от заданного закона распредеjr ления. Таким образом, на выходы с номерами О, т-1 коммутатора 6 соответственно подаются разряды числа X и часть двойных и тройных сумм по модулю два разрядов числа X. Сигнал на JQ i-м выходе коммутатора 6 обозначим Z;: . С выхода блока 8 памяти на пер

та И 10 поступает значение, на втоZj; ), которые равны i-м разрядам двоичных чисел Р- и О j. Выходы (n-ci) старших разрядов вычитателя являются выходом двоичного числа.

Y:

Форму

PJ - Qj)/2 . изобретения

Генератор случайных чисел, содержащий генератор тактовых импульсов, выход которого соединен с входом Опрос первичного источника равномерно распределенных случайных чисел, группу двухвходовых сумматоров по модулю два, входы которых соединены с выходами первичного источника pasHjiMepно распределенных случайньЬс чисел соответственно, группу трехвходовых сумматоров по модулю два, входы которых соединены с выxoдa 3и разрядов первичного источника равномерно распре- деленных случайных чисел соответственно, отличающийся тем, что,.с целью повышения точности, он содержит коммутатор, регистр кода, группу элементов И, вычитатель,группу элементов Запрет, блок памяти и счетчик, счетный вход которого соединен с выходом генератора тактовых импульсов, а информационный выход

Составитель А.Карасов Редактор Л.Гратилло Техред Л.Олейник Корректор А.Ильин

Заказ 1217/48 Тираж 673Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

счетчика соединен с адресным входом блока памяти, выходы разрядов которого соединены с HHBepCHbiM i входами элементов Запрет группы соответственно и.с первыми входами элементов И группы соответственно, вторые входы которых соединены с прямыми входами соответствующих элементов Запрет группы и подключены к соответствующим выходам коммутатора, первая группа информационных входов которого соединена с выходами первичного источника равномерно распределенных случайных чисел соответственно, выходы двухвходовых сумматоров по модулю два группы соединены с второй группой информационных входов коммутатора соответственно, третья группа информационных входов которого Я:оединена с выходами трехвходовых сумматоров по модулю два группы соответственно, выход регистра кода соединен с управляющим входом коммутатора выходы элементов Запрет группы соединены с группой входов уменьшаемого вычитателя, выходы элементов И группы соединены с группой входов вычитаемого вычитателя, выход которого является выходом генератора,

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Многоканальный релейный спектроанализатор | 1983 |

|

SU1140129A1 |

| Генератор случайных чисел | 1985 |

|

SU1262492A1 |

| Генератор функций Уолша | 1985 |

|

SU1262470A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Устройство для выполнения преобразования Фурье | 1987 |

|

SU1424027A1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| Генератор случайных чисел | 1981 |

|

SU980093A1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1137479A1 |

Изобретение относится к области вычислительной техники и может быть использовано при статистическом моделировании. Цель изобретения - повышение точности. Генератор содержит генератор 1 тактовых импульсов, счетчик 2, первичньш источник 3 тактовых импульсов, двухвходовые импульсы 4 по модулю два, трехвходовые сумматоры 5 по модулю два, коммутатор- 6, регистр 7 кода, блок 8 памяти, элементы ЗАПРЕТ 9, элементы И 10, вы- читатель 11. 1 ил.

| Генератор случайных чисел | 1981 |

|

SU991421A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования случайного процесса | 1977 |

|

SU680008A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-07—Публикация

1985-12-29—Подача