Изобретение относится к вычислительной технике и предназначено для формирования квадратов двух величин и извлечения квадратного корня.

Цель изобретения - расширение класса решаемых задач за счет обеспечения вычисления корня квадратного из суммы квадратов двух чисел.

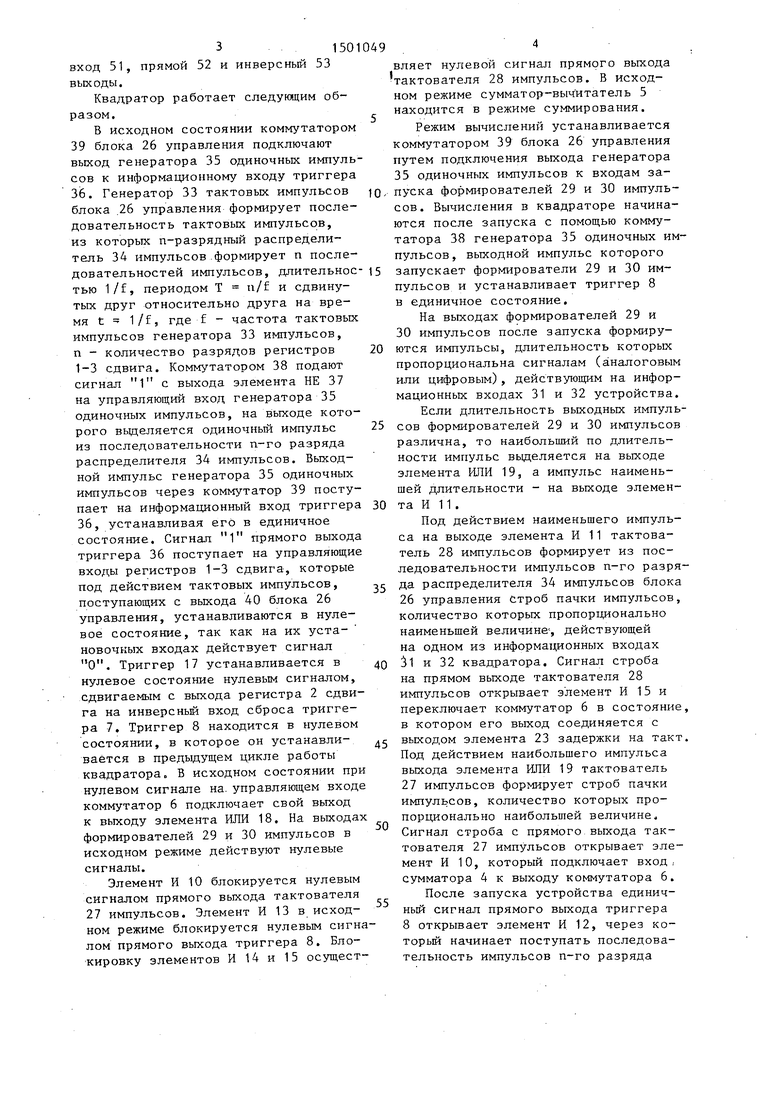

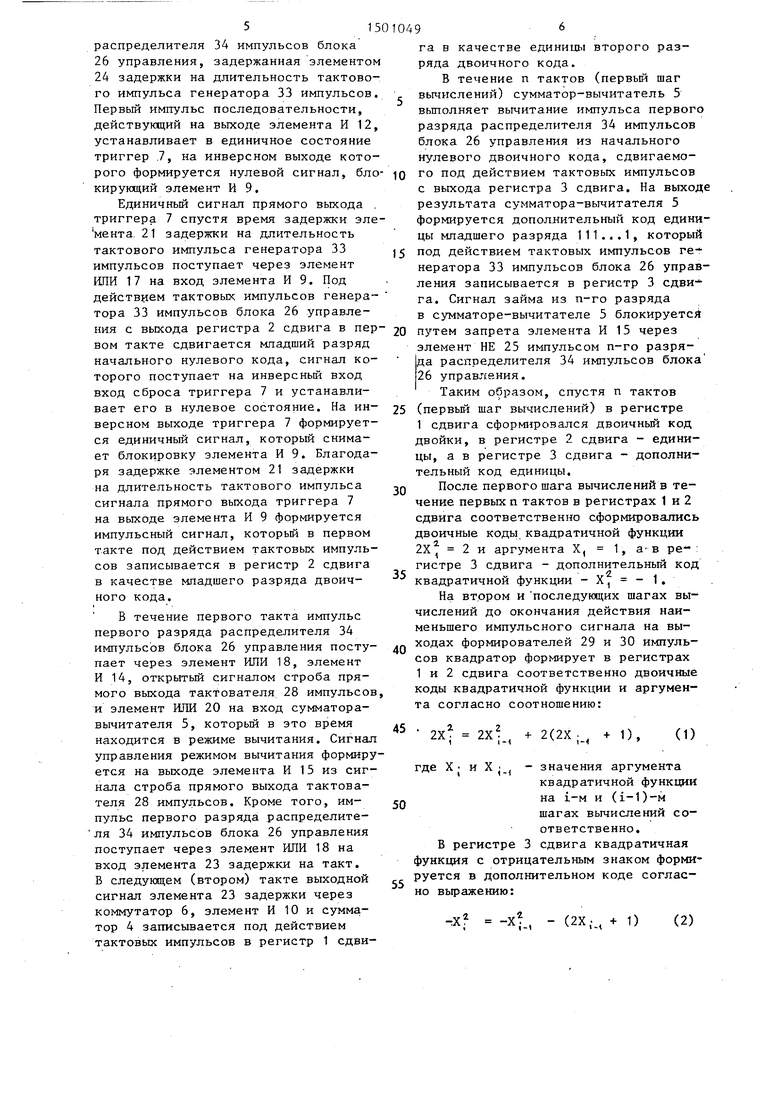

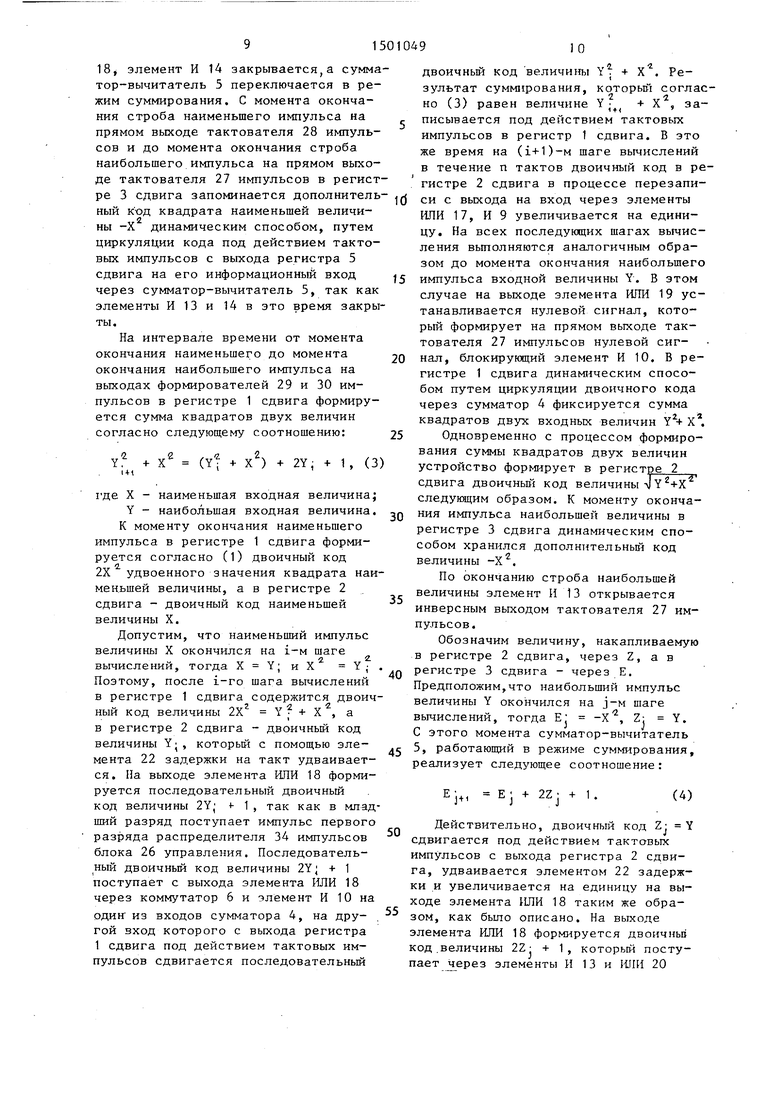

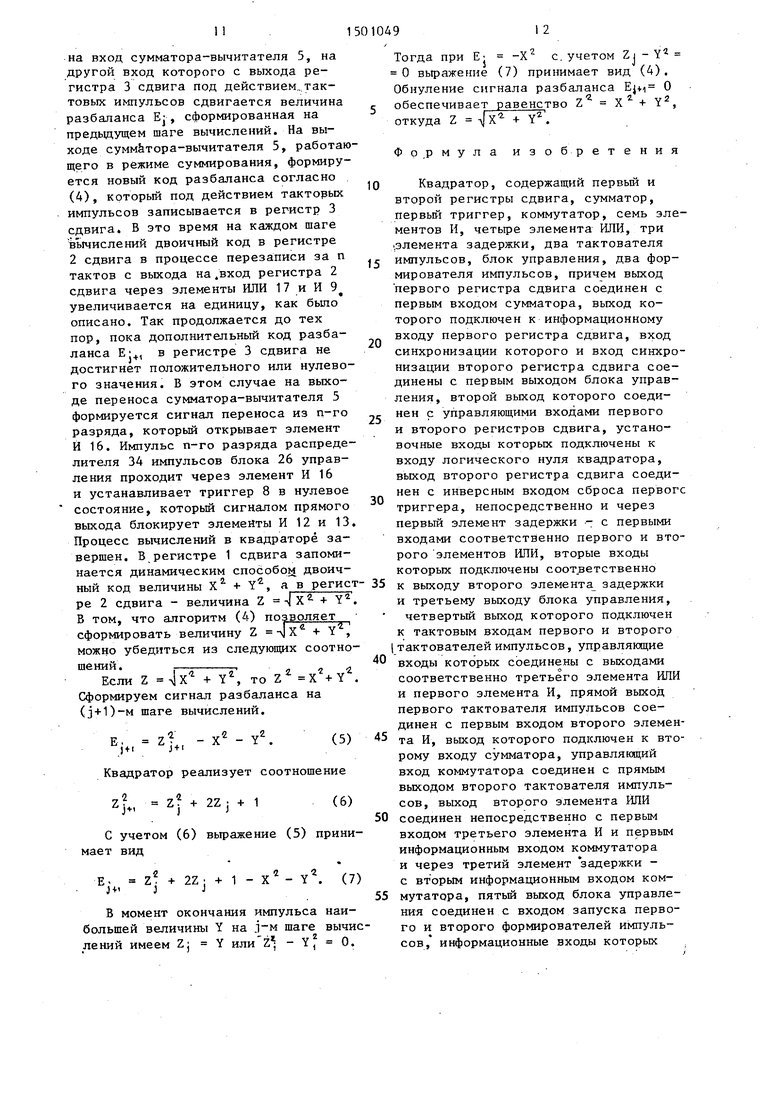

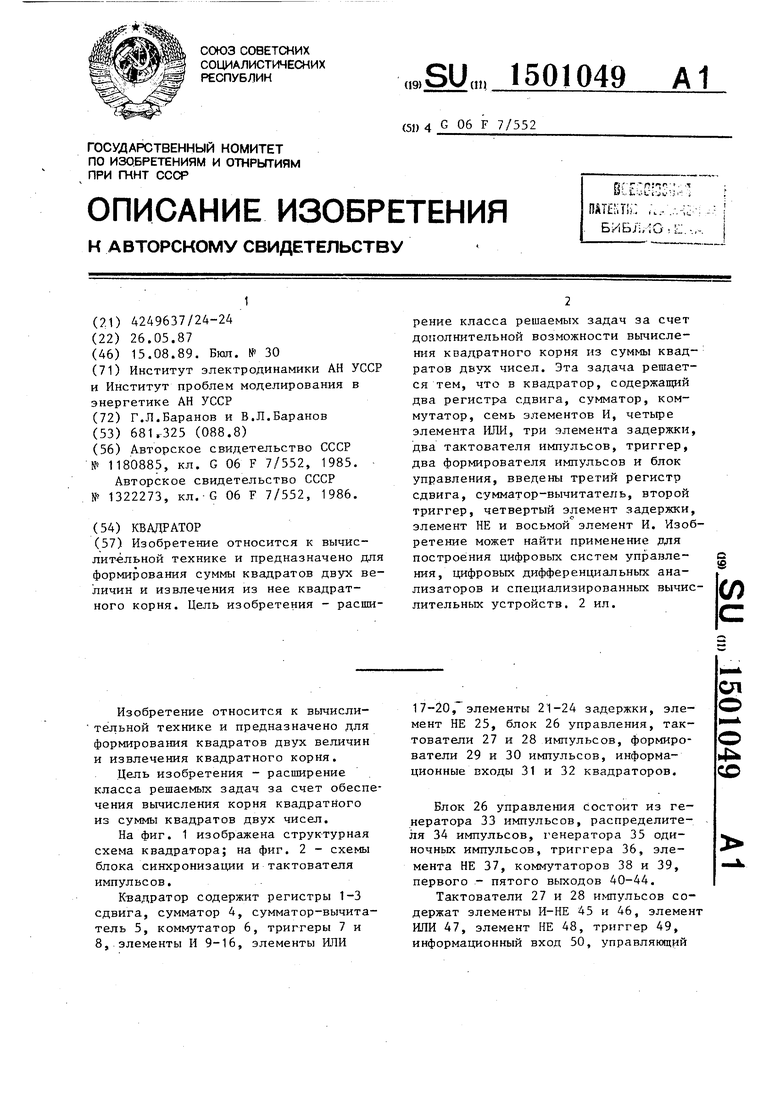

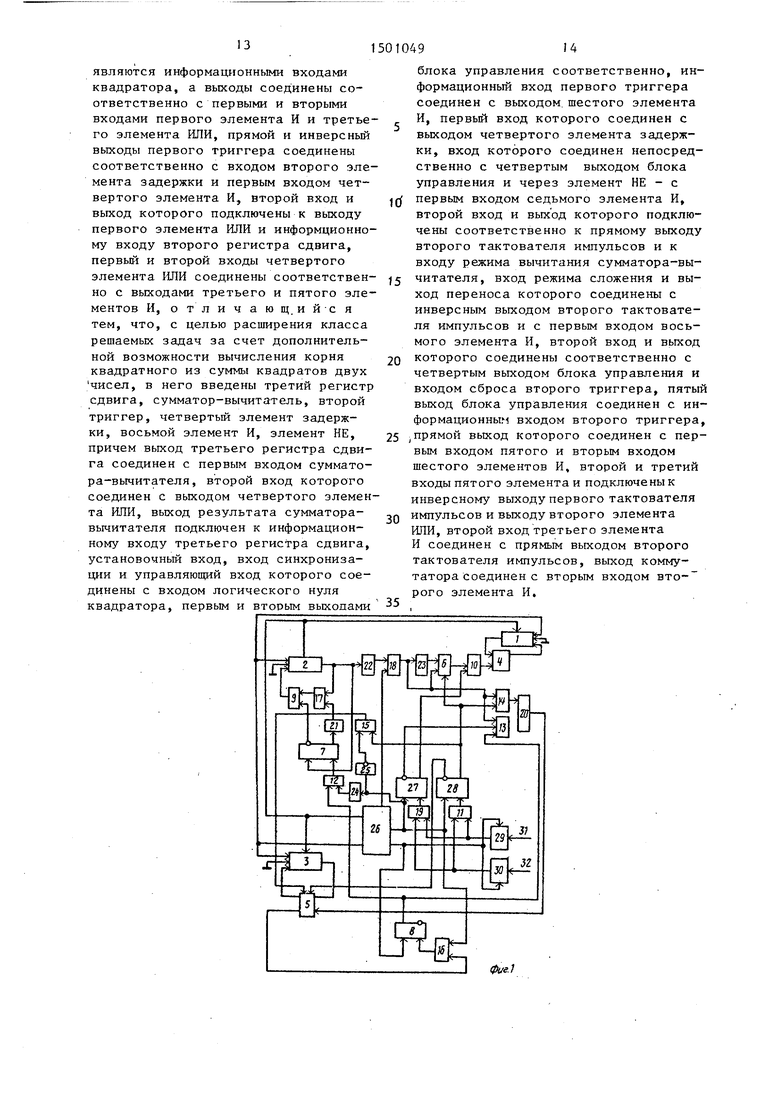

На фиг. 1 изображена структурная схема квадратора; на фиг. 2 - схемы блока синхронизации и тактователя импульсов.

Квадратор содержит регистры 1-3 сдвига, сумматор 4, сумматор-вычитатель 5, коммутатор 6, триггеры 7 и 8, элементы И 9-16, элементы ИЛИ

17-20, элементы 21-24 задержки, элемент НЕ 25, блок 26 управления, так- тователи 27 и 28 импульсов, формирователи 29 и 30 импульсов, информационные входы 31 и 32 квадраторов.

Блок 26 управления состоит из генератора 33 импульсов, распределителя 34 импульсов, генератора 35 одиночных импульсов, триггера 36, элемента НЕ 37, коммутаторов 38 и 39, первого - пятого выходов 40-44.

Тактователи 27 и 28 импульсов содержат элементы И-НЕ 45 и 46, элемент Ш1И 47, элемент НЕ 48, триггер 49, информационный вход 50, управляющий

СП

4

3150

вход 51, прямой 52 и инверсный 53 выходы.

Квадратор работает следующим образом.

В исходном состоянии коммутатором 39 блока 26 управления подключают выход генератора 35 одиночных импульсов к информационному входу триггера 36. Генератор 33 тактовых импульсов блока .26 управления формирует последовательность тактовых импульсов, из которых п-разрядный распределитель 34 импульсов формирует п последовательностей импульсов, длительное тью 1/f, периодом Т n/f и сдвинутых друг относительно друга на время t 5 1/f, где f - частота тактовых импульсов генератора 33 импульсов, п - количество разрядов регистров 1-3 сдвига. Коммутатором 38 подают сигнал 1 с выхода элемента НЕ 37 на управляющий вход генератора 35 одиночных импульсов, на выходе которого вьщеляется одиночньш импульс из последовательности п-го разряда распределителя 34 импульсов. Выходной импульс генератора 35 одиночных импульсов через коммутатор 39 поступает на информационный вход триггера 36, устанавливая его в единичное состояние. Сигнал 1 прямого выхода триггера 36 поступает на управляющие входы регистров 1-3 сдвига, которые под действием тактовых импульсов, поступающих с выхода 40 блока 26 управления, устанавливаются в нулевое состояние, так как на их установочных входах действует сигнал О. Триггер 17 устанавливается в нулевое состояние нулевым сигналом, сдвигаемым с выхода регистра 2 сдвига на инверсньй вход сброса триггера 7. Триггер 8 находится в нулевом состоянии, в которое он устанавли- ваётся в предыдущем цикле работы квадратора. В исходном состоянии при нулевом сигнале на. управляющем входе коммутатор 6 подключает свой выход к выходу элемента ИЛИ 18. На выходах формирователей 29 и 30 импульсов в исходном режиме действуют нулевые сигналы.

Элемент И 10 блокируется нулевым сигналом прямого выхода тактователя 27 импульсов. Элемент И 13 в исходном режиме блокируется нулевым сигналом прямого выхода триггера В. Блокировку элементов И 14 и 15 осущест

- 5 0 5 0 с 0

0

5

вляет нулевой сигнал прямого выхода тактователя 28 импульсов. В исходном режиме сумматор-выч итатель 5 находится в режиме суммирования.

Режим вычислений устанавливается коммутатором 39 блока 26 управления путем подключения выхода генератора 35 одиночных импульсов к входам запуска формирователей 29 и 30 импульсов. Вычисления в квадраторе начинаются после запуска с помощью коммутатора 38 генератора 35 одиночных импульсов, выходной импульс которого запускает формирователи 29 и 30 импульсов и устанавливает триггер 8 в единичное состояние.

На выходах формирователей 29 и 30 импульсов после запуска формируются импульсы, длительность которых пропорциональна сигналам (аналоговым или цифровым), действующим на информационных входах 31 и 32 устройства.

Если длительность выходных импульсов формирователей 29 и 30 импульсов различна, то наибольший по длительности импульс выделяется на выходе элемента ИЛИ 19, а импульс наименьшей длительности - на выходе элемента И 1 1 .

Под действием наименьшего импульса на выходе элемента И 11 тактова- тель 28 импульсов формирует из последовательности импульсов п-го разряда распределителя 34 импульсов блока

26управления строб пачки импульсов, количество которых пропорционально наименьшей величине-, действующей

на одном из информационных входах Si и 32 квадратора. Сигнал строба на прямом выходе тактователя 28 импульсов открывает элемент И 15 и переключает коммутатор 6 в состояние, в котором его выход соединяется с выходом элемента 23 задержки на такт. Под действием наибольшего импульса выхода элемента ИЛИ 19 тактователь

27импульсов формирует строб пачки импульсов, количество которых пропорционально наибольшей величине. Сигнал строба с прямого выхода тактователя 27 импульсов открывает элемент И 10, который подключает вход, сумматора 4 к выходу коммутатора 6.

После запуска устройства единичный сигнал прямого выхода триггера 8 открывает элемент И 12, через ко- торьй начинает поступать последовательность импульсов п-го разряда

10

15

20

30

35

40

45

50

51501049

распределителя 34 импульсов блока 26 управления, задержанная элементом 24 задержки на длительность тактового импульса генератора 33 импульсов. Первый импульс последовательности, действующий на выходе элемента И 12, устанавливает в единичное состояние триггер .7, на инверсном выходе которого формируется нулевой сигнал, блокирующий элемент И 9.

Единичньш сигнал прямого выхода триггера 7 спустя время задержки эле- мента 21 задержки на длительность тактового импульса генератора 33 импульсов поступает через элемент ИЛИ 17 на вход элемента И 9. Под действием тактовых импульсов генера- тора 33 импульсов блока 26 управления с выхода регистра 2 сдвига в первом такте сдвигается младший разряд начального нулевого кода, сигнал которого поступает на инверсный вход вход сброса триггера 7 и устанавливает его в нулевое состояние. На инверсном выходе триггера 7 формируется единичный сигнал, который снимает блокировку элемента И 9, Благодаря задержке элементом 21 задержки на длительность тактового импульса сигнала прямого выхода триггера 7 на выходе элемента И 9 формируется импульсный сигнал, который в первом такте под действием тактовых импульсов записывается в регистр 2 сдвига в качестве мпадшего разряда двоичного кода,

В течение первого такта импульс первого разряда распределителя 34 импульсов блока 26 управления поступает через элемент ИЛИ 18, элемент И 14, открытый сигналом строба прямого выхода тактователя 28 импульсов, и элемент ИЛИ 20 на вход сумматора- вычитателя 5, который в это время находится в режиме вычитания. Сигнал управления режимом вычитания формируется на выходе элемента И 15 из сигнала строба прямого выхода тактователя 28 импульсов. Кроме того, импульс первого разряда распределите- я 34 импульсов блока 26 управления оступает через элемент ИЛИ 18 на вход элемента 23 задержки на такт, В следующем (втором) такте выходной сигнал элемента 23 задержки через оммутатор 6, элемент И 10 и суммаор 4 записывается под действием актовых импульсов в регистр 1 сдвил

25 ( д

те

че сд дв

ги кв

чи ме хо со ко та

гд

55

фу ру но

0

5

0

га в качестве единицы второго разряда двоичного кода.

В течение п тактов (первый шаг вычислений) сумматор-вычитатель 5 вьтолняет вычитание импульса первого разряда распределителя 34 импульсов блока 26 управления из начального нулевого двоичного кода, сдвигаемого под действием тактовых импульсов с выхода регистра 3 сдвига. На выходе результата сумматора-вьгчитателя 5 формируется дополнительный код единицы младшего разряда 111 ,. , 1 , который под действием тактовых импульсов ге- нератора 33 импульсов блока 26 управления записывается в регистр 3 сдви- га. Сигнал займа из п-го разряда в сумматоре-вычитателе 5 блокируется путем запрета элемента И 15 через элемент НЕ 25 импульсом п-го разря- 1да распределителя 34 импульсов блока 26 управления,

Таким образом, спустя п тактов 5 (первый шаг вычислений) в регистре 1 сдвига сформировался двоичньм код двойки, в регистре 2 сдвига - едини0

5

0

цы, а в регистре 3 сдвига - дополнительный код единицы,

После первого шага вычислений в течение первых п тактов в регистрах 1 и 2 сдвига соответственно сформировались двоичные коды квадратичной функции

л

2Х 2 и аргумента X, 1, а в ре-: гистре 3 сдвига - дополнительный код квадратичной функции X, - 1,

На втором и последующих шагах вычислений до окончания действия наименьшего импульсного сигнала на выходах формирователей 29 и 30 импульсов квадратор формирует в регистрах 1 и 2 сдвига соответственно двоичные коды квадратичной функции и аргумента согласно соотношению:

2Х 2Х.,

+ 2(2Х .

1).

(1)

где X. и X

- значения аргумента квадратичной функции на i-M и (i-l)-M шагах вычислений соответственно,

В регистре 3 сдвига квадратичная функция с отрицательным знаком формируется в дополнительном коде согласно выражению:

у2 у1

-

- (2Х,.., + 1)

(2)

Например, на i-м шаге вычислений под действием тактовых импульсов, формируемых генератором 33 имггуль- сов блока 26 управления, на первый вход сумматора 4 сдвигается начиная с младшего разряда последовательный двоичный код величины 2Х| , сформированный на предьщущем (1-1)-м шаге вычислений, а с выхода регистра 2 сдвигается начиная с младшего разряда последовательный двоичный код аргумента , которьй задерживается элементом 22 задержки на такт. На выходе,элемента 22 задержки формируется -последовательный двоичный код величины 2Х j. , в младшем разряде которого всегда содержится нулевой сигнал. Импульс первого разряда распределителя 34 импульсов блока 26 управления поступает на пер вьм вход элемента ИЛИ 18 одновременно с поступлением на его второй вход с выхода элемента 22 задержки младшего разряда двоичного кода величины 2Х;., . На выходе элемента ИЛИ 18 формируется последовательньй двоичный код величины +1, из которого элемент 23 задержки на такт формируе последовательный двоичный код величины 2(2Х;,, + 1), поступающий через коммутатор 6 и элемент И 10 на вход сумматора 4. Под действием тактовых импульсов -на другой вход сумматора 4

с выхода регистра 1 сдвига поступает начиная с младшего-разряда последо-

вательный код величины 2Х , , сфор-г мированный на предьщущем шаге вычисления. На выходе сумматора 4 согласно соотношению (1) формируется последовательньй двоичный код величины 2Х- , который под действием тактовых импульсов записывается в регистр 1 сдвига.

На каждом шаге вычислений в регистре 2 сдвига двоичньй код X ;, увеличивается на единицу. Действительно установка триггера 7 в единич ное состояние импульсом последовательности выхода элемент И 12 обеспе чивает разрыв цепи циркуляции кодов с выхода регистра 2 сдвига на его информационный вход, так как элемент И 9 закрыт нулевым сигналом инверсного выхода триггера 7.

До возврата триггера 7 в нулевое состояние в младшие разряды двоичного кода регистра 2 сдвига записываются нулевые сигналы. Триггер 7 воз0

5

0

5

0

5

0

5

0

5

вращает в нулевое состояние первый начиная с младшего разряда нулевой сигнал двоичного кода, который сдвигается под действием тактовых импульсов с выхода регистра 2 сдвига. Переход триггера 7 из единичного состояния в нулевое приводит к формированию на выходе элемента И 9 импульсного сигнала благодаря задержке элементом 21 на длительность тактового импульса единичного сигнала прямого выхода триггера 7 его предыдущего состояния. Следовательно, вместо первого начиная с младшего разряда нулевого разряда двоичного кода, сдвигаемого под действием тактовых импульсов с выхода регистра 2, на его информационный вход поступает импульс, сформированный на выходе элемента И 9. Остальные разряды двоичного кода, сдвигаемого с выхода регистра 2, переписываются без изменения через элементы ИЛИ 17 и И 9 в регистр 2 сдвига ; Таким образом, двоичный код в регистре 2сдвига на каждом шаге вычислений за время п тактов увеличивается на единицу и соответствует количеству импульсов, действунхдих на выходе элемента И 12 с момента запуска устройства.

Одновременно в регистре 3 сдвига формируется дополнительный код отрицательной величины квадратичной функции -X. согласно вьфажению (2). Последовательньй двоичный код величины 2Х;, + 1, сформированньй на i-M шаге вычислений, поступает с выхода элемента ИЛИ 18 на вход сумматора-вычитателя 5 через элементы И 14,и ИЛИ 20. Под действием : тактовых импульсов с выхода регистра З поступает начиная с младшего разряда дополнительньй код величины - х|, , сформированньй на предьщущем

(i-1)-M шаге вычислений. Сумматор-вы- читатель 5 выполняет вычитание согласно выражению (2), а дополнительный код результата -X записывается под действием тактовьк импульсов в регистр 3 сдвига.

Устройство работает аналогичным . образом до окончания действия наименьшего импульса на одном из выходов формирователей 29 и 30 импульсов. После окончания -строба наименьшего импульса, на прямом выходе тактователя 28 импульсов коммутатор 6 подключает свой выход к выходу элемента ИЛИ

18j элемент И 14 закрывается, а сумма тор-вычитатель 5 переключается в режим суммирования. С момента окончания строба наименьшего импульса на прямом выходе тактователя 28 импульсов и до момента окончания строба наибольшего импульса на прямом выходе тактователя 27 импульсов в регистре 3 сдвига запоминается дополнитель ный код квадрата наименьшей величины -X динамическим способом, путем циркуляции кода под действием тактовых импульсов с выхода регистра 5 сдвига на его информационный вход через сумматор-вычитатель 5, так как элементы И 13 и 14 в это время закрыты.

На интервале времени от момента окончания наименьшего до момента окончания наибольшего импульса на выходах формирователей 29 и 30 импульсов в регистре 1 сдвига формируется сумма квадратов двух величин согласно следующему соотношению:

+ 2Y; 1, (3)

входная величина; я величина.

К моменту окончания наименьшего импульса в регистре 1 сдвига формируется согласно (1) двоичный код 2Х удвоенного значения квадрата наименьшей величины, а в регистре 2 сдвига - двоичный код наименьшей величины X.

Допустим, что наименьший импульс

величины X окончился на i-м шаге

2 вычислений, тогда X Y; и X Y ;

Поэтому, после i-ro шага вычислений

в регистре 1 2

сдвига содержится двоич л

НЫЙ код величины 2Х У + X , а

в регистре / сдвига - двоичный код величины У;, который с помощью элемента 22 задержки на такт удваивается. Па выходе элемента ИЛИ 18 формируется последовательный двоичный код величины 2У; - 1 , так как в младший разряд поступает импульс первого разряда распределителя 34 импульсов блока 26 управления. Последовательный двоичный код величины 2У; + 1 поступает с выхода элемента ИЛИ 18 через коммутатор 6 и элемент И 10 на один из входов сумматора 4, на другой вход которого с выхода регистра 1 сдвига под действием тактовых импульсов сдвигается последовательный

х

,1

двоичньй код величины У . + X . Результат суммирования, который согласно (3) равен величине У ; + X , записывается под действием тактовых импульсов в регистр 1 сдвига. В это же время на (1+1)-м шаге вычислений в течение п тактов двоичный код в регистре 2 сдвига в процессе перезаписи с выхода на вход через элементы ИЛИ 17, И 9 увеличивается на единицу. На всех последующих шагах вычисления вьтолняются аналогичным образом до момента окончания наибольшего импульса входной величины У. В этом случае на выходе элемента ИЛИ 19 устанавливается нулевой сигнал, который формирует на прямом выходе тактователя 27 импульсов нулевой сиг- 0 нал, блокируюш;ий элемент И 10. В регистре 1 сдвига динамическим способом путем циркуляции двоичного кода через сумматор 4 фиксируется сумма квадратов двух входных величин х . Одновременно с процессом формирования суммы квадратов двух величин устройство формирует в регистре 2

5

5

5

сдвига двоичный код величины следугацим образом. К моменту оконча- Q ния импульса наибольшей величины в регистре 3 сдвига динамическим способом хранился дополнительньд код величины -Х.

По окончанию строба наибольшей величины элемент И 13 открывается инверсным выходом тактователя 27 импульсов.

Обозначим величину, накапливаемую в регистре 2 сдвига, через Z, а в регистре 3 сдвига - через Е. Предположим,что наибольший импульс величины У окончился на j-м шаге вычислений, тогда Е; -х , Z; У. С этого момента сумматор-вычитатель 5 5, работающий в режиме суммирования, реализует следующее соотношение :

0

Е;

J+

Е ; + 2Z ; + 1 .

(4)

Действительно, двоичный код Z: Y сдвигается под действием тактовых импульсов с выхода регистра 2 сдвига, удваивается элементом 22 задержки и увеличивается на единицу на выходе элемента ИЛИ 18 таким же образом, как было описано. На выходе элемента ИЛИ 18 формируется двоичньп код.величины 2Z- + 1, которьй поступает через элементы И 13 и Ш1И 20

на вход сумматора-вычитателя 5, на другой вход которого с выхода регистра 3 сдвига под действием, тактовых импульсов сдвигается величина разбаланса Е:, сформированная на предыдущем шаге вычислений. На выходе сумм&тора-вычитателя 5, работающего в режиме суммирования, формируется новый код разбаланса согласно (4), который под действием такторых импульсов записывается в регистр 3 сдвига. В это время на каждом шаге вьмислений двоичный код в регистре 2 сдвига в процессе перезаписи за п тактов с выхода на .вход регистра 2 сдвига через элементы ИЛИ 17 и И 9 увеличивается на единицу, как бьшо описано. Так продолжается до тех пор, пока дополнительный код разбаланса Е:., в регистре 3 сдвига не достигнет положительного или нулевого значения. В этом случае на выходе переноса сумматора-вычитателя 5 формируется сигнал переноса из п-го разряда, который открывает элемент И 16. Импульс п-го разряда распределителя 34 импульсов блока 26 управления проходит через элемент И 16 и устанавливает триггер 8 в нулевое состояние, который сигналом прямого выхода блокирует элементы И 12 и 13. Процесс вычислений в квадраторе завершен. В регистре 1 сдвига запоминается динамическим способо двоичный код величины Х + Y, а в регист ре 2 сдвига - величина Z NX + Y.

Тогда при Е -X

. --.с. учетом Zj - Y

0 выражение (7) принимает вид (4). Обнуление сигнала разбаланса Eui О

Z 2.

обеспечивает равенство Z X + откуда Z л|х

+

Y,

20

25

30

В том, что алгоритм (4) позволяет сформировать величину Z + Y , можно убедиться из следующих соотношений.

Если Z Х + Y ,

то Z xVY.

Сформируем сигнал разбаланса на (з+1)-м шаге вычислений.

о -99

Е,ч- j.. -х -Y .

Квадратор реализует соотношение

Z

Zj + 2Zj + 1

С учетом (6) выражение (5) принимает вид

.

Е. Z + 2Zj + 1 - Х - Y. (7)

В момент окончания импульса наибольшей величины Y на j-м шаге вычис W Z

лений имеем Zj Y или Z; - Y, 0.

Фо.рмула изобретения

10 Квадратор, содержащий первый и второй регистры сдвига, сумматор, первый триггер, коммутатор, семь элементов И, четыре элемента ИЛИ, три элемента задержки, два тактователя

J5 импульсов, блок управления, два формирователя импульсов, причем выход первого регистра сдвига соединен с первым входом сумматора, выход которого подключен к информационному входу первого регистра сдвига, вход синхронизации которого и вход синхронизации второго регистра сдвига соединены с первым выходом блока управления, второй выход которого соединен с управляющими входами первого и второго регистров сдвига, установочные входы которых подключены к входу логического нуля квадратора, выход второго регистра сдвига соединен с инверсным входом сброса первого триггера, непосредственно и через первый элемент задержки - с первыми входами соответственно первого и второго элементов ИЛИ, вторые входы которых подключены соот.ветственно к выходу второго элемента задержки и третьему выходу блока управления, четвертый выход которого подключен к тактовым входам первого и второго 1 тактователей импульсов, управляющие входы которых соединены с выходами соответственно третьего элемента ИЛИ и первого элемента И, прямой выход первого тактователя импульсов соединен с первым входом второго элемен(5)45 та И, выход которого подключен к второму входу сумматора, управляющий вход коммутатора соединен с прямым выходом второго тактователя импуль(6)сов, выход второго элемента ШИ 50 соединен непосредственно с первым

входом третьего элемента И и первым информационным входом коммутатора и через третий элемент задержки - с вт орым информационным входом ком- 55 мутатора, пятый выход блока управления соединен с входом запуска первого и второго формирователей импульсов, информационные входы которых

- 35

40

Тогда при Е -X

. --.с. учетом Zj - Y

0 выражение (7) принимает вид (4). Обнуление сигнала разбаланса Eui О

Z 2.

обеспечивает равенство Z X + откуда Z л|х

+

Y,

J5

- 35

являются информационными входами квадратора, а выходы соединены соответственно с первыми и вторыми входами первого элемента И и третьего элемента ИЛИ, прямой и инверсный выходы первого триггера соединены соответственно с входом второго элемента задержки и первым входом четвертого элемента И, второй вход и выход которого подключены к выходу первого элемента ИЛИ и информционно- му входу второго регистра сдвига, первый и второй входы четвертого элемента ИЛИ соединены соответственно с выходами третьего и пятого элементов И, о т л и ч а ю щ. и и-с я тем, что, с целью расширения класса решаемых задач за счет дополнительной возможности вычисления корня квадратного из суммы квадратов двух чисел, в него введены третий регистр сдвига, сумматор-вычитатель, второй триггер, четвертый элемент задержки, восьмой элемент И, элемент НЕ, причем выход третьего регистра сдвига соединен с первым входом суммато- ра-вычитателя, второй вход которого соединен с выходом четвертого элемента ИЛИ, выход результата сумматора- вычитателя подключен к информационному входу третьего регистра сдвига, установочньй вход, вход синхронизации и управляющий вход которого соединены с входом логического нуля квадратора, первым и ВТОРЫМ выходами

(У

5

0

5

0

5

блока управления соответственно, информационный вход первого триггера соединен с выходом, шестого элемента И, первьй вход которого соединен с выходом четвертого элемента задержки, вход которого соединен непосредственно с четвертым выходом блока управления и через элемент НЕ - с первым входом седьмого элемента И, второй вход и выход которого подключены соответственно к прямому выходу второго тактователя импульсов и к входу режима вычитания сумматора-вы- читателя, вход режима сложения и выход переноса которого соединены с инверсным выходом второго тактователя импульсов и с первым входом восьмого элемента И, второй вход и выход которого соединены соответственно с четвертым выходом блока управления и входом сброса второго триггера, пятый выход блока управления соединен с ин- формационны.м входом второго триггера, прямой выход которого соединен с первым входом пятого и вторым входом шестого элементов И, второй и третий входы пятого элемента и подключенык инверсному выходу первого тактователя импульсов и выходу второго элемента ИЛИ, второй вход третьего элемента И соединен с прямым выходом второго тактователя импульсов, выход коммутатора соединен с вторым входом ВТО- рого элемента И.

фиеЛ

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1985 |

|

SU1258826A2 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления полинома второй степени | 1982 |

|

SU1026140A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

Изобретение относится к вычислительной технике и предназначено для формирования суммы квадратов двух величин и извлечения из нее квадратного корня. Цель изобретения - расширение класса решаемых задач за счет дополнительной возможности вычисления квадратного корня из суммы квадратов двух чисел. Это достигается тем, что в квадратор, содержащий два регистра сдвига, сумматор, коммутатор, семь элементов И, четыре элемента ИЛИ, три элемента задержки, два тактователя импульсов, триггер, два формирвателя импульсов и блок управления, ввелены третий регистр сдвига, сумматор-вычитатель, второй триггер, четвертый элемент задержки, элемент НЕ и восьмой элемент И. Изобретение может найти применение для построения цифровых систем управления, цифровых дифференциальных анализаторов и специализированных вычислительных устройств. 2 ил.

.2

| Квадратор | 1983 |

|

SU1180885A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

Авторы

Даты

1989-08-15—Публикация

1987-05-26—Подача