N5

О

tc

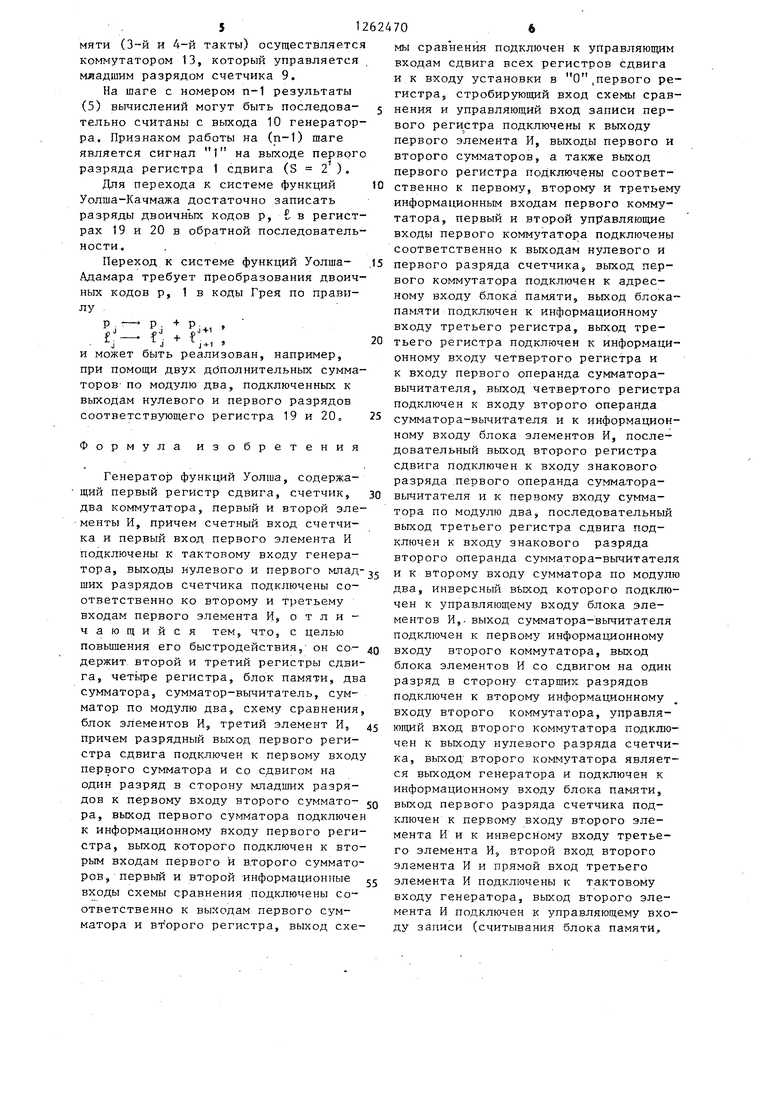

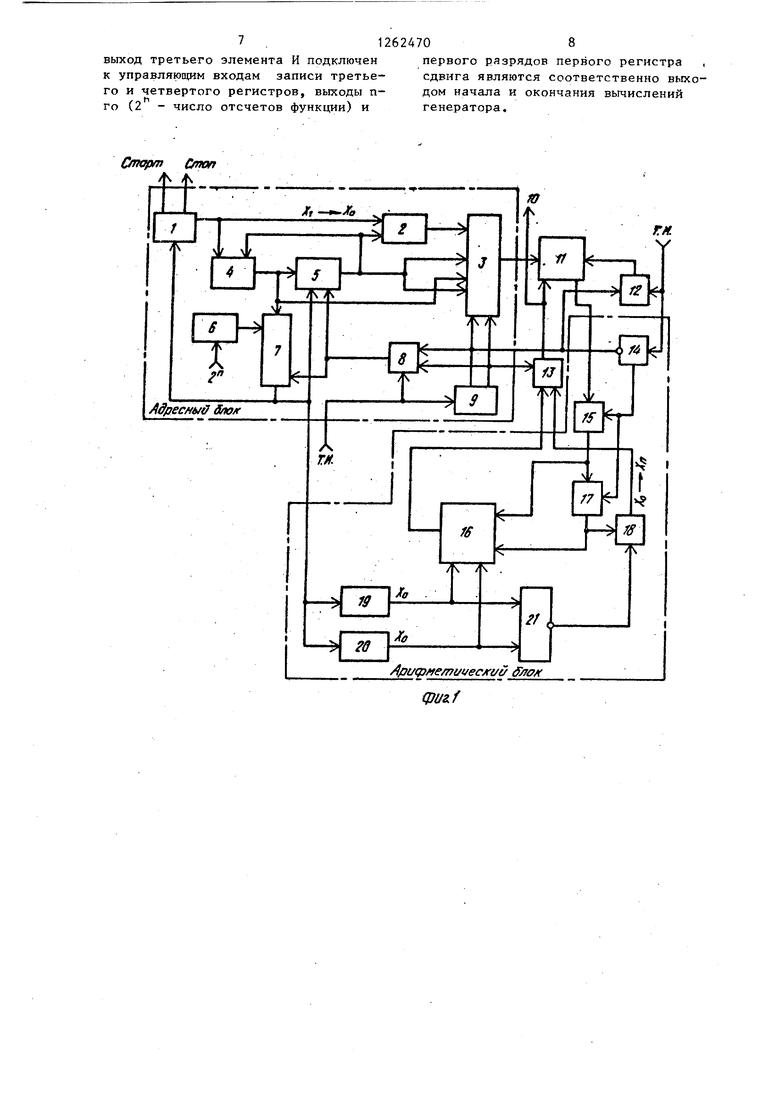

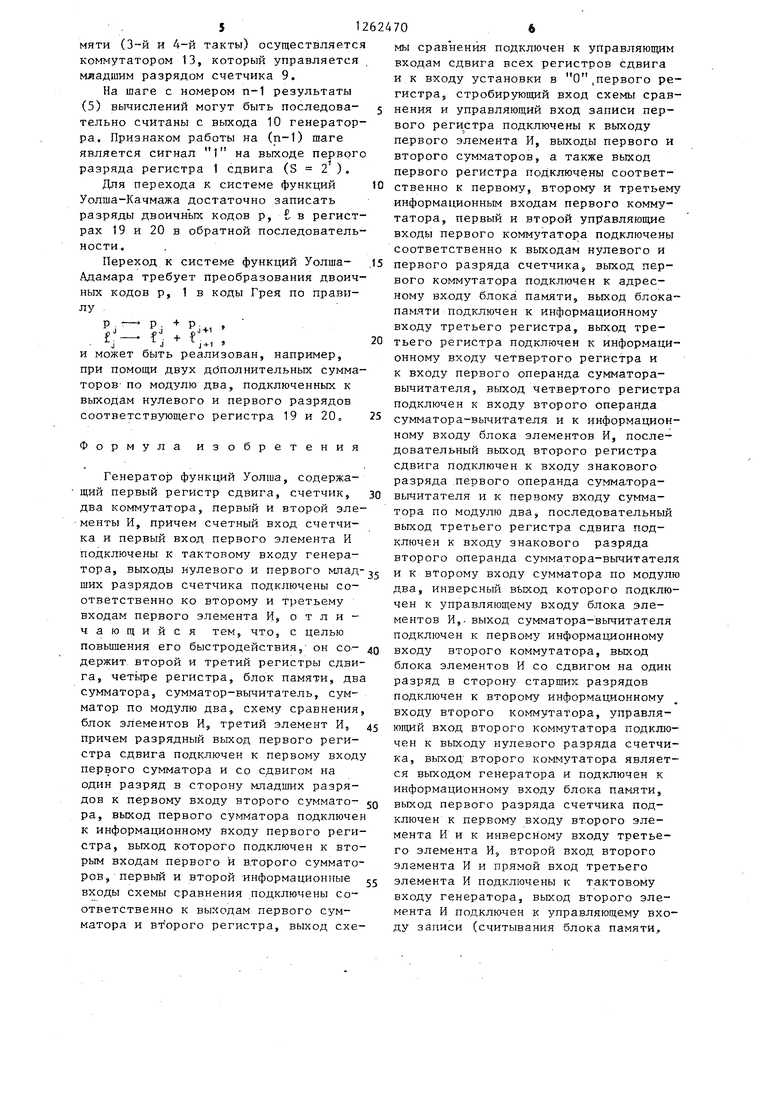

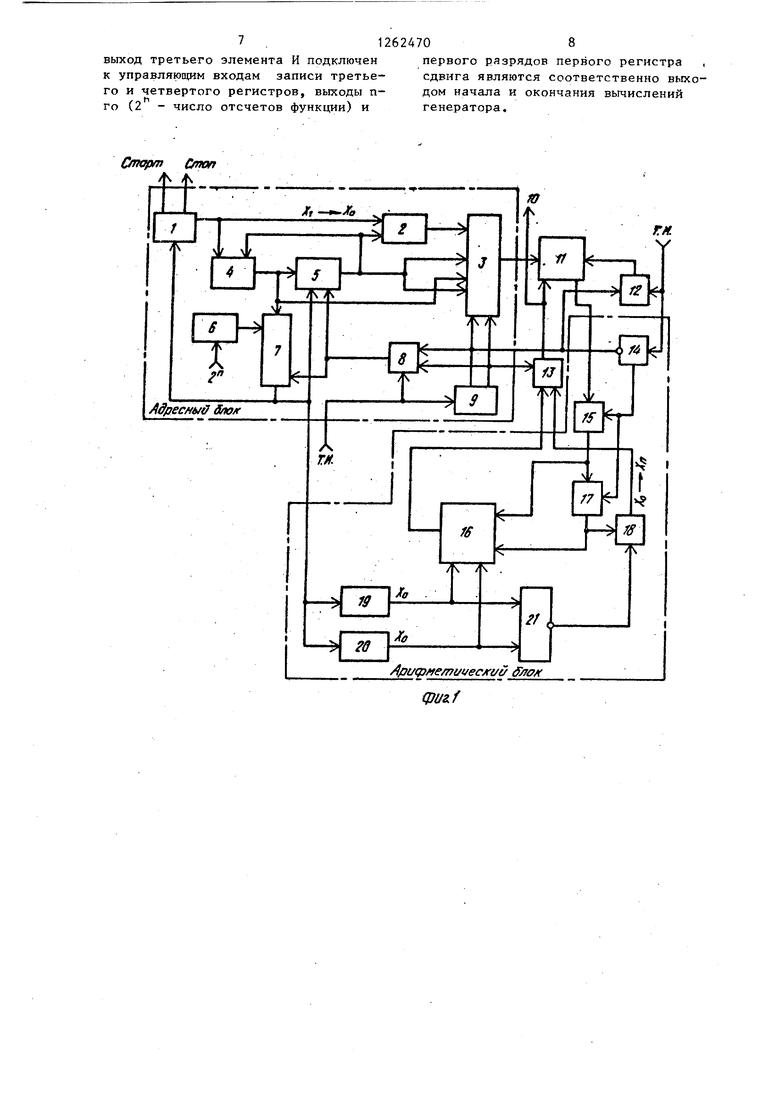

4 -J Изобретение относится к автоматике и вычислительной технике и может быть использозано в аппроксимирующих устройствах кусочно-линейного типа, для спектрального анализа случайных процессов, в устройствах сжатия информации. Целью изобретения является повышение быстродействия генератора. На фиг.1 представлена функциональная схема генератора функций Уолша, на фиг.2 - граф алгоритма вычислений фукций К (2, 7, х). Генератор функций Уолша содержит регистр 1 сдвига, сумматор 2, коммутатор 3, сумматор 4, регистр 5, регистр 6 сдвига, схему 7 сравнения, элемент И 8, двухразрядный счетчик 9, выходную шину 10, блок 11 памяти, элемент И 12, коммутатор 13, элемент И 14, регистр 15,.сумматор-вычитатель 16, регистр 17, блок 18 элементов И, регистры 19 и 20 сдвига, сумматор. 21 по модулю два. Группа блоков 1-9 образует адресную часть схемы генератора, группа блоков 14-21 - арифметическую часть. Система обобщенных интегральных .функций Уолша определяется следующим образом К(р, I, t) J wa{(p, х).. wafCe, X + t) dx. где waf(r, х) - функция Уолша с ном ром г. В зависимости от упорядочения си темы функций Уолша возможны различн способы упорядочения обобщенных интегральных функций: по Адамару, по Пэли и по Качмажу. При переходе из одной системы в другую номера pj€ п ры функций Уолша, используемых в вы ражении (1), изменяются. В системе Уолша-Пэли значения К(р, f, 1дх/Т), i 0; N дискретной обобщенной интегральной . функции Уолша К(р, t, х), где N 2 число отсчетов за период Т, могут быть получены в результате п шагов преобразования массива чисел i 0; N, j 0; n-1 при начальных условиях К. 1, К. 0 0. Преобразования на j-м шаге описываются рекурентными соотношениями tj, р - значения j-ro разряда в двоичных h- разрядных кодах t, Р (нумерация со стороны младших разрядов). После вьтолнения шага с номером п-1 получаем к , К(р f i-uX/T). В качестве примера рассмотрим вычисления при ,, 7. Для наглядности на фиг.2-показан граф вычислений функции К(2, 7, х), .стрелками отмечены операнды выражений (3) и (4) на каждом шаге преобразований:1-й шаг (j 0): {к. (100000000), S/2 4, R 0; о, S .to 1. Р 9R+) шаг (j (к, L (0000-10000), R 0; 1, S 4, S/2 2, f, 1, Р 1, .,R + 2 R a) (1) t.R 2К„; шаг (j 2): {K.,} (0010-20100), R 0; 3, S 2, S/2 1, 1, p 0. J) (1) 2R + 7. г( Таким образом, функция К (2, 7, х представляется отсчетами {K(2,7,.)} (О,/,0,-3,0,3, О,-1,0)/. Устройство работает следующим образом,, Массив чисел К хранится в блоке 11 памяти по адресам i. Перед началом вычислений содержимое блока 11 памяти определяется .вьфажением (2), Цикл обращений к блоку 11 памяти для чтения и записи операндов при однократном . выполнении операций (3) и (4) (при фиксированном значении R, S) регламентируется 2-разрядным счетчиком 9 и состоит из четырех тактов. Окончание каждого цикла соответствует состоянию 11 счетчика 9 и индицируется выходным сигналом элемента И 8, стробируемым тактовым импульсом. Значение S хранится в регистре 1 сдвига Пере началом вычислений в регистр 1 заносится 2 , что соответствует значению S при j 0. Сигнал 1 на выходе п-го разряда регистра 1 сдвига указывает на начало работы генератора. В регистре 5 формируется значение RS, а на комбинационном сумматоре Д - сумма RS+S содержимого регистров 1 и 5. Регистр 5 перед началом вычислений обнуляется, что соответствует начальному условию R 0. Совместно с комбинационным сумматором 4 регистр 5 функционирует как накапливающий сумматор с входом операнда S от регистра 1 сдвига. Схемой 7 сравнения вьфабатывается сигнал окончания шага преобразований дпя перехода от j к j+1 по условию RS+S 2 (адрес достигает наибольшего значения), Значение 2 постоянно хранится в регистре 6. Появление сигнала на выходе схемы 7 сравнения синрсронизируется выходным импульсом элемента И 8 и обуславливает сдвиг в сторону младших разрядов в регистре 1 сдвига (т.е. уменьшает S вдвое) и обнуление регистра 5 (R 0). На комбинационном сумматоре 2 формируется сумма RS+S/2, причем слагаемое S/2 получается благодаря подключению выхода регистра 1 сдвига к входу сумматора 2 со сдвигом в сторону младших разрядов. При выполнении операций (3) и (4) операнды К , RS+S извлеч; нные из блока 11 памяти, хранятся в регистрах 17 и 15 соответственно. На последовательных выходах регистров 19 и 20 сдвига, в которые перед началом вычислений заносятся значения р, {, присутствуют сдвинутые разряды р. , € . Сдвиги в регистрах 19 и 20 синхронизируютсЪ сигналами окончания выполнения шагов от с-хемы 7 сравнения. Результат операции (3) формгфуется на сумматоре 16, причем знаки (Cj, р ) слагаемых задаются с его управляющих входов. Результат операции (4) формируется на выходе блока 18 элементов И по управляющему признаку j Р , вьфабатываемому сумматором 21 по модулю два. При этом умножение на два обеспечивается благодаря подключению выхода блока 18 элементов И к входу коммутатора 13 со сдвигом в сторону старших разрядов. Четырехтактный цикл выполнения операций (3) и (4) имеет структуру, приведенную в таблице. Источниками адресов являются регистр 5 и сумматоры 2 и 4, подключаемые к адресному входу блока 11 памяти через коммутатор 3 в зависимости от состояния счетчика 9. В 1-ми 2-м тактах (О в старшем разряде счетчика 9) тактовые импульсы проходят через элемент И 14 на управляющие входы регистров 15 и 17, разрешая прием операндов. При этом операнд Крд проходит в регистр 17 (2-й такт1 через регистр 15 (1-й такт). В режиме Запись (1 в старшем разряде счетчика 9 - 3-й и 4-й такты) блок 11 памяти управляется тактовыми импуль1 ями, проходящими через элемент И 12. Отбор результатов операций (3) и (4) с выходов сумматора 16 и блока 18 лементов И для записи в блок 11 памяти (3-й и А-й такты) осуществляется коммутатором 13, который управляется младшим разрядом счетчика 9.

На шаге с номером п-1 результаты (5) вычислений могут быть последовательно считаны с выхода 10 генераторра. Признаком работы на (п-1) шаге является сигнал 1 на выходе первого разряда регистра 1 сдвига (),

Для перехода к системе функций Уолша-Качмажа достаточно записать разряды двоичных кодов р, в регистрах 19 и 20 в обратной последовательности.

Переход к системе функций УолшаАдамара требует преобразования двоичных кодов р, 1 в коды Грея по правилу

РО PJ ;: о

. ,- j + ч,

и может быть реализован, например,

при помощи двух дйполнительных сумматоров- по модулю два, подключенных к выходам нулевого и первого разрядов соответствующего регистра 19 и 20

Формула изобретения

Генератор функций Уолша, содержащий первый регистр сдвига, счетчик, два коммутатора, первый и второй элементы И, причем счетный вход счетчика и первый вход первого элемента И подключены к тактовому входу генератора, выходы нулевого и первого младших разрядов счетчика подключены соответственно ко второму и третьему входам первого элемента И, отличающийся тем, что, с целью повышения его быстродействия, он содержит, второй и третий регистры сдвига, четьфе регистра, блок памяти, два сумматора, сумматор-вычитатель, сумматор по модулю два, схему сравнения блок элементов И, третий элемент И, причем разрядный выход первого регистра сдвига подключен к первому входу первого сумматора и со сдвигом на один разряд в сторону младших разрядов к первому входу второго сумматоpa, выход первого сумматора подключен к информационному входу первого регистра, выход которого подключен к вторым входам первого и второго сумматоров, первый и второй информационные входы Схемы сравнения подключены соответственно к выходам первого сумматора и второго регистра, выход схемы сравнения подключен к управляющим входам сдвига всех регистров сдвига и к входу установки в О,первого регистра, стробируюш 1й вход схемы сравнения и управляющий вход записи первого регистра подключены к выходу первого элемента И, выходы первого и второго сумматоров, а также выход первого регистра подключены соответственно к первому, второму и третьему информационным входам первого коммутатора, первый и второй управляющие входы первого коммутатора подключены соответственно к выходам нулевого и первого разряда счетчика, выход первого коммутатора подключен к адресному входу блока памяти, выход блокапамяти подключен к информационному входу третьего регистра, выход третьего регистра подключен к информационному входу четвертого регистра и к входу первого операнда сумматоравычитателя, выход четвертого регистра подключен к входу второго операнда сумматора-вычитателя и к информационному входу блока элементов И, последовательный выход второго регистра сдвига подключен к входу знакового разряда .первого операнда сумматоравьгчитателя и к первому входу сумматора по модулю два, последовательный выход третьего регистра сдвига подключен к входу знакового разряда второго операнда сумматора-вычитателя и к второму входу сумматора по модулю два, инверсный которого подключен к управляющему входу блока элементов И,, выход сумматора-вычитателя подключен к первому информационному входу второго коммутатора, выход блока элементов И со сдвигом на один разряд в сторону старшине разрядов подключен к второму информационному входу второго коммутатора, управляющий вход второго коммутатора подключен к выходу нулевого разряда счетчика, вьгхоД второго коммутатора является выходом генератора и подключен к информационному входу блока памяти, выход первого разряда счетчика подключен к первому входу второго элемента И и к инверсному входу третьего элемента И, второй вход второго элемента И и прямой вход третьего элемента И подключены к тактовому входу генерато.ра, выход второго элемента И подключен к управляющему входу записи (считывания блока памяти.

7 .12624708

выход третьего элемента И подключен первого разрядов первого регистра к управляющим входам записи третье- сдвига являются соответственно выхого и четвертого регистров, выходы п- дом начала и окончания вычислений го (2 - число отсчетов функции) и генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Генератор функций Уолша | 1985 |

|

SU1335967A1 |

| Устройство для вычисления спектра уолша функций синуса и косинуса | 1979 |

|

SU864291A1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Генератор квазиортогональных сигналов | 1989 |

|

SU1755270A1 |

| Устройство для реализации быстрых преобразований | 1986 |

|

SU1416981A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

| Генератор функций Уолша | 1984 |

|

SU1166134A1 |

| Устройство для вычисления преобразования Уолша (его варианты) | 1982 |

|

SU1075269A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в аппроксимирующих устройствах кусочно-линейного типа, для спектрального анализа случайных процессов,в устройствах сжатия информации. Цель изобретения - повьшение быстродействия генератора. В состав блока генератора входят три регистра сдвига, четыре регистра, блок памяти, два сумматора, сумматорвычитатель, сумматор по модулю два, два коммутатора, схе.мй сравнения, блок элементов И, три элемента И. Предлагаемая конструкция позволяет реализовать алгоритм вычислений обобщенных интегральных функций Уолша с числом шагов, существенно меньшим, Q чем в известном генераторе. 2 нл.

ГН.

V/

/}pc/(pfte/77i/vecArt/if ff/fox ЙУг/

8

0 -J o -/ 0

Ф1/Э.2

| Свайный молот | 1949 |

|

SU86427A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор функции Уолша | 1983 |

|

SU1156089A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-03-19—Подача