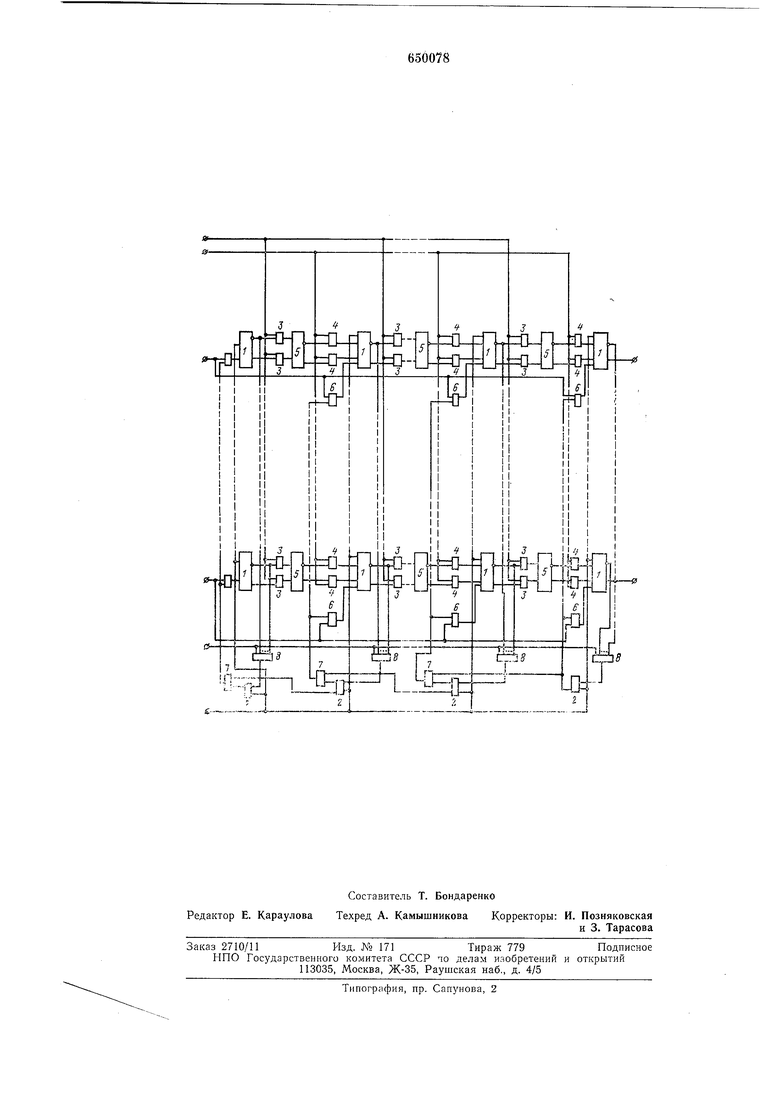

ющего регистра, в который должен liociyпить следующий запрос задержки сигнала в п группах элементов И, через которые последовательно проходит очередной запрос до записи его в соответствующий запоминающий регистр, а также вследствие последовательного во времени обнуления запоминающих регистров, посредством которых запрос передавался на запись в соответствующий запоминающий регистр. Кроме того, задержка при сдвиге записанных в запоминающих регистрах запросов после обнуления отработанного запроса в последнем запоминающем регистре по причине организации сдвига последовательным переписыванием запросов также накладывает ограничение на промежуток времени, после которого запрос очередного абонента может быть занесен в запоминающие регистры. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в предлагаемое устройство введены п-1 групп триггеров, п-1 групп входных элементов И, п-1 групп выходных элементов Я, причем прямые и обратные выходы триггеров каждой группы триггеров соединены с первыми входами соответствующих элементов И одноименной группы выходных элементов И. Выходы элементов И каждой группы выходных элементов И соединены с вторыми единичными и первыми пулевыми входами соответствующих разрядов последующего запоминающего рс:.-С;)а. Прямые и обратные зылсды ра р;.дов калсдого запоминающего регистра, кроме последнего, соединены с первыми входами соответствующих элементов И одноименной группы входных элементов П. Выходы элементов И каждой группы входных элементов И соединены с единичными и нулевыми входами соответствующих триггеров одноименной группы триггеров. Вторые зходы элементов И входной группы элементов И соединены с второй шиной синхронизации, третья шина синхронизации нодключена к вторым входам элементов И каждой выходной группы элементов И. Вторые нулевые входы разрядов каждого запоминающего рБгистра подключены к входной шине, первые входы элементов И каждой группы элементов И, кроме последней, соединены с выходами одноименных элементов ИЛИ нервой группы элементов ИЛИ. Вторые входы элементов ИЛИ нервой группы элементов ИЛИ соединены с единичными выходами одноименных триггеров регистрации состояния, вторые входы элементов И каладой группы элементов И соединены с одноименной шиной запроса группы шин запросов. Предлагаемое устройство для обслуживания запросов в порядке поступления изображено на чертеже. Устройство содерж1гг запоминающие реi-истры 1, триггеры 2 регистрации состояния, группу входных элементов И 3, группы выходных элементов И 4, триггеры 5, группу элементов И 6, группу элементов ИЛИ 7, 8. Устройство работает следующим образом. В исходном состоянии запоминающие регистры 1 и триггеры 2 регистрации состояния обнулены сигналом с входной шины, входные элементы И 3 открыты уровнем «1 с второй шины синхронизации, выходные элементы И 4 закрыты уровнем «О с третьей шины синхронизации, при этом состояние каждого триггера 5 совпадает с состоянием триггера соответствующего разряда предшествующего регистра. Элементы И 6 груниы элементов И каждого запоминающего регистра, кроме тех, которые относятся к последнему регнстру матрицы, закрыты уровнем «О с выхода одноименного элемента ИЛИ 7. Элементы И 6, относящиеся к последнему запоминающему регистру, открыты уровнем «1 с триггера 2 регистрации состояния, соответствующего последнему запоминающему регистру. Первый запрос по информационным шинам постунает на входы элементов И 6 каждого запоминающего регистра и записывается в последний запоминающий регистр. После поступления с первой ш-ины синхронизации разрещающего импульса, с выхода элемента ИЛИ 8 последнего заиоминающего регистра триггер 2 регистрации состоянья последнего запоминающего регистра устанавливается в состояние, при котором элементы И 6 последнего заноминающего регистра закрываются, а элемепты И 6 предшествующего запоминающего регистра открываются с выхода одноименного элемента ИЛИ 7. Следующий поступающий запрос заиисывается в предпоследний запоминающий регистр, ПОДГОТОВИВ при этом ему предшествующий регистр для заниси очередного запроса. Аналогично происходит заполнение запросами всех остальных запоминающих регистров, после чего запись запросов в запоминающие регистры прекрандается до отработкн первого ностунившего запроса. После отработки первого ностуиившего запроса происходит сдвиг информации на один заноминающий регистр, при этом запрос из предпоследнего запоминающего регистра поступает в последний запоминающий регистр для очередного обслуживания, а первый запоминающий регистр освобождается для заниси очередного запроса. Сдвиг осуществляется следующим образом. Элементы И 3 закрываются уровнем «О с второй шины синхронизации, информация, содержан1;аяся в триггерах, повторяет

информацию, содержащуюся в соответствующих раз)ядах регистров 1. Импульс уровня «О с входной шины обнуляет все заиоминающие регистры 1 и все триггеры 2 регистрации состояния, после чего импульс уровня «1 с третьей щииы синхронизациИ открывает элементы И 4, и информация с триггеров неренисывается в последующий запоминающий регистр. Импульс уровня «1 с входной Шины устанавливает Триггер регистрации состояния тех запоминающих регистров, в которых содержится запрос, в cocTOHHiie. при котором закрываются соответствующие этим регистрам элементы И 6, и открываются элементы И 6, относящиеся к предшествующему незаполненному запоминающему регистру. В это же время уровень «О с второй шины синхронизации снимается.

Сдвиг информации в запоминающих регистрах происходит по окончании обслуживания очередного запроса независимо от заполнения запросами запоминающих регистров.

Таким образом, задержка при записи в такое устройство определяется задержкой элементов одного запоминающего регистра независимо от места расположения его. Перепись запросов в каждый соседний запоминающий регистр проводится одновременно, т. е. время, за которое происходит сдвиг запросов в запоминающих регистрах, не зависит от количества запоминающих регистров.

Формула изобретения

Устройство для обслуживания запросов в порядке поступления, содержащее п запоминающих регистров, п групп элементов И, выходы элементов И каждой группы элементов И соединены с первыми единичными входами соответствующих разрядов одноименных запоминающнх регистров, две группы элементов ИЛИ, из которых первая группа содержит п-1 элементов ИЛИ, вторая группа - п элементов ИЛИ, причем первый вход каждого элемента ИЛИ второй группы элементов ИЛИ соединен с первой щиной синхронизации, инверсные выходы всех разрядов каждого запоминающего регистра соединены с соответствующими входами одноименного элемента ИЛИ второй группы элементов ИЛИ, п триггеров регистрации состояния, нулевые входы которых соединены с входной щиной, единичный вход каждого триггера регистрации состояния соединен с выходом о;1.ноименного э.чемента ИЛИ второй группы элементов НЛИ, нулевой выход каждого триггера регистрации состояния, кроме последнего, соедннен с первым входом предшествующего элемента ИЛИ первой эле.ментов ИЛИ, нулевой выход последнего триггера регистрации состояния соединен с первыми входами элементов И одноименной группы элементов И и первым входом предшествующего элемента ИЛИ первой группы элементов ИЛИ, отличающееся тем, что, с целью повышения быстродействия, в устройство введены п групп триггеров, п- групп входных

элементов И, п-1 грунн выходных элементов И, причем прямые и обратные выходы триггеров каждой группы триггеров соединены с нервы.ми входами соответствующих элементов И одноименноГ группы выходных

элементов И, выходы элементов И каждой группы выходных элементов И соединены с вторыми единичными и первыми нулевыми- входами соответствующих разрядов последующего запоминающего регистра, прямые и обратные выходы разрядов каждого запоминающего регистра, кроме последнего, соединены е первыми входами соответствующих элементов И одноименной группы входных элементов И, выходы элементов И каждой группы входных элелМентов И соединены с единичными и нулевыми входами соответствующих триггеров одноименной группы триггеров, вторые входы элементов И каждой входной группы элементов И соединены с второй шиной синхронизации, третья щина синхронизации подключена к вторым входам элементов И каледой выходной группы элементов И, вторые нулевые входы разрядов

каждого запоминающего регистра подключены к входно шине, первые входы элементов И каждой группы элементов И, кроме последней, соединены с выходамн одноименных элементов ИЛИ первой группы

элементов ИЛР1, вторые входы элементов ИЛИ первой группы элементов ИЛИ соединены с единичными выходами одноименных триггеров регистрации состояния, вторые входы элементов И каждой группы

эле.ментов 11 соединены с одноименной шиной запроса группы щпн запросов. Источники информации, принятые во внимание при эксперт)зе

1.Патент Великобритании № 1293032, кл. G 4С, 1972.

2.Патент США № 3588847, кл. G 11 С 19/00, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов в порядке поступления | 1983 |

|

SU1120330A2 |

| УСТРОЙСТВО ДЛЯ КОМПРЕССИИ ДАННЫХ | 2017 |

|

RU2672625C1 |

| УСТРОЙСТВО ДЛЯ КОМПРЕССИИ ДАННЫХ | 2019 |

|

RU2710987C1 |

| УСТРОЙСТВО ДЛЯ УПАКОВКИ ДАННЫХ | 2019 |

|

RU2701711C1 |

| Устройство для управления обменом информации | 1982 |

|

SU1081638A1 |

| Буферное запоминающее устройство с автономным контролем | 1984 |

|

SU1180983A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1580442A1 |

| Буферное запоминающее устройство | 1978 |

|

SU748509A1 |

| Управляемый распределитель | 1989 |

|

SU1684922A1 |

Авторы

Даты

1979-02-28—Публикация

1976-11-15—Подача