Изобретемте относится к измерительной технике и может быть использовано для измерения амплитуды и фазы гармоник периодических напряжений.

Цель изобретения - расширение

функциональных возможностей анализатора и повышение точности при изменении частоты анализируемого сигнала.

Кроме того, автоматическое измене ние масштаба интегратора обеспечива- ет работу анализатора с большим уровнем сигнала, что увеличивает его по- мехозаищщенность и уменьшает погрешность, возникающую в блоках, обрабатывающих сигнах, после фиаьтров низких частот.

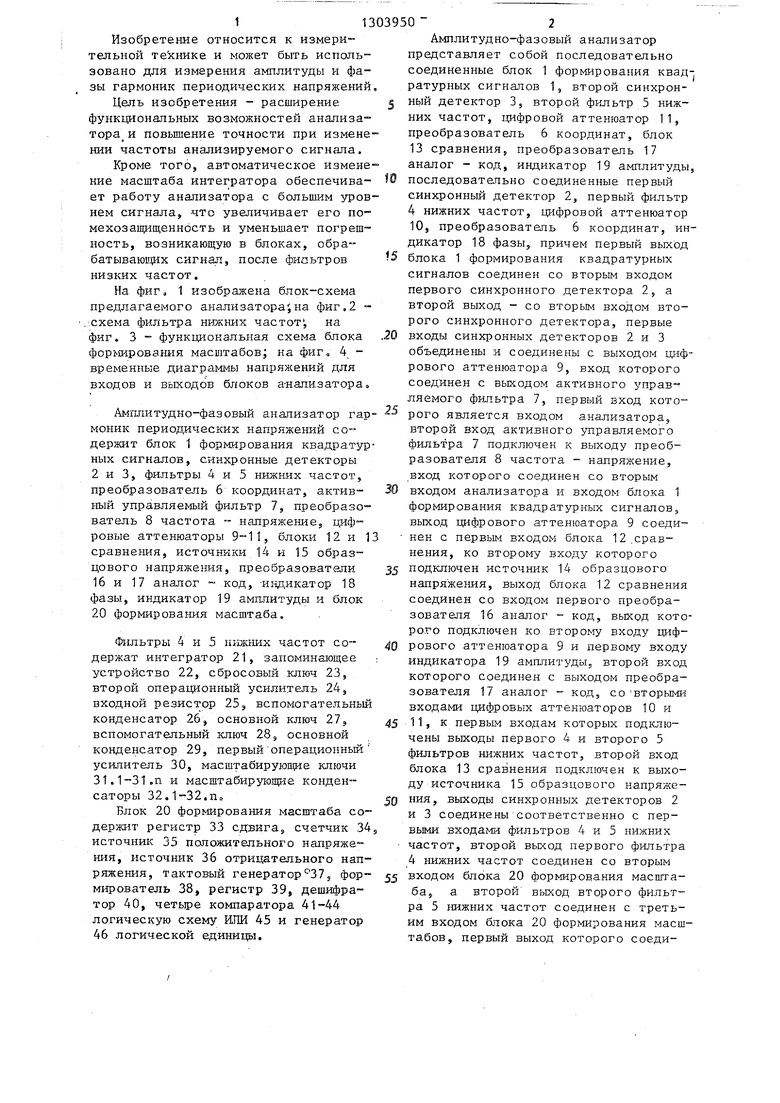

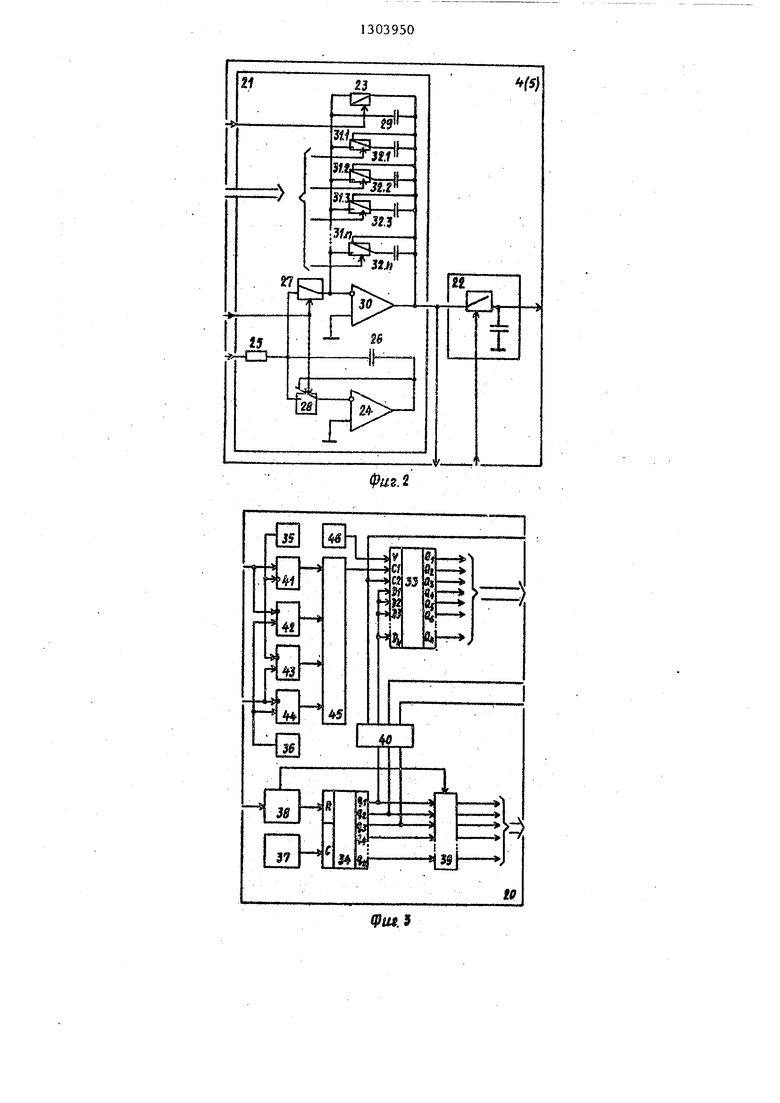

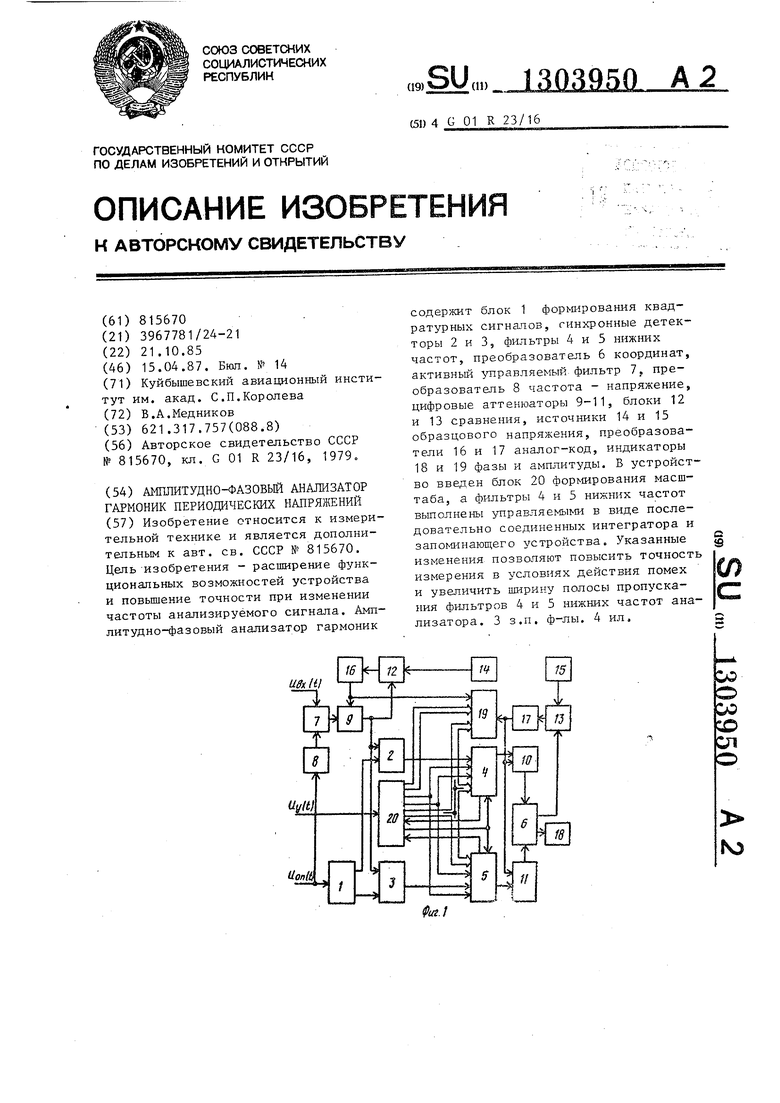

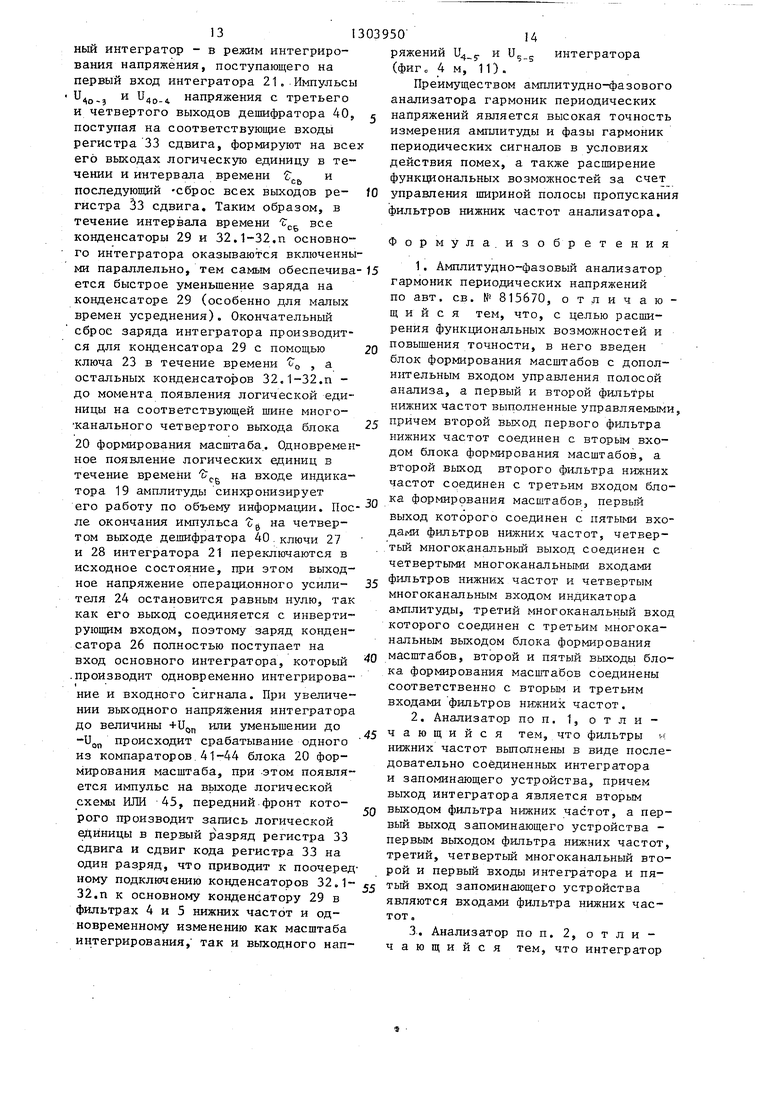

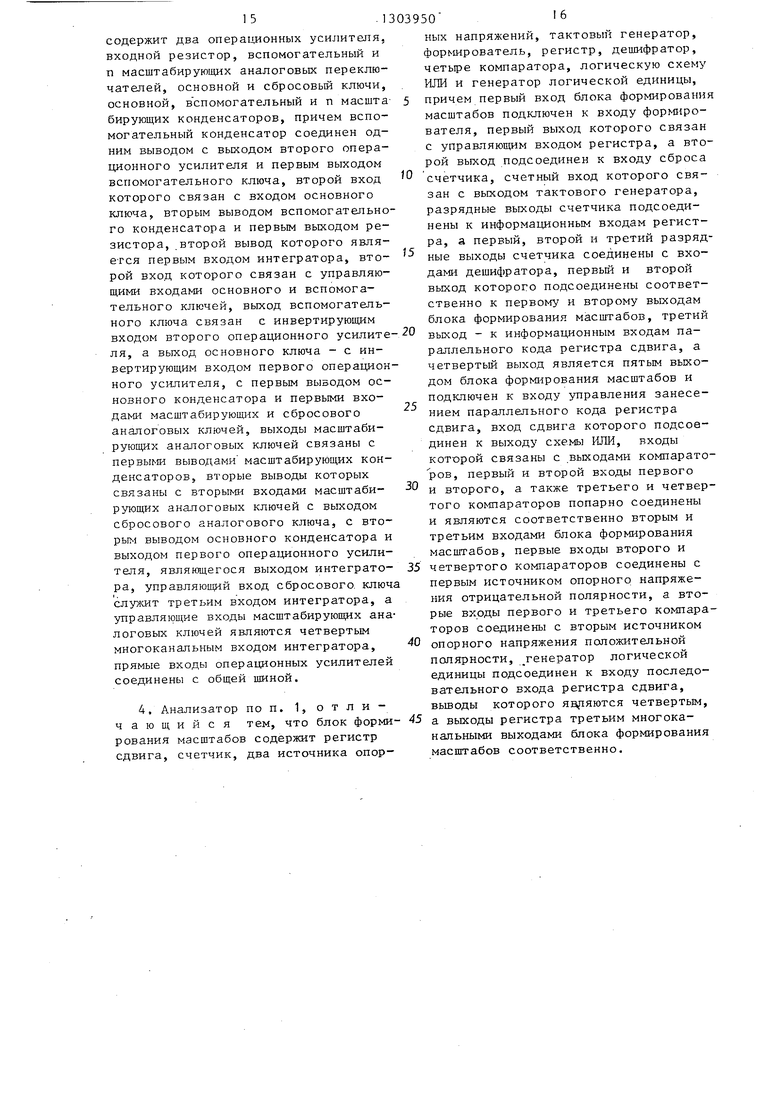

На фиг, 1 изображена блок-схема предлагаемого анализатора ,на фиг,2 - ..схема фильтра нижних частот , на фиг. 3 - функциональная схема блока формирования масштабов; на фиг, 4 - временные диаграммы напряжений для входов и выходов блоков а-налЕзатора,

Амплитудно-фазовый анализатор гар- МОНИК периодических напряжений содержит блок 1 формирования квадратурных сигналов, синхронные детекторы 2 и 3, фильтры 4 и 5 нижних частот, преобразователь 6 координат, актив- ный управляемый фильтр 7, преобразователь 8 частота - напряжение, цифровые атте.нюаторы 9-11, блоки 12 и 1 сравнения, источники 14 и 15 образцового напряжения, преобразователи 16 и 17 аналог - код, -индикатор 18 фазы, индикатор 19 амплитуды и блок 20 формирования масштаба.

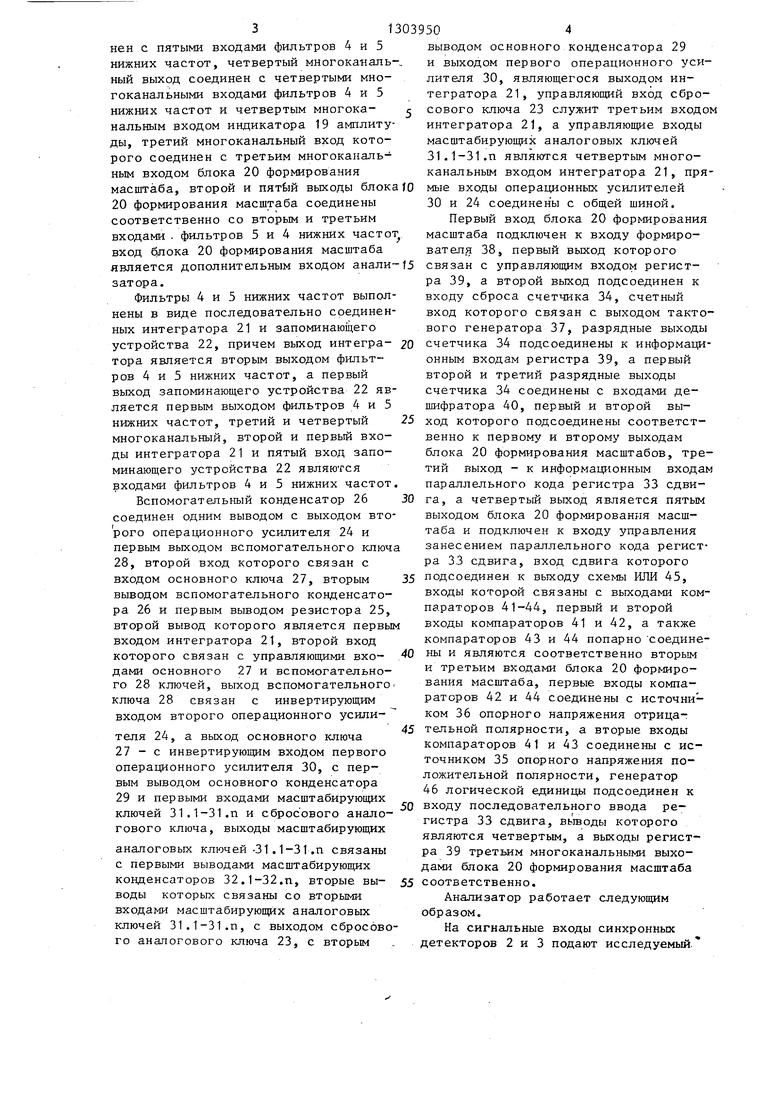

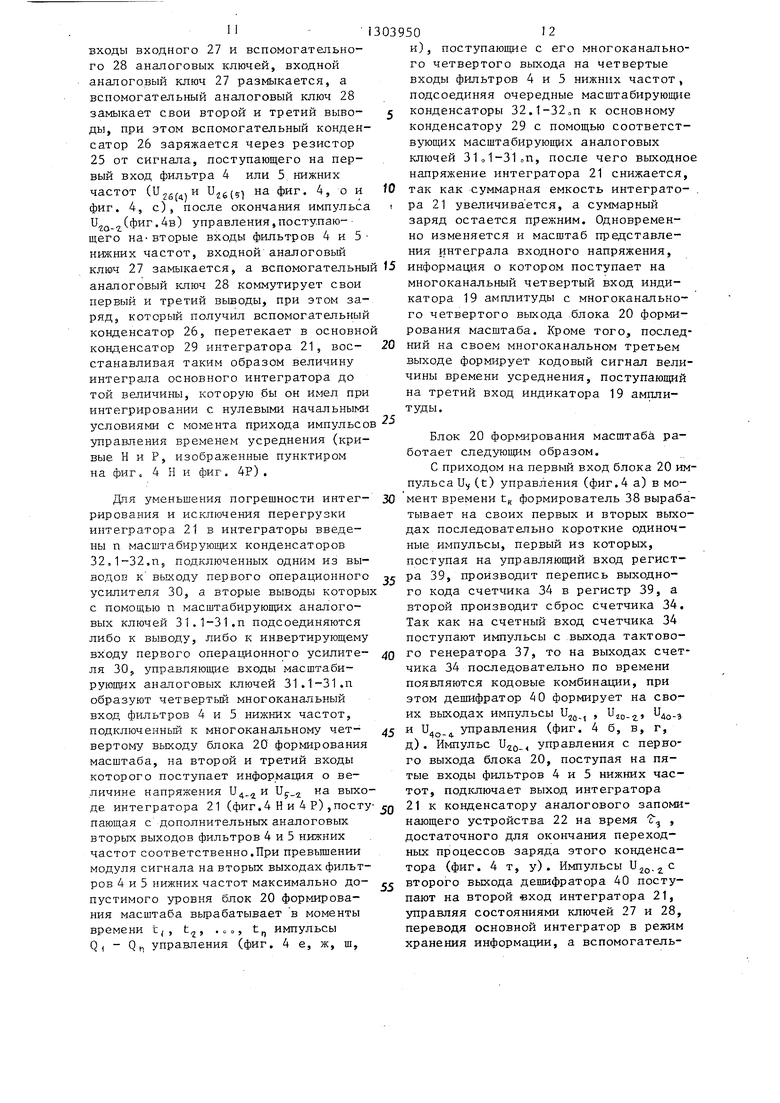

Фильтры 4 и 5 Н1гжних частот содержат интегратор 21, запоминающее устройство 22, сбросовый ключ 23, второй операционный усилитель 24, входной резист ор 25, вспомогательный конденсатор 26, основной ключ 27, вспомогательный ключ 28, основной конденсатор 29, первый операционный усилитель 30, масштабируюпре ключи 31,1-31,п и масштабирующие конденсаторы 32.1-32.По

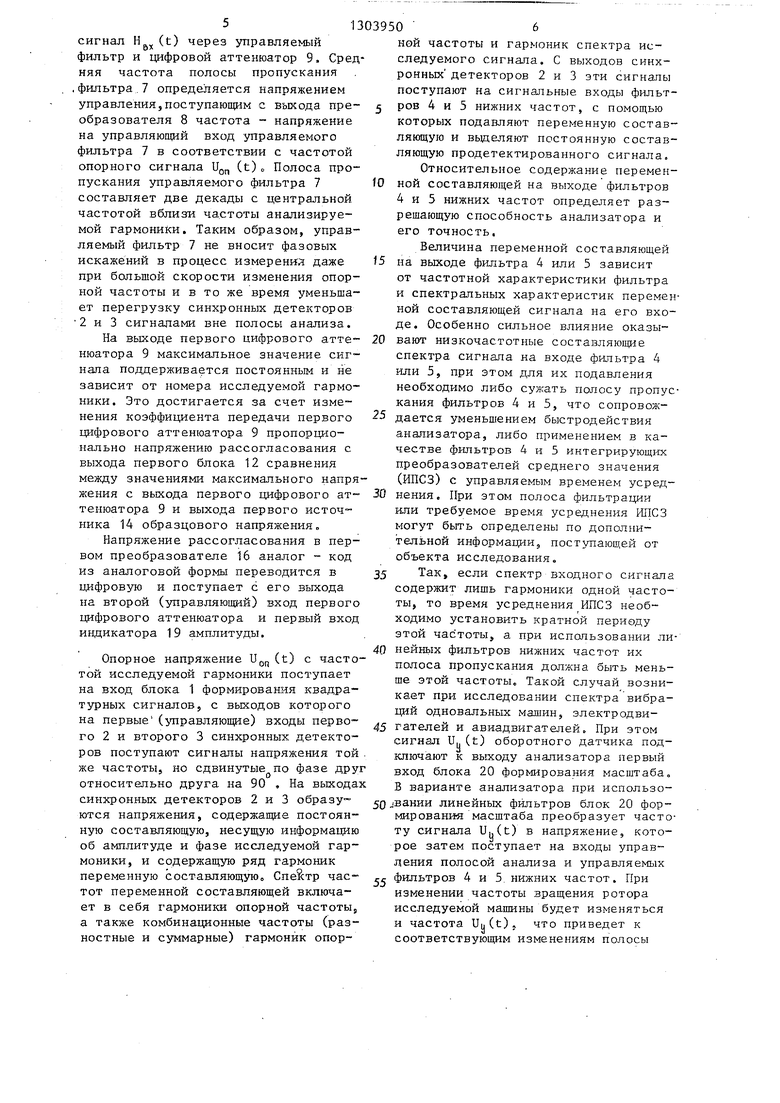

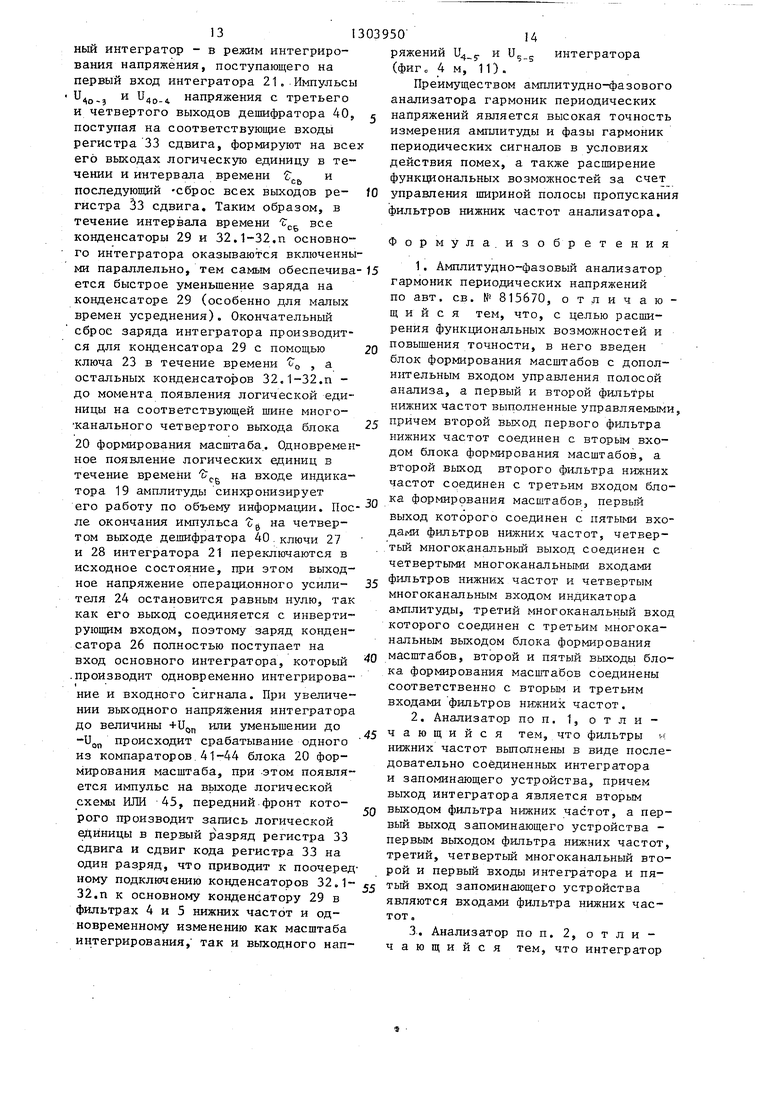

Блок 20 формирования масштаба содержит регистр 33 сдвигаJ счетчик 34 источник 35 положительного напряжения, источник 36 отрицательного напряжения, тактовый генератор - 375 фор- мирователь 38, регистр 39, дешифратор 40, четыре компаратора 41-44 логическую схему И.ПИ 45 и генератор 46 логической единицы.

0

0 5

0

5 g

5

Амплитудно-фазовый анализатор представляет собой последовательно соединенные блок 1 формирования квадратурных сигналов 1, второй синхронный детектор 3, второй фильтр 5 нижних частот, цифровой аттенюатор 11, преобразователь 6 координат, блок 13 сравнения, преобразователь 17 аналог - код, индикатор 19 амплитуды, последоватепьно соединенные первый синхронньш детектор 2, первый фильтр 4 нижних частот, цифровой аттенюатор

10,преобразователь 6 координат, индикатор 18 фазы, причем первый выход блока 1 формирования квадратурных сигналов соединен со вторым входом первого синхронного детектора 2, а второй выход - со вторым входом второго синхронного детектора, первые входы синхронных детекторов 2 и 3 объединены и соединены с выходом цифрового аттенюатора 9, вход которого соединен с выходом активного управ- ляемого фильтра 7, первый вход которого является входом анализатора, второй вход активного управляемого фильтра 7 подключен к выходу преобразователя 8 частота - напряжение, вход которого соединен со вторым входом анализатора и входом блока 1 формирования квадратурных сигналов, выход цифрового аттенюатора 9 соединен с первым входом блока 12.сравнения, ко второму входу которого подключен источник 14 образцового напряжения, выход блока 12 сравнения соединен со входом первого преобразователя 16 аналог - код, выход которого подключен ко второму входу цифрового аттенюатора 9 и первому входу индикатора 19 амплитуды, второй вход которого соединен с выходом преобразователя 17 аналог код, со-вторьпуи входами цифровых аттенюаторов 10 и

11,к первым входам которых подключены выходы первого 4 и второго 5 фильтров нижних частот, второй вход блока 13 сравнения подключен к выходу источника 15 образцового напряжения, выходы синхронных детекторов 2 и 3 соединены соответственно с первыми входам фильтров 4 и 5 нижних частот, второй выход первого фильтра 4 нижних частот соединен со вторым входом блока 20 формирования масштаба, а второй выход второго фильтра 5 нижних частот соединен с третьим входом блока 20 формирования масштабов, первый выход которого соединен с пятыми входами фильтров 4 и 5 нижних частот, четвертый многоканаль-, ный выход соединен с четвертыми многоканальными входами фильтров 4 и 5 нижних частот и четвертым многоканальным входом индикатора 19 амплитуды, третий многоканальный вход которого соединен с третьим многоканальным входом блока 20 формирования

масштаба, второй и пятЬш выходы блокаfO мые входы операционных усилителей

30 и 24 соединен ы с общей шиной.

20 формирования масштаба соединены соответственно со вторым и третьим входами . фильтров 5 и 4 нижних частот,, вход блока 20 формирования масштаба

является дополнительным входом анали 15 связан с управляющим входом регистра 39, а второй выход подсоединен к входу сброса счетчика 34, счетный вход которого связан с выходом тактового генератора 37, разрядные выходы

затора.

Фильтры 4 и 5 нижних частот выполнены в виде последовательно соединенных интегратора 21 и запоминающего устройства 22, причем выход интегра- 20 счетчика 34 подсоединены к информаци- тора является вторым выходом фильт- онным входам регистра 39, а первый ров 4 и 5 нижних частот, а первый выход запоминающего устройства 22 является первым выходом фильтров 4 и 5

25

нижних частот, третий и четвертый многоканальный, второй и первый входы интегратора 21 и пятый вход запоминающего устройства 22 являются входами фильтров 4 и 5 нижних частот

Вспомогательный конденсатор 26 соединен одним выводом с выходом второго операционного усилителя 24 и первым выходом вспомогательного ключа 28, второй вход которого связан с входом основного ключа 27, вторым выводом вспомогательного конденсатора 26 и первым выводом резистора 25, второй вывод которого является первым входом интегратора 21, второй вход которого связан с управляющими входами основного 27 и вспомогательного 28 ключей, выход вспомогательного ключа 28 связан с инвертирующим входом второго операционного усилителя 24, а выход основного ключа 21 - с инвертируюпщм вхоДом первого операционного усилителя 30, с первым выводом основного конденсатора 29 и первыми входами масштабирующих ключей 31.1-31.П и сброс ового аналогового ключа, выходы масштабирующих

аналоговых ключей -31.1-31 .п связаны с первыми выводами масштабирующих

второй и третий разрядные выходы счетчика 34 соединены с входами дешифратора 40, первый и второй выход которого подсоединены соответственно к первому и второму выходам блока 20 формирования масштабов, третий выход - к информационным входам параллельного кода регистра 33 сдви30 га, а четвертый выход является пятым выходом блока 20 формирования масштаба и подключен к входу управления занесением параллельного кода регистра 33 сдвига, вход сдвига которого

35 подсоединен к выходу схемы ИЛИ 45, входы которой связаны с выходами компараторов 41-44, первый и второй входы компараторов 41 и 42, а также компараторов 43 и 44 попарно соедине40 ны и являются соответственно вторым и третьим входами блока 20 формирования масштаба, первые входы компараторов 42 и 44 соединены с источником 36 опорного напряжения отрица45 тельной полярности, а вторые входы компараторов 41 и 43 соединены с источником 35 опорного напряжения положительной полярности, генератор 46 логической единицы подсоединен к

50 входу последовательного ввода регистра 33 сдвига, вь тоды которого являются четвертым, а выходы регистра 39 третьим многоканальными выходами блока 20 формирования масштаба

конденсаторов 32.1-32.П, вторые вы- 55 соответственно.

воды которых связаны со вторыми Анализатор работает следующим

входами масштабирующих аналоговых образом.

ключей 31.1-31.П, с выходом сбросово- На сигнальные входы синхронных

го аналогового ключа 23, с вторым . детекторов 2 и 3 подают исследуемый.

выводом основного конденсатора 29 и выходом первого операционного усилителя 30, являющегося выходом интегратора 21, управляющий вход сбросового ключа 23 служит третьим входом интегратора 21, а управляющие входы масштабирующих аналоговых ключей 31.1-31.П являются четвертым многоканальным входом интегратора 21, прямые входы операционных усилителей

30 и 24 соединен ы с общей шиной.

Первый вход блока 20 формирования масштаба подключен к входу формирователя 38, первый выход которого

ра 39, а второй выход подсоединен к входу сброса счетчика 34, счетный вход которого связан с выходом тактового генератора 37, разрядные выходы

счетчика 34 подсоединены к информаци- онным входам регистра 39, а первый

счетчика 34 подсоединены к информаци- онным входам регистра 39, а первый

второй и третий разрядные выходы счетчика 34 соединены с входами дешифратора 40, первый и второй выход которого подсоединены соответственно к первому и второму выходам блока 20 формирования масштабов, третий выход - к информационным входам параллельного кода регистра 33 сдвига, а четвертый выход является пятым выходом блока 20 формирования масштаба и подключен к входу управления занесением параллельного кода регистра 33 сдвига, вход сдвига которого

подсоединен к выходу схемы ИЛИ 45, входы которой связаны с выходами компараторов 41-44, первый и второй входы компараторов 41 и 42, а также компараторов 43 и 44 попарно соединены и являются соответственно вторым и третьим входами блока 20 формирования масштаба, первые входы компараторов 42 и 44 соединены с источником 36 опорного напряжения отрицательной полярности, а вторые входы компараторов 41 и 43 соединены с источником 35 опорного напряжения положительной полярности, генератор 46 логической единицы подсоединен к

входу последовательного ввода регистра 33 сдвига, вь тоды которого являются четвертым, а выходы региста 39 третьим многоканальными выхоами блока 20 формирования масштаба

игнал H,j (t) через управляемый ильтр и цифровой аттенюатор 9. Средняя частота полосы пропускания ильтра.7 определяется напряжением управления5поступающим с выхода преобразователя 8 частота - напряжение на управляющий вход управляемого ильтра 7 в соответствии с частотой опорного сигнала Ugj, (t) о Полоса пропускания управляемого фильтра 7 составляет две декады с центральной частотой вблизи частоты анализируемой гармоники. Таким образом, управяемый фильтр 7 не вносит фазовых искажений в процесс измеренял даже при большой скорости изменения опорной частоты и в то же время уменьшает перегрузку синхронных детекторов 2 и 3 сигналами вне полосы анализа.

На выходе первого цифрового аттенюатора 9 максимальное значение сигнала поддерживается постоянным и не зависит от номера исследуемой гармоники. Это достигается за счет изменения коэффициента передачи первого цифрового аттенюатора 9 пропорционально напряжению рассогласования с выхода первого блока 12 сравнения между значениями максимального напряжения с выхода первого цифрового аттенюатора 9 и выхода первого источника 14 образцового напряжения.

Напряжение рассогласования в первом преобразователе 16 аналог - код из аналоговой формы переводится в цифровую и поступает с его выхода на второй (управляющий) вход первого цифрового аттенюатора и первый вход индикатора 19 амплитуды.

Опорное напряжение U(t) с частотой исследуемой гармоники поступает на вход блока 1 формирования квадратурных сигналов, с выходов которого на первые (управляющие) входы первого 2 и второго 3 синхронных детекторов поступают сигналы напряжения той . же частоты, но сдвинутые по фазе друг относительно друга на 90 , На выходах синхронных детекторов 2 и 3 образуются напряжения, содержащие постоянную составляющую, несущую информацию об амплитуде и фазе исследуемой гармоники, и содержащую ряд гармоник

полоса пропускания должна быть мен ше этой частоты. Такой случай возн кает при исследовании спектра вибр ций одновальных машин, электродви45 гателей и авиадвигателей. При этом

оборотного датчика по

сигнал и (t) ключают к выходу анализатора первы вход блока 20 формирования масштаб В варианте анализатора при использ

50 вании линейных фильтров блок 20 фо мирования масштаба преобразует час ту сигнала Uj.(t) в напряжение, кот рое затем поступает на входы управ ления полосой анализа и управляемы

переменную составляющую. Спектр час- фильтров 4 и 5. нижних частот. При

тот переменной составляющей включает в себя гармоники опорной частоты, а также комбинационные частоты (разностные и суммарные) гармоник опоризменении частоты вращения ротора исследуемой машины будет изменятьс и частота Un(t). что приведет к соответствующим изменениям полосы

яод

ой . уг ах ю303950 6

ной частоты и гармоник спектра исследуемого сигнала. С выходов синхронных детекторов 2 и 3 эти сигналы поступают на сигнальные входы фильт ров 4 и 5 нижних частот, с помощью которых подавляют переменную составляющую и выделяют постоянную составляющую продетектированного сигнала. Относительное содержание перемен10 ной составляющей на выходе фильтров 4 и 5 нижних частот опредаляет разрешающую способность анализатора и его точность,

Величина переменной составляющей

15 на выходе фихсьтра 4 или 5 зависит от частотной характеристики фильтра и спектральных характеристик переменной составляющей сигнала на его входе. Особенно сильное влияние оказы20 вают низкочастотные составляющие спектра сигнала на входе фильтра 4 или 5, при этом для их подавления необходимо либо сужать полосу пропускания фильтров 4 и 5, что сопровож25 дается уменьшением быстродействия анализатора, либо применением в качестве фильтров 4 и 5 интегрирующих преобразователей среднего значения (ИНСЗ) с управляемым временем усред30 нения. При этом полоса фильтрации или требуемое время усреднения ИПСЗ могут быть определены по дополнительной информации, поступающей от объекта исследования.

J5 Так, если спектр входного сигнала содержит лишь гармоники одной частоты, то время усреднения ИПСЗ необходимо установить кратной периоду этой частоты, а при использовании ли40 нейнь х фильтров нижних частот их

полоса пропускания должна быть меньше этой частоты. Такой случай возникает при исследовании спектра вибраций одновальных машин, электродви45 гателей и авиадвигателей. При этом

оборотного датчика подсигнал и (t) ключают к выходу анализатора первый вход блока 20 формирования масштаба, В варианте анализатора при использо50 вании линейных фильтров блок 20 формирования масштаба преобразует частоту сигнала Uj.(t) в напряжение, которое затем поступает на входы управления полосой анализа и управляемых

изменении частоты вращения ротора исследуемой машины будет изменяться и частота Un(t). что приведет к соответствующим изменениям полосы

71

пропускания фильтров 4 и 5 нижних частот таким образом, что гармоника переменной составляющей на входе фильтров 4 и 5 нижних частот с самой низкой частотой, равной частоте

UyCt), окажется вне полосы пропускания фильтров 4 и 5 нижних частот и будет эффективно подавлена при любых вариациях частоты сигнала.

Блок 20 формирования масштаба формирует импульсы управления временем усреднения так, нтобы оно было кратных .периоду частоты U(.(t).

Подавление переме.нной составляющей ИПСЗ можно пояснить следующим.

Пусть исследуемый сигнал равен

UexCt) flU sinCCcot +С|.Л. (1)

с 1,

При вьщелении амплитуды U К-й гармоники формируют опорное напряже

ние UQP (t) с частотой COgn Ксо. На первом и втором выходах блока 1 формирования квадратурных сигналов сформируются напряжения

и Удsin Kut, Un Kcot,

и

(2)

поступающие на вторые входы синхрон- ных детекторов 2 и 3 соответственно.

В синхронных детекторах входной сигнал перемножается на эти сформированные сигналы, в результате чего на выходах синхронных детекторов 2 и 3 образуются сигналы, содержащие постоянную и переменную составляющие соответственно

и

Ix

mU и s in Kot

xsinCCcot + q) ) U -m-UexCt)-,

и

l

m U,

и cos Ktot к

xsinCCot срс.) Uy-m-Ug (t),

где m - постоянный коэффициент, которые можно представить в виде спектров

2x

joo.CTn

-yU,U,cosq.,+ U ZlUe

cos

(C - K) ut +

00

+ 11 COS (C + K)wt + tfj

Г(и,с-гк

и,а -b-f-u,|E:u,

sin(C -K)ut +Cfcl- -

+ K)cot +q c,

(3)

где первое слагаемое представляет собой постоянную составляющую, а второе слагаемое -.переменную составляющую .

Эти сигналы поступают на первые входы фильтров 4 и 5 нижних частот, где переменная составляющая ослабляется в линейных фильтрах частично, а в фильтрах, выполненных в виде инт тегрирующих преобразователей средних значений ослабляется полностью при

20 условии, что время Т. усреднения кратно периоду входной частоты

-|.

25 где f

Z-uТ„ nTi п 1, 2, 3

Сказанное доказывается следующим. В ИПСЗ происходит преобразование сигнала согласно вьгражекий

V1

2х

At.;

-t+T.

«9

(4)

Проведя операции выражения (4) ад сигналом (3), получаем:

IT

U, U,U,cosc,.

(C-K)Qt 4 Cf, -f (C-K)COT U r

COS

ч Sin

C t

(C+K)co

COS

0

P4.T7

+ K)cot +4,,j

и

5

b sin

UgUx

2

-in

r«pC7

Uoin

I-

C7K

y-Lk

- (r.-

(C-K)a5

s in cp + inj(C-Kbt + q, ,

00p

COT. + J sin (C+K)wt +

C-K

+ QC

с+к

«т,

.

Ui

3 (C+K)wT

a

. C+K ; к sin

Если принять

п21Г

Ту п т

ы

то

sin sinCC-lOfT О,

sin

0. 2I

Так как С и К целые.натуральные числа, то на выходе ИПСЗ переменная составляющая будет отсутствовать полностью:

и

4х

и

m

(рх

-J

и„

и„

m

1- .sinK.

йа ру

I

Таким образом, на выходе первого 4 и второго 5 фильтров нижних частот остается лишь по одной постоянной составляющей сигнала, которые представляют собой проекции вектора (амплитуды гармоники в прямоугольной системе координат), Эти сигналы соответственно через второй 10 и третий 10 цифровые аттенюаторы поступают на второй и первый входы преобразователя 6 координат, со второго (амплитудного) выхода которого напряжение Ид поступает на первый вход второго блока 13 сравнения

130395010

Амплитудно-фазовьм анализатор гармоник периодических напряжений может быть существенно упрощен, а точность его работы повышена за счет того,

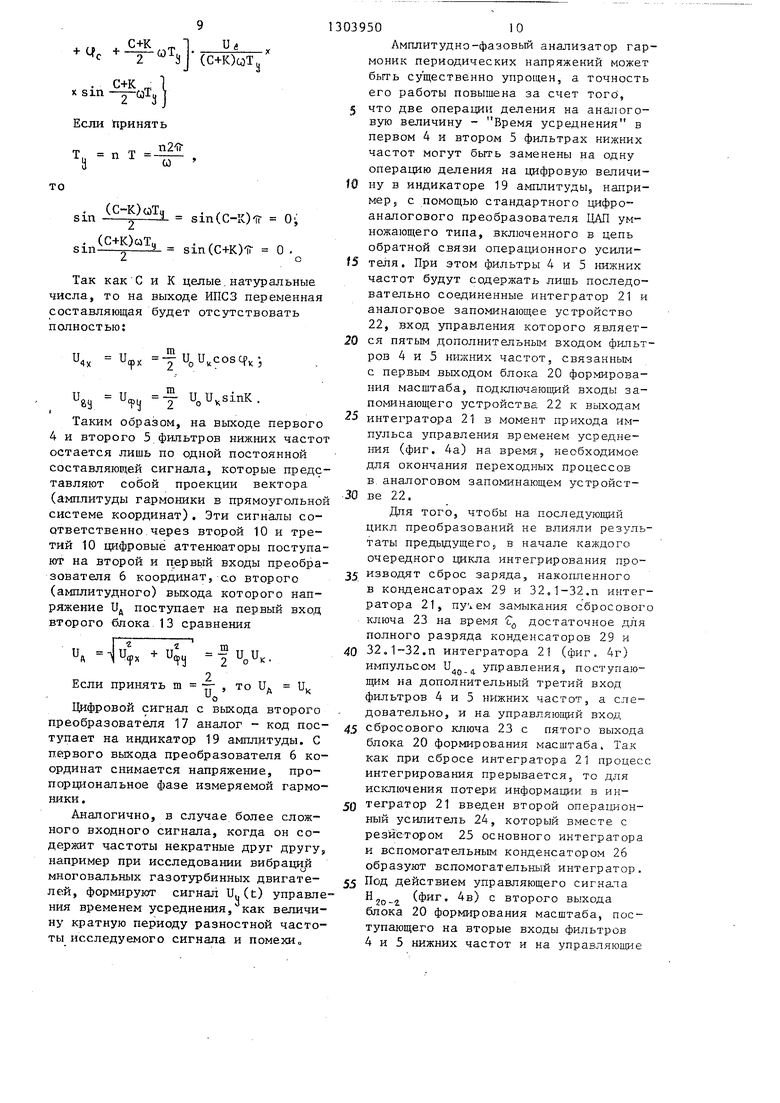

5 что две операции деления на аналоговую величину - Время усреднения в первом 4 и втором 5 фильтрах нижних частот могут быть заменены на одну операцию деления на цифровую величи10 ну в индикаторе 19 амплитуды, например, с помощью стандартного цифро- аналогового преобразователя ЦАП умножающего типа, включенного в цепь обратной связи операционного усили15 теля. При этом фильтры 4 и 5 нижних частот будут содержать лишь последовательно соединенные интегратор 21 и аналоговое запоминающее устройство 22, вход управления которого являет20 ся пятым дополнительньц-1 входом фильтров 4 и 5 нижних частот, связанным с первым выходом блока 20 формирования масштаба, подключающий входы запоминающего устройства 22 к выходам

25 интегратора 21 в момент прихода импульса управления временем усреднения (фиг, 4а) на время, необходимое для окончания переходных процессов в,аналоговом запоминающем устройст30 ве 22.

Для того, чтобы на последующий цикл преобразований не влияли результаты предыдущего,, в начале каждого очередного цикла интегрирования про35 изводят сброс заряда, накопленного в конденсаторах 29 и 32,1-32.п интегратора 21, ny i. ем замыкания сбросового ключа 23 на время Г достаточное для полного разряда конденсаторов 29 и

HU.

г

«рх

+ Ц

- 11 II

-2 .

Если принять m -г- , то U 11,,

УО Цифровой сигнал с вькода второго

преобразователя 17 аналог - код пос- тз пает на индикатор 19 амплитуды. С первого выхода преобразователя 6 координат снимается напряжение, пропорциональное фазе измеряемой гармоники .

Аналогично, в случае более сложного входного сигнала, когда он содержит частоты некратные друг другу, например при исследовании вибраций многовальных газотурбинных двигателей, формируют сигнал U(t) управления временем усреднения, как величину кратную периоду разностной частоты исследуемого сигнала и помехи

аты предыдущего,, в начале каждого очередного цикла интегрирования прозводят сброс заряда, накопленного в конденсаторах 29 и 32,1-32.п интегатора 21, ny i. ем замыкания сбросового ключа 23 на время Г достаточное для полного разряда конденсаторов 29 и

32.1-32.П интегратора 21 (фиг, 4г) импульсом и,о,4. управления, поступающим на дополнитех ьный третий вход ильтров 4 и 5 нижних частот, а следовательно, и на управляющий вход

сбросового ключа 23 с пятого выхода блока 20 формирования масштаба. Так как при сбросе интегратора 21 процесс интегрирования прерывается, то для исключения потери информации в интегратор 21 введен второй операционный усилитель 24, который вместе с резистором 25 основного интегратора и вспомогательным конденсатором 26 образуют вспомогательный интегратор.

Под действием управляющего сигнала 20-2 ( ) второго выхода блока 20 форм1-фования масштаба, поступающего на вторые входы фильтров 4 и 5 нижних частот и на управляющие

входы входного 27 и вспомогательного 28 аналоговых ключей, входной аналоговый ключ 27 размыкается, а вспомогательный аналоговый ключ 28 замыкает свои второй и третий выводы, при этом вспомогательный конденсатор 26 заряжается через резистор 25 от сигнала, поступающего на первый вход фильтра 4 или 5, нижних частот () t6( - . 4, о и фиг. 4, с), после окончания импульса (фиг.4в) управления,поступаю-- щего на-вторые входы фильтров 4 и 5 нижних частот, входной аналоговый

fO

и), поступающие с его многоканаль го четвертого выхода на четвертые входы фильтров 4 и 5 нижних частот подсоединяя очередные масштабирующ конденсаторы 32.1-32„п к основному конденсатору 29 с помощью соответс вующих масштабирующих аналоговых ключей 31 о 1-31,п, после чего выход напряжение интегратора 21 снижаетс так как суммарная емкость интеграт ра 21 увеличивается, а суммарный заряд остается прежним. Одновремен но изменяется и масштаб представле ния интеграла входного напряжения.

ключ 27 замыкается, а вспомогательный 15 информация о котором поступает на

аналоговый ключ 28 коммутирует свои первый и третий вьшоды, при этом заряд, который получил вспомогательный конденсатор 26, перетекает в основной конденсатор 29 интегратора 21, восстанавливая таким образом величину интеграла основного интегратора до той величины, которую бы он имел при интегрировании с нулевыми начальными условиями с момента прихода импульсов управления временем усреднения (кривые Н и Р, изображенные пунктиром на фиг, 4 Н и фиг. 4Р).

Для уменьшения погрешности интегрирования и исключения перегрузки интегратора 21 в интеграторы введены п масштабирующих конденсаторов 32,,П5 подключенных одним из выводов к выходу первого операционного усилителя 30, а вторые выводы которых с помощью п масштабирующих аналоговых ключей 31.1-31.п подсоединяются либо к выводу, либо к инвертирующему входу первого операционного усилителя 30, управляюш 1е входы масштабирующих аналоговых ключей 31.1-31.п образуют четвертый многоканальный вход фильтров 4 и 5 нижних частот, подключенньш к многоканальному четвертому выходу блока 20 формирования масштаба, на второй и третий входы которого поступает информация о величине напряжения U. и на выхо20

25

многоканальный четвертый вход индикатора 19 амплитуды с многоканального четвертого выхода блока 20 формирования масштаба. Кроме того, последний на своем многоканальном третьем выходе формирует кодовый сигнал величины времени усреднения, поступающий на третий вход индикатора 19 амплитуды.

Блок 20 формирования масштаба работает следуюш 1м образом.

С приходом на первый вход блока 20 импульса Uy(t) управления (фиг.4 а) в мо- 30 мент времени t формирователь 38 вырабатывает на своих первых и вторых выходах последовательно короткие одиночные импульсы, первый из которых, поступая на управляющий вход регистра 39, производит перепись выходного кода счетчика 34 в регистр 39, а второй производит сброс счетчика 34, Так как на счетный вход счетчика 34 поступают импульсы с выхода тактового генератора 37, то на выходах счетчика 34 последовательно по времени появляются кодовые комбинации, при этом дешифратор 40 формирует на сво35

40

45

их выходах импульсы ,, , ло-ъ и и. управления (фиг. 4 б, в, г.

д) . Импульс управления с парного выхода блока 20, поступая на пятые входы фильтров 4 и 5 нижних частот, подключает выход интегратора де интегратора 21 (фиг.4Ни 4Р),посту jg 21 к конденсатору аналогового запоминающего устройства 22 на время 2 , достаточного для окончания переходных процессов заряда этого конденсатора (фиг, 4 т, у) . Импульсы U.c j5 второго выхода дешифратора 40 поступают на второй вход интегратора 21, управляя состояниями ключей 27 и 28, переводя основной интегратор в режим хранения информации, а вспомогательнающая с дополнительных аналоговых вторых выходов фильтров 4 и 5 нижних частот соответственно.При превьш1ении модуля сигнала на вторых выходах фильтров 4 и 5 нижних частот максимально допустимого уровня блок 20 формирования масштаба вьфабатывает в моменты времени t, t, .„о, t импульсы Q, - Q t, управления (фиг. 4 е, ж, щ.

и), поступающие с его многоканального четвертого выхода на четвертые входы фильтров 4 и 5 нижних частот, подсоединяя очередные масштабирующие конденсаторы 32.1-32„п к основному конденсатору 29 с помощью соответствующих масштабирующих аналоговых ключей 31 о 1-31,п, после чего выходное напряжение интегратора 21 снижается, так как суммарная емкость интегратора 21 увеличивается, а суммарный заряд остается прежним. Одновременно изменяется и масштаб представления интеграла входного напряжения.

многоканальный четвертый вход индикатора 19 амплитуды с многоканального четвертого выхода блока 20 формирования масштаба. Кроме того, последний на своем многоканальном третьем выходе формирует кодовый сигнал величины времени усреднения, поступающий на третий вход индикатора 19 амплитуды.

Блок 20 формирования масштаба работает следуюш 1м образом.

С приходом на первый вход блока 20 импульса Uy(t) управления (фиг.4 а) в мо- 0 мент времени t формирователь 38 вырабатывает на своих первых и вторых выходах последовательно короткие одиночные импульсы, первый из которых, поступая на управляющий вход регистра 39, производит перепись выходного кода счетчика 34 в регистр 39, а второй производит сброс счетчика 34, Так как на счетный вход счетчика 34 поступают импульсы с выхода тактового генератора 37, то на выходах счетчика 34 последовательно по времени появляются кодовые комбинации, при этом дешифратор 40 формирует на сво5

0

45

их выходах импульсы ,, , ло-ъ и и. управления (фиг. 4 б, в, г.

нающего устройства 22 на время 2 , достаточного для окончания переходных процессов заряда этого конденсатора (фиг, 4 т, у) . Импульсы U.c второго выхода дешифратора 40 поступают на второй вход интегратора 21, управляя состояниями ключей 27 и 28, переводя основной интегратор в режим хранения информации, а вспомогатель131

ный интегратор - в режим интегрирования напряжения, поступающего на первый вход интегратора 21..Импульсы 40-4. напряжения с третьего и четвертого выходов дешифратора 40, поступая на соответствующие входы регистра 33 сдвига, формируют на все его выходах логическую единицу в течении и интервала времени Z. и

последующий -сброс всех выходов ре- гистра ЗЗ сдвига. Таким образом, в течение интервала времени fj, все конденсаторы 29 и 32.1-32,п основного интегратора оказываются включенными параллельно, тем самым обеспечива ется быстрое уменьшение заряда на конденсаторе 29 (особенно для малых времен усреднения). Окончательный сброс заряда интегратора производится для конденсатора 29 с помощью ключа 23 в течение времени о , а остальных конденсато ров 32.1-32.П - до момента появления логической единицы на соответствующей шине много- канального четвертого выхода блока 20 формирования масштаба,. Одновременное появление логических единиц в течение времени & на входе индикатора 19 амплитуды синхронизирует его работу по объему информагщи. Пос ле окончания импульса о на четвертом выходе дешифратора 40.ключи 27 и 28 интегратора 21 переключаются в исходное состояние, при этом выходное напряжение операци.онного усилителя 24 остановится равным нулю, та как его выход соединяется с инвертирующим входом, поэтому заряд конденсатора 26 полностью поступает на вход основного интегратора, который .производит одновременно интегрирование и входного сигнала. При увеличении выходного напряжения интегратор

до величи1-1ы или уменьшении до -UQJ, происходит срабатывание одного из компараторов 41-44 блока 20 формирования масштаба, при -этом появляется импульс на выходе логической схемы ИЛИ 45, передний фронт которого производит запись логической единицы в первый разряд регистра 33 сдвига и сдвиг кода регистра 33 на один разряд, что приводит к поочередному подключению конденсаторов 32.1- тьй вход запоминающего устройства 32.п к основному конденсатору 29 вявляются входами фильтра нижних час- фильтрах 4 и 5 нижних частот и од-тот„

новременному изменению как масштаба3. Анализатор поп. 2, отлиинтегрирования, так и выходного нап-чающийся тем, что интегратор

14

O 5 0

5

0

5

0

ряжений . и и, (фиг„ 4 м, 11).

Преимуществом амплитудно-фазового анализатора гармоник периодических напряжений является высокая точность измерения амплитуды и фазы гармоник периодических сигналов в условиях действия помех, а также расширение функциональных возможностей за счет управления шириной полосы пропускания фильтров нижних частот анализатора.

Формула, изо бр ет ения

1.Амплитудно-фазовый анализатор гармоник периодических напряжений

по авт. св. № 815670, отличающийся тем, что, с целью расширения функциональных возможностей и повышения точности, в него введен блок формирования масштабов с дополнительным входом управления полосой анализа, а первый и второй фильтры нижних частот выполненные управляемыми, причем второй выход первого фильтра нижних частот соединен с вторым входом блока формирования масштабов, а второй выход второго фильтра нижних частот соединен с третьим входом блока формирования масштабов, первый выход которого соединен с пятыми входами фильтров нижних частот, четвер- , тый многоканал:1ьный выход соединен с четвертыми многоканальными входами фильтров нижних частот и четвертым многоканальным входом индикатора амплитуды, третий многоканальный вход которого соединен с третьим многоканальным выходом блока формирования масштабов, второй и пятый выходы блока формирования масштабов соединены соответственно с вторым и третьим входами фильтров нижних частот.

2.Анализатор по п. 1, отличающийся тем, что фильтры и; нижних частот вьтолнены в виде последовательно соединенных интегратора

и запоминающего устройства, причем выход интегратора является вторым выходом фильтра нижних частот, а первый выход запоминающего устройства - первым выходом фильтра нижних частот, третий, четвертый многоканальный второй и первый входы интегратора и пя15

содержит два операционных усилителя, входной резистор, вспомогательный и п масштабирующих аналоговых переключателей, основной и сбросовый ключи, основной, вспомогательный и п масштабирующих конденсаторов, причем вспомогательный конденсатор соединен одним выводом с выходом второго операционного усилителя и первым выходом

которого связан с входом основного ключа, вторым выводом вспомогательного конденсатора и первым выходом резистора, второй вывод которого является первым входом интегратора, второй вход которого связан с управляющими входами основного и вспомогательного ключей, выход вспомогательного ключа связан с инвертирующим входом второго операционного усилите ля, а выход основного ключа - с инвертирующим входом первого операционного усилителя, с первым выводом основного конденсатора и первыми вхо- мacштaбиpyю щix и сбросового аналоговых ключей, выходы масштабирующих аналоговых ключей связаны с первь ми выводами масштабирующих конденсаторов, вторые выводы которых связаны с вторыми входами масштабирующих аналоговых ключей с выходом сбросового аналогового ключа, с вторым выводом основного конденсатора и выходом первого операционного усилителя, являющегося выходом интегратора, управляющий вход сбросового, ключ третьим входом интегратора, а управляющие входы масштабируюш х аналоговых ключей являются четвертым многоканальным входом интегратора, прямые входы операционных усилителей соединены с общей шиной.

4. Анализатор по п. 1, отли- ч а ю щ и и с я тем, что блок форми рования масштабов содержит регистр сдвига, счетчик, два источника опор-

1303950

16

5

5

0

5

0

5

0

ных напряжении, тактовый генератор, формирователь, регистр, дешифратор, четыре компаратора, логическую схему ИЛИ и генератор логической единицы, причем первый вход блока формирования масштабов подключен к входу формирователя, первый выход которого связан с управляющим входом регистра, а второй выход подсоединен к входу сброса счетчика, счетный вход которого связан с выходом тактового генератора, разрядные выходы счетчика подсоединены к информационным входам регистра, а первый, второй и третий разрядные выходы счетчика соединены с входами дешифратора, первый и второй выход которого подсоединены соответственно к первому и второму выходам блока формирования масштабов, третий выход - к информационным входам параллельного кода регистра сдвига, а четвертый выход является пятым выходом блока формирования масштабов и подключен к входу управления занесением параллельного кода регистра сдвига, вход сдвига которого подсоединен к выходу схемы ИЛИ, входы которой связаны с .выходами компарато- ров, первый и второй входы первого и второго, а также третьего и четвертого компараторов попарно соединены и являются соответственно вторым и третьим входами блока формирования масштабов, первые входы второго и четвертого компараторов соединены с первым источником опорного напряжения отрицательной полярности, а вторые входы первого и третьего компараторов соединены с вторым источником опорного напряжения положительной полярности, генератор логической единицы подсоединен к входу последовательного входа регистра сдвига, вьшоды которого яв яются четвертым, а выходы регистра третьим многоканальными выходами блока формирования масштабов соответственно.

щ

rW

15

.-CD-i- 25

и

Т

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1337784A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347027A1 |

| Амплитудно-фазовый анализатор гар-МОНиК | 1979 |

|

SU815669A1 |

| Амплитудно-фазовый анализатор гармоник | 1985 |

|

SU1272272A2 |

| РАДИОВЫСОТОМЕР | 2001 |

|

RU2212684C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Анализатор спектра | 1985 |

|

SU1287033A1 |

| АНАЛОГО-ЦИФРОВОЕ МНОГОПРОЦЕССОРНОЕ УСТРОЙСТВО ВЫЧИСЛЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2006 |

|

RU2333531C1 |

| Устройство для калибровки многоканальной аппаратуры | 1988 |

|

SU1583753A1 |

Изобретение относится к измерительной технике и является дополнительным к авт. св. СССР № 815670. Цель изобретения - расширение функциональных возможностей устройства и повьшение точности при изменении частоты анализируемого сигнала. Амплитудно-фазовый анализатор гармоник содержит блок 1 формирования квадратурных сигналов, синхронные детекторы 2 и 3, фильтры 4 и 5 нижних частот, преобразователь 6 координат, активный гправляемый фильтр 7j преобразователь 8 частота - напряжение, цифровые аттенюаторы 9-11, блоки 12 и 13 сравнения, источники 14 и 15 образцового напряжения, преобразователи 16 и 17 аналог-код, индикаторы 18 и 19 фазы и амплитуды. В устройство введ.ен блок 20 формирования масштаба, а фильтры 4 и 5 нижних частот выполнены управляемыми в виде последовательно соединенных интегратора и запоминающего устройства. Указанные изменения позволяют повысить точность измерения в условиях действия помех и увеличить ширину полосы пропускания фильтров 4 и 5 нижних частот анализатора., 3 з.п. ф-лы. 4 ил. с 9 :0 :х) х д f45

Редактор A.Pевин

Составитель В.Величкин

ТехреД; Л.Сердюкова Корректор Л.Патай

1305/46

Тираж 731 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д 4/5

Производственно-полиграфическое п редприятие, г. Ужгород, ул. Проектная, 4

.4

| Амплитудно-фазовый анализаторгАРМОНиК пЕРиОдичЕСКиХ НАпРяжЕНий | 1979 |

|

SU815670A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-04-15—Публикация

1985-10-21—Подача