Изобретение относится к средствам специализированной вычислительной техники и может найти применение в спектральном анализе сигналов в реальном масштабе времени.

Известны устройства [1] и [2], позволяющие выполнять дискретное преобразование Фурье. К недостаткам устройств относится отсутствие результата вычисления амплитуды гармоники сигнала в аналоговой форме и последовательное вычисление действительной и мнимой частей гармоники.

Наиболее близким по технической сущности является устройство для выполнения дискретного преобразования Фурье [3]. При поступлении сигнала запуска устройство выбирает входное значение и последовательно вычисляет действительную и мнимую части и амплитуду k-ой гармоники спектра Фурье.

Прототип имеет следующие недостатки: устройство выполняет операции вычисления действительной и мнимой частей и модуля результата последовательно во времени. Т.к. максимальная допустимая частота входного информационного сигнала в данной задаче обратно пропорциональна времени вычисления, то уменьшение времени обработки приведет к увеличению максимальной допустимой частоты входного анализируемого сигнала.

Цель изобретения - повышение быстродействия прототипа и расширения спектра входного анализируемого сигнала в 2 раза за счет распараллеливания вычисления действительной и мнимой частей и введения конвейеризации.

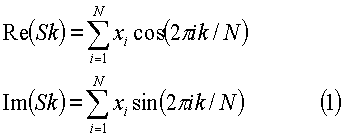

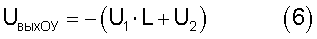

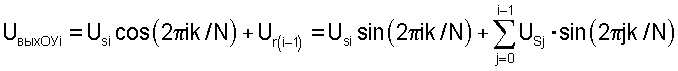

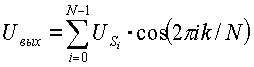

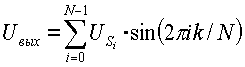

Устройство предназначено для определения действительной и мнимой составляющих гармоник разложения измеряемой величины в дискретный ряд Фурье в соответствии с выражениями

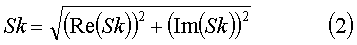

Кроме того, устройство обеспечивает вычисление как синусной и косинусной составляющих гармоник разложения сигнала в ряд Фурье в соответствии с (1), так и абсолютной амплитуда гармоники сигнала

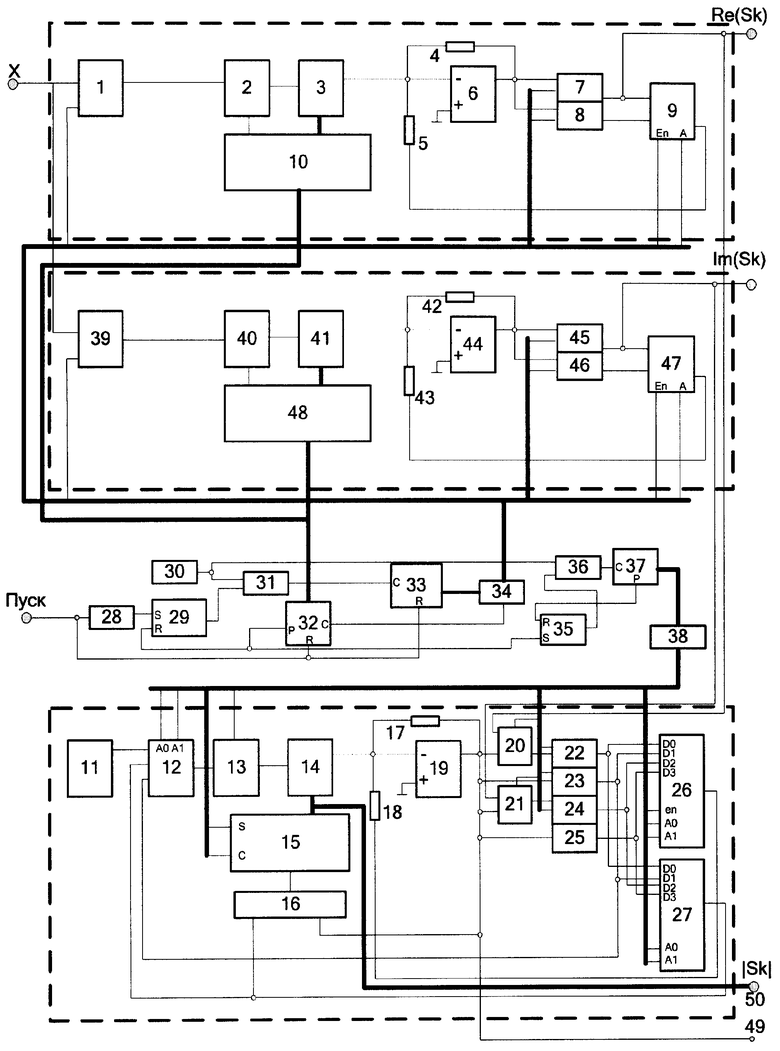

На чертеже представлена структурная схема устройства.

Устройство содержит блок 1 выборки, блок управляемой инверсии 2, масштабирующий потенциометр 3, два масштабирующих резистора 4 и 5, операционный усилитель 6, два блока 7 и 8 выборки, коммутатор 9, блок постоянной памяти 10, объединенные в первый процессор первого типа, источник опорного напряжения 11, коммутатор 12, блок управляемой инверсии 13, масштабирующий потенциометр 14, регистр последовательных приближений 15, компаратор 16, два масштабирующих резистора 17 и 18, операционный усилитель 19, два коммутатора 20 и 21, четыре блока выборки 22, 23, 24, 25, два коммутатора 26 и 27, объединенные в процессор второго вида, блок задержки 28, регистр 29, генератор тактовых импульсов 30, элемент И 31, первый и второй счетчики 32 и 33, второй блок постоянной памяти 34, второй регистр, 35, второй элемент И 36, третий счетчик 37, третий блок постоянной памяти 38, объединенные в блок управления, блок 39 выборки, блок управляемой инверсии 40, масштабирующий потенциометр 41, два масштабирующих резистора 42 и 43, операционный усилитель 44, два блока 45 и 46 выборки, коммутатор 47, блок постоянной памяти 48, объединенные во второй процессор первого типа.

Устройство работает следующим образом.

По внешнему сигналу запуска, поступающему на вход Пуск, устройство переключается в исходное состояние, в котором сбрасываются (обнуляются) по входам R счетчики 32 и 33. Далее сигнал запуска с задержкой в элементе 28 переключает (взводит) регистр 29, который деблокирует элемент И 31. Тактовые импульсы генератора 30 начинают поступать на счетный вход С счетчика 33. Выходы счетчика 33 подключены к адресным входам блока постоянной памяти 34, выходы которого подключены к управляющим входам блоков 1, 7, 8, 9, 39, 45, 46, 47 и тактовому входу С счетчика 32. Таким образом, по мере счета счетчика 33 на выходах узла постоянной памяти 34 возникают сигналы, управляющие работой первого и второго процессоров первого вида, вычисляющих действительную и мнимую части k-ой гармоники спектра Фурье. По завершению вычисления действительной и мнимой частей от N выборок на выходе Р счетчика 32 выставляется сигнал, устанавливающий в "1" регистр 35 по входу S, элемент И 36 пропускает тактовые импульсы на счетчик 37, выход которого поступает на блок 38 постоянной памяти, выдающий управляющие сигналы на процессор второго вида. По управляющим сигналам блока 38 постоянной памяти значения результатов вычисления первого и второго процессоров первого вида сохраняются в блоках 22 и 24 выборки процессора второго вида и происходит вычисление амплитуды k-ой гармоники спектра Фурье. С момента сохранения результатов вычисления в блоках выборки процессора второго вида устройство ждет появления сигнала Пуска для обработки следующих N выборок входного сигнала в процессорах первого вида.

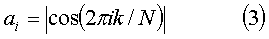

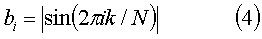

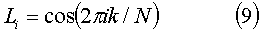

Блоки постоянной памяти процессоров первого вида 10 и 48 хранят цифровые двоичные коды, соответствующие модулям коэффициентов Фурье (с учетом знака):

для первого и второго процессоров соответственно,

где k - номер измеряемой гармоники;

i - номер текущего цикла вычислений;

N - общее число выборок.

Первый процессор первого вида работает следующим образом.

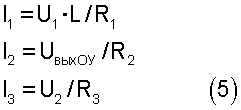

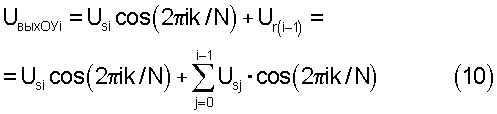

Вход операционного усилителя 6 является узлом суммирования трех токов: I1 - с выхода масштабирующего потенциометра 3, I2 - с выхода усилителя 6 и I3 - с выхода коммутатора 9.

При этом

где U1 - напряжение на выходе блока управляемой инверсии 2;

U2 - напряжение на выходе коммутатора 9;

UвыхОУ - выходное напряжение операционного усилителя 6;

R1 - сопротивление масштабирующего потенциометра 3;

R2 - сопротивление масштабирующего резистора 4;

R3 - сопротивление масштабирующего резистора 5;

L - величина кода, поступающего на управляющие входы

масштабирующего потенциометра 3.

Учитывая, что входной ток современных операционных усилителей пренебрежимо мал, по первому закону Кирхгофа

I1+I2+I3=0.

Тогда, принимая R1=R2=R3, из (5) получим

Выражение (6) может служить основой для выполнения базовой операции дискретного преобразования Фурье.

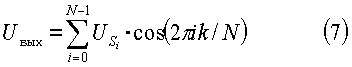

Пусть во времени выбираются значения напряжения входного информационного сигнала Us0, Us1, Us2, Us3, ... Us(N-1), сохраняемые в блоке 1 выборки, тогда для получения действительной (мнимой) части k-ой гармоники спектра сигнала необходимо выполнить операцию

Пусть Ur0, Ur1, Ur2, Ur3, ... Ur(N-1) значения напряжения, сохраняемые попеременно в блоках 7 и 8 выборки после выполнения операции (6) (четные значения выборок сохраняются в блоке 7 выборки, нечетные значения выборок сохраняются в блоке 8 выборки). Тогда

Ur0=-(L0Us0)

Ur1=-(L1Us1-L0Us0)=-L1Us1+L0Us0

Ur2=-(L2Us2-(L1Us1-L0Us0))=-L2Us2+L1Us1-L0Us0

Ur3=-(L3Us3-(L2Us2-(L1Us1-L0Us0)))=-L3Us3+L2Us2-L1Us1+L0Us0

где sgn(Li) - знак Li (sng(-1)=-1, sgn(1)=1), N - четное число.

Действительно, при

выражение (8) может быть приведено к выражению (7).

Тригонометрические функции cos(2πik/N) и sin(2πik/N) могут иметь произвольный знак, а цифровой масштабирующий потенциометр 3 обеспечивает умножения аналогового напряжения U1 лишь на положительное значение двоичного кода  ; для получения из выражения (8) выражения (7) необходимо инвертировать входной сигнал нечетных выборок Us(2m-1). Таким образом, в блоке постоянной памяти 10 каждого из процессоров должны храниться модули функции косинуса (синуса)

; для получения из выражения (8) выражения (7) необходимо инвертировать входной сигнал нечетных выборок Us(2m-1). Таким образом, в блоке постоянной памяти 10 каждого из процессоров должны храниться модули функции косинуса (синуса)  и значения управляющего сигнала входа блока 2 управляемой инверсии, управляющие сигналы для входа блока 2 управляемой инверсии должны формироваться следующим образом: все произведения

и значения управляющего сигнала входа блока 2 управляемой инверсии, управляющие сигналы для входа блока 2 управляемой инверсии должны формироваться следующим образом: все произведения  ·Usi с четными номерами индекса i должны иметь знак коэффициента sgn(Li), все произведения

·Usi с четными номерами индекса i должны иметь знак коэффициента sgn(Li), все произведения  ·Usi с нечетными номерами индекса i должны иметь знак, обратный знаку коэффициента косинуса sgn(Li).

·Usi с нечетными номерами индекса i должны иметь знак, обратный знаку коэффициента косинуса sgn(Li).

В каждом цикле вычислений блок постоянной памяти 34 выдает управляющий сигнал, обеспечивающий выборку входного информационного сигнала с информационного входа Х устройства в блок 1 выборки. Сигнал выхода блока 1 выборки инвертируется или не инвертируется (зависит от номера выборки и знака коэффициента) на блоке 2 управляемой инверсии и, умножаясь на коэффициент масштабирующего потенциометра 3, поступает на инвертирующий вход операционного усилителя 6.

На выходах блоков 10 постоянной памяти, как было показано выше, устанавливается цифровой двоичный код. В этом случае на выходе операционного усилителя 6 появляется сигнал UвыхОУi

На следующем такте установившееся значение выхода операционного усилителя 6 сохраняется в одном из блоков 7 или 8 выборки (попеременно в зависимости от номера выполняемого цикла вычислений) Uri, а коммутатор 9 переключается в положение, обеспечивающее прохождение на масштабирующий резистор 5 частной суммы, накопленной в предшествующем цикле вычислений (с выхода блока 7 или 8 выборки, в зависимости от номера выполняемого цикла вычислений). При этом блоки 7 или 8 выборки, используемые для хранения частной суммы в i-м и i+1-м циклах вычислений должны быть разные.

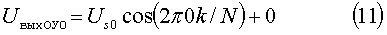

В первом цикле вычислений i=0 на вход разрешения коммутатора 9 поступает сигнал, отключающий его выход, чем обеспечивается суммирование произведения с нулем

а значение UвыхОУ0 сохраняется в блоке выборки 8.

При четных номерах выборки (за исключением i=0) i=2, 4, ... (N-2) (N - четное число) значение напряжения UвыхОУi сохраняется в блоке выборки 8, а на вход масштабирующего резистора 5 с выхода коммутатора 9 поступает напряжение блока выборки 7.

При нечетных номерах выборки i=1, 3, 5, ... (N-1) значение напряжения UвыхОУi сохраняется в блоке выборки 7, а на вход масштабирующего резистора 5 с выхода коммутатора 9 поступает напряжение блока выборки 8.

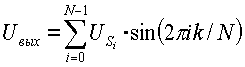

Последовательность действий второго процессора первого вида совпадает с последовательностью действий первого процессора первого вида, при этом используемые выражения и блоки первого процессора заменяются на следующие: блоки 1, 7 и 8 выборки на блоки 39, 45 и 46 выборки, блок управляемой инверсии 2 на блок управляемой инверсии 40, масштабирующий потенциометр 3 на масштабирующий потенциометр 41, блок постоянной памяти 10 на блок постоянной памяти 48, масштабирующие резисторы 4 и 5 на масштабирующие резисторы 42 и 43, операционный усилитель 6 на операционный усилитель 44, коммутатор 9 на коммутатор 47, выражение (7) на

,

,

выражение (9) на

Li=sin(2πik/N),

выражение (10) на

,

,

выражение (11) на

UвыхОУ0=Us0sin(2π0k/N)+0

Таким образом, по окончании выполнения N-1 цикла на выходе блока 7 выборки первого процессора первого вида формируется сигнал, удовлетворяющий выражению

и является действительной составляющей гармоники k разложения сигнала в ряд Фурье. На выходе блока 45 второго процессора первого вида формируется сигнал, удовлетворяющий выражению

и является мнимой составляющей гармоники k разложения сигнала в ряд Фурье.

Первый процессор второго вида работает следующим образом.

По окончанию вычисления N выборок выход переполнения Р счетчика 32 взводит регистр 35, выход которого разрешает поступление тактовых импульсов на счетчик 37, выход которого является адресным входом блока 38 постоянной памяти, выдающего управляющие сигналы на процессор второго вида.

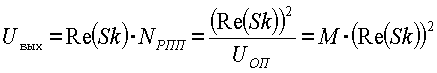

Коммутаторы 20 и 21 устанавливаются в состояние, обеспечивающее прохождение сигнала с информационного выхода первого и второго процессоров 1 вида. На блоки 22 и 24 выборки поступают управляющие сигналы для сохранения действительной и мнимой частей k-ой гармоники спектра. Коммутатор 12 устанавливается в состояние, обеспечивающее прохождение сигнала с выхода источника опорного напряжения 11 на вход блока 13 управляемой инверсии. Выход коммутатора 26 отключается с помощью сигнала разрешения, поступающего с выхода блока 38 постоянной памяти. Коммутатор 27 устанавливается в состояние, обеспечивающее прохождение сигнала с блока выборки 22 на аналоговый второй вход компаратора 16. На первый вход компаратора поступает сигнал с выхода операционного усилителя 19. Одновременно с выхода блока 38 постоянной памяти поступает сигнал запуска регистра 15 последовательных приближений. Далее с выхода блока 38 постоянной памяти на тактовый вход регистра 15 последовательных приближений поступает n (n - разрядность кода) тактовых импульсов. По окончании процесса последовательных приближений напряжения, поступающие на оба входа компаратора 16, становятся равными. На один вход компаратора поступает напряжение с выхода блока 22 выборки, т.е. Re(Sk), а на другой вход - UОП·NРПП, где UОП - выходное напряжение источника 11 опорного напряжения, NРПП - выходной код регистра последовательных приближений. Таким образом

Re(Sk)=UОП·NРПП

или

NРПП=Re(Sk)/UОП

Затем коммутатор 12 переключается в состояние, обеспечивающее прохождение сигнала с выхода коммутатора 27 на вход блока 13 управляемой инверсии. В этом случае на выходе операционного усилителя 19 возникает сигнал

где М - масштабирующий коэффициент, равный 1/UОП.

Выходное напряжение операционного усилителя 19 фиксируется в блоке 23 выборки.

Коммутатор 12 устанавливается в состояние, обеспечивающее прохождение сигнала с выхода источника 11 опорного напряжения 1 на вход блока 12 управляемой инверсии. Коммутатор 27 переключается в состояние, обеспечивающее прохождение сигналов с выхода блока 24 выборки на второй аналоговый вход компаратора 16. На первый аналоговый вход компаратора поступает выходной сигнал операционного усилителя 19. Блок 38 постоянной памяти выдает сигналы, обеспечивающие выполнение операции последовательного приближения. Тогда, аналогично рассмотренному случаю, на выходе регистра последовательных приближений формируется код NРПП=Im(Sk)/UОП.

Коммутатор 12 переключается в положение, обеспечивающее прохождение сигнала с выхода коммутатора 27 на вход блока 13 управляемой инверсии. Коммутатор 26 переключается в активное состояние и обеспечивает прохождение сигнала с выхода блока 23 выборки на масштабирующий резистор 18. В этом случае на выходе операционного усилителя 19 формируется напряжение

Uвых=Im(Sk)·NРПП+M·(Re(Sk))2=M·(Im(Sk))2+M·(Re(Sk))2,

которое фиксируется в блоке 25 выборки.

Коммутатор 12 переключается в положение, обеспечивающее прохождение сигнала с выхода источника 11 опорного напряжения на информационный вход блока 13 управляемой инверсии. Коммутатор 26 блокируется сигналом разрешения, поступающим на его управляющий вход. Коммутатор 27 переключается в состояние, обеспечивающее прохождение сигнала с выхода блока 25 выборки на второй аналоговый вход компаратора 16. На первый аналоговый вход компаратора поступает выходной сигнал операционного усилителя 19. На вход запуска регистра 15 последовательных приближений поступает импульс запуска, а затем первый тактовый импульс - на тактовый вход регистра. Одновременно с приходом тактового импульса открывается блок 23 выборки, обеспечивающий фиксацию произведения UОП на первый разряд формируемого кода. По окончании процесса выборки коммутатор 12 переключается в положение, обеспечивающее прохождение сигнала с выхода блока 23 выборки на вход блока 13 управляемой инверсии. Следовательно, на выходе операционного усилителя 19 формируется сигнал

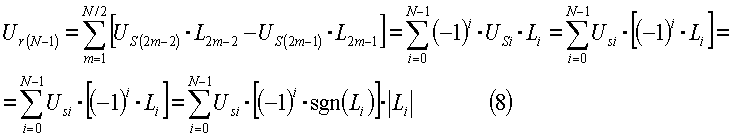

,

,

где I - номер такта приближения.

По окончании процесса установления напряжения на выходе операционного усилителя 19 на тактовый вход регистра 15 последовательных приближений поступает следующий тактовый импульс и происходит фиксация в регистре значения выхода компаратора 16. Далее коммутатор 12 переключается в положение, обеспечивающее прохождение сигнала с выхода источника 11 опорного напряжения, открывается блок 23 выборки и процесс последовательного приближения повторяется для всех n разрядов формируемого кода.

По окончании процесса формирования кода выходное напряжение операционного усилителя 19 равно

или

Таким образом, на выходах регистра 15 последовательных приближений появляется цифровой двоичный код, равный модулю k-ой гармоники исследуемого сигнала. Этот код является цифровым выходом амплитуды сигнала процессора второго вида и устройства 50.

Коммутатор 12 переключается в состояние, обеспечивающее прохождение сигнала с выхода источника 11 опорного напряжения. В этом случае на выходе операционного усилителя 19 формируется сигнал

Одновременно открывается блок 25 выборки, обеспечивающий фиксацию выходного напряжения. Сформированный аналоговый сигнал поступает на аналоговый выход амплитуды сигнала процессора второго вида и является выходом устройства 49.

При переполнении счетчика 37 на выходе переполнения вырабатывается сигнал, обеспечивающий установку регистра 35 в ноль. Работа процессора второго вида заканчивается до следующего вычисления Re(Sk) и Im(Sk) в первом и втором процессорах первого вида от N выборок входного сигнала устройства.

Расширение входного диапазона обеспечивается более чем в 2 раза за счет параллельного вычисления действительной и мнимой составляющих и введения конвейера. Конвейер заключается в том, что за счет процессора второго вида, вычисляющего амплитуду k-ой гармоники от N выборок, в процессорах первого вида выполняется операция свертки от следующих N выборок входного информационного сигнала.

Источники информации

1. Патент РФ №2182358 от 2000.02.28.

2. Патент РФ №2000104761 от 2002.03.27.

3. Патент СССР №1679501 от 1989.03.03.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения дискретного преобразования Фурье | 1989 |

|

SU1679501A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1223248A1 |

| Устройство для вычисления спектра сигналов | 1986 |

|

SU1383392A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

Изобретение относится к средствам специализированной вычислительной техники и может найти применение в спектральном анализе сигналов в реальном масштабе времени. Технический результат изобретения заключается в повышении быстродействия и расширении спектра входного сигнала за счет распараллеливания вычисления действительной и мнимой частей и введения конвейеризации. Он достигается тем, что устройство вычисляет действительную, мнимую части и амплитуду k-ой гармоники спектра сигнала. Так как время вычисления обратно пропорционально максимальной допустимой частоте входного информационного сигнала, то уменьшение времени обработки приводит к увеличению максимальной допустимой частоты входного сигнала. Устройство содержит 2 процессора, выполняющих свертку входного сигнала с определенными коэффициентами, и один процессор, выполняющий вычисление амплитуды k-ой гармоники спектра. Выходами устройства являются информационные выходы первых двух процессоров, действительная и мнимая части k-ой гармоники спектра в аналоговой форме, и информационные выходы третьего процессора - амплитуда k-ой гармоники спектра в цифровой и аналоговой форме. 1 ил.

Аналого-цифровое многопроцессорное устройство вычисления дискретного преобразования Фурье, содержащее первый, второй и третий блоки выборки, первый блок управляемой инверсии, первый масштабируемый потенциометр, первый блок постоянной памяти, содержащий цифровые двоичные коды, соответствующие модулю коэффициентов Фурье, первый и второй масштабирующие резисторы, операционный усилитель, коммутатор, объединенные в первый процессор первого вида, блока задержки, первый регистр, генератор тактовых импульсов, элемент И, первый и второй счетчики, второй блок постоянной памяти, информационный вход первого блока выборки является информационным входом процессора первого вида, выход первого блока управляемой инверсии подключен к информационному входу первого масштабирующего потенциометра, выход которого подключен к инвертирующему входу первого операционного усилителя и входам первого и второго масштабирующих резисторов, выход первого операционного усилителя подключен к выходу первого масштабирующего резистора и информационным входам второго и третьего блоков выборки, выход второго блока выборки подключен к первому информационному входу первого коммутатора и является информационным выходом процессора, выход третьего блока выборки подключен ко второму информационному входу первого коммутатора, выход которого подключен к выходу второго масштабирующего резистора, неинвертирующий вход первого операционного усилителя заземлен, вход запуска устройства подключен к входу блока задержки и входам сброса первого и второго счетчиков, выход блока задержки подключен к входу установки в "1" первого регистра, выход которого подключен ко второму входу первого элемента И, первый вход которого подключен к выходу генератора тактовых импульсов, выход первого элемента И подключен к тактовому входу второго счетчика, выход которого подключен к адресному входу второго блока постоянной памяти, выход которого подключен к тактовому входу первого счетчика, выход переполнения которого подключен к входу сброса первого регистра, отличающееся тем, что введены четвертый, пятый и шестой блоки выборки, второй блок управляемой инверсии, второй масштабирующий потенциометр, третий блок постоянной памяти, содержащий цифровые двоичные коды, соответствующие модулю коэффициентов Фурье, третий и четвертый масштабирующие резисторы, второй операционный усилитель, второй коммутатор, объединенные во второй процессор первого вида, источник опорного напряжения, коммутаторы с третьего по седьмой, третий блок управляемой инверсии, третий масштабирующий потенциометр, регистр последовательных приближений, компаратор, третий операционный усилитель, пятый и шестой масштабирующие резисторы, блоки выборки с седьмого по десятый, объединенные в первый процессор второго вида, второй регистр, второй элемент И, третий счетчик, четвертый блок постоянной памяти, информационный вход четвертого блока выборки является информационным входом второго процессора первого вида, выход второго блока управляемой инверсии подключен к информационному входу второго масштабирующего потенциометра, выход которого подключен к инвертирующему входу второго операционного усилителя и входам третьего и четвертого масштабирующих резисторов, выход второго операционного усилителя подключен к выходу третьего масштабирующего резистора и информационным входам пятого и шестого блоков выборки, выход пятого блока выборки подключен к первому информационному входу второго коммутатора и является информационным выходом второго процессора первого вида, выход шестого блока выборки подключен ко второму информационному входу второго коммутатора, выход которого подключен к выходу четвертого масштабирующего резистора, неинвертирующий вход второго операционного усилителя заземлен, выход первого блока выборки первого процессора первого вида подключен к входу первого блока управляемой инверсии, управляющий вход которого подключен к первому выходу первого блока постоянной памяти, остальные выходы которого подключены к управляющему входу первого масштабирующего потенциометра, выход четвертого блока выборки второго процессора первого вида подключен к входу второго блока управляемой инверсии, управляющий вход которого подключен к первому выхода третьего блока постоянной памяти, остальные выходы которого подключены к управляющему входу второго масштабирующего потенциометра, выход переполнения первого счетчика подключен к входу установки в "1" второго регистра, выход которого подключен к второму входу второго элемента И, первый вход которого подключен к выходу генератора тактовых импульсов, выход второго элемента И подключен к тактовому входу третьего счетчика, выход переполнения которого подключен к входу сброса второго регистра, информационный выход третьего счетчика подключен к адресному входу четвертого блока постоянной памяти, выход источника опорного напряжения подключен к первому информационному входу третьего коммутатора, выход которого подключен к информационному входу третьего блока управляемого инверсией, выход которого подключен к информационному входу третьего масштабирующего потенциометра, выход которого подключен к инвертирующему входу третьего операционного усилителя и входам пятого и шестого масштабирующих резисторов, выход третьего операционного усилителя подключен к выходу пятого масштабирующего резистора, первому входу компаратора, информационному входу восьмого и десятого блоков выборки, первому информационному входу четвертого и пятого коммутаторов и является аналоговым выходом амплитуды гармоники сигнала первого процессора второго вида и устройства, выходы четвертого и пятого коммутаторов подключены к информационным входам соответственно седьмого и девятого блоков выборки, выход седьмого блока выборки подключен к первому информационному входу шестого и седьмого коммутаторов, выход восьмого блока выборки подключен ко второму информационному входу шестого и седьмого коммутаторов и к третьему информационному входу третьего коммутатора, выход девятого блока выборки подключен к третьему информационному входу шестого и седьмого коммутаторов, выход десятого блока выборки подключен к четвертому информационному входу шестого и седьмого коммутаторов, выход шестого коммутатора подключен к выходу шестого масштабирующего резистора, выход седьмого коммутатора подключен ко второму информационному входу третьего коммутатора и второму входу компаратора, выход которого подключен к информационному входу регистра последовательных приближений, выход которого подключен к управляющему входу третьего масштабирующего потенциометра и является цифровым выходом амплитуды гармоники сигнала первого процессора второго вида и устройства, неинвертирующий вход третьего операционного усилителя заземлен, первый информационный вход первого процессора второго вида подключен ко второму информационному входу четвертого коммутатора, второй информационный вход первого процессора второго вида подключен ко второму информационному входу пятого коммутатора, выход четвертого блока постоянной памяти подключен к адресным входам третьего, четвертого, пятого, шестого и седьмого коммутаторов, к входу разрешения шестого коммутатора, к управляющим входам седьмого, восьмого, девятого и десятого блоков выборки, к управляющему входу третьего блока управляемой инверсии, к установочному и тактовому входам регистра последовательных приближений, выходы со второго по шестой второго блока постоянной памяти подключены к управляющим входам первого и четвертого блоков выборки, к управляющим входам второго и пятого блоков выборки, к управляющим входам третьего и шестого блоков выборки, к разрешающему входу первого и второго коммутаторов, к адресному входу первого и второго коммутаторов, выход первого счетчика подключен к адресным входам первого и третьего блоков постоянной памяти, информационному входу устройства подключен к информационным входам первого и второго процессоров первого вида, информационный выход первого процессора первого вида подключен к первому информационному входу первого процессора второго вида и является выходом устройства действительной части к-й гармоники спектра сигнала, информационный выход второго процессора первого вида подключен ко второму информационному входу первого процессора второго вида и является выходом устройства мнимой части к-й гармоники спектра сигнала.

| Устройство для выполнения дискретного преобразования Фурье | 1989 |

|

SU1679501A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Процессор быстрого преобразования Фурье | 1987 |

|

SU1425709A1 |

| ЕР 1058435 А1, 06.12.2000. | |||

Авторы

Даты

2008-09-10—Публикация

2006-12-04—Подача