ния определения и обработки большего и меньшего координатных приращений на блоке 2 dpaBHeHHH координатных приращений и блоке 42 нормализации кодов. Повышение точности достигается за счет нормализации координатных приращений перед вьшолнением деления, определением и исключением с помощью дешифратора 34 кодов направлений и мультиплексора ситуации деления на нуль, разнесением во времени процессов интегрирования и коммутации аналоговых сигналов, а также принудительным вьгаодом усилителей 24, 25 откло1

Изобретение относится к вычислительной технике и может быть использовано в графических дисплеях функ- , ционального (векторного) типа.

Цель изобретения - повышение быстродействия и точности устройства.

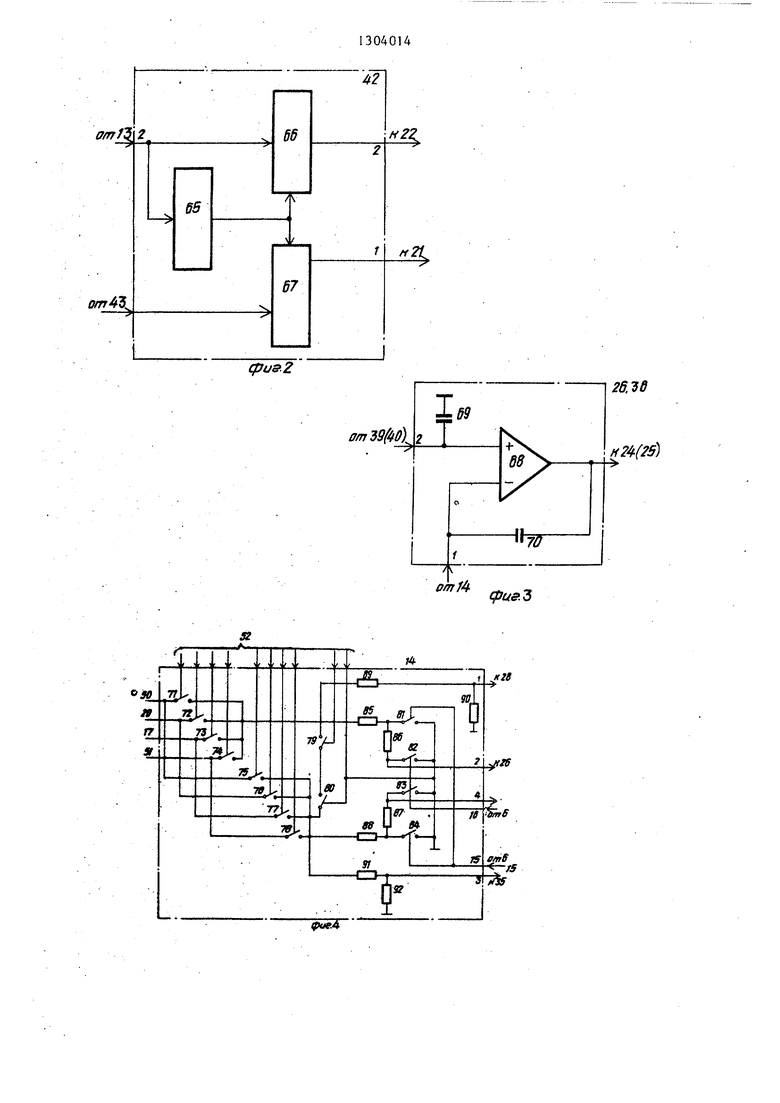

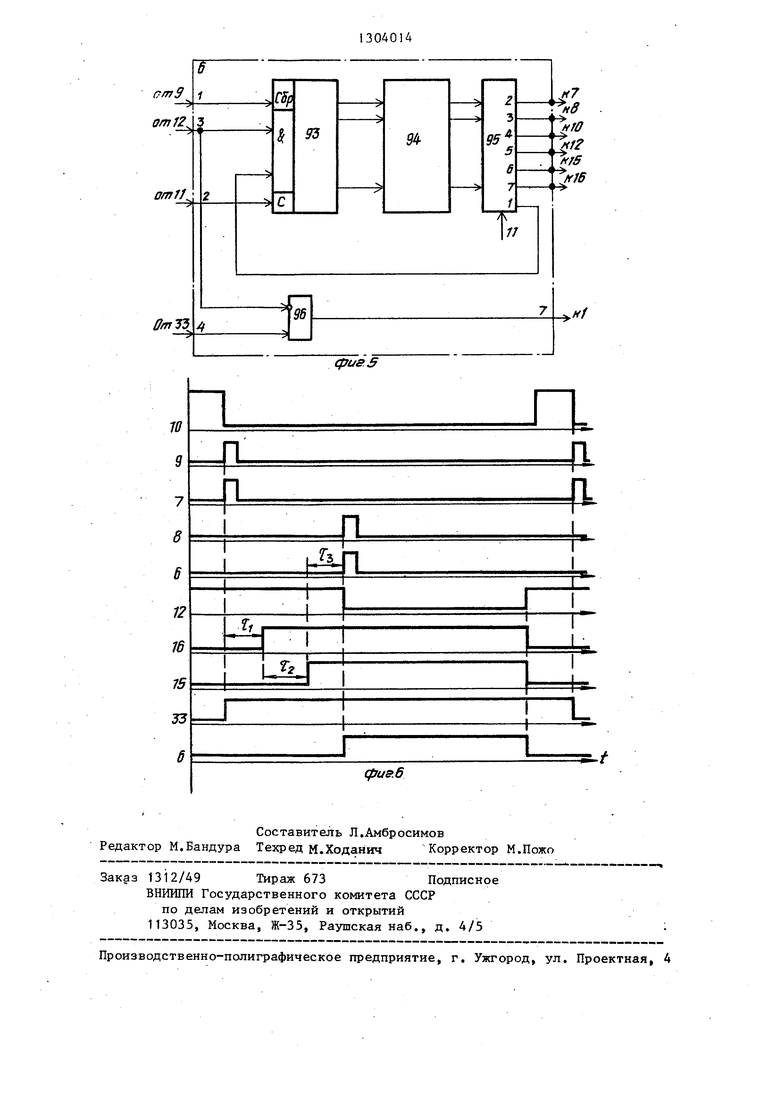

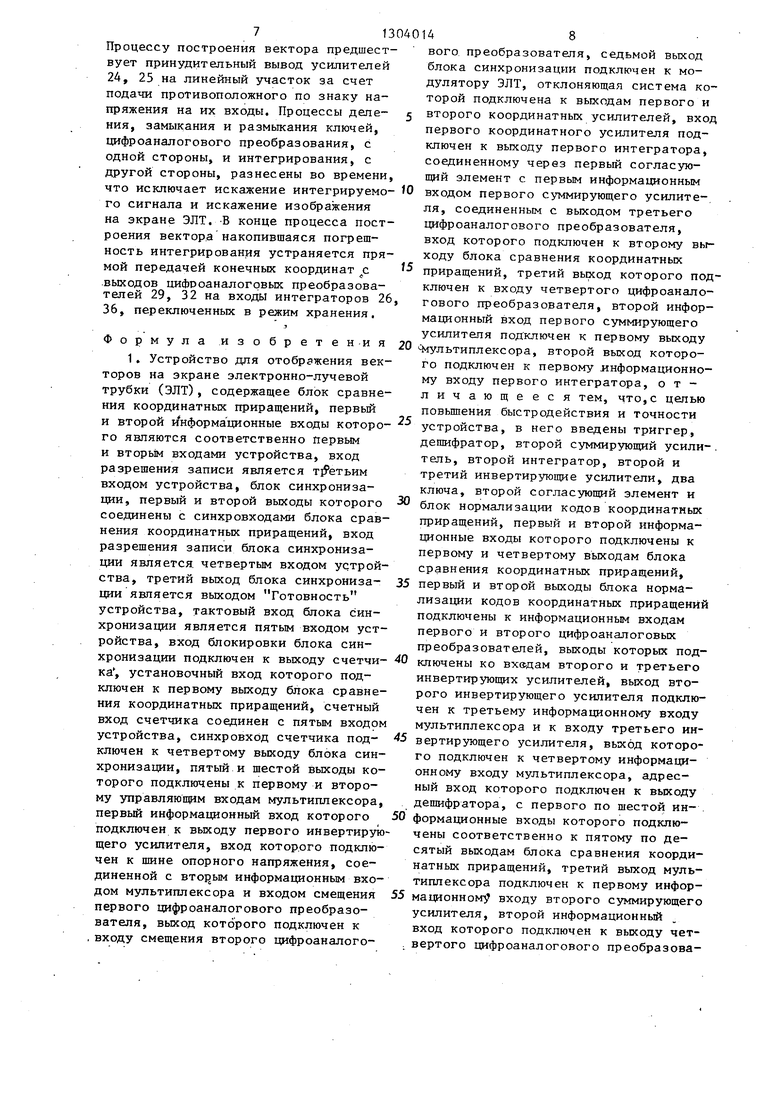

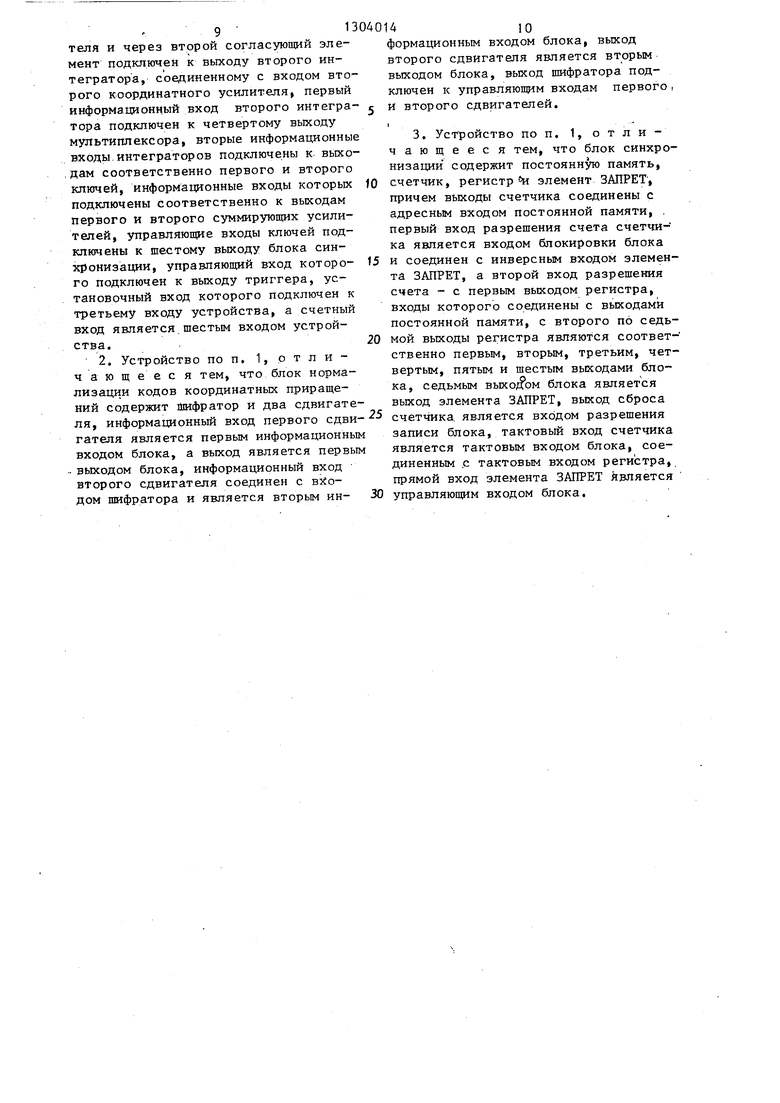

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - схема блока нормализации кодов координатных приращений на фиг. 3 - схема мультиплексора, на фиг. 4 - схема интегратора, на фиг. 5 - блок синхронизации; на фиг. 6 - временная диаграмма выработки управляюшях. сигналов синхронизации. .

Устройство для отображения векторов на экране электронно-лучевой трубки содержит электронно-лучевую трубку 1 (ЭЛТ), блок 2 сравнения координатных приращений, первый, второй и третий входы 3, 4 и 5, блок 6 синхронизации, синхровходы 7 и 8 блока 2, четвертый вход 9,выход 10 готовность и пятый эход 11, счетчик 12, первый выход 13 блока 2, мультиплексор 14, первый и второй управляющие входы 15, 16 мультиплексора 14, первый информационный вход 17 мультиплексора 14, первый инвертирующий усилитель 18, .шину 19 опорного напряжения, второй информационный .вход 20 мультиплексора 14, первый цифроаналоговый преобразователь 21, второй цифроаналоговый преобразователь 22, отклоняющую систему 23 ЭЛТ 1, первый и второй коор- .динатные усилители 24 и 25, первый интегратор 26, первый согласуюший

няющей системы ЭЛГ на линейный участок и коррекдаей накопившейся .погрешности интегрирования. Для обеспечения реализации цели в состав устройства дополнительно введены триггер 33, дешифратор 34, второй суммирующий усилитель 35, второй интегратор 36, второй и третий инвертируюш 1е усилители 37 и 38, два ключа 39, 40, второй согласующий : лемент 41 и блок 42 нормализации кодов. Кроме того,введен ряд новых связей и изменена структура блока синхронизации и мультиплексора, 2 з.п.ф-лы, 6 ил, f табл.

элемент 27, первьЙ суммирующий усилитель 28, третий цифроаналоговый преобразователь 29, второй и третий выходы 30 и 31 блока 2, четвертый циф- роаналоговый преобразователь 32, триггер 33, дешифратор 34, второй сумми- усилитель 35, второй интегратор 36, второй и третий ипвертирую- ш;ие усилители 37 и 38, первый 39 и О второй 40 ключи, второй согласующий элемент 41, блок 42 нормализации ко- дрв координатных приращений, с четвертого по десятый выходы 43-49 блока 2, третий и четвертый информацион- ные входы 50-51 мультиплексора 14, адресный вход 52 мультиплексора 14 и шестой вход 53.

Блок 2 сравнения координатных приращений содержит с первого по шестой регистры 54-59, первый 60 и второй 61 вычитатели, элемент 62 сравнения, мультиплексоры 63 и 64.

Блок 42 нормализации кодов координатных приращений содержит шифратор 65 и сдвигатели 66 и 67.

Каждый интегратор 26 и 36 содержит усилитель 68 и элементы памяти на конденсаторах 69 и 70.

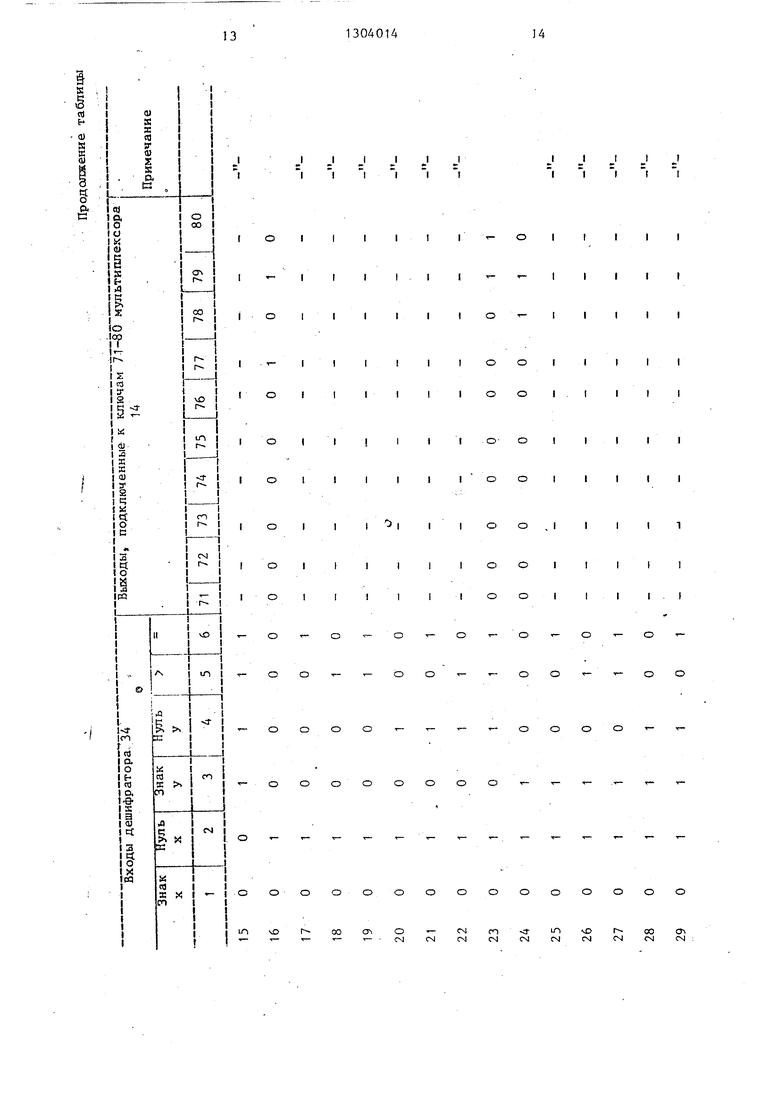

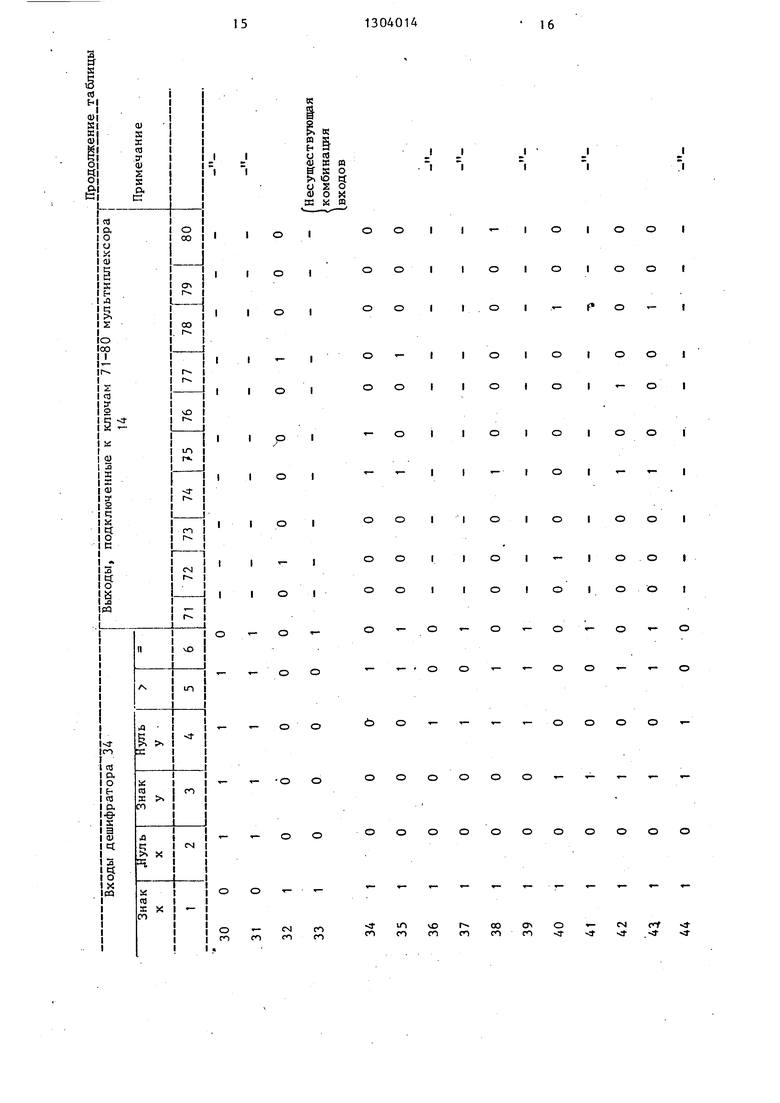

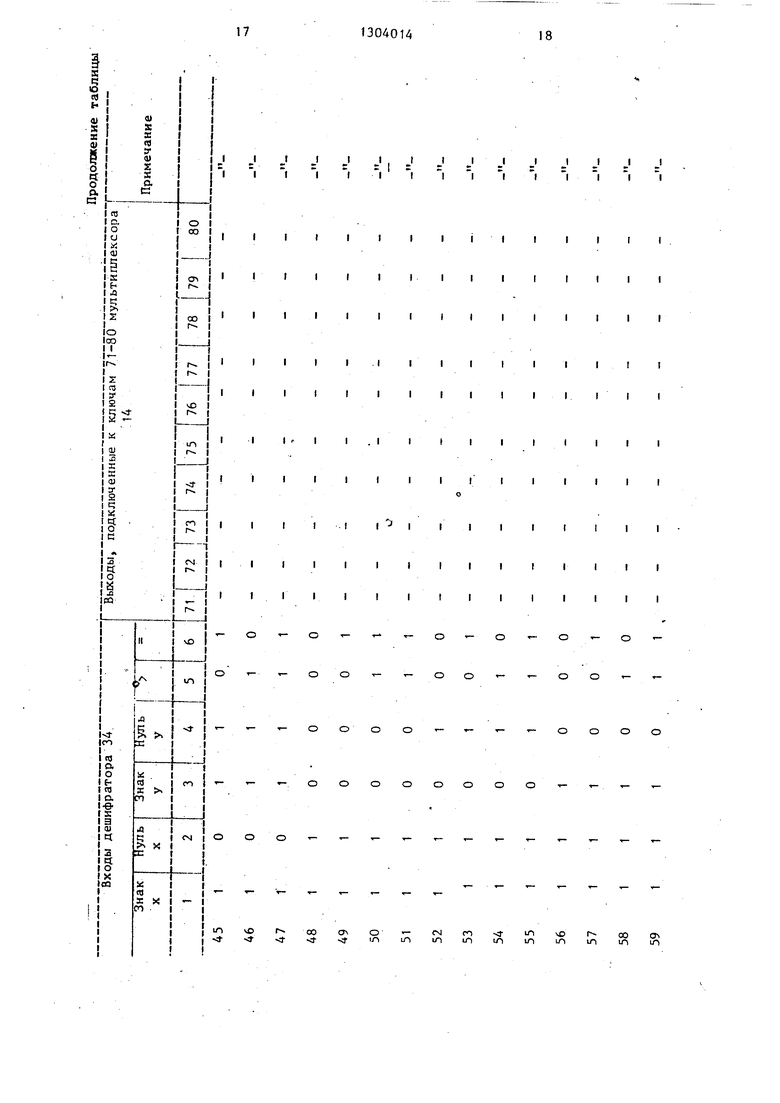

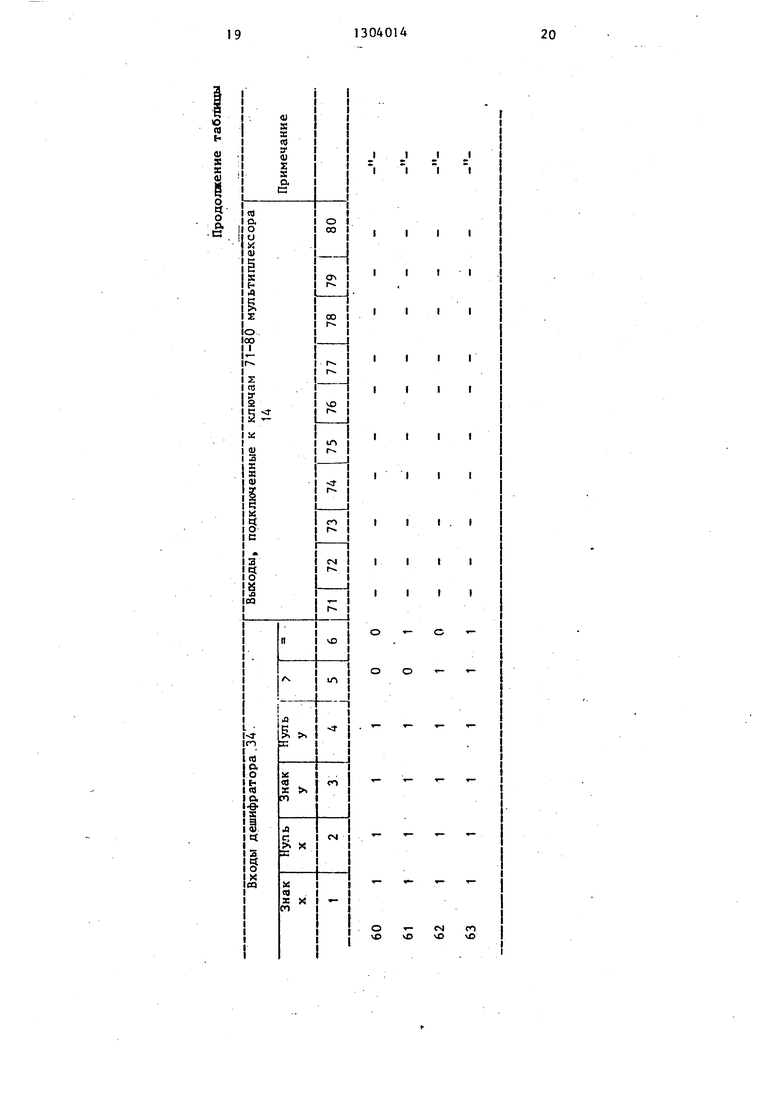

Мультиплексор 14 содержит аналого5

0

вые ключи 71-84 и резисторы 85-92.

Управляю.шде входы ключей 71-80 соеди-- нены с соответствующими входами мультиплексора, а управляющие входы ключей 81-84 являются управляюшими входами 35 15 и 16 мультиплексора.

Блок 6 синхронизации содержит счетчик 93, узел 94 постоянной памяти.

регистр 95 микрокоманды и элемент 96 ЗАПРЕТ.

При этом вход сброса счетчика 93 является входом разрешения записи блошает глубину обратной связи в зависи мости от значения большего приращени В результате по истечении времени ус тановления цифроаналогозого преобразователя 22 на выходе усилителя 37 п появляется напряжение, пропорциональ ное опорному напряжению и отношению значений меньшего приращения к большему.

Усилители 18 и 38 инвертируют опорное напряжение и напряжение с усилителя 37. Эти четыре сигнала пос тупают на входы 17, 20 50, 51 мультиплексора 14 и в соответствии с пока, а объединенные входы разрешения счета - входом блокировки блока и соединены с первьм выходом регистра 95 микрокоманды.

Устройство работает следующим образом.

По сигналу готовность на выходе 10 устройства осуществляется загрузка координат конца очередного вектора, входящего в цепочку векторов. Для этого на входы 3 и 4 устройства из ff ложением ключей 71-84 появляются на ЭВМ поступают значения пары конечных первом-четвертом выходах мультиплек- координат, а на вход 5 - сигнал Раз- сора 14, поделенными делителями на решение записи, который вызывает запись этих координат в регистры 54 и 55. Одновременно с этим бит разреше- 20 (.четвертом выходах мультиплексора 14 ния подсветки-данного вектора заносит- сигнал равен 0. Сигналы, поступающие ся в триггер 33 с входа 53. Далее осу- на неинвертируюшгте входы усилителей ществляется вычисление модулей координат приращений на вычитателях 60 и 61 путем вычитания из значений конеч-25 ли 28, 35, через интеграторы 26, 36 ных координат значений начальных ко- и поступают на входы усилителей 24, ординат из регистров 56 и 57, Кроме модулей приращений вычитателй вьщают также разряды знака и признаки нулевого кода. Результаты вычитания зано-30 сятся в регистры 58 и 59 по сигналу на втором выходе блока 6 синхронизации. Элемент 62 сравнивает значения модулей координатных приращений и управляет мультиплексорами 63 и 64 так,35 вызывающий размыкание ключей 39, 40 чтобы на первый вход блока 42 норма- и ключей 82, 83 в мультиплексоре ,14.

резисторах 89-92. Ключи 81-84 в это время замкнуты.поэтому на втором и

28, 35 при замкнутых ключах 39, 40, проходят без изменения через усилите25 отклонения. В результате изменяется значение тока в отклоняющей системе пропорционально этим сигналам.

По истечении времени f , необходимого для завершения переходного процесса, в усилителях 24, 25 отклонения на шестом выходе блока 6 синхронизации появляется логический сигнал,

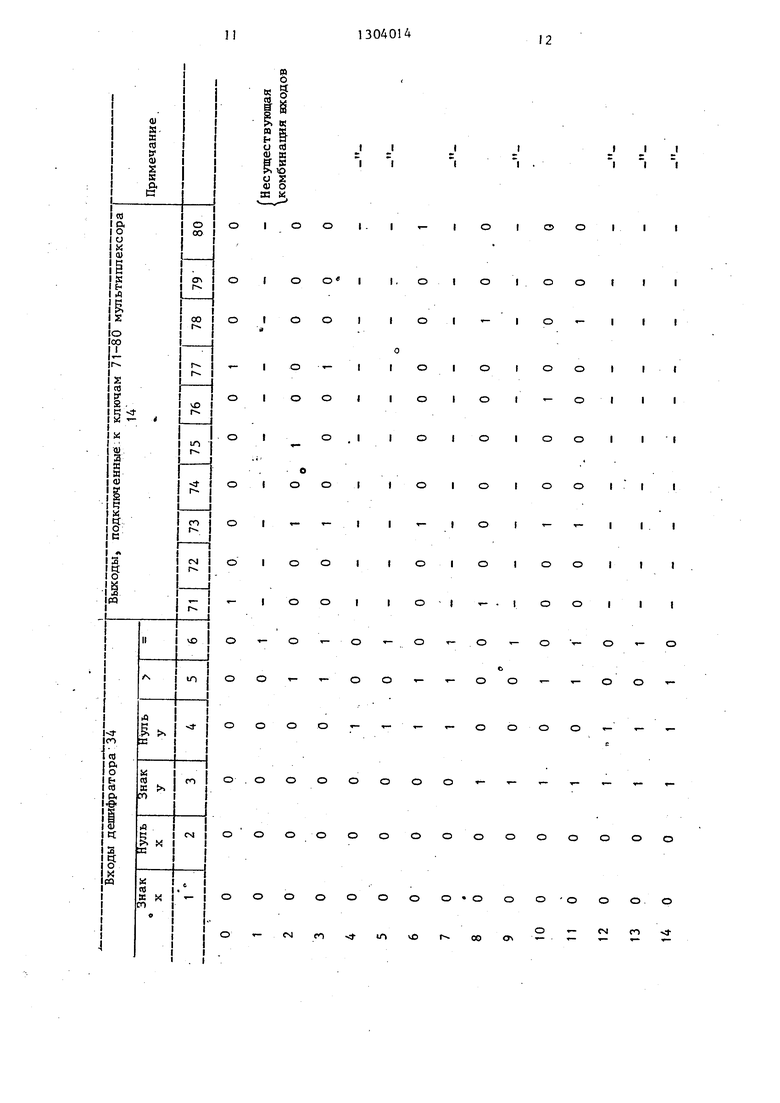

лизации кодов координатных приращений поступило меньшее координатное приращение, а на второй вход блока 42 - большее. Одновременно с этим на выходе дешифратора 34 появляются управляющие сигналы, которые замыкают ключи 71-80 аналогового мультиплексоПосле задержки Т, , необходимой для надежного срабатывания ключей 39, 40, появляется сигнал на пятом выходе блора 14 в соответствии с таблицей. На

входы дешифратора 34 при этом посту- 45 а 6 синхронизации. Этот сигнал вьгпают коды знаков и признаков нулево- зывает размыкание ключей 81, 84 в

го кода по каждой из координат,а так-же признаки больше и равно из

элемента 62 сравнения.

мультиплексоре 14. В результате ин- вертируюш 1е входы интеграторов 26 и 36 через резисторы 85, 86 и 87, 88 50 подключаются к входным сигн алам муль- Опорное напряжение с входа 19 де- типлексора 14 в соответствии с замкну- - лится при помощи цифроаналогового пре- тыми ключами 71-80. С этого момента образователя 21 на значение меньшего начинается интегрирование с постоян- приращения, поступающего с первогоной времени, обусловленной значением

выхода блока 42 нормализации кодов $5 напряжения-входного сигнала, сопро- координатных приращений, и передается на вход усилителя-37. В обратной связи усилителя 37 включен цифроаналоготивлениями резисторов 85, 86, 87, 88 и емкостями 70 в интеграторах 26 и 36. Изменение напряжения на выходах

вый преобразователь 22, который умень- интеграторов 26 и 36 будет противошает глубину обратной связи в зависимости от значения большего приращения В результате по истечении времени установления цифроаналогозого преобразователя 22 на выходе усилителя 37 по появляется напряжение, пропорциональное опорному напряжению и отношению значений меньшего приращения к большему.

Усилители 18 и 38 инвертируют опорное напряжение и напряжение с усилителя 37. Эти четыре сигнала поступают на входы 17, 20 50, 51 мультиплексора 14 и в соответствии с поожением ключей 71-84 появляются на первом-четвертом выходах мультиплек- сора 14, поделенными делителями на .четвертом выходах мультиплексора 14 сигнал равен 0. Сигналы, поступающие на неинвертируюшгте входы усилителей и 28, 35, через интеграторы 26, 36 и поступают на входы усилителей 24, вызывающий размыкание ключей 39, 40 ключей 82, 83 в мультиплексоре ,14.

ложением ключей 71-84 появляются на первом-четвертом выходах мультиплек- сора 14, поделенными делителями на (.четвертом выходах мультиплексора 14 сигнал равен 0. Сигналы, поступающие на неинвертируюшгте входы усилителей ли 28, 35, через интеграторы 26, 36 и поступают на входы усилителей 24, вызывающий размыкание ключей 39, 40 и ключей 82, 83 в мультиплексоре ,14.

резисторах 89-92. Ключи 81-84 в это время замкнуты.поэтому на втором и

ложением ключей 71-84 появляются на первом-четвертом выходах мультиплек- сора 14, поделенными делителями на .четвертом выходах мультиплексора 14 сигнал равен 0. Сигналы, поступающие на неинвертируюшгте входы усилителей ли 28, 35, через интеграторы 26, 36 и поступают на входы усилителей 24, вызывающий размыкание ключей 39, 40 и ключей 82, 83 в мультиплексоре ,14.

28, 35 при замкнутых ключах 39, 40, проходят без изменения через усилителожением ключей 71-84 появляются на первом-четвертом выходах мультиплек- сора 14, поделенными делителями на (.четвертом выходах мультиплексора 14 сигнал равен 0. Сигналы, поступающие на неинвертируюшгте входы усилителей ли 28, 35, через интеграторы 26, 36 и поступают на входы усилителей 24, вызывающий размыкание ключей 39, 40 и ключей 82, 83 в мультиплексоре ,14.

25 отклонения. В результате изменяется значение тока в отклоняющей системе пропорционально этим сигналам.

По истечении времени f , необходимого для завершения переходного процесса, в усилителях 24, 25 отклонения на шестом выходе блока 6 синхронизации появляется логический сигнал,

Напряжение, поступающее на вторые входы каждого интегратора 26, 36, запоминается на емкости 69. Токи в от- клоняющей системе 23 остаются без изменения.

После задержки Т, , необходимой для надежного срабатывания ключей 39, 40, появляется сигнал на пятом выходе блонапряжения-входного сигнала, сопро-

тивлениями резисторов 85, 86, 87, 88 и емкостями 70 в интеграторах 26 и 36. Изменение напряжения на выходах

положно no знаку предварительной установке, следовательно,через некоторое время tj значение токов в откло н.яющей системе 23 будет равно значениям, соответствующим начальной координате вектора. За это время должны закончит-ься переходные процессы в усилителях отклонения и изменение отклоняющих токов будет происходить строго по линейному закону. В этот момент блок 6 синхронизации вырабатывает импульс подсветки на седьмом выходе, начало которого совпадает с записью кода большего приращения в

счетчик 12, работающей на вычитание, 15 рующего сигнала на первом выходе реа окончание - с обнулением счетчика 12, после чего он прекращает счет.

После начала интегрирования значение модуля конечной координаты из регистров 54 и 55 переписывается в регистры 56 и 57 по управляющему сигналу на первом выходе блока 6. Это вузьгоает изменение напряжения на выходах цифроаналогоных преобразоватегистра 95 или нулевого сигнала на т1)етьем входе блока 6, начинает счет. В исходном состоянии счетчик 12 находится в нулевом состоянии, слеДова- 20 тельно,на его выходе - единичный сигнал. Запись кода с выхода мультиплексора 64 в счетчи: 12 снимает сигнал tra выходе счетчика 12 и блокирует счет в счетчике 93, что приводит к

лей 29,32 в соответствии с поступив- 25 повторению одной-и той же микрокоманды - поддержанию единичных сигналов на пятом и шестом выходах блока 6 синхронизации,, Обнуление счетчика 12 вызовет продолжение счета в счетчике

30 93. Последняя микрокоманда вьдает сигнал на выход 10 Готовность и заблокирует счет по сигналу с первого выхода регистра 95 до нового запуска. Сигнал подсветки формируется элемен35 том 96 ЗАПРЕТ по состоянию триггера 33 и признаку нулевого кода счетчика 12.

шими значениями.

Так как перемещение луча по одной из координат всегда происходит с одной и той же скоростью, длина вектора определяется длительностью импульса подсветки. После снятия этого импульса при помошти сигналов, поступающих с пятого и шестого выходов блока синхронизации, замыкаются ключи 39, 40 и 81-84 в мультиплексоре 14. Напряжения с цифроаналоговых преобразователей 29, 32, соответствуюшяе новым координатам, через усилители 28 и 35 заряжают емкости 69 интеграторов 26 и 36 и передаются на входы усилителей 24, 25 отклонения .Устойчивость цепи усилитель 28(35) - интегратор 26(36) обеспечивается согласующими

Таким образом, за счет введения в 0 устройство триггера 33, дещифратора 34, блока 42 нормализации кодов координатных приращений, второго инт е- гратора 36, усилителей 35, 37,. 38, двух аналоговых ключей 39, 40, измеТаким образом, за счет введения в 0 устройство триггера 33, дещифратора 34, блока 42 нормализации кодов координатных приращений, второго инт е- гратора 36, усилителей 35, 37,. 38, двух аналоговых ключей 39, 40, измеэлементами 27(41). Ток, соответствующий конечной координате построенного 45 ения структуры блока 6 синхрониза- вектора, будет поддерживаться в от-Ц мультиплексора 14, а также введения новых связей удается повысить быстродействие и точность устройства. Повьшение быстродействия достигается 50 благодаря перенесению операции деления на аналоговые цепи, а также быстрому определению и обработке большего и меньшего координатных приращений на элементе сравнения, мульти- 55 плексорах и блоке нормализации кодов. Ситуация деления нуля на нуль исключается вьщачей соответствующего кода с выхода дешифратора 34 на мультиплексор 14 и замыканием ключей 75,80.

клоняющей системе 23 до начала построения следующего вектора, начальные координаты которого совпадают с конечными координатами построенного вектора.

Блок 42 нормализации кодов координатных приращений осуществляет нормализацию модулей координатных приращений, т.е. сдвигает их коды так, чтобы на втором выходе блока 42 единица была бы в старшем разряде. Эта операция осуществляется на комбина

ционных сдвигателях. Величина сдвига задается шифратором 65, определяющим положение старшей единицы в канале большего приращения (второй вход блока 42).

Блок 6 синхронизации вырабатывает управляющие сигналы в соответствии с линейной микропрограммой,, записанной в узле 94 и реализующей временную диаграмму, приведенную на фиг. 6. Перебор адресов узла 94 осуществляется счетчиком 93. По сигналу на входе 9 Разрешение запуска счетчик 93 устанавливается в О и если кет блокигистра 95 или нулевого сигнала на т1)етьем входе блока 6, начинает счет. В исходном состоянии счетчик 12 находится в нулевом состоянии, слеДова- тельно,на его выходе - единичный сигнал. Запись кода с выхода мультиплексора 64 в счетчи: 12 снимает сигнал tra выходе счетчика 12 и блокирует счет в счетчике 93, что приводит к

Таким образом, за счет введения в устройство триггера 33, дещифратора 34, блока 42 нормализации кодов координатных приращений, второго инт е- гратора 36, усилителей 35, 37,. 38, двух аналоговых ключей 39, 40, изме ения структуры блока 6 синхрониза- Ц мультиплексора 14, а также вве713040148

Процессу построения вектора предшест- вого преобразователя, седьмой выход вует принудительный вывод усилителейблока синхронизации подключен к мо24, 25 на линейный участок за счетдулятору ЭЛТ, отклоняющая система коподачи противоположного по знаку на-торой подключена к выходам первого и

пряжения на их входы. Процессы деле- 5 второго координатных усилителей, вход ния, замыкания и размыкания ключей,первого координатного усилителя подцифроаналогового преобразования, сключен к выходу первого интегратора,

одной стороны, и интегрирования, ссоединенному через первый согласуюдругой стороны, разнесены во времени, щий элемент с первым информационным что исключает искажение интегрируемо- О входом первого суммирующего усилите-, го сигнала и искажение изображенияля, соединенным с выходом третьего

на экране ЭЛТ. -В конце процесса пост- цифроаналогового преобразователя, роения вектора накопившаяся погрещ-вход которого подключен к второму выность интегрирования устраняется пря- ходу блока сравнения координатных мой передачей конечных координат с приращений, третий вькод которого под- .выходов цифроаналоговых преобразова-ключен к входу четвертого цифроаналотелей 29, 32 на входы интеграторов 26, гового преобразователя, второй инфор- 36, переключенных в режим хранения.мационный вход первого суммирующего

усилителя подключен к первому выходу Формула изобретен.и я 20 смультиплексора, второй выход которо1. Устройство для отображения век- го подключен к первому информационно- торов на экране электронно-лучевойму входу первого интегратора, о т трубки (ЭЛТ), содержащее блок сравне- личающееся тем, что,с цепью ния координатных приращений, первьйповьшения быстродействия и точности

и второй и нформа ционные входы которо- устройства, в него введены триггер, го являются соответственно первымдещифратор, второй суммирующий усили-.

и BTopbiM входами устройства, входтель, второй интегратор, второй и

разрешения записи является т: етьимтретий инвертирующие усилители, два

входом устройства, блок синхрониза-ключа, второй согласующий элемент и

ции, первый и второй выходы которого -30 блок нормализации кодов координатных соединены с синхровходами блока срав- приращений, первый и второй информа- нения координатных приращений, входционные входы которого подключены к

разрешения записи блока синхрониза-первому и четвертому выходам блока

ции является, четвертым входом устрой- сравнения координатных приращений, ства, третий выход блока синхрониза- 35 первый и второй выходы блока норма- ции является выходом Готовность лизации кодов координатных приращений

устройства, тактовый вход блока син-подключены к информационным входам

хронизации является пятым входом уст- первого и второго цифроаналоговых ройства, вход блокировки блока син-преобразователей, выходы которых подхронизации подключен к выходу счетчи- 40 ключены ко вхадам второго и третьего ка, установочный вход которого под-инвертирующих усилителей, выход втоключен к первому выходу блока сравне- рого инвертирующего усилителя подклю- ния координатных приращений, счетныйчен к третьему информационному входу

вход счетчика соединен с пятым входом мультиплексора и к входу третьего ин- устройства, синхровход счетчика под- 45 вертирующего усилителя, вькод которо- ключен к четвертому выходу блока син- го подключен к четвертому информаци- хронизации, пятый и шестой выходы ко- онному входу мультиплексора, адрес- торого подключены к первому и второ-ный вход которого подключен к выходу

му управляющим входам мультиплексора, дещифратора, с первого по шестой ин- . первьй информационный вход которого 50 формационные входы которого подклю- подключен к выходу первого инвертирую- чены соответственно к пятому по де- щего усилителя, вход котор.ого подклю- сятый выходам блока сравнения коорди- чен к шине опорного напряжения, сое-натных приращений, третий выход мульдиненной с вто1)ым информационным вхо- типлексора подключен к первому инфор- дом мультиплексора и входом смещения 55 мационном; входу второго суммирующего первого цифроаналогового преобразо-усилителя, второй информационный

вателя, выход которого подключен квход которого подключен к выходу чет, входу смещения второго цифроаналого- . вертого цифроаналогового преобразователя и через второй согласующий элемент подключен к выходу второго интегратора, соединенному с входом второго координатного усилителя, первый информационный вход второго интегра- тора подключен к четвертому выходу мультиплексора, вторые информационные входы.интеграторон подключены к выхо,дам соответственно первого и второго ключей, информационные входы которых подключены соответственно к выходам первого и второго суммирующих усилителей, управляющие входы ключей подключены к шестому выходу блока синхронизации, управляющий вход которо- го подключен к выходу триггера, установочный вход которого подключен к третьему входу устройства, а счетный вход является.шестым входом устройства.

2. Устройство по п. 1, р т л и - ч а ю щ ее с я тем, что блок нормализации кодов координатных приращений содержит шифратор и два сдвигате- ля, информационный вход первого сдвигателя является первым информационным входом блока, а выход является первым

- выходом блока, информационный вход второго сдвигателя соединен с Bko- дом шифратора и является вторым ин-

04014

10

10 1520

30

формационным входом блока, выход второго сдвигателя является вторым выходом блока, выход шифратора подключен к управляюшим входам первого, и второго сдвигателей.

I

3. Устройство по п. 1, отличающееся тем, что блок синхронизации содержит постоянную память, счетчик, регистр и элемент ЗАПРЕТ, причем выходы счетчика соединены с адресным входом постоянной памяти, . первый вход разрешения счета счетчика является входом блокировки блока и соединен с инверсньм входом элемента ЗАПРЕТ, а второй вход разрешения счета - с первым выходом регистра, входы которого соединены с выходами постоянной памяти, с второго по седьмой выходы регистра являются соответ- ственно первым, вторым, третьим, четвертым, пятым и шестым выходами блока, седьмым выхо; ом блока является выход элемента ЗАПРЕТ, выход сброса счетчика, является входом разрешения записи блока, тактовый вход счетчика является тактовым входом блока, соединенным .с тактовым входом регистра, прямой вход элемента ЗАПРЕТ является управляющим входом блока.

I

о I I -- I I о II

II

о 1 I

о ( I о I I

о I I

о I t о 1 I

о о о оо r- о о

I II

I II

I I I

II 1

III

I I1

I II

1 II

I II

Ог-

о о

о

о о

in о

со СТч

J J J J l l l t

III - о ItIII

III - - IIIII

I I10- 1IIII

I 1I о о IIIII

III о о IIII1

I

1001IIII

о I1 1001 I III

III 00,1 I II1

II I о о I t II1

II I 00 I II1-1

Ог- о -г- о -о о о

о о

о

о

о

о о

о

о - с fi-a- ш-х) г со cTi

CNlCslrxlCslCMirSCMCNOJCN

IоI

IоI

I01

p

IоI

IоI

I -I

101

- оо

.- оо

г--оо

т- оо

о ,--

о - « с го СП f f

I о о

001IоIо

о о

о о I 10 I гО --I1010

о оI1010

I о о

о

011010

о о

I - о о II о I о

о о

001101001IоIо

о о о о

о - о - о

Or- о -о о -о о -

t о т- - - - о

о о ОООООО - - о о о о о о о

о о

ю о г оо о о со со со го со

CSof

-

sr

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканального интерполирования функций | 1986 |

|

SU1377878A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1520564A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Устройство для считывания графической информации | 1986 |

|

SU1383416A1 |

| Цифровой регистратор повторяющихся сигналов | 1987 |

|

SU1610279A1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

Изобретение относится к вычислительной технике и может быть использовано в графических дисплеях функционального (векторного) типа. Целью изобретения яатяется повышение быстродействия и точности устройства. По- вьннение быстродействия достигается за счет перенесения операции деления на аналоговые цепи, а также ускоре(Л со о 4 О Ift/ef

| Патент США № 3800183, , кл | |||

| Способ очищения амида ортотолуолсульфокислоты | 1921 |

|

SU315A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Патент США № 4056713, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1987-04-15—Публикация

1985-06-27—Подача