(Л

ft-e. /

7, - 7,, 8, - 8„, ключи 9/- 9„, 10, -.10„, вторые сумматоры 11, - llfj, ключи 12 ( - 12, первые интеграторы 13 4 - 13, цифpoyпpaвляe alle резисторы 14, - 14„, вторые интегра торы 15, - 15о, цифроуйравляемые ре зисторы 16) - 16„, блоки 174 - 17„ формирования шага интерполирования с выходами 18-23, входящие в состав интерполирующих каналов 24 - 24, информационные входы 25, шину 26

377878

тактовьк импульсов, выходы 27, -27„, В каляом из интерполирующих каналов по информации об очередной координате функции и очередном интервале интерполяции осуществляется линейное интерполирование. По истечении очередного интервала соответствующий канал запрашивает и получает из блока памяти 2 очередную информацию. Каналы работают независимо друг от . друга. 2 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Интерполятор | 1986 |

|

SU1345217A1 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| Имитатор технологического объекта | 1980 |

|

SU924672A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Линейный интерполятор | 1988 |

|

SU1522157A1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2028665C1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки (ЭЛТ) | 1988 |

|

SU1509862A1 |

| СПОСОБ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА НА ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА РАКЕТЕ. ЛИНЕАРИЗАТОР СИГНАЛА. ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА. СПОСОБ ИНТЕГРИРОВАНИЯ ДЛЯ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2549231C1 |

Изобретение относится к вычислительной технике. Цель иэобретения- повьшение точности и автономности функционирования. Устройство содержит коммутатор-каналов 1, блок памяти 2, цифроаналоговый преобразователь 3, первые сумматоры 4/ - 4f, интерполирующих каналов, ключи 5,- 5„, 6, - бц, запоминающие элементы

1

Изобретение относится к вычисли- тельной технике и может быть использовано для визуализации информации, формирования управляющих сигналов и в качестве генератора функций.

Цель изобретения - повышение точности и автономности функционирования,

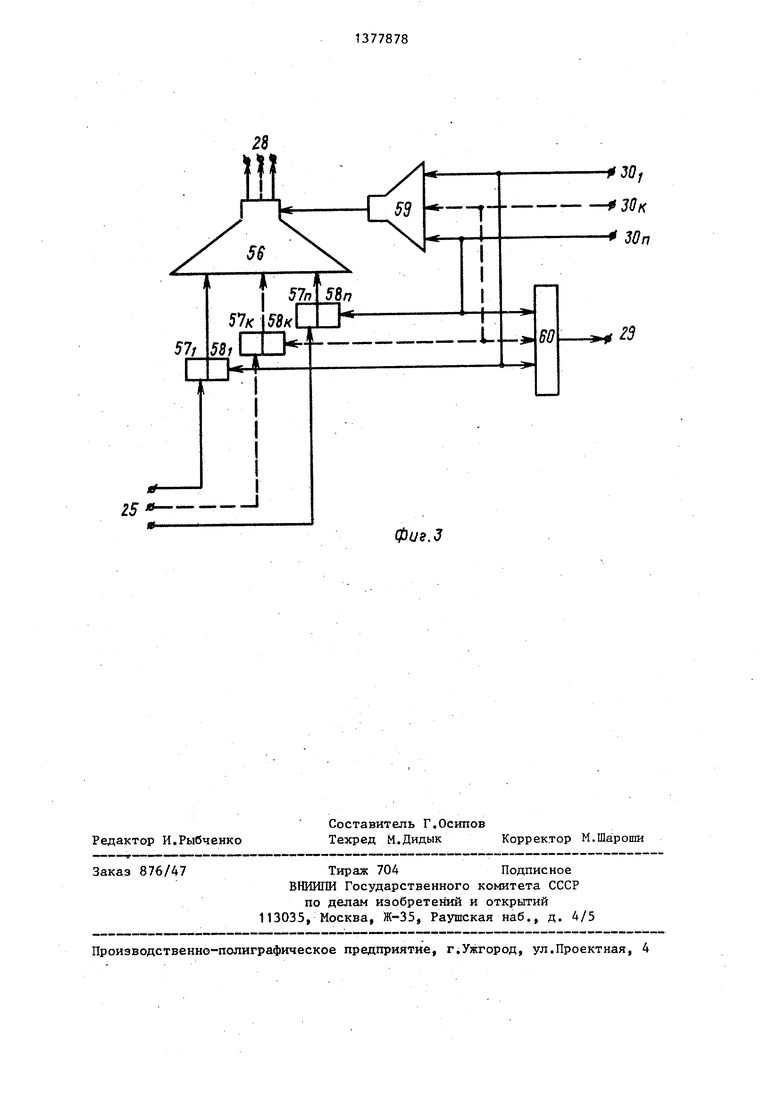

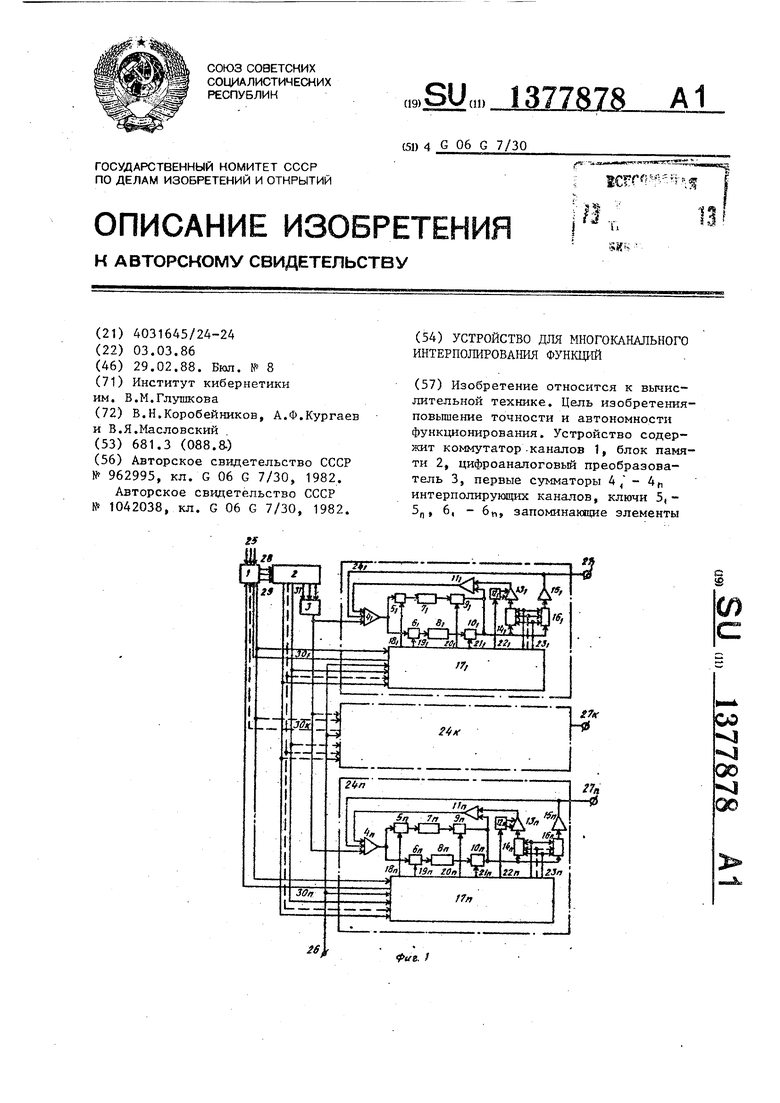

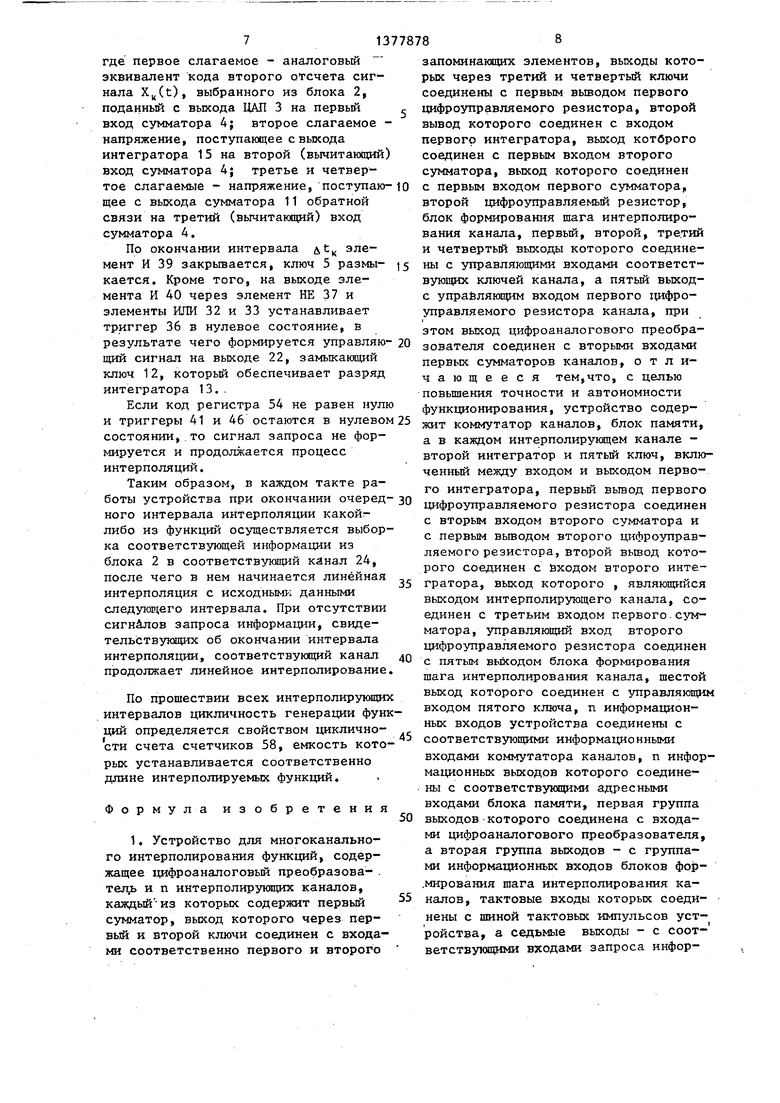

На фиг. 1 представлена схема устройства; на фиг. 2 - схема блока формирования шага интерполирования; на фиг, 3 - схема коммутатора каналов.

Устройство содержит коммутатор 1 каналов, блок памяти 2, цифроаналого- ,вый преобразователь (ЦАП) 3, первые сумматоры 4, ключи 5 и 6, запоминающие элементы 7 и 8, ключи 9 и 10, вторые сумматоры 11, ключи 12, пер- вые интеграторы 13, первые цифроупра- вляемые резисторы 14, вторые интеграторы 15, вторые цифроуправляемые резисторы 16, блоки 17 формирования шага интерполирования с выходами 18-23. Элементы 4-17 образуют интерполирующие каналы 24. Кроме того, устройство содержит информационные . входы 25, шину 26 тактовых импульсов, выходы 27, информационные выходы 28 блока синхронизации, синхронизирующий выход 29, входы 30 запроса информации коммутатора каналов, информационные выходы 31 блока памяти 2.

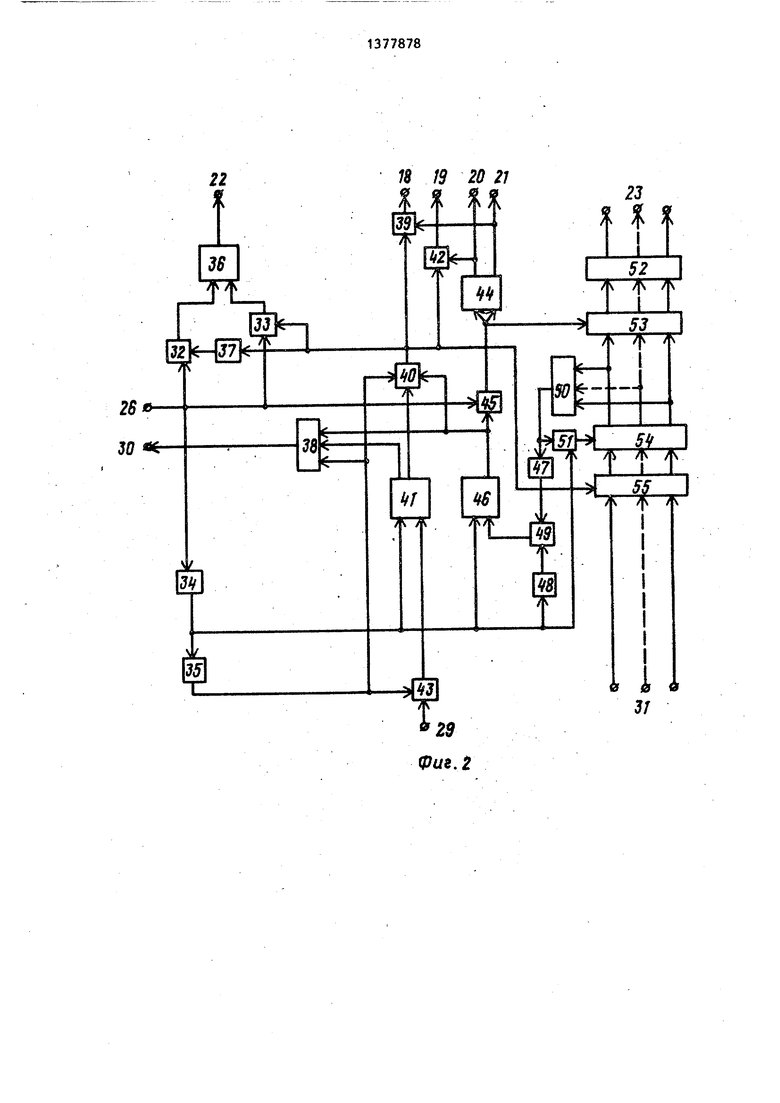

Блок 17 содержит элементы ИЛИ 32, 33, элементы 34 и 35 задержки, триггер 36, элемент НЕ 37, элементы И 38- 40, триггер 41, элементы И 42, 43, триггер 44. элемент И 45, триггер 46,

элементы НЕ 47,48, элемент И 49, элемент ИЛИ 50, элемент И 51, регист 52, блок 53 элементов И, счетчик 54, сблок 55 элементов И.

Коммутатор 1 каналов содержит мультиплексор 56, п регистров 57 адреса, п счетчиков 58, шифратор 59, формирователь 60 импульсов синхронизации.

Устройство работает следуклцим образом.

По исходным значениям ординат и абсцисс интервалов , где k - номер функции; i - номер интервала, хранящимся в блоке 2 памяти, в интерполирующих каналах 24 восстанавливаются функции времени X(t). Ординаты функций через ЦАП 3 поступают на . входы сумматоров 4, а абсциссы - на информационные входы блоков 17.

Период следования тактовых сигналов на шине 26 совпадает с длительностью минимального интервала интерполирования Т , а ut (длительность тактовых сигналов) совпадает с интервалом времени, вьщеляемым на обслуживание одного канала 24, причем .

Т /V t -г, где п - число каналов 24.

Переменный интервал интерполирования любой из цепочек 24 может изменяться только кратным . Каждый из параллельных каналов 24 формирует функцию времени независимо. Синхронизация их работы осуществляется только для узлов, участвующих в обмене информацией с блоком 2. Работу каждого из каналов можно представить в виде совокупности двух одновременных процессов: процесса вьщеления и запоминания приращения форт-шруемой функч ции и процесса интегрирования приращения.

Обслуживание каналов 2А выполняет- Р.Я циклически с периодом Т следования тактовых сигналов на шине 26 таким образом, что первый канал 24 обслуживается в течение интервала

времени &t, , второй -&t.

k-й j

ut|, ..., n-й - it, причем эти интервалы равны. Они один за другим, причем k-й канал 24 обслуживается в текущем интервале времени Т только в том случае, если вслед за его окончанием происходит изменение в этом канале шага интерполирования (ордината k-й функции при этом может как изменяться, так и остаться прежней), Если же текущий шаг интерполирования для k-ro канала 24 не оканчивается с окончанием данного интервала Т, а продолжается в последующем интервале Т, то соответствующий интервал времени it выдерживается без использования. Управление работой каждого из каналов 24 выполняет соответствующий блок 17.

Длительность задержки элемента 34 задержки составляет небольшую долю от длительности t и одинакова для всех блоков 17. Длительность задержки элемента 35 такова, что обеспечивает форм1-фование на его вьгходе сигнала, сдвинутого относительно сигнала на шине 26 для блока 17 первого канала на величину t, для блока 17 k-ro канала - на величину k -ut, для блока 17 п-го канала - на величину .

В начальном состоянии регистры 52, счетчики 54, триггеры 36,41, 44 и 46 блоков 17 установлены в нуль, в запоминающих элементах 7 и 8 - нулевые значения приращения функций, а на выходе ЦАП 3 и выходах 27- нулевые напряжения. Замкнуты ключи 9 и 12. С входов 25 в регистры 57 коммутатора 1 записываются начальные коды адресов массивов координат генерируемых функций. Первый тактовый сигнал с шины 26, поступая через элементы ИШ1 32 и 33 одновременно на входы триггера 36, устанавливает триггеры 36 всех каналов в единичное срстоя ние; триггеры 36 своими выход

5

0

5

0

5

0

5

0

5

ными сигналами раз 1ыкают ключи 12. Этот же тактовый сигнал устанавливает в нуль триггеры 41 и 46. После окончания сигнала на выходе элемента 34 он через элемент НЕ 48 вместе с единичным сигналом на вькоде элемента НЕ 47 открывает элемент И 49 и устанавливает триггеры 46 в единичное состояние. I

По окончании тактового сигнала на

выходе элемента 35 формируется сигнал длительностью ДЬ, которьй проходит через элемент И 38 и формирует на входе 30 блока 17 первого канала сигнал запроса информации. Этот сиг- 1нал, поступая на соответствуюпщй вход коммутатора 1, увеличивает на единицу содержимое соответствующего

счетчика 58, через шифратор 59 подключает через мультихтлексор 56 выхо ды соответствующего регистра 57 и счетчика 58 к информационным выходам 28 коммутатора 1. Информация с выходов 28 определяет формирование и выдачу на выходы блока 2 цифровых кодов ординаты и абсциссы (X , , и Т ) первого значения функции X.(t), Эти коды удерживаются на первых и вторых выходах блока 2 до подачи с выходов 28 коммутатора 1 новой информации. Одновременно коммутатор 1 в ответ на сигнал запроса информации формирует на выходе 29 формирователя 60 синхросигнал, который в блоке 17 первого канала 24 вместе с сигналом на выходе элемента 35 задержки открывает элемент И 43, сигнал с выхода которого устанавливает триггер 41 в единичное состояние. При этом снимается сигнал запроса информации с выхода 30 и открьшается элемент И 40. Сигнал с выхода элемента И 40 открывает блок 55 элементов И, через кото- рьш код значения Т, записьтается в счетчик 54, и вместе с нулевым сигналом триггера 44 открьгоает элемент И 42, формируя сигнал на выхо де,19, который замыкает ключ 6. Замкнутый ключ 6 подключает выход сумматора 4 к входу запоминающего элемента 8, в котором запоминается прираще- кие напряжения Ь X . С окончанием сигнала на выходе элемента 35 размыкается ключ 6, триггер 36 устанавливается в нулевое состояние, на выходе 22 появляется сигнал, замыкающий ключ 12 первого канала. Замкну513

тьй ключ 12 обеспечивает разряд интегратора 13.

Аналогичным образом из блока 2 выбираются коды координат функции Xj(t) Этот процесс для второго канала 24 выполняется в течение интервала времени &t , сдвинутого относительно начала первого тактового сигнала на величину 2 &t. Точно также в тече- Ш1е интервала времени ut, сдвинутого относительно начала первого тактового сигнала на величину п . bt, запоминается приращение ординаты и X

П, 1

и

шага интерполирования Т„ , .

Интервал вре.мени ., выдерживается без использования и необходим для разряда интегрирующего конденсатора интегратора 13 последнего канала .

Таким образом, перед приходом второго тактового сигнала на щину 26 в блоках 17 триггеры 36 и 44 находятся в нулевом состоянии, а триггеры 41 и 46 - в единичном состоянии.

Второй тактовый сигнал, поступая через элементы ИЛИ 32 и 33 на входы триггеров 36 всех блоков 17, устанавливает их передним фронтом в единичное состояние - с выходов 22 снимает ся управляющий сигнал, что приводит к размыканию ключей 12 всех цепочек 24. Одновременно этот же сигнал проходит через элементы И 45, открытые единичными импульсами триггеров 46, разрешает запись через блоки 53 кодов счетчиков 54 в регистры 52 и переводит триггеры 44 в единичное состояние. В результатов снимается разрешающий сигнал с выходов 20, устанавливается разрешающий сигнал на выходах 21, а на выходах 23 соответствующих каналов 24 устанавливаются коды шага интерполирования. Замыкаются ключи 10, код вькодов 23 блока 17 устанавливает соответствующие значения цифровых управляемых резисторов 14 и 16, определяющие постоянные времени интегрирования в каналах от Т,, до Т, . Интеграто- ры 13 и 15 в течение второго цикла интервала времени Т интегрируют приращение функции, запомненное на пре- дьздущем интервале времени, так как в первом канале формируется выход-

ное напряжение X,(t) ЛХ,, ;;;-.

(,1

которое в конце второго цикла достигает величины Х,, ; в п-ом канале

.ю Xn(t)

йХ

пи

, которое до П.1

X

стигает значения Х, в конце третьего цикла, а также формируется напряжение обратной связи на выходах сумматоров 11: на первом канале X,, (t)

t ---, в п-м кана t

- йХ,

ЛХ,,, ле X(t)

- ЛХ

,

ЛХп,,

15

20

25

3050 55

П,1 т п,ч

Одновременно с процессом интегрирования запоминаются приращения сигналов в соответствующем запоминающем элементе. Второй тактовый сигнал устанавливает триггеры 41 и 46 в нулевое состояние и вычитает единицу из кодов счетчиков 54. В случае обнуления счетчика 54 k-ro канала элемент И 48 в соответствующем канале открьтается и устанавливает триггер 46 в единичное состояние. В результате на выходе 30 формируется сигнал запроса информации. Этот сигнал в блоке 1 увеличивает содержимое соответствующего счетчика 58 и, управляя через шифратор 59 мультиплексором 56, подключает выходы соответствующих регистра 57 и счетчика 58 к выходам 28 блока 1. Код выходов 28 определяет выборку из блока 2

координат X

К,1

и т

к,7

второ00 5

го значения функции. Одновременно формирователь 60 ввдает на выход 29 синхросигнал, который вместе с сигна5 шом на выходе схемы 35 задержки от- крьгоает элемент И 43 и устанавливает триггер 41 в единичное состояние.Тем самь1М снимается сигнал запроса информации. Единичные состояние триггеров

41 и 46 и сигнал с выхода схемы 35

открывает элемент И 40. Сигнал с вы- хода элемента И 40 открывает блок 55, разрешая прием в регистр 54 с выходов 31 блока 2 кода второго шага ин5 терполирования Т , и, пройдя через элемент И 39, открытый единичным сигналом триггера 44, формирует управляющий сигнал, которьй замыкает ключ 5. Замкнутый ключ 5 подключает выход сумматора 4 к входу запоминаккдего элемента 7, в котором запоминается приращение X,j X | - Х, функции X(t) - результат суммирования в сумматоре 4 его входных сигналов:

t

Х - U X.

кд

X

к л ЬХ

U X к и

t к,( т

К,1

где первое слагаемое - аналоговый эквивалент кода второго отсчета сигнала X(t), выбранного из блока 2, поданный с выхода ЦАП 3 на первьй вход сумматора 4; второе слагаемое - напряжение, поступающее с выхода интегратора 15 на второй (вычитанхций) вход сумматора 4; третье и четвертое слагаемые - напряжение, поступающее с выхода сумматора 11 обратной связи на третий (вычитающий) вход сумматора А.

По окончании интервала t элемент И 39 закрьшается, ключ 5 размы- кается. Кроме того, на выходе элемента И 40 через элемент НЕ 37 и элементы ИЛИ 32 и 33 устанавливает триггер 36 в нулевое состояние, в результате чего формируется управляю- щий сигнал на выходе 22, замыкакядий ключ 12, который обеспечивает разряд интегратора 13, .

Если код регистра 54 не равен нулю и триггеры 41 и 46 остаются в нулевом состоянии,.то сигнал запроса не формируется и продолжается процесс интерполяций.

Таким образом, в каждом такте работы устройства при окончании очеред- ного интервала интерполяции какой- либо из функций осуществляется выборка соответствующей информации из блока 2 в соответствующий кйнал 24, после чего в нем начинается линейная интерполяция с исходнымк данными следующего интервала. При отсутствии сигналов запроса информах и, свидетельствующих об окончании интервала интерполяции, соответствующий канал продолжает линейное интерполирование

По прошествии всех интерполирующих интервалов цикличность генерации функций определяется свойством циклично- сти счета счетчиков 58, емкость которых устанавливается соответственно длине интерполируемых функций.

Формула изобретения

о

5 0

5

о о

5

0

5

запоминающих элементов, выходы которых через третий и четвертый ключи соединены с первым вьтодом первого цифроуправляемого резистора, второй вывод которого соединен с входом первого интегратора, выход которого соединен с первым входом второго сумматора, выход которого соединен с первым входом первого сумматора, второй цифроуправляемый резистор, блок формирования шага интерполирования канала, первый, второй, третий и четвертый выходы которого соединены с управляющими входами соответствующих ключей канала, а пятый выход- с упраблякщим входом первого цифроуправляемого резистора канала, при этом выход цифроаналогового преобразователя соединен с вторыми входами первых сумматоров каналов, отличающееся тем,что, с целью повышения точности и автономности функционирования, устройство содержит коммутатор каналов, блок памяти, а в каждом интерполирукщем канале - второй интегратор и пятый ключ, включенный между входом и выходом первого интегратора, первый вьгаод первого цифроуправляемого резистора соединен с вторым входом второго сумматора и с первым вьгоодом второго цифроуправляемого резистора, второй вьшод которого соединен с входом второго интегратора, выход которого , являющийся выходом интерполирующего канала, соединен с третьим входом первого.сумматора, управлякшщй вход второго цифроуправляемого резистора соединен с пятым вькодом блока формирования шага интерполирования канала, шестой выход которого соединен с управляющим входом пятого ключа, п информационных входов устройства соединены с соответствующими информационными входами коммутатора каналов, п информационных выходов которого соединены с соответствующими адресными входами блока памяти, первая группа выходовкоторого соединена с входами цифроаналогового преобразователя, а вторая группа выходов - с группами информационных входов блоков фор- .мирования шага интерполирования каналов, тактовые входы которых соединены с шиной тактовых импульсов устройства, а седыфш выходы - с соответствующими входами запроса инфор

мации коммутатора каналов, синхрони зирукнций выход которого соединен с входами синхронизации блоков формирования шага интерполирования каналов ,

элемента И, а нулевой выход подклю

чен к третьему входу пятого элемента И, выход которого является седьмым выходом блока, выход первого элемента И соединен с управлякяцим входом второго- блока элементов И с со счетным входом третьего триггера, выходы которого являются третьим и четвертым выходами блока и соединены с первыми входами соответственно седьмого и восьмого элементов И, выходы которых являются вторым и первым выходами блока, а вторые входы седьмого и восьмого элементов И соединены с вторым входом второго эле

мента ИЛИ, с входом третьего элемен- ,та НЕ и с управляющим входом первого блока элементов И и подключены к выхо- |ДУ третьего элемента И, выход третьего элемента НЕ соединен с вторым входом первого элемента ИЛИ,выход которого подключен к входу синхронизации четвертого триггера, информационньй вход которого соединен с вьссрдом второго элемента ИЛИ, а нулевой выход является шестым выходом блока. 3. Устройство по П.1, отличающееся тем, что коммутатор каналов содержит мультиплексор, шифратор, формирователь импульсов синхронизации, п регистров адреса и п счетчиков, при этом входы регистров адреса являются информационными входами коммутатора, а входы запроса информации соединены с со- ответствукщими входами шифратора и формирователя импульсов синхронизации, а также с входами соответствующих счетчиков, вькод шифратора соединен с управляющим входом мультиплексора, информационные входы которого подключены к выходам регистров адреса и счетчиков адреса, а выходы мультиплексора являются информационными выходами коммутатора каналов, выход формирователя импульсов синхронизации является синхронизирующим выходом коммутатора каналов.

2В

30

18 19 20 21

23 f

I . S2 1

A

53

IfL

f 7 t

J/

Фиг.З

| Генератор функций | 1980 |

|

SU962995A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Линейный интерполятор | 1982 |

|

SU1042038A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-28—Публикация

1986-03-03—Подача