Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах чисг левого программного управления (ЧПУ) станками.

Известно устройство для програм- . много управления, содержащее блок Зсшания скорости, импульсный датчик и по каждой координате счетчик импульсов и последовательно соединенные счетчик, блок ключей и сумматор, выход которого подключен к управляющему входу другой координаты 1.

Недостатком такого устройства явлйется то, что изменения величин приращения при линейной интерполяции и величин радиуса при круговой интерполяции приходится учитывать при задании скорости в блоке задания скорости подачи. При этом в случае малых величин приращений и большой разрядности интерполяторов устройство должно работать на частотах, превышающих в 2-К раз заданную выходную частоту (К - число нулевых разрядов интерполятора, следуюишх за старшим значащим разрядом). При числе двоичных разрядов ,,что приблизительно соответствует десятичной величине Ю, число К может

достигать 23, т.е. частота работы интегратора.должна в 2 раз превышать выходную частоту устройства.

ПерехЪд систем ЧПУ на работу с ценой отсчета (импульса) 0,001 мм-с одновременным повышением выходной частоты до 200000 - 500000 Гц делает прямое использование такого известного решения невозможным, так как/

10 в этом случае тактовая частота должна была бы составить (200000-500000) , что обеспечить невозможно.

Известны устройства, позволяющие снизить тактовую частоту интерполя15торов, работающих по принципу цифрового дифференциального ансшизатора (ЦДА). Так, в одном из них используется задаваемое в программе кодирование множителя, который открыва20ет ключ переноса со старшего значаtuefo разряда 2 .

Однако известное устройство сильно усложняет программирование, так как возникает необходимость расчета

25 и задания в программе соответствующего множителя, что особенно усложняется при работе в двоичном коде и, кроме того, требует значительного объема электронного оборудования t

30 ключи отбора, сборки выходов, опер тивная и промежуточная память множи телей. KIоме того, в режиме кругово интерполяции такое решение не всегд приемлемо, так как значения подинтег ральной функции в этом режиме меняются и предварительно рассчитанные соотношения, заданные в программе, могут быть нарушены. Известное устройство с интерполя ризаторами с автоматическим выделением переноса из старшего значащего разряда благодаря использованию схе мы определения ста1дшего значащего разряда приращений, включеиощей пв ренос из соответствующих разрядов / с одновременной блокировкой ключей переноса всех маадших разрядов интеграторов всех координат интерполятора 3 . Недостатком данного решения является его высокая сложность, приводящая к возрастанию объемов электронного оборудования в показатель.ной степени при возрастании числа одновременно работающих координат и числа разрядов интегратора и пониженное быстродействие из-за возникновения больших задержек в громоздкой комбинационной логике, причем объем электронного оборудования этих схем может значительно превышать объем основного оборудования интеграторов. Известно также устройство, основанное на последовательном запоминании всех переносов, врзникающих при суммировании значений подынтегральной функции в ЦДА каждой коорди наты с последующим сбросом каждого заполненного переноса любой единице более старшего разряда подынтеграль ной функции и стробированием состоя ния триггеров запоминания переноса последним тактом импульсов управления поразрядным сложением 4. Однако указанное устройство, обл дая функциональной полнотой и простотой технической реализации, может быть применено только в ЦДЛ последо вательного действия. Но на ЦДА посл .довательного действия невозможно построить интерполяторы с быстродей ствием более 45-50 кГц при числе дв ичных разрядов 24. Следовательно, в перспективных разработках это техни ческое решение использовано быть не может. Наиболее близким техническим решением к предлагаемому, является ре шение, основанное на одновременной нормализации величин подынтегрально функции il в цепи обратной связи кр гового интерполятора, построенного на ЦДА. Устройство содержит генератор тактовой частоты, к выходу кото рого подключен управляющим входом первый ключ, информационный вход ко торого подключен к выходу элемента И через первый элемент НЕ, и по каждой координате первый блок ключей и последовательно соединенный второй блок ключей, первый накапливающий сумматор и счетчик, выход которого подключен к соответствующему входу элемента И, а управляющие входы вторых блоков ключей каждой координаты соединены с выходом первого ключа. Кроме того, устройство содержит блок переключения режимов, генератор импульсов, последовательно соединенные элемент ИЛИ, второй элемент НЕ и второй ключ, а по каждой координате - первый регистр сдвига и последовательно соединенные второй регистр сдвига, третий блок ключей и второй накапливающий сумматор, подключенный выходом - к информационному входу второго блока ключей данной координаты, причем в каждой.координате выход первого блока ключей соединен с входом второго накапливающего сумматора, информационный вход - с выходом блока переключения режимов через первый регистр сдвига данной координаты, а управляющий вход - с выходом первого накапливающего сумматора другой координаты, управляющий вход второго ключа подсоединен к выходу генератора импульсов, выход - к управляющим входам первого и второго регистров сдвига каждой координаты, а входы элемента ИЛИ - к выходам вторых регистров сдвига каждой координаты. Причем элементы - первый генератор, первый ключ, первый элемент НЕ совместно с элементом И - предсгавляют собой блок задания скорости, счетчики часть схемы центрального управления, а именно схему определения окончания отработки перемещения. Элемент ИЛИ, второй элемент НЕ , второй ключ, генератор и блок переключения режимов обобщенно представляют собой коммутатор сигналов обратной связи 5. , Недостатком известного устройства является то, что в процессе отработки окружности возможно уменьшение быстродействия в два раза, так как не исключен случай, при котором в процессе отработки дуги окружности исчезнут единицы в старших значащих разрядах регистров (реверсивных счетчиков) подынтегральныхфункций. Кроме того, не исключена Jc:итyaция переполнения счетчика подынтегральной функции, считающей сигналы обратной связи в плюс, что может привести ю. искажению траектории. Цель изобретения - повышение точности и быстродействия устройства с круговым интерполятором, построенным на ЦДА. Поставленная цель достигается тем, что в устройство для двухкоординатного програ Ф1Ного управления, содержащее коммутатор, последовательно соединенные блок центрального управления,- блок ввода програ 1мы, блок задания скорости, блок формирования выходных сигналов и блок управления координатными приводами, н дпя каждой координаты - последовательно соединенные регистр сдвига, реверсивный счетчик, комбинационный сумматор и буферный регистр, второй и третий выходы блока ввода программы подключены к соответствующим вторым входам

блока формирования выходных сигналов, второй выход которого подключен к второму входу блока задания скорости, третий выход блока ввода прогрг ммы подсоединен к первому, входу блока центрального управления, а третий вход - к второму входу блока центрального управления и к выходу блока задания скорости, четвертый и пятый выходы блока ввода программы подключены к третьему и четвертому входам блока центрального управления соответственно, шестой и седьмой выходыК. первому входу регистра сдвига соответствующей координаты, а восьмой выход - к первому входу коммутатора, управляющий вход реверсивного счетчика каждой координаты подключен к соОтветствук)щему выходу коммутатора, второй информа1ционный выход блока центрального управления подсоединен к счетному входу реверсивного счетчика каждой координаты, причем для каждой координаты выходы каждого разряда буферного регистра подключены к вторым входам соответствующих

разрядов комбинационного сумматора данной координаты, введенц блок управления нормализацией, первый и второй элементы ИЛИ и для каждой координаты - элемент НЕ, пять элементов И и третий элемент ИЛИ, девятый, десятый и одиннадцатый выходы блока ввода программы соединены соответственно с первым, вторым и третьим входами блока управления нормализацией, первый выход, которого подключен к вторсялу входу регистра сдвига каждой координаты и к второму входу коммутатора, а второй выход - к пятому входу блока центрального управления, шестой и седьмой входы которого соединены с четвертым и пятым входами блока формирования выходных сигналов соответственно, с третьим и четвертым входами коммутатора соответственно и с выходами третьих элементов ИЛИ первой и второй координат соответственно, выход первого элемента ИЛИ подклйчен к первым входам первых элементов И обеих координат и к входу элемента НЕ первой координаты, выход второго элемента ИЛИ соединен с первым входом первогр элемента ИЛИ, с первьом входом второго элемента И каждой координаты и с входом элемента НЕ второй KO-J :ординаты, подключенного выхрдом к первому входу третьего элемента И обеих координат, выход элемента НЕ первой координаты соединен с вторыми входами вторых и третьих элементов И обеих координат, вторые и третьи входы первого элемента ИЛИ соединены соответственно с выходом ч-го разряда буферного регистра каждой

0 координаты и с выходом п-го разряда реверсивного счетчика каждой координаты, а четвертый вход. - с третьим выходом блока ввода программы, первые и вторые входы второго элемента

5 ИЛИ соединены соответственно с выходом (п-1}-го разряда буферного регистра каждой координаты и с выходом (n-l)-ro разряда реверсивного счетчика каждой координаты, двенадцатый

0 выход блока ввода прогргьммы подключен к четвертому входу блока управления нормализацией, кроме того, для каждой координаты выход (n-l)-ro разряда комбинационного сумматора соединен с вторым входом первого и с

5 третьим входом третьего элементов И данной координаты, выход п-го разряда - с первым входом четвертого и третьим входом второго элемента И данной координаты, а выход переноса 0 с первым входом пятого элемента И данной координаты, подключенного вторым входом к вторсму входу четвертого элейента И и к выходу первого элемента ИЛИ, третьим входом - к управляющему входу буферного регистра

и к четвертым входам второго и третьего элементов И данной координаты и. к соответствующему тактовому выходу блока центрального управления, а

0 выходом - к первому входу третьего -элемента ИЛИ данной координаты, второй и Третий входы которого соединены с выходами второго и третьего элементов И той же координаты, выходы первого и четвертого элементов И каждой координаты соединены с входами соответственно (n-l)-ro и .п-го разрядов буферного регистра Сданной коордщнаты, а выходы (n-l)-ro

n И п-ГО разрядов регистра сдвига

каждой координаты подключены к пятым и шестым входам блока управления нормализацией.

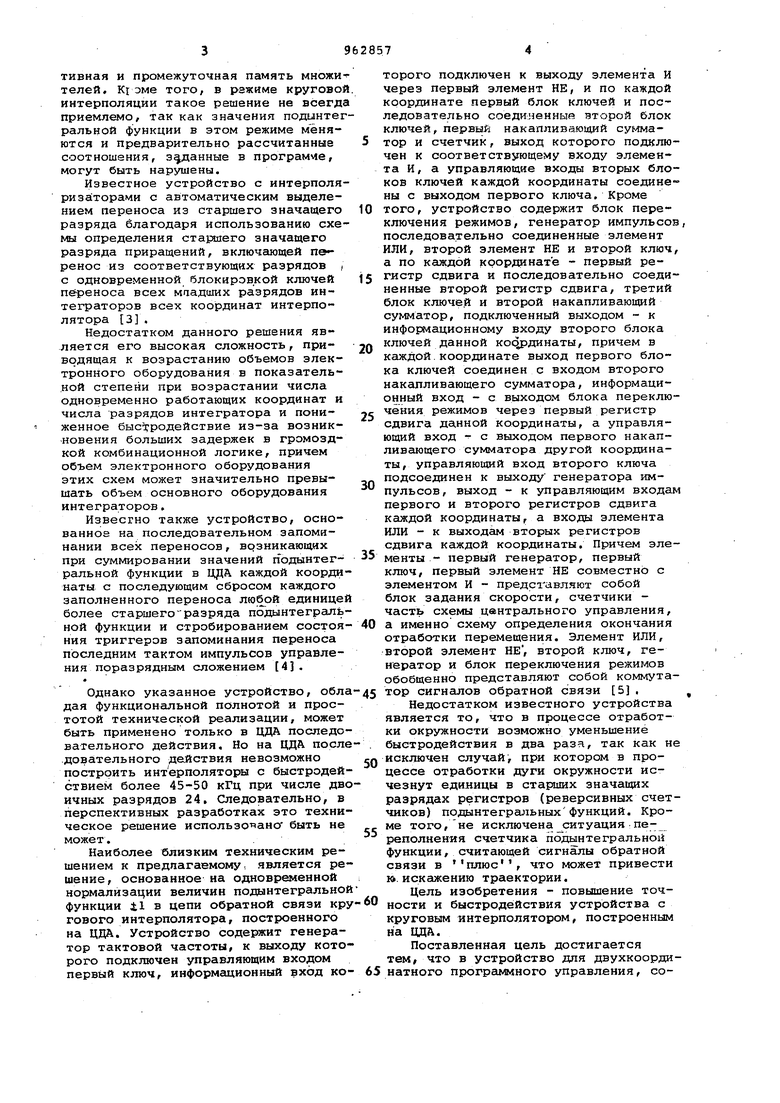

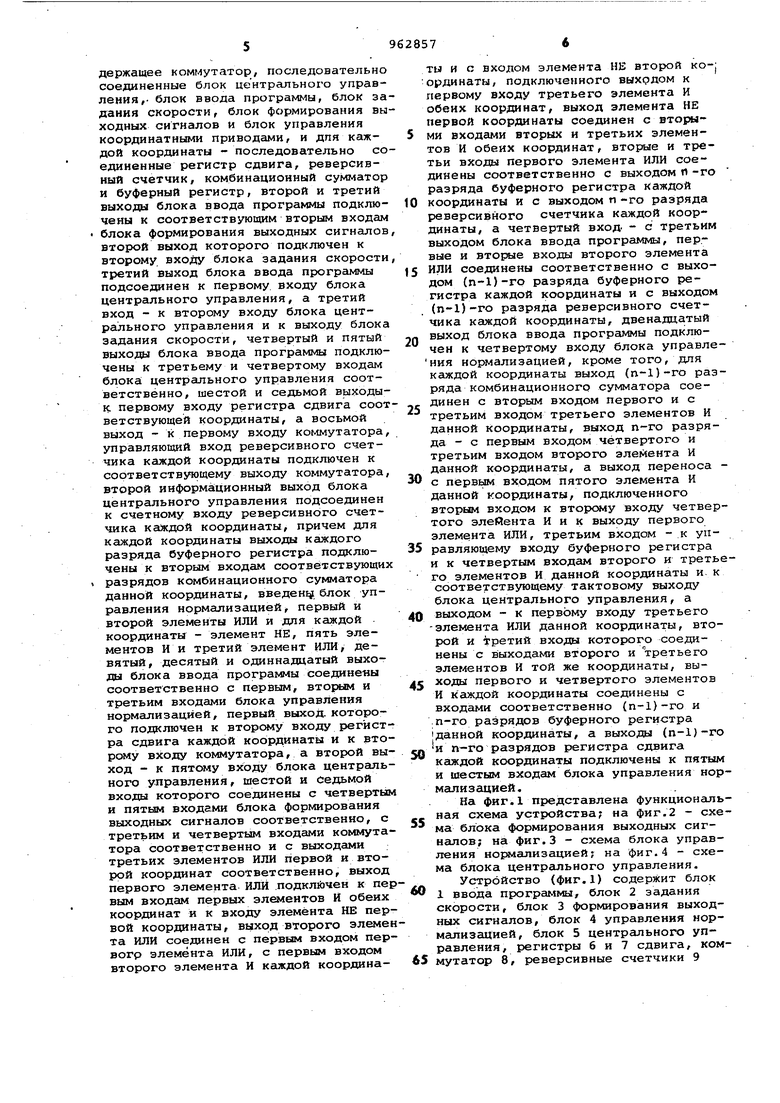

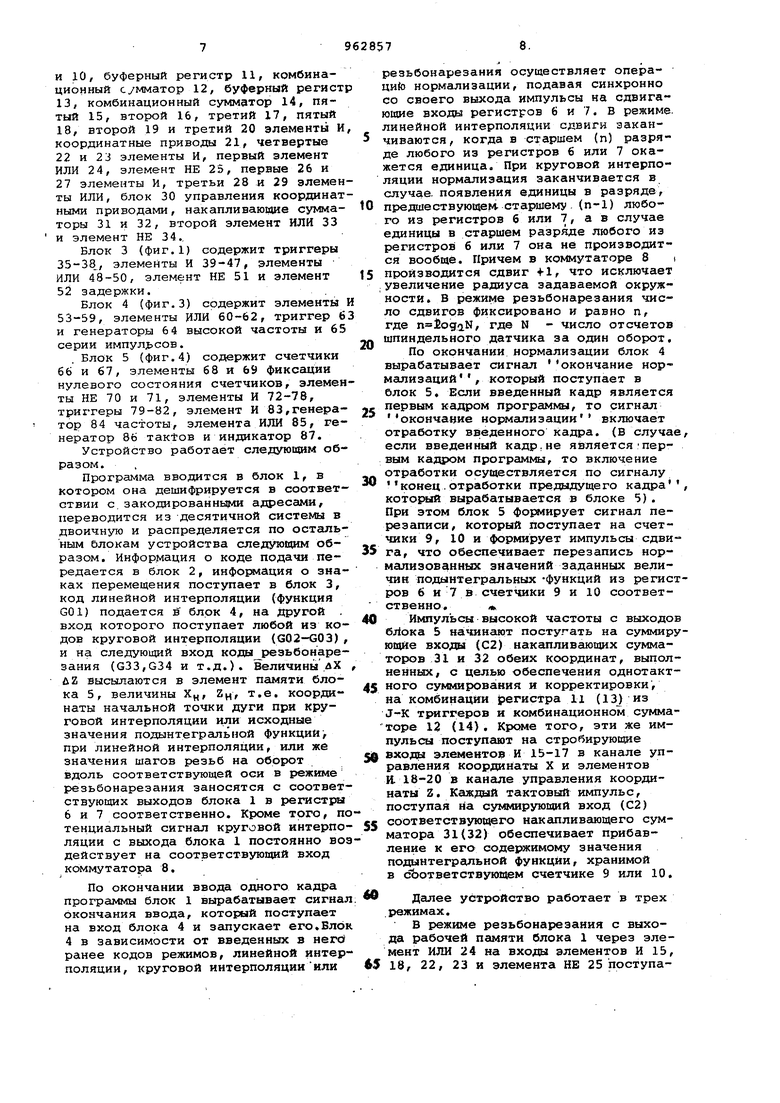

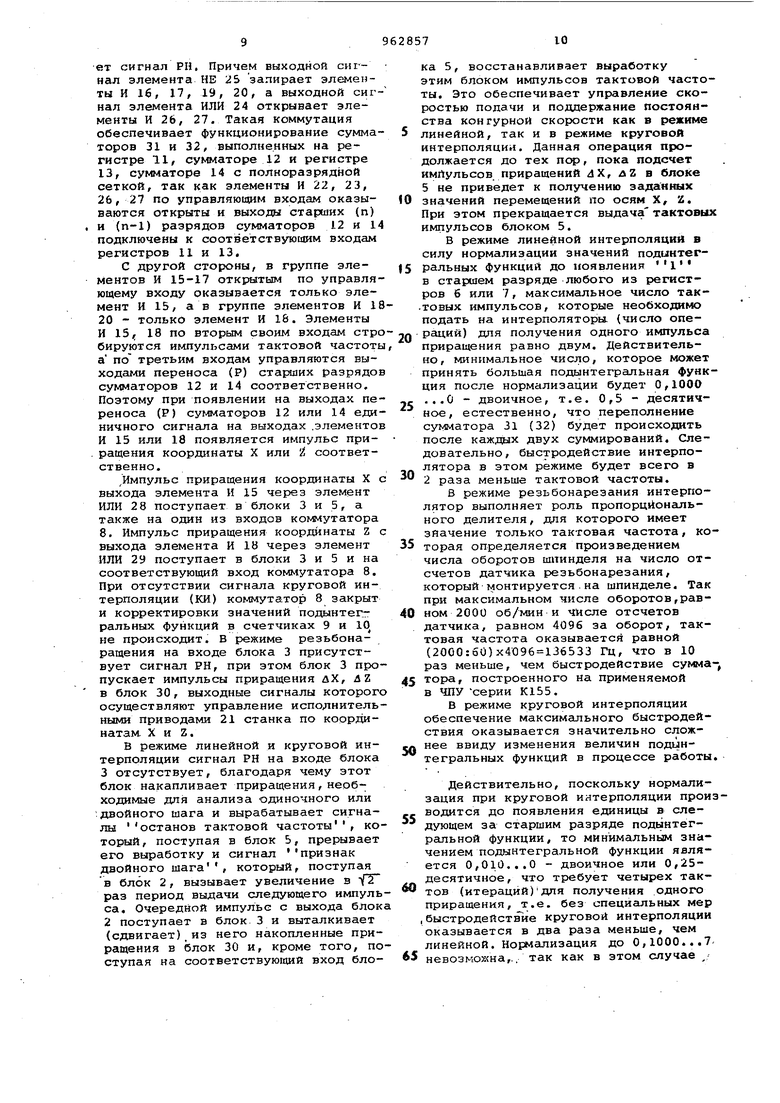

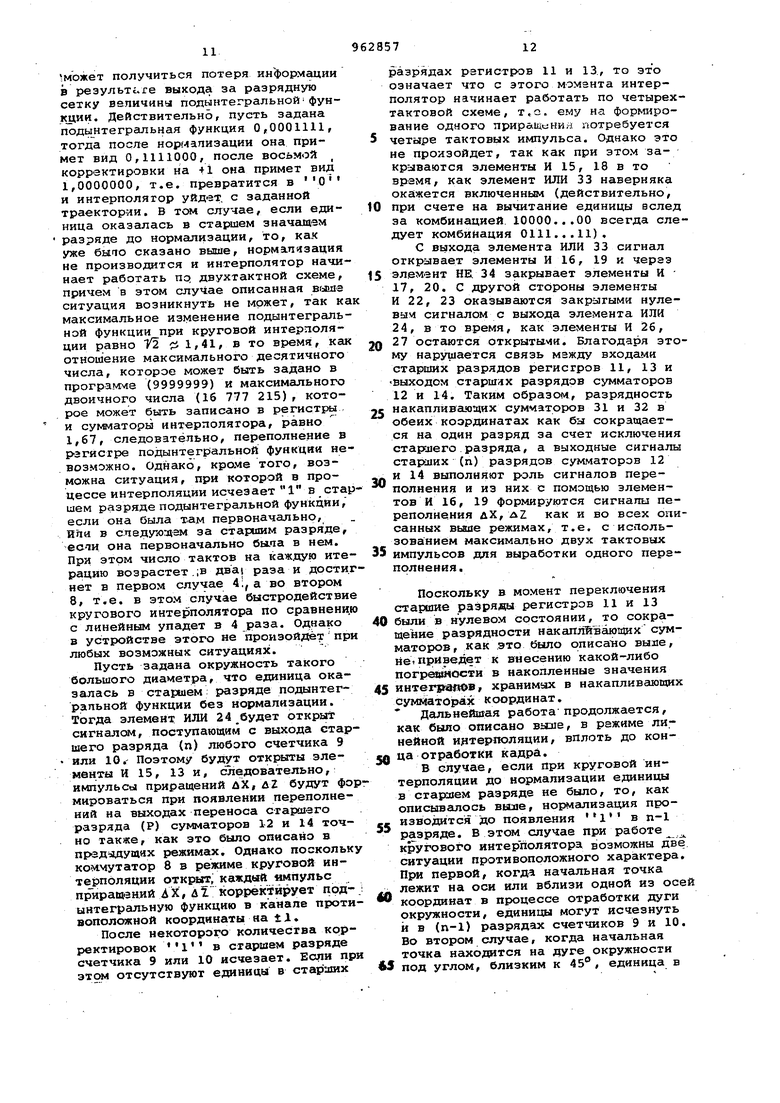

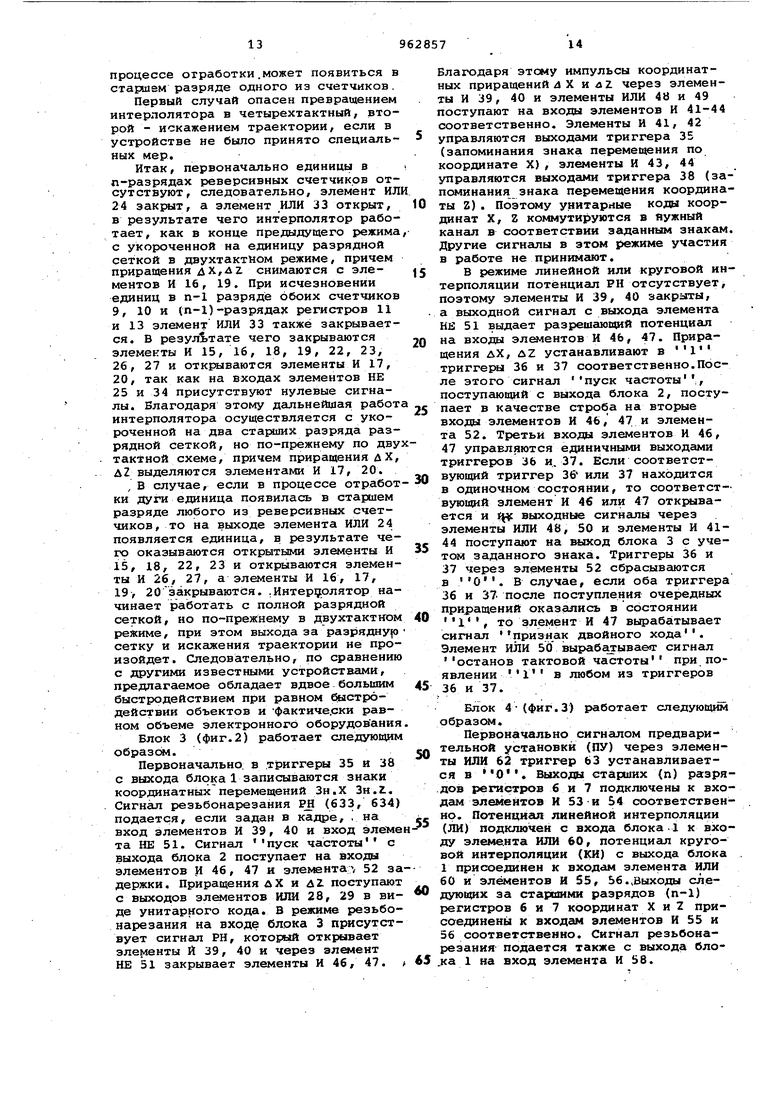

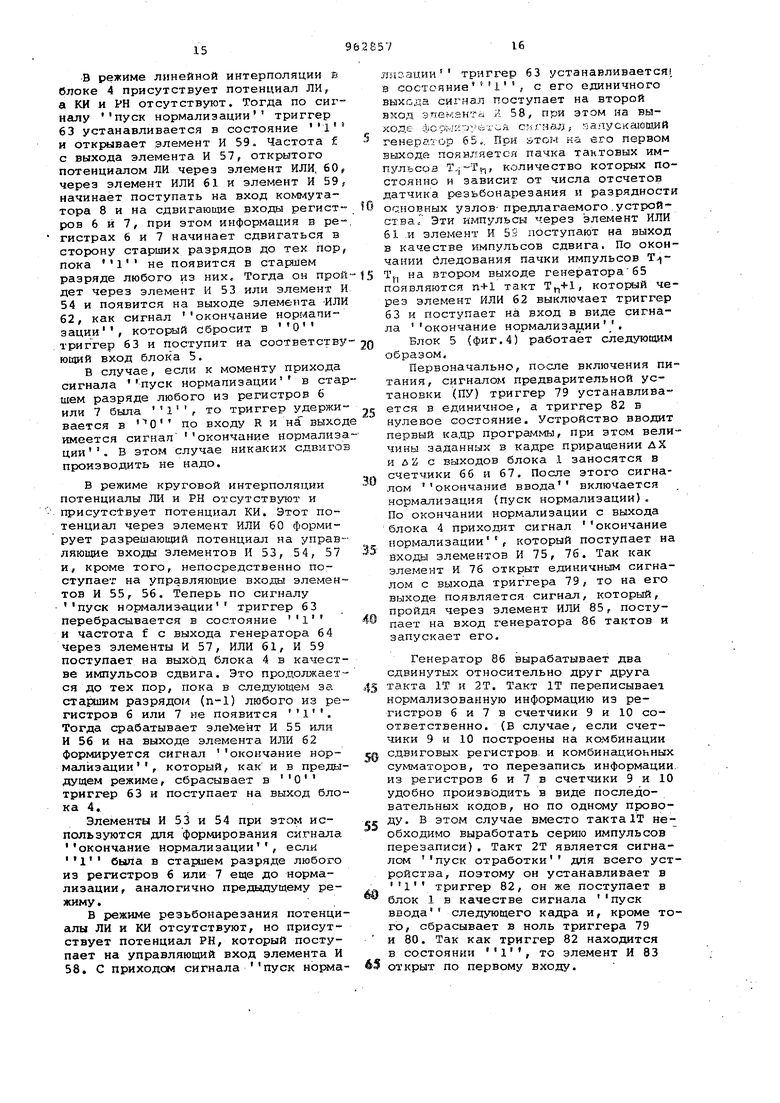

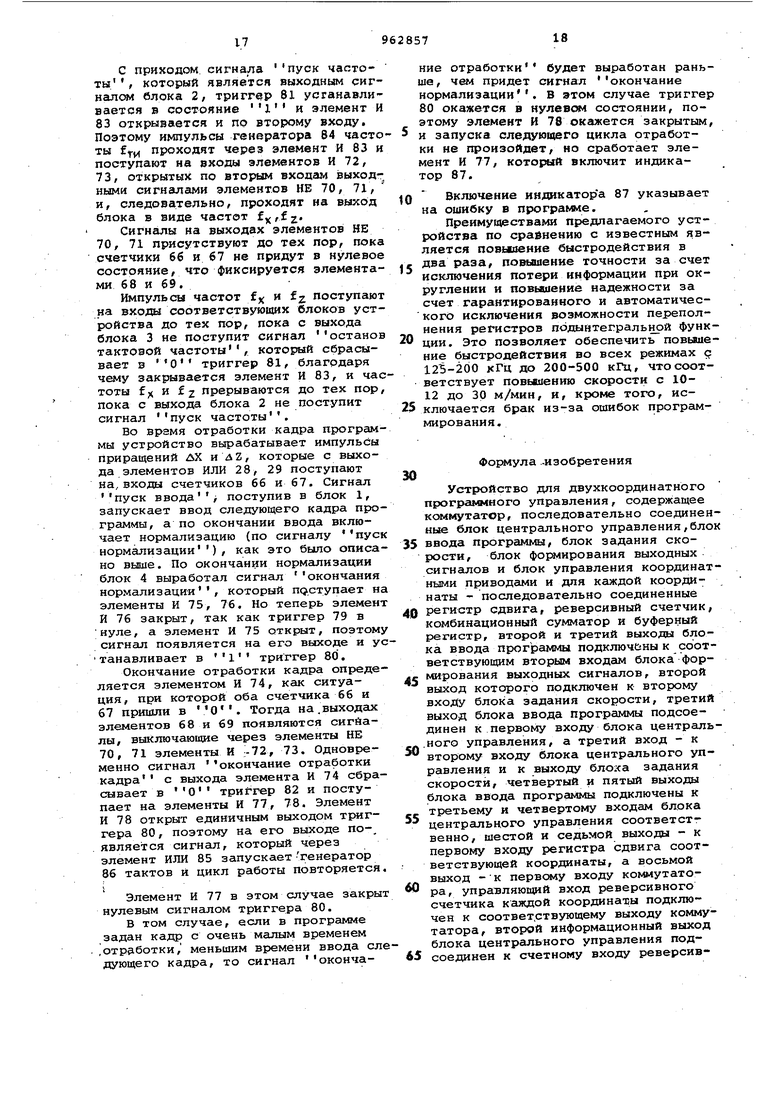

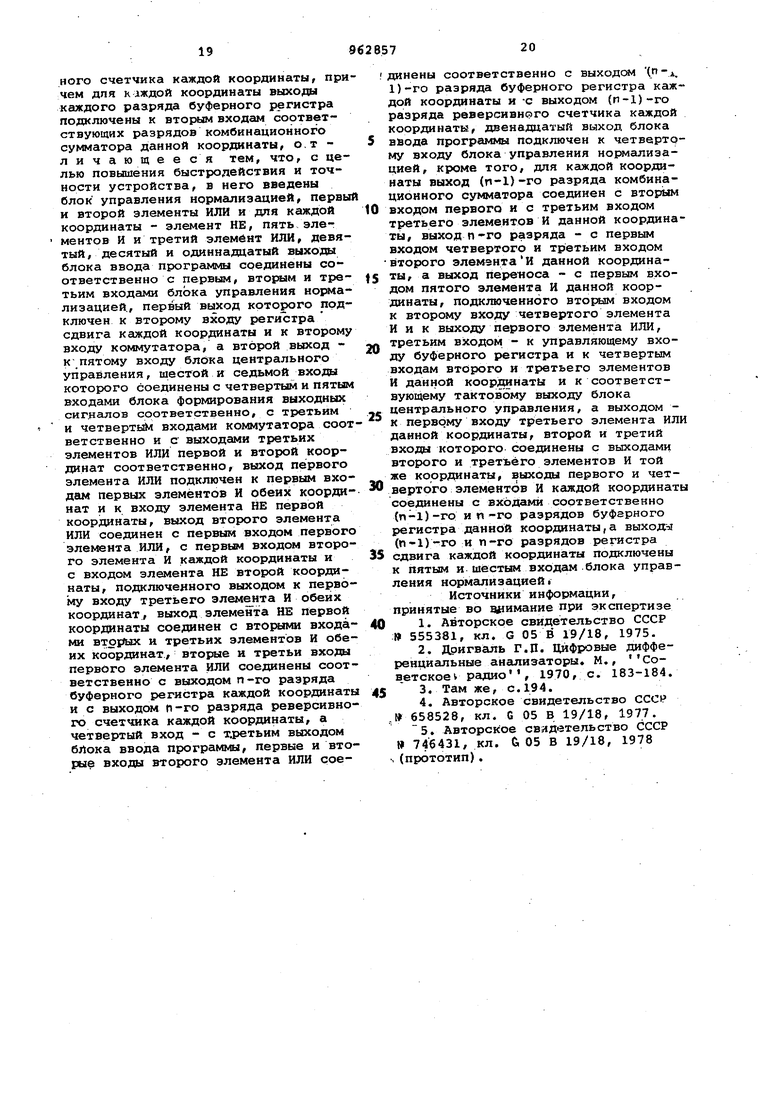

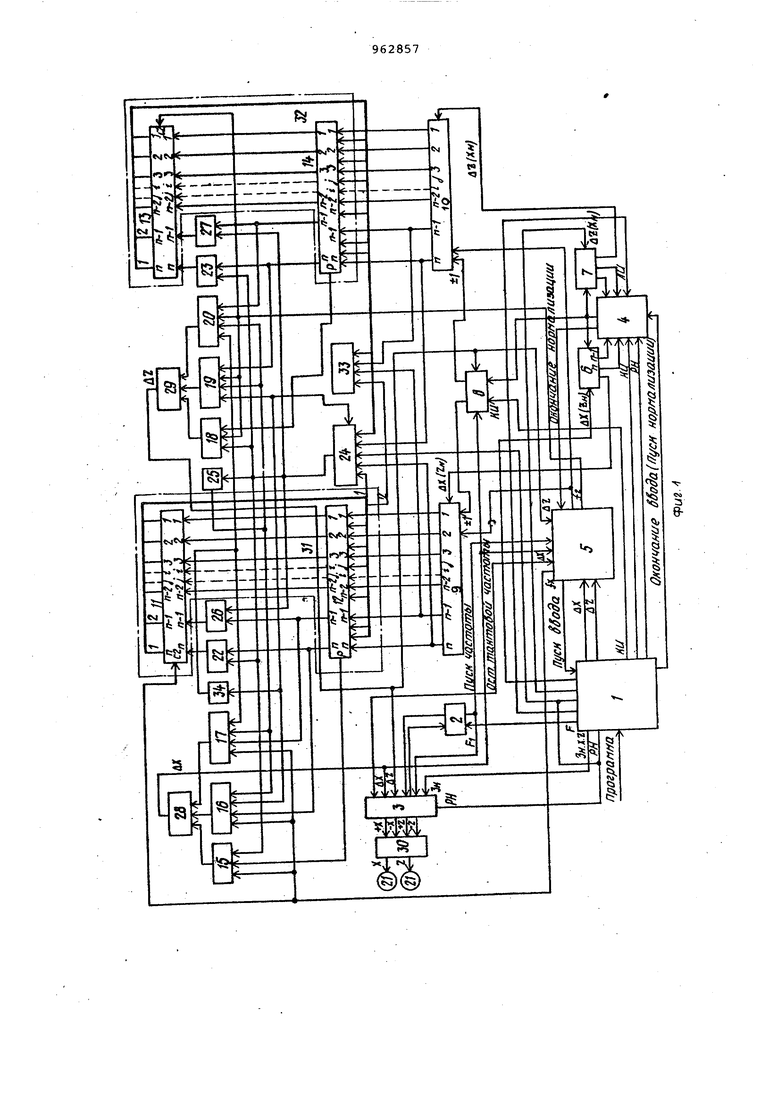

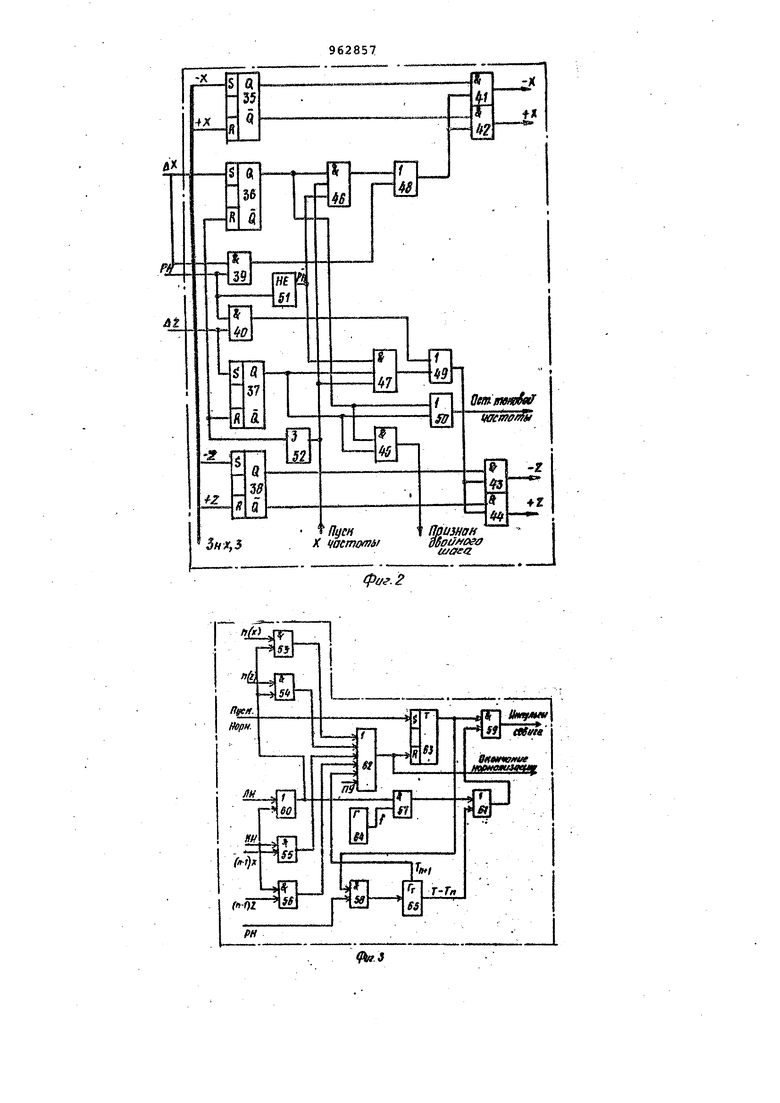

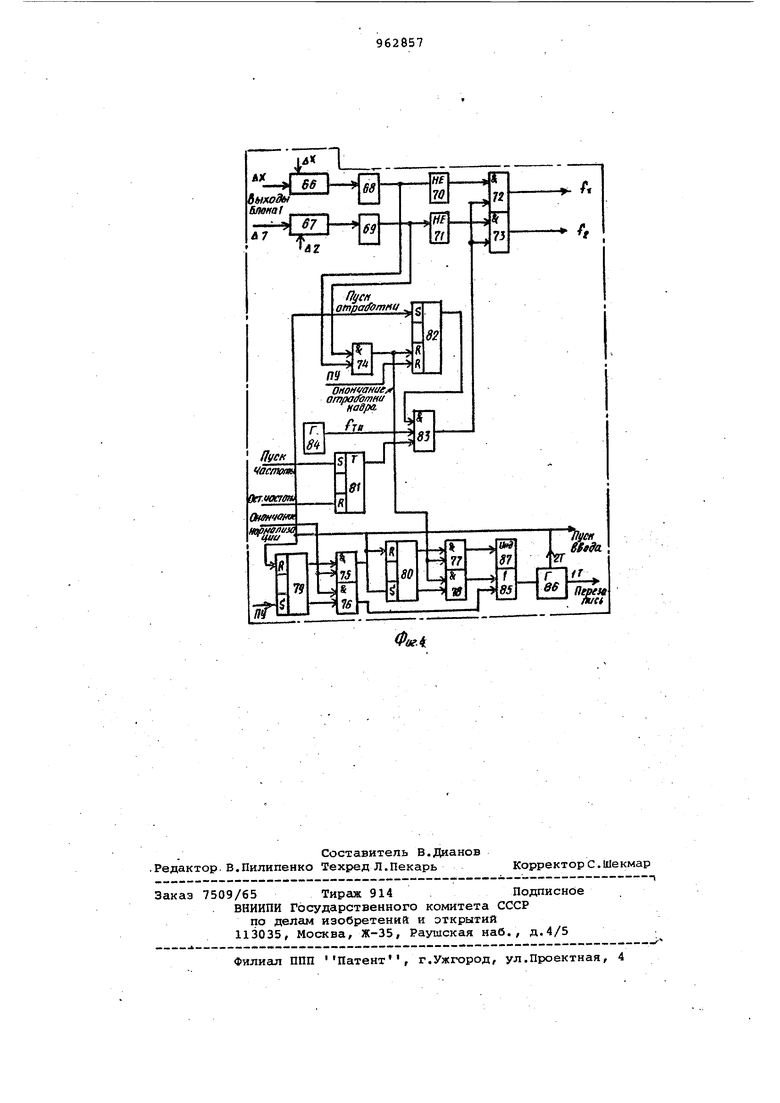

На фиг.1 представлена функционгшьная схема устройства; на фиг.2 - схе5ма блока формирования выходных сигналов; на фиг.3 - схема блока управления но1 лализацией; на фиг. 4 - схема блока центрального управления. Устройство {фиг.1) содержит блок

® 1 ввода программы, блок 2 задания

скорости, блок 3 формирования выходных сигналов, блок 4 управления нормализацией, блок 5 центрального управления, регистры 6 и 7 сдвига, коммутатор 8, реверсивные счетчики 9 и 10, буферный регистр 11, комбинационный с/мматор 12, буферный регист 13, комбинационный сумматор 14, пятый 15, второй 16, третий 17, пятый 18, второй 19 и третий 20 элементы И координатные приводы 21, четвертые 22 и 23 элементы И, первый элемент ИЛИ 24, элемент НЕ 23, первые 26 и 27 элементы И, третьи 28 и 29 элемен ты ИЛИ, блок 30 управления координат ными приводами, накапливающие сумматоры 31 и 32, второй элемент ИЛИ 33 и элемент НЕ 34., Блок 3 (фиг.1) содержит триггеры 35-38, элементы И 39-47, элементы ИЛИ 48-50, элемент НЕ 51 и элемент 52 задержки. Блок 4 (фиг.З) содержит элементы 53-59, элементы ИЛИ 60-62, триггер 6 и генераторы 64 высокой частоты и 65 серии импул сов. Блок 5 (фиг.4) содержит счетчики 66 и 67, элементы 68 и 69 фиксации нулевого состояния счетчиков, элемен ты НЕ 70 и 71, элементы И 72-78, триггеры 79-82, элемент И 83,генератор 84 частоты, элемента ИЛИ 85, генератор 86 тактов и индикатор 87. Устройство работает следующим образом. . Программа вводится в блок 1, в котором она дешифрируется в соответствии с,закодированными адресами, переводится из десятичной системы в двоичную и распределяется по остальным блокам устройства следуюгцим образом. Информация о коде подачи передается в блок 2, инфоЕялация о зна ках перемещения поступает в блок 3, код линейной интерполяции (функция G01) подается tf блрк 4, на другой . вход которого поступает любой из кодов круговой интерполяции () и на следующий вход коды резьбонарезания (G33,G34 и т.д.). Величины лX uZ высылаются в элемент памяти блока 5, величины Х, Z, т.е. коорди наты начальной точки дуги при круговой интерполяции или исходные значения подынтегральной функции; при линейной интерполяции, или же значения шагов реэьб на оборот вдоль соответствующей оси в режиме резьбонарезания заносятся с соответ ствующих выходов блока 1 в регистры 6 и 7 соответственно. Кроме того, п тенциальный сигнал круговой интерпо ляции с выхода блока 1 постоянно во действует на соответствующий вход коммутатора 8. По окончании ввода одного кадра програ7 мы блок 1 вырабатывает сигна окончания ввода, который поступает на вход блока 4 и запускает его.Бло 4 в зависимости от введенных в него ранее кодов режимов, линейной интер поляции, круговой интерполяцииили резьбонарезания осуществляет операций нормализации, подавая синхронно со своего выхода импульсы на сдвигающие входы регистров 6 и 7. В режиме, линейной интерполяции сдвиги заканчиваются, когда в старшем (п) разряде любого из регистров 6 или 7 окажется единица. При круговой интерполяции нормализация заканчивается в случае, появления единицы в разряде, предшествующем- старшему.(п-1) любого из регистров б или 7, а в случае единицы в старшем разряде любого из регистров б или 7 она не производится вообще. Причем в коммутаторе 8 i производится сдвиг 1, что исключает увеличение радиуса задаваемой окружности. В режиме резьбонарезания число сдвигов фиксировано и равно п, где (iN, где N - число отсчетов шпиндельного датчика за один оборот. По окончании нормализации блок 4 вырабатывает сигнал окончание нормализации , который поступает в блок 5. Бели введенный кадр является первым кадром программы, то сигнал окончание нормализации включает отработку вв1еденного кадра. (В случае, если введенный кадр,не являетсяпервым кадром программы, то включение отработки осуществляется по сигналу конец.отработки предыдущего кадра , который вырабатывается в блоке 5). При этом блок 5 фо1 1ирует сигнал перезаписи, который поступает на счетчики 9, 10 и формирует импульсы сдвига, что обеспечивает перезапись нормализованных значений заданных величин подынтегральных -функций из регистров 6 и 7 в счетчики 9 и 10 соответственно. «, Импульсы высокой частоты с выходов drfoKa 5 на чинают постугать на суммирующие входы (С2) накапливающих сумматоров 31 и 32 обеих координат, выполненных, с целью обеспечения однотактного суммирования и корректировки, на комбинации {регистра 11 (13) из J-K триггеров и комбинационном сумматоре 12 (14) . Кроме того, эти же импульсы поступают на стробирующие входы элементов И 15-17 в канале управления координаты X и элементов И- 18-20 в канале управления координаты Z. Каждалй тактовый импульс, поступая на суммирующий вход (С2) соответствующего накапливеиощего сумматора 31(32) обеспечивает прибавление к его содержимому значения подынтегральной функции, хранимой в соответствующем счетчике 9 или 10. Далее устройство работает в трех режимах. В режиме резьбонарезаиия с выхода рабочей памяти блока 1 через элемент ИЛИ 2 4 на входы элементов И 15, 18, 22, 23 и элемента НЕ 25 поступает сигнал РН, Причем выходной сиг-- нал элемента НБ 25 запирает элементы И 16, 17, 19, 20, а выходной сигнал элемента ИЛИ 24 открывает элементы И 26, 27, Такая коммутация обеспечивает функционирование сумматоров 31 и 32, выполненных на регистре 11, сумматоре 12 и регистре 13, сумматоре 14 с полноразрядной сеткой, так как элементы И 22, 23, 26, 27 по управляю1цим входам оказываются открыты и выходы старших (п) и (п-1) разрядов сумматоров 12 и 14 подключены к соответствующим входам регистров 11 и 13.

С другой стороны, в группе элементов И 15-17 открытым по управляющему входу оказывается только элемент И 15, а в группе элементов И 1820 - только элемент И 18. Элементы И 15 18 по вторым своим входам стробируются импульсами тактовой частоты, а по третьим входам управляются выходами переноса (Р) старших разрядов сумматоров 12 и 14 соответственно. Поэтому при появлении на выходах переноса (Р) сумматоров 12 или 14 единичного сигнала на выходах .элементов И 15 или 18 появляется импульс при- ращения координаты X или t соответственно.

Импульс приращения координаты X с выхода элемента И 15 через элемент ИЛИ 28 поступает в блоки 3 и 5, а также на один из входов коммутатора 8. Импульс приращения координаты Z с выхода элемента И 18 через элемент ИЛИ 2У поступает в блоки 3 и 5 и на соответствующий вход коммутатора 8. При отсутствии сигнала круговой интерполяции (КИ) коммутатор 8 закрыт и корректировки значений подынтег.г ральных функций в счетчиках 9 и 10 не происходит. В режиме резьбонаращения на входе блока 3 присутствует сигнал РН, при этом блок 3 пропускает импульсы приращения дХ, Л2 в блок 30, выходные сигналы которого осуществляют управление исполнительными приводами 21 станка по координатам. X и Z.

В режиме линейной и круговой интерполяции сигнал РН на входе блока 3 отсутствует, благодаря чему этот блок накапливает приращения,необходимые для анализа одиночного или двойного шага и вырабатывает сигналы останов тактовой частоты , который, поступая в блок 5, прерывает его выработку и сигнал признак двойного шага , который, поступая в блок 2, вызывает увеличение в тП раз период выдачи следующего импульса. Очередной импульс с выхода блока 2 поступает в блок. 3 и выталкивает (сдвигает), из него накопленные приращения в блок 30 и, кроме того, поступая на соответствующий вход блока 5, восстанавливает выработку этим блоком импульсов тактовой частоты. Это обеспечивает упЕ)авление скоростью подачи и поддержание постоянства конгурной скорости как в реж1сме линейной, так и в режиме круговой интерполяции. Данная операция продолжается до тех пор, пока подсчет имЛульсов приращений ЛХ, л2 в блоке 5 не приведет к получению заданных

0 значений перемещений по осям К, L. При этом прекращается выдача тактовых импульсов блоком 5.

В режиме линейной интерполяций в силу нормализации значений подынтегральных функций до появления i

5 в старшем разряде любого из регистров б или 7, максимальное число так-товых импульсов, которые необходимо подать на интерполяторы (число операций) для получения одного импульса

0 приращения равно двум. Действительно, минимальное число, которое может принять большая подынтегральная функция после нормализации будет 0,1000 ...О - двоичное, т.е. 0,5 - десятич5ное, естественно, что переполнение сум1 атора 31 (32) будет происходить после каждых двух суммирований. Следовательно, быстродействие интерполятора в этом режиме будет всего в

0 2 раза меньше тактовой частоты.

В режиме резьбонарезания интерполятор выполняет роль пропорцйонгшьного делителя, для которого имеет значение только тактовая частота, ко5торая определяется произведением числа оборотов шпинделя на число отсчетов датчика резьбонарезания, который монтируется.на шпинделе. Так при максимальном числе оборотов,рав0ном 2000 об/мини числе отсчетов датчика, равном 4096 за оборот, тактовая частота оказывается равной (2000:бО)х4С96 136БЗЗ Гц, что в 10 раз меньше, чем быстродействие сумматора, построенного на применяемой

5 в ЧПУ -серии К155.

В режиме круговой интерполяции обеспечение максимального быстродействия оказывается значительно сложнее ввиду изменения величин подын0тегральных функций в процессе работы.

Действительно, поскольку нормализация при круговой интерполяции производится до появления единицы в сле5дующем за старшим разряде подынтегральной функции, то минимальным значением подынтегральной функции является 0,010...О - двоичное или 0,25десятичное, что требует четырех так0тов (итераций) для получения .одного приращения, т.е. без специальных мер I быстродействие круговой интерполяции оказывается в два раза меньше, чем линейной. Нормализация до 0,1000...7

5 невозкояша,., так как в этом случае

Сможет получиться потеря информации в результс ге выхода за разрядную сетку величина подынтегральнойфунклии. Действительно, пусть задана подынтегральная функция 0,0001111, тогда после нормализации она примет вид 0,1111000, после восьмой корректировки на +1 она примет вид 1,0000000, т.е. превратится в О и интерполятор у идет, с заданной траектории, В том случае, если единица оказалась в старшем значащем разряде до нормализации, то, как уже бнто сказано выше, нормалязация не производится и интерполятор начинает работать пр двухтактной схеме. Причем в этом случае описанная ситуация возникнуть не может, так ка максимальное изменение подынтегральной функции при круговой интерполяции равно 1 1,41, в то время, как отношение максимального десятичного числа, которое может быть задано в nporpaM;vie (9999999) и максимального двоичного числа (16 777 215), которое может быть записано в регистры . и сумматоры интерполятора, равно 1,67, следовательно, переполнение в Рзгистре подынтегральной функции невозможно. Однако, кроме того, возможна ситуация, при которой в процессе интерполяции исчезает 1 в старшем разряде подынтегральной функции, если она была хам первоначально, НИИ в следух)31-эм за старшим разряде, есаи она первоначально была в нем. При этом число тактов на каждую итерацию возрастет.;в дваг раза и достигнет в первом случае 4;, а во втором 8, т.е. в этом случае быстродействие кругового интерполятора по сравнени.ю с линейным упадет в 4 раза. Однако в устройстве этого не произойдет при любых возможных ситуациях.

Пусть задана окружность такого большого диаметра, что единица оказалась в старшем разряде подынтегральной функции без нормализации. Тогда элемент ИЛИ 24 будет открыт сигналом, поступающим с выхода старшего разряда (п) любого счетчика 9 или 10. Поэтому будут открыты элементы И 15, 13 и, сле довательно, импульсы приращений ЛХ, Д2 будут формироваться при появлении переполнений на выходах переноса старсаего разряда (Р) сумматоров 12 и 14 точно также, как это было описано в прздчдущях режимах. Однако поскольку коммутатор 8 в режиме круговой интерполяции открьпг, каждый «мпульс приравдэний АХ, д 1 корректирует подынтегральную функцию в канапе противоположной координаты на t Д.

После некоторого количества кррв старшем разряде

ректировок

счетчика 9 или 10 исчезает. Если при этом отсутствуют единицы в старших

разрядах регистров 11 и 13, то это означает что с этого момента интерполятор начинает работать по четырехтактовой схеме, т.о. ему на формирование одного прирйщения потребуется четыре тактовых импульса. Однако это не произойдет, так как при этом закраваются элементы И 15, 18 в то время, как элемент ИЛИ 33 наверняка окажется включенным (действительно,

0 при счете на вычитание единицы вслед за комбинацией 10000...00 всегда следует комбинация 0111...11).

С выхода элемента ИЛИ 33 сигнал открывает элементы И 16, 19 и черэз

5 элемент НЕ 34 закрывает элементы И 17, 20. С другой стороны элементы И 22, 23 оказываются закрытыми нулевыи сигналом с выхода элемента ИЛИ 24, в то время, как элементы И 26,

27 остаются открыты.ли. Благодаря этому нарушается связь мэжду входами старших разрядов регистров 11, 13 и выходом старших разрядов сумматоров 12 и 14. Таким образом, разрядность

5 накапливающих сумматоров 31 и 32 э обеих координатах как бы сокращается на один разряд за счет исключения стариего разряда, а выходные сигналы старших (п) разрядов сумматоров 12 и 14 выполняют роль сигналов переполнения и из них с помощью элементов И 16, 19 формируются сигналы переполнения дХ,AZ как и во всех описанных вьше режимах, т.е. с ислользованием максимально двух тактовых

5 импульсов для выработки одного переполнения.

Поскольку в момент переключения старшие разряды регистров 11 и 13

0 были в нулевом состоянии, то сокращение разрядности накапливающих сумматоров, как это было описало выде, liei приведет к внесению какой-либо погре вности в накопленные значения

5 интегралов, хранимых в накапливающих сумматорах координат.

Дальнейагая работа продолжается, как было описано вьсяе, в режиме линейной и нтерполяции, вплоть до конА да отработки кадра.

В случае, если при круговой интерполяции до нормализации единицы в стармем разряде не было, то, как описывалось выне, нормализация пров п-1

изводится до появления

разряде. В этом случае при работе кругового интерполятора возможны две ситуации противоположного характера. П первой, когда начальная точка лежит на оси или вблизи одной из осей координат в процессе отработки дуги окружности, единицы могут исчезнуть и в (п-1) разрядах счетчиков 9 и 10. Во втором случае, когда начальная точка находится на дуге окружности под углом, близким к 45, единица в процессе отработки.может появиться в старшем разряде одного из счетчиков. Первый случай опасен превращением интерполятора в четырехтактный, второй - искажением траектории, если в устройстве не было принято специаль ных мер. Итак, первоначально единицы в п-разрядах реверсивных счетчиков отсутствуют, следовательно, ИЛ 24закрыт, а элемент ИЛИ 33 открыт, в результате чего интерполятор работает, как в конце предыдущего режима с укороченной на единицу разрядной сеткой в двухтактном режиме, причем приращения лх,дг снимаются с элементов И 16, 19. При исчезновении единиц в n-i разряде обоих счетчиков 9, 10 и Сп-1)-разрядах регистров 11 и 13 элемент ИЛИ 33 также закрывается. В результате чего закрываются элемекты И 15, 16, 18, 19, 22, 23, 26, 27 и открываются элементы И 17, 20, так как на входах элементов НЕ 25и 34 присутствуют нулевые сигналы. Благодаря этому дальнейшая работ интерполятора осуществляется с укороченной на два старших разряда разрядной сеткой, но по-прежнему по дву тактной схеме, причем приращения дХ, д2 выделяются элементами И 17, 20. , В случае, если в процессе отработ ки дуги единица появилась в старшем разряде любого из реверсивных счетчиков, то на выходе элемента ИЛИ 24 появляется единица, в результате чеГ9 оказываются открытыми элементы И 15, 18, 22, 23 и открываются элементы И 26, 27, а элементы И 16, 17, 19, 20 закрываются. .Интерцолятор начинает работать с полной разрядной сеткой, но по-прежнему в двухтактном режиме, при этом выхода за разряднур сетку и искажения траектории не произойдет. Следовательно, по сравнению с другими известными устройствами, предлагаемое обладает вдвое большим быстродействием при равном быстродействии объектов и фактиче.ски равном объеме электронного оборудрвания Блок 3 (фиг.2) работает следующим образом. Первоначально в .триггеры 35 и 3S с выхода блока 1 записываются знаки координатных перемещений Зн.Х 3H.Z.. Сигнал резьбонарезания РН (633, 634) подается, если задан в кадре, , на вход элементов И 39, 40 и вход элёме та НЕ 51. Сигнал пуск частоты с выхода блока 2 поступает на входы элементов И 46, 47 и эле1«нтал 52 за держки. Приращения лХ и Д2. поступают с выходов элементов ШШ 28, 29 в виде унитарного кода. В режиме резьбонарезания на входе блока 3 присутствует сигнал РН, который открывает элементы И 39, 40 и через элемент ИВ 51 закрывает элементы И 46, 47. Благодаря этому импульсы координатных приращений л X я лТ. через элементы И 39, 40 и элементы ИЛИ 4t) и 49 поступают на входы элементов И 41-44 соответственно. Элементы И 41, 42 управляются выходами триггера 35 (запоминания знака перемещения по координате X), элементы И 43, 44 управляются выходами триггера 38 (запоминания знака перемещения координаты Z). Поэтому унитарные коды координат X, Z коммутируются в яужный канал в соответствии заданным знакам. Другие сигналы в этом режиме участия в работе не принимгиот. В режиме линейной или круговой интерполяции потенциал РН отсутствует, поэтому элементы И 39, 40 закрыты, а выходной сигнал с выхода элемента НЕ 51 выдает разрешаюнщй потенциал на входы элетлентов И 46, 47. Приращения ДХ, Л2 устанавливают в тригге ил 36 и 37 соответственно.После этого сигнал пуск частоты ,, поступаюпщй с выхода блока 2, поступает в качестве строба на вторые входы элементов И 46, 47 и элемента 52. Третьи входы элементов И 46, 47 управляются единичными выходами триггеров 36 и.37. Если соответствующий триггер 36 или 37 находится в одиночном состоянии, то соответствующий элемент И 46 или 47 открывается и выходные сигнсшы через элементы ИЛИ 48, 50 и элементы И 4144 поступают на выход блока 3 с учетом заданного энака. Триггеры 36 и 37 через элементы 52 сбрасываются в О. В случае, если оба триггера 36 и 37 после поступления очередных приращений оказались в состоянии , то элемент И 47 вырабатывает сигнал признак двойного хода . Элемент ИЛИ 50 вырабатываем сигнал останов тактовой частоты при появлении в любом из триггеров 36 и 37. Блок 4-(фиг.З) работает следующий образом. Первоначально сигналом предварительной установки (ПУ) через элементы ИЛИ 62 триггер 63 устанавливаетя в О , Выходы старших (п) разрядов регистров 6 и 7 подключены к вхоам элементов И S3 и 54 соответственно. Потенциал линейной интерполяции (ЛИ) подключен с входа блока -1 к вхоу элеме.нта ИЛИ 60, потенциал круговой интерполяции (КИ) с выхода блока 1 присоединен к входам элемента ИЛИ 0 и элементов И 55, 56.,Выходы сле5 щих за старсоими разрядов (п-1) егистров 6 и 7 координат X и 2 приоединены к входам элементов И 55 и 6 соответственно. Сигнал резьбонаезания подается также с выхода блоа 1 на вход элемента И 58. В режиме линейной интерполяции в блоке 4 присутствует потенциал ЛИ, а КИ и РН отсутствуют. Тогда по сиг налу пуск нормализации триггер 63 устанавливается в состояние и открывает элемент И 59« Частота f с выхода элемента И 57, открытого потенциалом ЛИ через элемент ИЛИ, 60 через элемент ИЛИ 61 и элемент И 59 начинает поступать на вход коммутатора 8 и на сдвигаюидие входы регист ров 6 и 7, при этом информация в ре гистрах 6 и 7 начинает сдвигаться в сторону старших разрядов до тех пор пока 1 не появится в старшем разряде любого из них. Тогда он про дет через элемент И 53 или элемент 54 и появится на выходе элемента -ИЛ 62, как сигнал окончание нормализации, который сбросит в О триггер 63 и поступит на соответству юишй вход блока 5. В случае, если к моменту прихода сигнала пуск нормализации в ста шем разряде любого из регистров 6 7 была то триггер удержи или О по входу R и на выхо вается в окончание нормализ имеется сигнал ции, В этом случае никаких сдвиго производить не надо. В режиме круговой интерполяции потенциалы ЛИ и РН отсутствуют и присутсфвует потенциал КИ. Этот потенциал через элемент ИЛИ 60 формирует разрешающий потенциал на управ ляющие входы элементов И 53, 54, 57 и, кроме того, непосредственно поступает на управляющее входы элемен тов И 55, 56. Теперь по сигналу пуск нормализации триггер 63 перебрасывается в состояние i и частота f с выхода генератора 64 через элементы И 57, ИЛИ 61, И 59 поступает на выход блока 4 в качестве импульсов сдвига. Это продолжается до тех пор, пока в следующем за стариим разрядом (п-1) любого из регистров 6 или 7 не появится . Тогда срабатывает И 55 или И 56 и на выходе элемента ИЛИ 62 формируется сигнал окончание нормализации, который, как и в предыдущем режиме, сбрасывает в О триггер 63 и поступает на выход блока 4. Элементы И 53 и 54 при этом используются для формирования сигнала окончание нормализации 1 была в старшем разряде любого из регистров 6 или 7 еще до нормализации, аналогично предыдущему режиму . В режиме резьбонарезания потенциалы ЛИ и КИ отсутствуют, ко присутствует потенциал РН, который поступает на управляющий вход элемента И 58. С приходом сигнала пуск HOfSviaлиз аиии триггер 63 устанавливается 8 состояние 1 , с его единичного выхода сигнал поступает на второй вход эпеманга И 58, при этом на выходе форм:ггг;/егся сигнал, яалускаюсйий генера.; ор 65., При атом на его первом выходе поянляется пачка тактовых импульсоа T.J-1V,, количество которых постоянно и зависит от числа отсчетов датчика резьбонарезания и разрядности основных узлов- предлагаемого.устройства Эти импульсы через элемент ИЛИ 61 .и элемент И 59 поступают на выход в качестве импульсов сдвига. По окончании йледования пачки импульсов Т на втором выходе генератора65 появляются п+1 такт , который через элемент ИЛИ 62 выключает триггер 63 и поступает на вход в виде сигнала окончание нормализации/. Блок 5 (фиг.4) работает следующим образом. Первоначально, по-сле включения питания, сигналом предварительной установки (ПУ) триггер 79 устанавливается в единичное, а триггер 82 в нулевое состояние. Устройство вводит первый кадр программы, при этом величины заданных в кадре приращении ДХ и д и с выходов блока 1 заносятся в счетчики 66 и 67. После этого сигнаокончание ввода включается нормализация (пуск нормализации) . По окончании нормализации с выхода блока 4 приходит сигнал окончание нормализации , который поступает на входы элементов И 75, 76. Так как элемент И 76 открыт единичным сигналом с выхода триггера 79, то на его выходе появляется сигнал, который, пройдя через элемент ИЛИ 85, поступает на вход генератора 86 тактов и запускает его. Генератор 86 вырабатывает два сдвинутых относительно друг друга такта IT и 2Т. Такт IT переписывае нормализованную информацию из регистров 6 и 7 в счетчики 9 и 10 соответственно. (В случае, если счетчики 9 и 10 построены на комбинации сдвиговых регистров и комбинационных сумматоров, то перезапись информации. из регистров 6 и 7 в счетчики 9 и 10 удобно производить в виде последовательных кодов, но по одному проводу. В этом случае вместо такта IT не-; обходимо выработать серию импульсов перезаписи). Такт 2Т является сигналом пуск отработки для всего устройства, поэтому он устанавливает в триггер 82, он же поступает в блок 1 в качестве сигнала пуск ввода следующего кадра и, кроме того, сбрасывает в ноль триггера 79 и 80. Так как триггер 82 находится в состоянии 1 то элемент И 83 открыт по первому входу. С приходом, сигнала пуск частоты, который является выходным сиг налсад блока 2, триггер 81 усганавли и элемент вается в состояние 83 открывается и по второму входу. Поэтому импульсы генератора 84 част ты f проходят через элемент И 83 поступают на входы элементов И 72, 73, открытых по вторым входам выход ными сигналами элементов НЕ 70, 71, и, следовательно, проходят на выход блока в виде частот f ,f -,. Сигналы на выходах элементов НЕ 70, 71 присутствуют до тех пор, пок счетчики 66 и 67 не придут в нулево состояние, что фиксируется элемента ми 6В и 69. Импульсы частот f и f поступаю на входы соответствующих блоков уст ройства до тех пор, пока с выхода блока 3 не поступит сигнал остано тактовой частоты , который сбрасывает в О триггер 81, благодаря чему закрывается элемент И 83, и ча тоты fj( и f 2 прерываются до тех пор пока с выхода блока 2 не поступит сигнал пуск частоты . Во врзмя отработки кадра програм мы устройство вырабатывает импульсы приращений ДХ и дг, которые с выхода элементов ИЛИ 28, 29 поступают на, входы счетчиков 66 и 67. Сигнал пуск вводаj поступив в блок 1, запускает ввод следующего кадра про граммы, а по окончании ввода включает нормализацию (по сигналу пус нормализации ), как это было описа но BbEiie, По окончании нормализации блок 4 выработал сигнал окончания нормализации , который подступает н элементы И 75, 76, Но теперь элемент И 76 закрыт, так как триггер 79 в нуле, а элемент И 75 открыт, поэтом сигнзьп появляется на его выходе и ус танавливает в ч триггер 80. Окончание отработки кадра определяется элементом И 74, как ситуация, при которой оба счетчика 66 и 67 пришли в VO. Тогда на.выходах элементов 68 и 69 появляются сигйалы, выключающие через элементы НЕ 70, 71 элементы И --72, 73. Одновременно сигнал окончание отработки кадра с выхода элемента И 74 сбрасывает в О триггер 82 и поступает на элементы И 77, 78. Элемент И 78 открыт единичным выходом триггера 80, поэтому на его выходе по-, является сигнал, который через элемент ИЛИ 85 запускает генератор 86 тактов И цикл работы повторяется, i Элемент И 77 в этом случае закрыт нулевым сигналом триггера 80. В том случае, если в программе задан кадр с очень малым временем .отработки, меньшим времени ввода сле дующего кадра, то сигнал окончание отработки будет выработан раньше, чем придет сигнал окончание нормализации . В этом случае триггер 80 окажется в нулевом состоянии, поэтому элемент И 78 окажется закрытым, и запуска следующего цикла отработки не произойдет, но сработает элемент И 77, который включит индикатор 87. Включение индикатора 87 указывает на ошибку в программе. Преимуществами предлагаемого устройства по сравнению с известным является повыоюние быстродействия в два раза, повышение точности за счет исключения потери информации при округлении и повышение надежности за счет гарантированного и автоматического исключения возможности переполнения регистров подынтегральной функции. Это позволяет обеспечить повышение быстродействия во всех режимах 125-200 кГц до 200-500 кГц, что соответствует повышению скорости с 1012 до 30 м/мин, и, кроме того, исключается брак из-за ошибок программирования. Формула -изобретения Устройство для двухкоординатного программного управления, содержащее коммутатор, последовательно соединенные блок центрального управления,блок ввода программы, блок задания скорости, блок формирования выходных сигналов и блок управления координатными приводами и для каждой координаты - последовательно соединенные регистр сдвига, реверсивный счетчик, комбинационный сумматор и буферный регистр, второй и третий выходы блока ввода программы подключены к соответствующим вторым входам блока формирования выходных сигналов, второй выход которого подключен к второму входу блока задания скорости, третий выход блока ввода программы подсоединен к первому входу блока центрального управления, а третий вход - к второму входу блока центрального управления и к выходу блоха задания скорости, четвертый и пятый выходы блока ввода программы подключены к третьему и четвертому входам блока центрального управления соответственно, шестой и седьмой выходы - к первому входу регистра сдвига соответствующей координаты, а восьмой выход - к первому входу коммутатора, управляющий вход реверсивного счетчика каждой координаты подключен к соответствующему выходу коммутатора, второй информационный выход блока центрального управления подсоединен к счетному входу реверсивного счетчика каждой координаты, причем для каждой координаты выходы каждого разряда буферного регистра подключены к вторым входам соответствующих разрядов комбинационного сумматора данной координаты, о.т личающееся тем, что, с целью повышения быстродействия и точности устройства, в него введены блок управления нормализацией, первы и второй элементы ИЛИ и для каждой координаты - элемент НЕ, пять/элементов И и третий элемент ИЛИ, девятый, десятый и одиннадцатый выходы блока ввода программы соединены соответственно с первым, вторым и третьим входами блока управления нормализацией., первый выход которого подключен к второму входу региЪтра сдвига каждой координаты и к второму входу коммутатора, а второй выход к пятому входу блока центрального управления, шестой и седьмой входы которого соединены с четвертым и пятым входами блока формирования выходных сиг.налов соответственно, с третьим и четвертьАл входами коммутатора соответственно и с выходами третьих элементов ИЛИ первой и второй координат соответственно, вьвсод первого элемента ИЛИ подключен к первым входам первых элементов И обеих координат и к входу элемента НЕ первой координаты, выход второго элемента ИЛИ соединен с первым входом первого элемента ИЛИ, с первым входом второго элемента И каждой координаты и с входом элемента НЕ второй координаты, подключенного выходом к первому входу третьего элемента И обеих координат, выход элемента НЕ первой координаты соединен с вторыми входами втрс(ых и третьих элементов И обеих координат, вторые и третьи входы первого элемента ИЛИ соединены соответственно с выходом п-го разряда буферного регистра каждой координаты и с выходом п-го разряда реверсивного счетчика каждой координаты, а четвертый вход - с т,ретьим выходом блока ввода программы, первые и вторые входы второго элемента ИЛИ соединены соответственно с выходсми (л, 1)-го разряда буферного регистра каждой координаты и -с выходом {п-1)-го разряда реверсивного счетчика каждой координаты, двенадцатый выход блока

вйода программы подключен к четвертому входу блока управления нормализацией, кроме того, для координаты выход (n-l)-ro разряда комбинационного сумматора соединен с вторым

входом первого и с третьим входом третьего элементов И данной координаты, выход п-го разряда - с первым входом четвертого и третьим входом второго элементаИ данной координаты, а выход переноса - с первым входом пятого элемента И данной координаты, подключенного вторым входом к второму входу четвертого элемента И и к выходу первого элемента ИЛИ,

третьим входом - к управляющему входу буферного регистра и к четвертым входам второго и третьего элементов И данной координаты и к соответствующему тактовому выходу блока

центрального управления, а выходом к первому входу тр етьего элемента ИЛИ данной координаты, второй и третий входы которого соединены с выходами второго и третьего элементов И той же координаты, выходы первого и четвертого элементов И каждой координаты соединены с входами соответственно (n-l)-ro и п-го разрядов буферного регистра данной координаты, а выход г (H-l)-ro и п-го разрядов регистра

сдвига каждой координаты подключены к пятым и шестым входам блока управления нормсшизацией

Источники информации, принятые во взимание при экспертизе

1. Авторское свидетельство СССР 555381, кл. G 05 В 19/18, 1975.

2. Дригваль Г.Ц. Цифровые дифференциальные анализаторы. М., Советское V радио , 1970, с. 183-184.

3. Там же, с.194.

4.Авторское свидетельство CCCi „ 658528, кл. G 05 В 19/18, 1977.

5.ABTopckoe свидетельство СССР 746431, кл. U 05 В 19/18, 1978

, (прототип).

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интерполятор | 1986 |

|

SU1310778A1 |

| Интерполятор для систем программного управления | 1977 |

|

SU658528A1 |

| Устройство для коррекции положения резца на станке с программным управлением | 1981 |

|

SU983651A1 |

| Устройство для программного управления | 1986 |

|

SU1376065A1 |

| Линейно-круговой интерполятор | 1978 |

|

SU746431A1 |

| Линейно-круговой интерполятор | 1978 |

|

SU807236A1 |

| Линейно-круговой интерполятор | 1986 |

|

SU1312530A1 |

| Линейно-круговой интерполятор | 1977 |

|

SU741234A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Линейно-круговой интерполятор | 1979 |

|

SU847279A1 |

Авторы

Даты

1982-09-30—Публикация

1981-01-16—Подача