сдвига первого регистра сдвига, входом синхронизации.триггера перенса и входом второго регистра сдвига .выход первого регистра сдвига соединен с первым входом сумматора по модулю два, второй вход которого об единен с управляющим входом мультиплексора и подключен к третьему разрядному выходу блока постоянной памяти, адресный вход которого подключен к первому выходу генератора тактовых импульсов, выход сумматора по модулю два соединен с первым входом одноразрядного сумматора, второй и третий входы которого соединены соответственно с выходом младшего разряда второго регистра сдвига и информационным выходом триггера переноса, единичный и нулевой установочные входы которого подключены к соответствующим выходам мультиплексора,выход переноса одноразрядного сумматора соединен с информационным входом триггера, выход одноразрядного .сумматора соеднен с входом старшего разряда второго регистра сдвига, разрядные выходы.которого соединены с соответствующими входами блока извлечения квадратного корня, выход которого соединен с входом регистратора.

2. Устройство по п.1,;о т л и чающееся тем, что вычисли21

тельный блок содержит цифроаналогоBfiiA преобразователь, сумматор, и второй компараторы, элемент НЕ, первую и вторую группы элементов И, выходы которых являются соответственно выходами дополнительного и прямого кодов блока, первые входы первой группы элементов И объединены и подключены к выходу элемента НЕ вход которого соединен с выходом первого крмпаратора, а вторые входы первой группы элементоы И объединены и являются первым управляющим входом блока, первые входы второй группы элементов И объединены и под ключены к выходу второго компаратора, а вторые входы второй группы элементов И объединены с входом цифроаналогового преобразователя и являются вторым управляющим входом блока, первые информационные входы компараторов объединены и являются первым информационным входом блока., второй информационный вход первого компаратора подключен к выходу сумматора, управляющие входы компараторов объединены и являются входами синхронизации блока, второй информащюнный вход второго компаратора объединен с первым входом сумматора и подключен к выходу цифроаналогового преобразователя, второй вход сумматора является вторым информационным вхоДом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения третьего центрального момента | 1983 |

|

SU1120353A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2010 |

|

RU2446444C1 |

| Коррелометр | 1983 |

|

SU1091173A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ БЫСТРОЙ СВЕРТКИ | 1991 |

|

RU2028666C1 |

| ГЕНЕРАТОР БЕЛОГО ШУМА (ВАРИАНТЫ) | 1997 |

|

RU2120179C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Цифровой коррелометр | 1983 |

|

SU1113806A1 |

1. УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДЕЙСТВУ1ОДЕГО ЗНАЧЕНИЯ СИГНАЛА, содержащее регистратор, блок масшта-, бирования, вход которого является входом устройства, выход блока масштабирования сбединен с первым информационным входом вычислительного блока, второй информационньй вход которого подключен к выходу источника постоянного напряжения, первый и второй управляющие входы первого вычислительного блока соответственно подключены к первым выходам первой и второй групп выходов генератора псевдослучайных чисел, а вход синхронизации подключен к первому выходу генератора тактовых импульсов, второй выход которого соединен с входом генератора псевдослучайных чисел, отличающийся тем,. что, с целью повышения быстродействия, - в него введены накапливающий сумматор, блок постоянной памяти, счетчик переноса, первый и второй регистры сдвига, сумматор по модулю два, одноразрядньй сумматор, мультиплексор, триггер переноса, блок извлечения квадратнс го корня и (Пг-1) вычислительных блоков, вторые информационные входы которых объединены и подключены к выходу источника постоянного напряжения, а первые информационные входы объединены и подключены К выходу блока масштабирования, первый и второй управляющие входы i-го ВЕмислительного блока (где ,..., : W) соответственно подключены KI-M выходам первой и второй групп выходов генератора псевдослучайных чисел, входы синхронизации вьгаислительных блоков, кроме первого, объединены и подклточены к первому выходу генератора тактовых импульсов, выходы 1 прямого и дополнительного кодов вычислительных блоков соединены с соответствующими входами накапливающего сумматора, выход которого через счетчик переноса соединен с информационным входом первого регистра сдвига, вход записи которого объединен с информационным входом мультиплексора и подключен к первому разрядному выходу блока постоянной памяти, второй разрядный выход которого соединен с входом

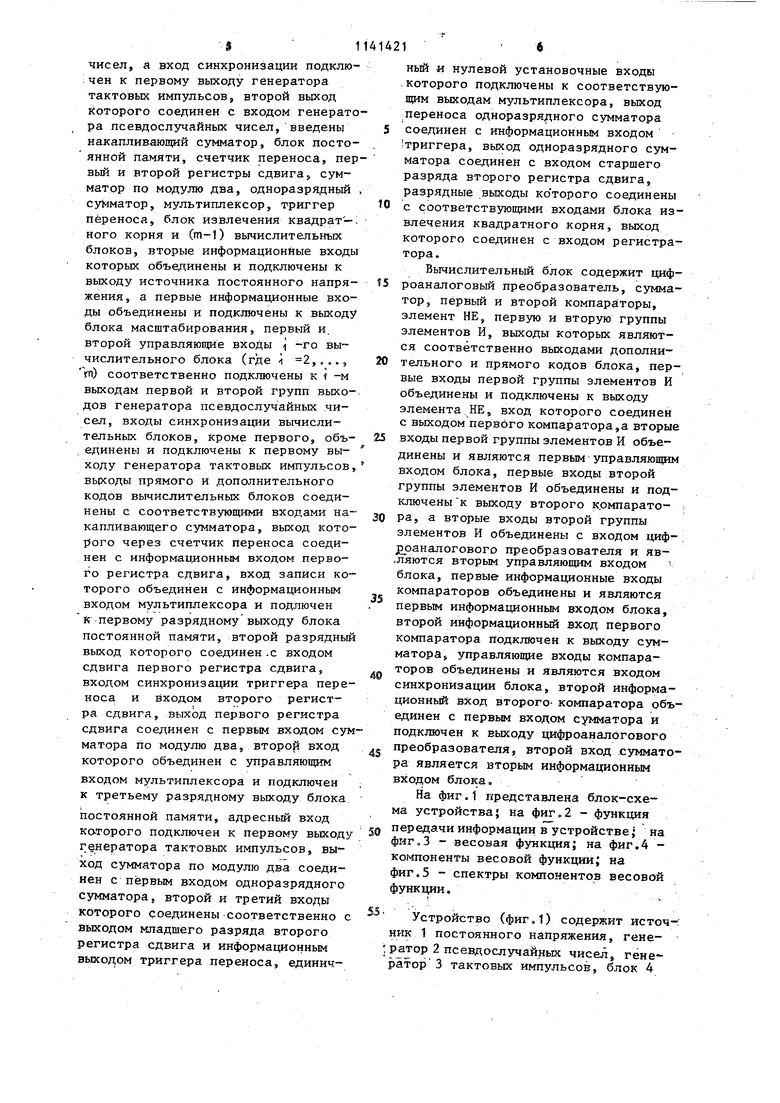

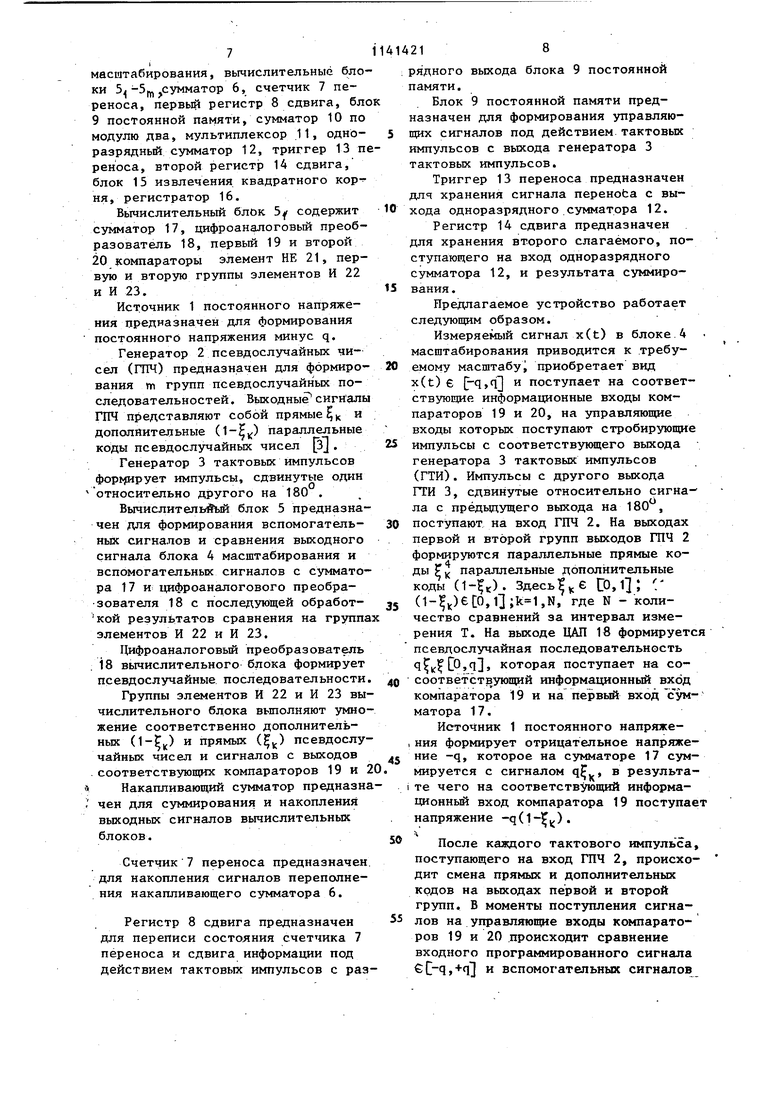

Изобретение относится к измерительной технике и может быть исполь зовано в производстве радиоэлектрон ной аппаратуры при определении действующего значения сигналов. Известен коррелометрический измеритель действующего значения сигн ла, построенный по автокомпенсацион ной схеме с цифроаналоговым преобра зователем и источником опорного напряжения в обратной связи, содержащей формирователь опорного переменного напряжения, запоминаюпщй элемент, масштабный преобразователь, устройства сравнения, устройство уравновешивания и измерительньй орган l . Подобные измерители сложны, обладают относительно большой погрешностью на инфранизких и радиочастотах. Наиболее близким по технической сущности к предлагаемому является коррелометрический цифровой измеритель действующего значения .сигнала, % содержащий входное устройство, источник постоянного напряжения, генератор псевдослучайных чисел, генератор тактовых импульсов, квантователь, регистрирующее устройство, причем вход измерителя соединен с входом входного устройства, выход которого соединен с первым входом . квантователя, второй вход которого соединен с выходом источника постоянного напряжения; третий вход квантователя соединен с первым выходом первой группы выходов генераторов псевдослучайных чисел, четвертый вход квантователя соединен с вторым выходом первой группы выходов генера .тора псевдослучайных чисел,пятый вход квайтователя соединен с первым выходом генератора тактовых импульсов, второй выход которого соединен с входом генератора псевдослучайных чисел, квантователь, содержащий цифроаналоговьй преобразователь, аналоговьй сумматор, первьш и второй компараторы, логический инвертор, первую и вторую группу вентилей, причем третий вход квантователя соединен с первыми входами первой группы вентилей, четвертый вход квантователя соединен с первыми входами второй группы вентилей и входами цифроаналогового преобразователя, выход которого соединен с первым входом второго компаратора и первым входом аналого-цифрового сумматора, вто рой вход которого соединён с вторым входом квантователя, выход аналогового сумматора соединен с первым вхо дом первого компаратора, выход которого через логический инвертор соединен с вторым входом первой группы вентилей, первый вход квантователя соединен с вторыми входами первого и второго компараторов, третьи входы соединены с пятым входом квантователя , выход второго компаратора соединен с вторым входом второй группы вентилей, а .выходы первой и второй групп вентилей соединены с первым и вторым выходами квантовате ля 2 . , Недостатком известного устройств является низкое быстродействие. Сиг нал, пропорциональный квадрату вход ного сигнала, поступает в решающий блок, которьй проводит операции равновесного усреднения, нормирования и извлечения квадратного корня, что соответствует обработке сигнала с помощью прямолинейной весовой функции (ПВФ). Модуль спектра ПВФ описывается известной функцией отсчетовJqOco}UlciCi)l.J. О) При вычислении эффективного значени например, гармонического сигнала 214 X (t) А S incjt после возведения в квадрат а,,х h-coi52cj-t x4tV-A( необходимо подавлять помеху двойной частоты. Погрешность описывается в худшем случае огибающей функции отсчетов,) Из последнего выражения при заданной погрешности время измерения Т равно Ti( Второй фактор, ограничивающий быстродействие известного устройства - необходимое количество сравнений для достижения заданной погрешности 8 . Для достижения заданной погрешности необходимо провести некоторое числр N сравнений. Концентрация взаимной независимости погрешностей квантования последовательных отсчетов приводит к результату, определяемому центральной предельной теоремой теории вероятностей - закон распределения стремится к нормальному, а погрешность 8 для N сравнений составляет ,/N, S, - среднеквадратическое отклонение одного сравнения. Время Тя, необходимое для получения заданной погрешности, равно ,(4) где -t - время одного сравнения. Цель изобретения - повышение быстродействия при заданной погрешности измерения. Указанная цель достигается тем, что в устройство для определения действующего значения сигнала, содержащее регистратор, блок масштабирования, вход которого является входом устройства, выход блока масштабирования соединен с первым информационньи входом первого вычислительного блока, второй информационньй вход которого подключен к выходу источника постоянного напряжения, первьй и второй управляюпще входы первого вычислительного блока соответственно подключены к первым выходам первой и второй групп выходов генератора псевдослучайных чисел, a вход синхронизации подключен к первому выходу генератора тактовых импульсов, второй выход Которого соединен с входом генерато ра псевдослучайных чисел,введены накапливающий сумматор, блок постоянной памяти, счетчик переноса, пер вый и второй регистры сдвига, сумматор по модулю два, одноразрядный cyJkiMaTop, мультиплексор, триггер переноса, блок извлечения квадрат- ного корня и (т-1) вычислительных блоков, вторые информационные входы которых объединены и подключены к выходу источника постоянного напряжения, а первые информационные входы объединены и подключены к выходу блока масштабирования, первый и. второй управляющие вхоДы -го вычислительного блока (где -i 2,.,., Vn) соответственно подключены к -м выходам первой и второй групп выходов генератора псевдослучайных чисел, входы синхронизации вычислительных блоков, кроме первого, объединены и подключены к первому выходу генератора тактовых импульсов вьрсоды прямого и дополнительного кодов вычислительных блоков соединены с соответствующими входами на капливающего сумматора, выход кото рого через счетчик переноса соединен с информационным входом первого регистра сдвига, вход записи ко торого объединен с информационным входом мультиплексора и подлючен к первому разрядному выходу блока постоянной памяти, второй разрядны выход которого соединен .с входом сдвига первого регистра сдвига, входом синхронизации триггера пере носа и входом второго регистра сдвига, выход первого регистра сдвига соединен с первым входом су матора по модулю два, второ вход которого объединен с управляющим входом мультиплексора и подключен к третьему разрядному выходу блока постоянной памяти, адресный вход которого подключен к первому выход генератора тактовых импульсов, выход сумматора по модулю два соединен с первым входом одноразрядного сумматора, второй и третий входы которого соединены соответственно выходом младшего разряда второго регистра сдвига и информационным выходом триггера переноса, единич1 6 ный и нулевой установочные входы которого подключены к соответствующим выходам мультиплексора, вькод , переноса одноразрядного сумматора соединен с информационным входом триггера, выход одноразрядного сумматора соединен с входом старшего разряда второго регистра сдвига, разрядные выходы которого соединены с соответствуюшлми входами блока извлечения квадратного корня, выход которого соединен с входом регистратора. Вычислительный блок содержит цифроаналоговьй преобразователь, сумматор, первый и второй компара торы, элемент НЕ, первую и вторую группы элементов И, выходы которых являются соответственно выходами дополнительного и прямого кодов блока, первые входы первой группы элементов И объединены и подключены к выходу элемента НЕ, вход которого соединен с выходом первого компаратора,а вторые входы первой группы элементов И объединены и являются первым управляющим входом блока, первые входы второй группы элементов И объединены и подключены к выходу второго крмпаратора, а вторые входы второй группы элементов И объединены с входом цифдрраналогового преобразователя и яв.ляются вторым управляющим входом блока, первые информационные входы компараторов объединены и являются первым информационным входом блока, второй информационный вход первого компаратора подключен к выходу сумматора, управляющие входы компараторов объединены и являются входом синхронизации блока, второй информационньй вход второго- компаратора объединен с первым входом сумматора и подключен к выходу цифроаналОгового преобразователя, второй вход сумматора является вторым информационным входом блока. На фиг,1 представлена блок-схема устройства; на фиг.2 - функция передачи информации в устройстве; на фиг,3 - весовая функция; на фиг.4 компоненты весовой функции; на фиг.5 - спектры компонентов весовой функции. Устройство (фиг,1) содержит источ-: ник 1 постоянного напряжения, генератор2 псевдослучайных чисел, генеатор 3 тактовых импульсов, блок 4 масштабирования, вычислительные бло ки , сумматор 6, счетчик 7 переноса, первый регистр 8 сдвига, бл 9 постоянной памяти, сумматор 10 по модулю два, мультиплексор 11, одноразрядный сумматор 12, триггер 13 п реноса, второй регистр 14 сдвига, блок 15 извлечения квадратного корня, регистратор 16. Вычислительный блок 5 содержит сумматор 17, цифроаналоговый преобразователь 18, первый 19 и второй 20 компараторы элемент НЕ 21, первую и вторую группы элементов И 22 и И 23. Источник 1 постоянного напряжения предназначен для формирования постоянного напряжения минус q. Генератор 2 псевдослучайных чисел (ПТЧ) предназначен для формирования m групп псевдослучайных последовательностей. Выходные сигналы ГПЧ представляют собой прямые и дополнительные (,) параллельные коды псевдослучайных чисел ЗJ. Генератор 3 тактовых импульсов фор ирует импульсы, сдвинутые один относительно другого на 180 . Вычислительный блок 5 предназначен для формирования вспомогательных сигналов и сравнения выходного сигнала блока 4 масштабирования и вспомогательных сигналов с сумматора 17 и цифроаналогового преобразователя 18 с последующей обработкой результатов сравнения на группа элементов И 22 и И 23. Цифроаналоговый преобразователь 18 вьтислительного блока формирует псевдослучайные последовательности Группы элементов И 22 и И 23 вы числительного блока выполняют умножение соответственно дополнительных (1-) и прямых (j.) псевдослучайных чисел и сигналов с выходов .соответствующих компараторов 19 и 2 Накапливающий сумматор предназна чен для суммирования и накопления выходных сигналов вычислительных блоков. Счетчик 7 переноса предназначен для накопления сигналов переполнения накапливающего сумматора 6. Регистр 8 сдвига предназначен для переписи состояния счетчика 7 переноса и сдвига информации под действием тактовых импульсов с раз 218 рядного выхода блока 9 постоянной памяти. Блок 9 постоянной памяти предназначен для формирования управляющих сигналов под действием тактовых импульсов с выхода генератора 3 тактовых импульсов. Триггер 13 переноса предназначен для хранения сигнала переноЬа с выхода одноразрядного .сумматора 12. Регистр 14 сдвига предназначен для хранения второго слагаемого, поступающего на вход одноразрядного сумматора 12, и результата суммирования . Предлагаемое устройство работает следуюпщм образом. Измеряемый сигнал x(t) в блоке.4 масштабирования приводится к требуемому масштабуi приобретает вид x(t)е ( и поступает на соответствующие информационные входы компараторов 19 и 20, на управляющие входы которых поступают стробирующие импульсы с соответствукяцего выхода генератора 3 тактовых импульсов (ГТИ). Импульсы с другого выхода ГТИ 3, сдвинутые относительно сигнала с прёдьщущего выхода на 180, поступают на вход ГПЧ 2. На выходах первой и второй групп выходов ГПЧ 2 формируются параллельные прямые коды ГУ; параллельные дополнительные коды (). Здесь е Со, . ()eCO,,N, где N - количество сравнений за интервал измерения Т. На выходе ЦАП 18 формируется псевдослучайная последовательность Q tf COjnlj которая поступает на сосоответствующий информационный вход компаратора 19 и на первый вход Ъумматора 17. Источник 1 постоянного напряжения формирует отрицательное напряжение -q, которое на сумматоре 17 суммируется с сигналом q , в результате чего на соответствующий информационный вход компаратора 19 поступает напряжение -q (1 -f.,) . После каждого тактового импульса, поступающего на вход ГПЧ 2, происходит смена прямых и дополнительных кодов на выходах первой и второй групп. В моменты поступления сигналов на управляющие входы компараторов 19 и 20 происходит сравнение входного программированного сигнала ,+п и вспомогательных сигналов -q(1-F;j) и q При этом результаты сравнения п.., и пя,,, поступают К соответственно на входы первой и вт рой групп элементов И 22 и 23, на другие входы которых поступают дополнительный код ()(); Го 1 и прямой ,1 . . Значения сигналов на выходах эле мента НЕ 21 и компаратора 20 имеют вид. n, если x(t)-q(1- ); O, если x(t)-q(lL..); у ч -ЛЙ1 - 4Д „ - Г1. если x(t)J 21I( to, если x(t)q|. Ha выходах групп элементов И 22 и И 23 вычислительных блоков 15 фор мируются сигналы 2:,, : 2ЛК §Vi В результате работы вычислительных блоков 15.-5 на входь накапливающего сумматора поступают слагаемые z,, 2,-2, zj. С вькода на капливающего сумматора 6 сигнал пер полнения поступает на вход счетчика 7 переноса. В конце интервсша измерения Т в счетчике 7 переноса и накапливаймцем сумматоре 6 накапливается величина, пропорциональная мощности РХ входного сигнала x(t). Оценка Р определяется вьфажением 2( М - символ математического ожидания Учитывая, что выходные сигналы . равномерно распределенные случайные последовательности выражение (5) запишем в вид ,lmi:z2,,l. Принима;я во взимание, что f (х) плотность распределения входного си нала, x(t) ,+qJ, а 1/q - плот ность распределения равномерно распределенных величин ,+q и -q() определим оценку Р , () +М П2, кЫ f (х) I .(1-.,) 1 /q d( 1 I X ;-,)dx+J f(x) J f 1/q d,.dx . 110 .0CV 1/2q x2f(x)dx+1/2qj x2f(x)dx -Vо 1/qJ x2f(x)dx 1/q P . . -K Таким образом, величина 1 /q Pj( , пропорциональная мощности входного сигнала, накапливается в накапливающем сумматоре 6 и счетчике 7 переносаВ процессе первичного накопления информации на накапливающем сумматоре 6 и счетчике 7 переноса происходит вторичное суммирование на одноразрядном сумматоре 12, причем на интервале времени 0-T/2j. На интервале т/2-Tj суммирова- кие осуществляется с отрицательным знаком. Работа одноразрядного сумматора поИсх од ит следующим образом. На соответствующем разрядном выходе блока 9 постоянной памяти на интервале p-T/2J формируется нуль, поступающий на сумматор 10 по модулю два и мультиплексор 11. По истечении каждых е импульсов b соответствующего выхсша ГТИЗ на соответствующем разрядном выходе блока 9 постоянной памяти формируется импульс записи информации из счетчика 7 переноса в регистр 8 сдвига Этот .же импульс проходит через мультиплексор 11 и устанавливает триггер 13 переноса в нулевое состояние. После каждой перезаписи информации из счетчика 7 переноса в регистр 8 сдвига на соответствующем выходе блока 9 формируется пакет импульсов, которые являются импульсами сдвига для регистров 8 и 14 сдвига и импульсами синхронизации для триггера 13 переноса , при этом состояние регистра 8 сдвига в последовательна коде через сумматор 10 по модулю два суммируется с состоянием регистра 8 сдвига на одноразрядном сумматоре 12, а результат суммирования записывается в регистр 14 сдвига. На интервале времени т/2-Tj на соответствующем разрядном выходе блока 9 постоянной памяти формируется единица, поступающая на входы сумматора 10 по модулю два и мультиплексора 11. По истечении каждых б стробирующих импульсов состояние счет-, чика 7 переноса через регистр 8 II сдвига и мультиплексор 11 позволяет устачовить триггер 13 переноса в единичное состояние. После перезаписи состояния счетчика 7 переноса в регистр 8 сдвига под действием сигналов с соответствующего разрядного выхода блока 9 состояние регистра 8 сдвига инвертируется на сумматоре 10 по модулю два и, учитьгоая единичное состояние триггера 13 переноса в начале цикла сдвига., в последоват,ельном коде вычитается из состояния регистра 14 сдвига. Таким образом,.информация, пропорциональная мощности входного сиг нала, накапливается на накапливающем сумматоре 6, а текущее значение состояния накапливающего сумматора на интервале O-T/Z) накапливается на регистре 14 сдвига с положительным знаком, а на интервале т/2-тЗ с отрицательньм знаком, причем накопление на регистре 14 сдвига имее характер выборок через каждые е сум мирований. Для удобства вычислений интервал р-тЗ представим в виде JJ-T/2-T/23. Проведение преобразования.описывается вьфажением vr/Z t.12 Ut-Te V C di-ilSit-iTe -Т|2 -TIZ-Т/2 XJ Pxlt dtiii, количество суммировани в первом сумматореJ интервал между выборка ми регистра 14 сдвига Т T/L,I.N/e-количество суммироваНИИ на одноразрядном сумматоре 12( ;H-L|eij442MVuV Из (6) ViJflrntMTe j P, it-jTe)j P,rOdi -TU-TI2 -1,2 s(b;TB)-eH-jTe) CW1i,Jt . ; -TU-T/2 Вьфажение в квадратных скобках представим в виде производства некоторой функхщи q(t) - чт)г .7% .т/г P. ) Щ PxrOdca lP U a-iJq t), (3 -T|2 -T/24 1 приняв X VcJtUi aW v И проинтегрировав (7) по частям получим .t т/2 Tf2 )lp()-j ((j)dj. (О -кг ст/2 -1/2 Проанализируем функции q(t) и q(t):, q(t)-L - дельта-пункция (фиг.2); т/2- . . )j (it)Jt t - ступенчатая тре- -1)2 угольная функция у.,- . (фиг. 3). ция (фиг.З). Учитывая, что q(-T/2)0 и q(T/2) 0, выражение (8) принимает вид 1г . . С Таким образом, на интервале Т информация Pjj(t), поступающая на вход накапливающего сумматора 6, проходит преобразование ца элементах 7-:14 и с регистра 14 сдвига поступает на блок .15 извлечения квадратичного корня. Преобразование (9) представим как интегрирование в пределах -Т/2-Т/2 с весовой функцией q(t) (фиг.З). Для оценки фильтрующих свойств весовой функции q(t необходимо определить ее спектральную характеристику G(ti))Frq(t)l . Функцию q(t) можно представить в виде свертки двух простых компонентов q(t)q(t)q2(t), (10) Х-- операция свертки q(t)2/U( ,...,-1,0, +,.«.,+М, , т.е. L/2 дельта-функЦия площадью 2/L с интервалом Тg (фиг.4й), /tV-f / i -T/4 tiT/4, иначе прямоугольник высотой 2/Т, длительностью Т/2 (фиг.4 Б). Учитывая (10) и теорему Бореля А можно записать (11) G(a) G,(u) )j G,(co)F|;q,(t) ; G2()(t)5 ; 05 ,„ , WTft 0. -jcot,SinU-Tq,( 2|Lle e 8a-iTe).i CU/2)5in(WTgfl)

ее . . TI4. . ,

- w.. , f (w)2|TJ

ЫТ /4dt-2/т e jt WT/4

- -TMчитывая (11) запишем OJTg

5in L 9 inMT/j.

Oa)

coTf-r

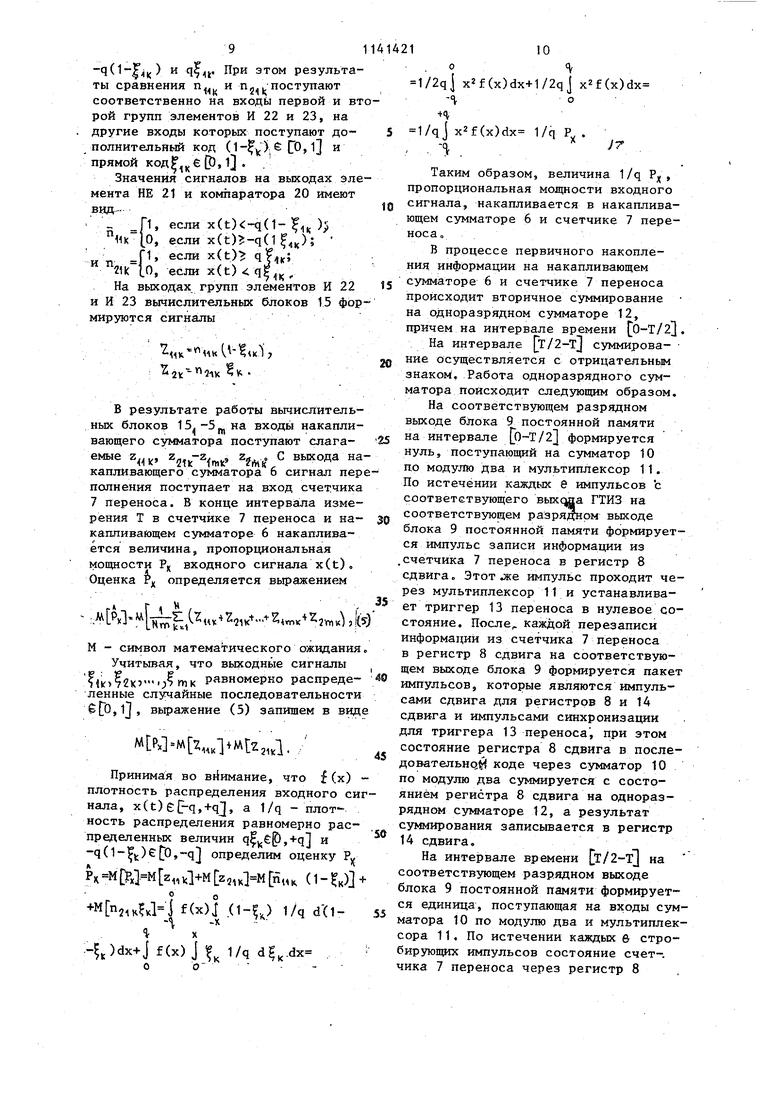

Йгз,.() :.Сомножители |о, (fit)) и (w)) спект ральной характеристики G(u)) показан на фиг.5 а ,S соответственно. . Огибающая |П „(&))) затухает по закону 4/сОТ 2/ Т. Огибающая ln/(w)|/ является периодической функцией частоты с периодом l/Tg (частота вы борок) и на отрезке частоты 0-1/2Tg затухает по закону 4/QTgL 2/«fT. Вы берем частоту выборок , для которой на частоте 1/2Те затухание 1С2О)( firt - допустимая погрешность преобразования, тогда для частот Tg спектральная характеристика G(CJ), а значит погрешност преобразования меньше допустимой. В области низких частот на отрезке частот 0-1/2 Tg огибающа я спектраль ной характеристики JQ(oJ)) , а значит погрешность преобразования 8 , равн произведению огибающих iG, ((о)1 и 02(М)1 , Определим время измерения при вычис лении эффективного значения гармонического сигнала x(t)A ) . Учитьшая удвоение частотпри возведении сигнала в квадрат или сигна ла x4t) 1/2(1-cos2Gjt), ). (15) Сравним (2) и (15) при заданной погрешностиТ,. (16) Учитывая, i 1 увеличение быстродействия за счет дополнительной обработки на элементах 14-21 существенное: напримерj для S 0,1% . Оценим увеличение быстро действия за счет введения (гя-1) вычислительных блоков. ИспользоваU

ниё дополнительных квантователей дает возможность увеличить количество сравнений в m раз.

В известном устройстве погрешность преобразования как функция количества отсчетов определяется выражением (3). В предлагаемом устройстве. Время T, необходимое для достижения заданной погрешности, для из- вестного устройства определяется из (4), В предлагаемом устройстве при 5jj количество сравнений N/m, при этом время измерения 1 fjf Т тН Сравним (4) и (18): выигрьпи в быстродействии в ш раз . Необходимое количество вычислительных блоков определяется из условия Определим время измерения Т и количество hi вычислительных блоков при частоте входного сигнала Гц и погрешности преобразования ,05%. Из (15) время измерения для подавления низкочастотной погрешности(и10- |с,0005ч1,5 с. Из 1(17) погрешность для Nm отсчетов ;8,.8,/4Ти; о, - погрешность OArforo отсчета (сравнения). Для данного метода измерения S(q/2 Чз, q - ступень квантования. ля данного устройства q определяет пикфактор и реально q44. Из (17) общее количество сравнений для m параллельных вычислительных блоков н4/5„(4/2-4з0,0005) 5,3-10. Время измерения Т при времени установления НАЛ , и mN 5 3 Ю. ,,3 с. ля достижения необходимо 4, при этом - - Т, 1,3 с

i

h

JL ff

M

92ii)

X

т

. r

T

Uг,t

TeL

/G2(()l

О

Фиг.5

a

Авторы

Даты

1985-02-23—Публикация

1983-04-04—Подача