Изобретение относится к накоплению информации, а именно к устройствам для многоканальной записи аналоговых процессов.

Цель изобретения - уменьшение потребления энергии.

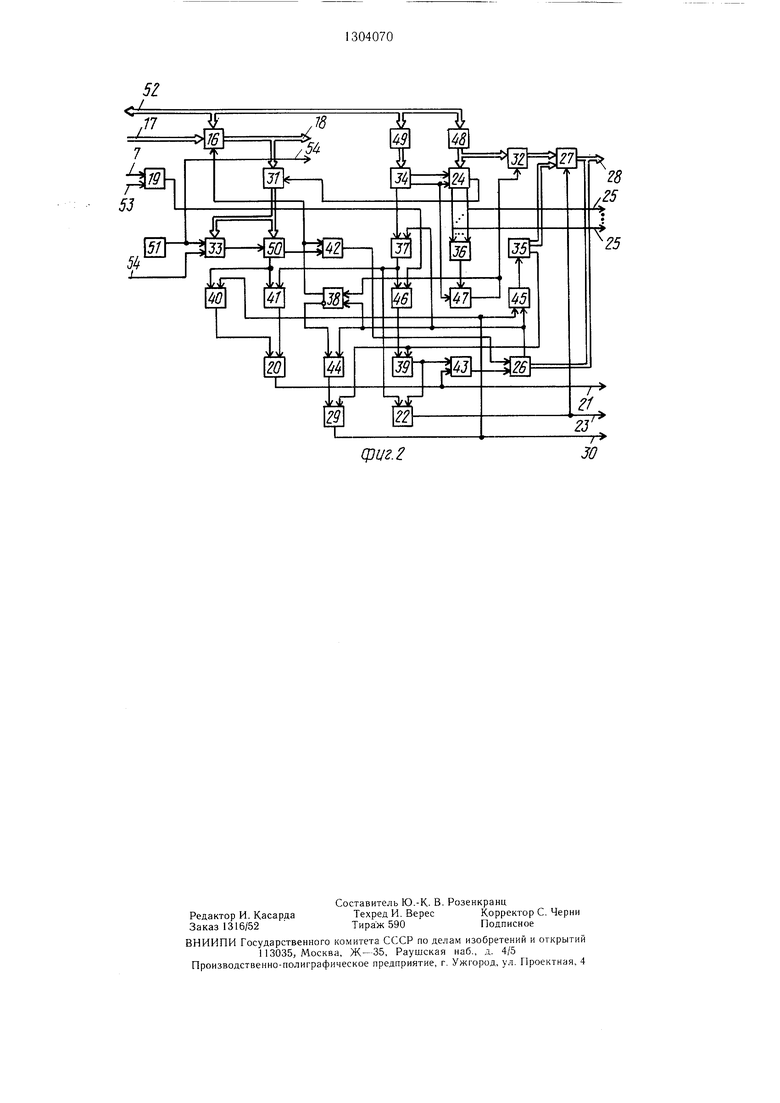

На фиг. 1 изображено устройство для многоканальной записи аналоговых процессов; на фиг. 2 - формирователь управляющих импульсов

блока 10 сравнения, подсоединенного другими информационными входами к выходам второго регистра 12.

Формирователь 6 управляющих импульсов содержит приемо-передатчик 16, подсоединенный первой группой 17 информационных входов к выходам блока 9 памяти и подключенный выходами 18 к информационным входам первого и второго регистров 11 и 12 каждого канала задом канале записи входная шина 4 соединена с информационным входом масштабирующего усилителя 1. Выходы аналого- цифрового преобразователя 2 подключены к информационным входам блока 3 оперативной памяти.

Устройство содержит также мультиплексор 8, подсоединенный информационными входами к выходам блоков 3 оперативной памяти всех каналов записи-, и блок 9 памя20

ключенный выходом 30 к входу записи- считывания блока 9 памяти, первый и второй дополнительные регистры 31 и 32, второй дополнительный мультиплексор 33, треУстройство содержит каналы записи, Q писи, первый элемент ИЛИ 19, подсое- каждый из которых состоит из масщта-диненный первым входом к входной щине 7

бирующего усилителя 1, аналого-цифровогопуска, второй элемент ИЛИ 20, подклюпреобразователя 2, блока 3 оперативнойченный выходом 21 к тактовому входу гепамяти, входной 4 и выходной 5 шины,нератора 13 псевдослучайного сигнала и к

формирователь 6 управляющих импульсов истробирующим входам аналого-цифрового

входную шину 7 пуска. При этом в каж- 15 преобразователя 2 и блока 10 сравнения

каждого канала записи, первый дешифратор 22, соединенный выходом 23 с входом записи-считывания блока 3 оперативной памяти каждого канала записи, второй дешифратор 24, подключенный выходами к входам 25 записи первого и второго регистров 11 и 12 каждого канала записи, первый счетчик 26 и первый дополнительный мультиплексор 27, соединенные выходами 28 с управляющими входами муль- ти. Каждый канал записи в нем снаб- 25 типлексора 8 и с адресными входами бло- жен блоком 10 сравнения, соединенным вы- ка 9 памяти, первый триггер 29, подходом с выходной шиной 5, первым регистром 11, подключенным выходами к управляющим входам масштабирующего усилителя 1, вторым регистром 12, генератором 13 псевдослучайного сигнала, цифро- 30 тий дешифратор 34, второй счетчик 35, тре- аналоговым преобразователем 14 и анало- тий элемент ИЛИ 36, второй, третий и чет- говым сумматором 15. Формирователь 6 уп- вертый триггеры 37-39, первый, второй, равляющих импульсов подсоединен входами третий, четвертый, пятый, шестой, седьмой к входной шине 7 пуска и к выходам бло- и восьмой элементы И 40-47, первый ка 9 памяти и соединен выходами с инфор- и второй приемники 48 и 49, делитель 50 час- мационными входами и входами записи пер- 35 тоты, генератор 51 тактовых импульсов, ши- вого и второго регистров 11 и 12 каждого ну 52 данных, шину 53 пускового сигна- канала записи, тактовым входом генератора 13 псевдослучайного сигнала каждого канала записи, стробирующими входами аналого-цифрового преобразователя 2 и бло--, ,- -г-г ---ка 10 сравнения каждого канала записи, приемо-передатчика 16, подключенного выхо- входами записи-воспроизведения блоков 3 дами к информационным входам первого оперативной памяти всех каналов записи, дополнительного регистра 31,подсоединенно- управляющими входами мультиплексора 8, го входом записи к второму дешифратору входом записи-воспроизведения и адресными 24. Первый дополнительный регистр 31 входами блока 9 памяти, подсоединенного 45 подключен выходами к управляющим входам информационными входами к выходам муль- делителя 50 частоты и к управляющим типлексора 8.входам второго допапнительного мультиплекВ каждом канале записи выходы генера- сора 33, который соединен первым и вто- тора 13 псевдослучайного сигнала подклю- рым информационными входами соответ- чены к адресным входам блока 3 опера- ственно с выходом генератора 51 такто- тивной памяти и к входам цифроаналого- ЗО вых импульсов и шиной 54 сигнала дис- вого преобразователя 14, соединенного выхо- кретизации и подсоединен выходом к так- дом с первым входом аналогового сумма- товому входу делителя 50 частоты, тора 15. При этом аналоговый сумматор 15Делитель 50 частоты подключен первым

подсоединен вторым входом к выходу мае- выходом к первым входам первого и вто- штабирующего усилителя 1 и подключен рого элементов И 40 и 41 и соединен выходом к информационному входу анало- 55 вторым выходом с первым входом тре- го-цифрового преобразователя 2, соединен- тьего элемента И 42. Третий элемент И 42 ного выходами с информационными входами подключен выходом к первому входу перла и шину 54 сигнала дискретизации.

Шина 52 даннь х соединена с входами первого и второго приемников 48 и 49 и второй группой информационных входов

блока 10 сравнения, подсоединенного другими информационными входами к выходам второго регистра 12.

Формирователь 6 управляющих импульсов содержит приемо-передатчик 16, подсоединенный первой группой 17 информационных входов к выходам блока 9 памяти и подключенный выходами 18 к информационным входам первого и второго регистров 11 и 12 каждого канала заключенный выходом 30 к входу записи- считывания блока 9 памяти, первый и второй дополнительные регистры 31 и 32, второй дополнительный мультиплексор 33, трекаждого канала записи, первый дешифратор 22, соединенный выходом 23 с входом записи-считывания блока 3 оперативной памяти каждого канала записи, второй дешифратор 24, подключенный выходами к входам 25 записи первого и второго регистров 11 и 12 каждого канала записи, первый счетчик 26 и первый дополнительный мультиплексор 27, соединенные выходами 28 с управляющими входами муль- типлексора 8 и с адресными входами бло- ка 9 памяти, первый триггер 29, подтий дешифратор 34, второй счетчик 35, тре- тий элемент ИЛИ 36, второй, третий и чет- вертый триггеры 37-39, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И 40-47, первый и второй приемники 48 и 49, делитель 50 час- тоты, генератор 51 тактовых импульсов, ши- ну 52 данных, шину 53 пускового сигна- -, ,- -г-г ---каждого канала записи, первый дешифратор 22, соединенный выходом 23 с входом записи-считывания блока 3 оперативной памяти каждого канала записи, второй дешифратор 24, подключенный выходами к входам 25 записи первого и второго регистров 11 и 12 каждого канала записи, первый счетчик 26 и первый дополнительный мультиплексор 27, соединенные выходами 28 с управляющими входами муль- типлексора 8 и с адресными входами бло- ка 9 памяти, первый триггер 29, подтий дешифратор 34, второй счетчик 35, тре- тий элемент ИЛИ 36, второй, третий и чет- вертый триггеры 37-39, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И 40-47, первый и второй приемники 48 и 49, делитель 50 час- тоты, генератор 51 тактовых импульсов, ши- ну 52 данных, шину 53 пускового сигна- -, ,- -г-г ---приемо-передатчика 16, подключенного выхо- дами к информационным входам первого дополнительного регистра 31,подсоединенно- го входом записи к второму дешифратору 24. Первый дополнительный регистр 31 подключен выходами к управляющим входам делителя 50 частоты и к управляющим входам второго допапнительного мультиплекла и шину 54 сигнала дискретизации.

Шина 52 даннь х соединена с входами первого и второго приемников 48 и 49 и второй группой информационных входов

t5

вого счетчика 26, соединенного вторым входом с выходом четвертого элемента И 43, и подсоединен к первым входам пятого и шестого элементов И 44 и 45 и второго триггера 37 и к первому входу третьего триггера 38.

Третий триггер 38 соединен прямым выходом с управляющим входом приемопередатчика 16 и с вторым входом третьего элемента И 42 и подключен инверсным выходом к второму входу пятого элемента И 44, подсоединенного выходом к первому входу первого триггера 29.

Первый триггер 29 соединен выходом 30 с вторым входом первого элемента И 40 и вторым входом шестого элемента И 45. Выход шестого элемента И 45 подключен к тактовому входу второго счетчика 35, который подсоединен выходом к второму входу первого триггера 29 и к первому входу четвертого триггера 39, соединенного вторым входом с выходом седьмого элемента И 46. Седьмой элемент И 46 подключен первым входом к выходу первого элемента ИЛИ 19, соединенного вторым входом с шиной 52 пускового сигнала, и подсоединен вторым входом к выходу второго триггера 37, соединенному с первым входом первого дешифратора 22 и вторым входом второго элемента И 41.

Выход второго элемента И 41 подключен к первому входу второго элемента ИЛИ 20, который подсоединен вторым входом к выходу первого элемента И 40 и соединен выходом 21 с первым входом четвертого элемента И 43. Второй вход четвертого элемента И 43 подсоединен к выходу четвертого триггера 39, подключенному к второму входу первого дешифра- 35 тора 22, соединенного выходом 23 с управ- ляюш,им входом первого дополнительного мультиплексора 27.

Информационные входы первого дополнительного мультиплексора 27 подсоединены к

Каналы записи, мультиплексор 8, блок 9 памяти и формирователь 6 управляющих импульсов образуют группу 55 каналов за писи в многоканальной системе (фиг. 1) Эта многоканальная система содержит ряд 5 групп 55 каналов записи и объединяющий их блок 56 управления, состоящий из пуль та управления, формирователя импульсов дешифратора и приемо-передатчика, соеди ненного с шиной 52 данных с общей вы 0 ходной шиной. При этом выходные шины 5 входят в шину 53 пускового сигнала.

Многоканальная запись аналоговых про цессов посредством предлагаемого устройст ва осуш,ествляется следующим образом.

В каждом канале записи подлежащий за писи сигнал, поступающий по входной щине 4, проходит через масщтабирующий усили тель 1 на аналоговый сумматор 15. На последний подается также результат преобразования псевдослучайных чисел генератора 13 псевдослучайного сигнала цифро- аналоговым преобразователем 14. Суммарный сигнал с аналогового сумматора 15 подается на аналого-цифровой преобразователь 2, который производит его квантование.

Результат квантования сравнивается в блоке 10 сравнения с заданным кодом уровня пуска. Если результат квантования пре- выщает заданный код уровня пуска, то блок 10 сравнения вырабатывает импульс пуска, поступающий по выходной шине 5 на шину 53 пускового сигнала. Импульс пуска поступает на формирователь 6 управляющих импульсов, в котором он через первый элемент ИЛИ 19 и седьмой эле.мент И 46 устанавливает четвертый триггер 39 в единичное состояние.

Четвертый триггер 39 вырабатывает сигнал, который через четвертый элемент И 43 поступает на первый счетчик 26, а через первый дешифратор 22 воздействует на блок 3 оперативной памяти. При это.м результат квантования с аналого-цифрового

20

25

30

другим выходам второго счетчика 35 и к преобразователя 2 заносится в блок 3 опевыходам второго дополнительного регистра 32, соединенного входом записи с выходом восьмого элемента И 47, подключенным к второму входу третьего триггера 39, и подративной памяти. Первый счетчик 26 подсчитывает тактовые импульсы и сбрасывает второй триггер 37 в нулевое состояние, когда число тактовых и.мпульсов стасоединенного информационными входами к новится равным длине выборки блока 3

выходам первого приемника 48, соединенный с первой группой входов второго дещифратора 24.

Выходы второго дешифратора 24 подсоединены через третий элемент ИЛИ 36 к

оперативной памяти.

Одновременно с установкой в нулевое состояние второго триггера 37 происходит установка в единичное состояние первого триггера 29. Это разрешает прохождение

первому входу восьмого элемента И 47. 50 импульсов через второй элемент ИЛИ 20

Третий дешифратор 34 подсоединен входами к выходам второго приемника 49 и соединен выходами с второй группой входов второго дещифратора 24 и вторыми входами второго триггера 37 и восьмого элемента И 47. При этом выход генератора 51 тактовых импульсов соединен с шиной 54 сигнала дискретизации.

на все каналы записи. При этом на блоки 3 оперативной памяти с первого дешифратора 22 подается сигнал, соответствующий считыванию. Последнее приводит к перезаписи из блока 3 оперативной 55 памяти каждого канала записи в блок 9 памяти. При этом второй счетчик 35 определяет канал записи, а первый счетчик 265

Каналы записи, мультиплексор 8, блок 9 памяти и формирователь 6 управляющих импульсов образуют группу 55 каналов записи в многоканальной системе (фиг. 1). Эта многоканальная система содержит ряд 5 групп 55 каналов записи и объединяющий их блок 56 управления, состоящий из пульта управления, формирователя импульсов, дешифратора и приемо-передатчика, соединенного с шиной 52 данных с общей вы- 0 ходной шиной. При этом выходные шины 5 входят в шину 53 пускового сигнала.

Многоканальная запись аналоговых процессов посредством предлагаемого устройства осуш,ествляется следующим образом.

В каждом канале записи подлежащий записи сигнал, поступающий по входной щине 4, проходит через масщтабирующий усилитель 1 на аналоговый сумматор 15. На последний подается также результат преобразования псевдослучайных чисел генератора 13 псевдослучайного сигнала цифро- аналоговым преобразователем 14. Суммарный сигнал с аналогового сумматора 15 подается на аналого-цифровой преобразователь 2, который производит его квантование.

Результат квантования сравнивается в блоке 10 сравнения с заданным кодом уровня пуска. Если результат квантования пре- выщает заданный код уровня пуска, то блок 10 сравнения вырабатывает импульс пуска, поступающий по выходной шине 5 на шину 53 пускового сигнала. Импульс пуска поступает на формирователь 6 управляющих импульсов, в котором он через первый элемент ИЛИ 19 и седьмой эле.мент И 46 устанавливает четвертый триггер 39 в единичное состояние.

Четвертый триггер 39 вырабатывает сигнал, который через четвертый элемент И 43 поступает на первый счетчик 26, а через первый дешифратор 22 воздействует на блок 3 оперативной памяти. При это.м результат квантования с аналого-цифрового

0

5

0

преобразователя 2 заносится в блок 3 оперативной памяти. Первый счетчик 26 подсчитывает тактовые импульсы и сбрасывает второй триггер 37 в нулевое состояние, когда число тактовых и.мпульсов стаоперативной памяти.

Одновременно с установкой в нулевое состояние второго триггера 37 происходит установка в единичное состояние первого триггера 29. Это разрешает прохождение

импульсов через второй элемент ИЛИ 20

на все каналы записи. При этом на блоки 3 оперативной памяти с первого дешифратора 22 подается сигнал, соответствующий считыванию. Последнее приводит к перезаписи из блока 3 оперативной 55 памяти каждого канала записи в блок 9 памяти. При этом второй счетчик 35 определяет канал записи, а первый счетчик 26

;1лнпу fii i6opKH каждого канала записи. По OKOiinaiiiiii перезаписи второй счетчик 35 сбрасьшает первый и четвертый триггеры 29 и 39 Л liv- eiioe состояние.

При считывании результата записи адре- сованная команда считывания через второй приемник 49 поступает на третий дешифратор 34, разрешающий работу второго депшф- ратора 24. Последний формирует сигнал, который через третий элемент ИЛИ 36 и вось- мой элемент И 47 устанавливает третий триггер 38 в единичное состояние и обеспечивает запись кода выбранного канала записи во второй регистр 32. Код выбранного Kana;ia записи через первый дополнительный мультиплексор 27 поступает па бл.ок 9 памяти. При этом третий триггер 38 подключает выходы блока 9 памяти через приемо-передатчик 16 к шине 52 данных и обеспечивает прохождение импульсов считывания через третий элемент И 42 па первый счетчик 26, который формирует адрес для блока 9 памяти. По окончании считывания первый счетчик 26 вырабатывает си1-нал, который сбра- ei iuacT третий триггер 38 в нулевое сос- пяннс.

Исп().1ьзован11е предлагаемого устройства lio.fiio. iJiCT 15 зпачите.пьпой степени умень- ,1ить потреб.чение :якфгии в пропеесе заии- Ci и с1П тывания аналоговых процессов.

Формула изобретения

1. Устройство для многоканальной записи аналог овых процессов, содержащее ка- на.|ы записи, каждый из которых состоит из маснп абируюпхего усилителя, аналого- цифрового преобразователя, блока оператив- ной памяти, входной и выходной щин, формирователь управляющих импульсов и входную тину пуска, причем в каждом канале записи входная тина соединена с информационным входом .масщтабируюпдего усилителя, а выходы аналого-цифрового пре- образователя подключены к информационным входам блока онеративной памяти, отличающееся тем, что, с целью уменьшения потребления энергии, в него введены мультиплексор, подсоединенный информационными входами к выходам блоков оперативной памяти всех каналов записи, и блок памяти, а каждый канал записи снабжен блоком сравнения, соединенным выходом с выходной шиной, первым регистром, подключенным выходом к управляющим вхо- ;;;;м масн1табирующего уеилителя, вторым регистром, генератором псевдослучайного сигнала, цифроаналоговым преобразователем и аналоговым сумматором, причем фор- М1 1ователь управляющих импульсов подсоединен входами к входной щице пуска и вы- ходам блока памяти и соединен с информационными входами и входами записи пер

0

5 5

о

5 0 Q 5

5

вого и второго регистров каждого канала записи, с тактовым входом генератора псевдослучайного сигнала каждого канала записи, стробирующими входами аналого-цифрового преобразователя и блока сравнения каждого канала записи, входами записи-воспроизведения блоков оперативной памяти всех каналов записи, управляющими входами мультиплексора, входо.м записи-воспроизведения и адресными входами памяти, подсоединенного информационными входами к выходам мультиплексора, а в каждом канале записи выходы генератора псевдослучайного сигнала подключены к адресным входам блока оперативной па.мяти и входам цифроаналогового преобразователя, соединенного выходо.м с нервы.м входом аналогового сумматора, который подсоединен вторым входом к выходу масштабирующего усилителя и подключен выходом к информационному входу аналого-цифрового преобразователя, соединенного выходами с информационными входа.ми блока сравнения, другие информационные входы которого нод- соединены к выходам второго регистра.

2. Устройство по п. 1, отличающееся тем, что формирователь управляющих импульсов содержит приемо-передатчик, подсоединенный первой группой информационных входов к выходам блока памяти и подключенный выходами к информационным входам первого и второго регистров каждого канала записи, первый элемент ИЛИ, подсоединенный первым входом к входной шине пуска, второй элемент ИЛИ, подключенный выходом к тактовому входу генератора псевдослучайного сигнала и к стробирую- щим входам аналого-цифрового преобразователя и блока сравнения каждого канала заниси, первый дешифратор, соединенный выходом с входом записи-считывания блока оперативной памяти каждого канала записи, второй дещифратор, подключенный выходами к входам записи первого и второго регистров каждого канала записи, первый счетчик и первый дополнительный мультиплексор, соедипенные выходами с управляющими входами мультиплексора и с адресными входами блока памяти, первый триггер, подключенный выходом к входу записи-считывания блока памяти, первый и второй дополнительные регистры, второй дополнительный мультиплексор, третий дешифратор, второй счетчик, третий элемент ИЛИ, второй, третий и четвертый триггеры, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, первый и второй приемники, делитель частоты, генератор тактовых импульсов, шину данных, шину пускового сигнала и шипу сигнала дискретизации, причем шина данных/ соединена с входами первого и второго приемников и второй группой информационных входов приемо-передатчика.

подключенного выходами к информационным входам первого дополнительного регистра, который подсоединен входом записи к второму дешифратору и подключен выходами к управляющим входам делителя частоты и управляющим входам второго дополнительного мультиплексора, соединенного первым и вторым информационными входами с выходом генератора тактовых импульсов и щиной сигнала дискретизации и подсоединенного выходом к тактовому входу делителя частоты, который подключен первым выходом к первым входам первого и второго элементов И и соединен вторым выходом с первым входом третьего элемента И, подключенного выходом к первому входу первого счетчика, второй вход которого соединен с выходом четвертого элемента И, и подсоединенного к первым входам пятого и щес- того элементов И и второго триггера и к первому входу третьего триггера, который соединен прямым выходом с управляющим входом приемо-передатчика и вторым входом третьего элемента И и подключен инверсным выходом к второму входу пятого элемента И, подсоединенного выходом к первому входу первого триггера, выход которого соединен с вторым входом первого элемента И и вторым входом щес- того элемента И, подключенного выходом к тактовому входу второго счетчика, который подсоединен выходом к второму входу первого триггера и к первому входу четвертого триггера, соединенного вторым входом с выходом седьмого элемента И, который подключен первым входом к выходу первого элемента ИЛИ, соединенного вторым входом с шиной пускового сигнала, и подсоединен вторым входом к выходу второго триггера, соединенному с первым входом второго дешифратора и вторым входом второго элемента И, подключенного выходом к первому входу второго элемента ИЛИ, который подсоединен вторым входом к выQ ходу первого элемента И и соединен выходом с первым входом четвертого элемента И, подсоединенного вторым входом к выходу четвертого триггера, подключенному к второму входу первого дещифратора, соединенного выходом с управляющим вхо5 дом первого дополнительного мультиплексора, информационные входы которого подсоединены к другим выходам второго счетчика и к выходам второго дополнительного регистра, который соединен входом записи с выходом восьмого элемента И, подключен0

ным к второму входу третьего триггера.

и подсоединен информационными входами к выходам первого приемника, соединенным с первой группой входов второго дешифратора, выходы которого подсоединены через тре- тий элемент ИЛИ к первому входу восьмого элемента И, а третий дешифратор подсоединен входами к выходам второго приемника и соединен выходами с второй группой входов второго дещифратора и вторыми входами второго триггера и восьмого элемента И.

(рцг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1986 |

|

SU1327174A1 |

| Устройство для многоканальной магнитной записи аналоговых сигналов | 1987 |

|

SU1520582A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2129338C1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1990 |

|

SU1771533A3 |

| Устройство для записи-считывания звуковых сигналов | 1989 |

|

SU1712964A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1985 |

|

SU1272355A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

Изобретение относится к технике на- конления информации и позволяет уменьшить потребление энергии. Подлежащий записи сигнал проходит через масштабирующий усилитель I на аналоговый сумматор 15, куда подается также результат преобразования псевдос.чучайных чисел генератора 13 псевдослучайного сигнала цифроаналоговым преобразователе.м 14. Квантование полученного су.ммарного сигнала подается на аналого-цифровой преобразовате, 1Ь 2. Результат кантования заносится в блок 3 оперативной памяти, туда же с дешифратора подается сигнал, соответствуюш,ий считыванию. Последнее приводит к перезаписи из блока 3 оперативной памяти каждого канала в блок 9 памяти. Один из счетчиков определяет канал записи, другой - длину выборки каждого кана.ча записи. После окончания перезаписи информации от оперативного запоминающего устройства в блок 9 памяти система регистрации отключается от питающей среды, что повышает надежность хранения и исключает влияние помех из сети питания. Дано описание формирователя 6 управляющих импульсов, i з.п. ф-лы, 2 ил. С ЕР (Л со о 4: О ifusi

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Многоканальная система регистрации аналоговых процессов | 1981 |

|

SU951146A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-04-15—Публикация

1985-12-03—Подача