Изобретение относится к автоматике и нычислительной технике и может быть использовано в системах моделирования сложных объектов.

Цель изобретения - повышение точности интегратора,

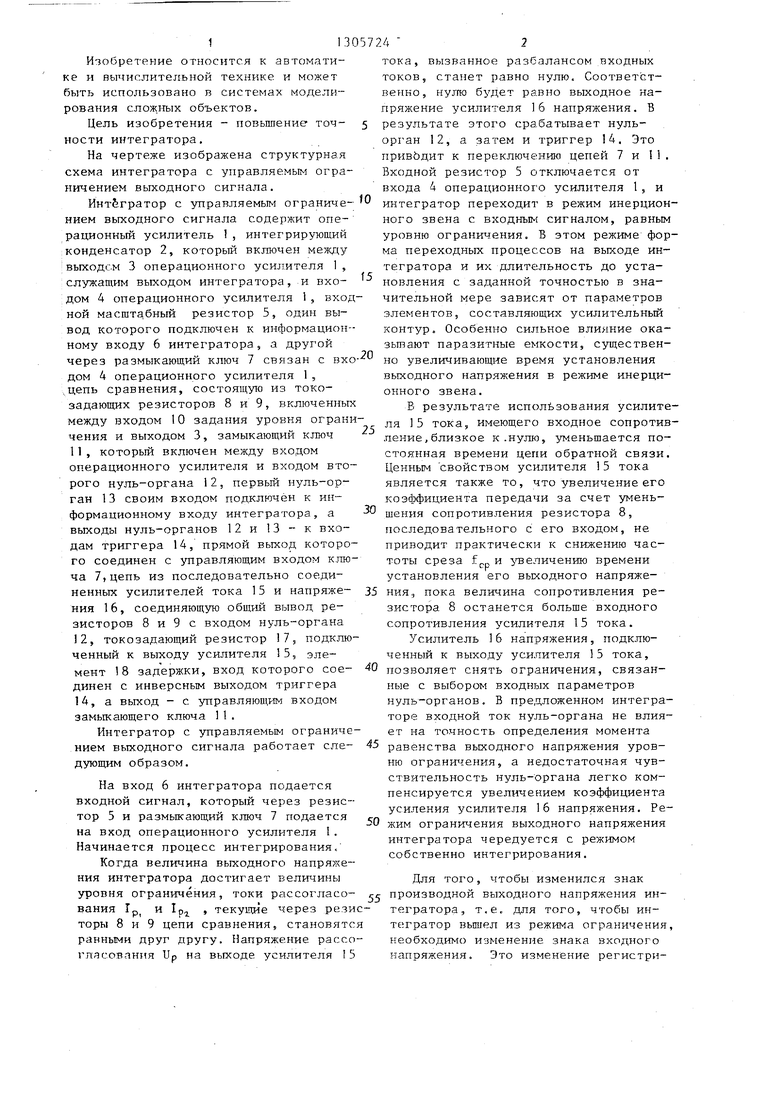

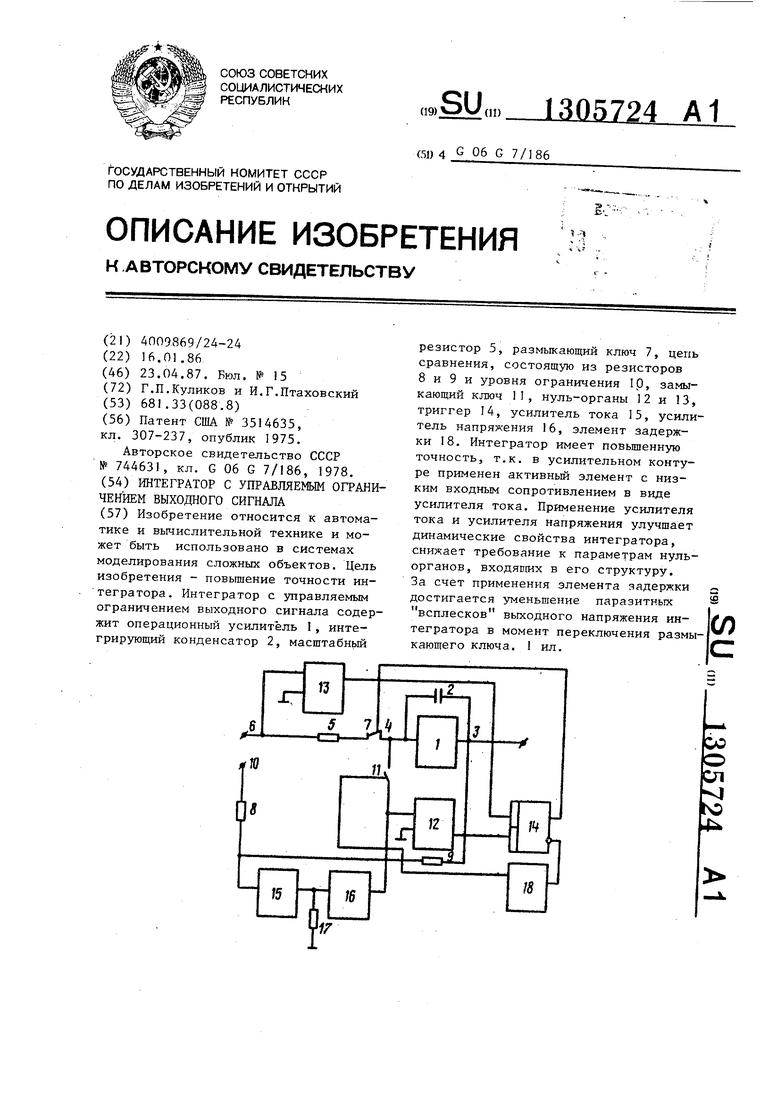

На чертеже изображена структурная схема интегратора с управляемым ограничением выходного сигнала.

тока, вызванное разбалансом входных токов, станет равно нулю. Соответственно, нулю будет равно выходное напряжение усилителя 16 напряжения. В результате этого срабатывает нуль- орган 12, а затем и триггер 14. Это привЬдит к переключению цепей 7 и П. Входной резистор 5 отключается от входа 4 операционного усилителя 1, и

Инт&гратор с управляемым ограниче- интегратор переходит в режим инерционнием выходного сигнала содержит операционный усилитель 1, интегрирующий конденсатор 2, который включен между выходом 3 операционного усилителя 1, служащим выходом интегратора, и БХО- дом 4 операционного усилителя 1, входной масштабный резистор 5, один вывод которого подключен к информацион-- ному входу 6 интегратора, а другой

15

ного звена с входныг Г сигналом, равн уровню ограничения. В этом режиме ф ма переходных процессов на выходе и тегратора и их длительность до уста новления с заданной точностью в зна чительной мере зависят от параметро элементов, составляющих усилительны контур. Особенно сильное влияние ок зьгоают паразитные емкости, существе

-гРП

через размыкающий ключ / связан с вxo но увеличивающие время установления

дом 4 операционного усилителя 1, .цепь сравнения, состоящую из токо- задающих резисторов 8 и 9, включенных между входом 10 задания уровня ограничения и выходом 3, замыкающий ключ 11, который включен между входом операционного усилителя и входом второго нуль-органа 12, первый нуль-орган 13 своим входом подключён к информационному входу интегратора, а выходы нуль-органов 12 и 13 - к входам триггера 14, прямой выход которого соединен с управляющим входом к.гао ча 7,цепь из последовательно соединенных усилителей тока 15 и напряжения 16, соединяющую общий вывод резисторов 8 и 9 с входом нуль-органа 12, токозадающий резистор 17, подключенный к выходу усилителя 15, элемент 18 зад ержки, вход которого соединен с инверсным выходом триггера 14, а выход - с управляюа,им входом замыкающего ключа 11.

Интегратор с управляемым ограничением выходного сигнала работает следующим образом.

На вход 6 интегратора подается входной сигнал, который через резистор 5 и размыкающий ключ 7 подается на вход операционного усилителя I. Начинается процесс интегрирования.

Когда величина выходного напряжения интегратора достигает величины уровня ограничения, токи рассогласования Гп и I

/j

Рг

текущие через резисторы 8 и 9 цепи сравнения, становятся ранными друг другу. Напряжение рассогласования Up на выходе усилителя 15

тока, вызванное разбалансом входных токов, станет равно нулю. Соответственно, нулю будет равно выходное напряжение усилителя 16 напряжения. В результате этого срабатывает нуль- орган 12, а затем и триггер 14. Это привЬдит к переключению цепей 7 и П. Входной резистор 5 отключается от входа 4 операционного усилителя 1, и

интегратор переходит в режим инерцион

ного звена с входныг Г сигналом, равным уровню ограничения. В этом режиме форма переходных процессов на выходе интегратора и их длительность до установления с заданной точностью в значительной мере зависят от параметров элементов, составляющих усилительный контур. Особенно сильное влияние ока- зьгоают паразитные емкости, существен

5

-

35

40

45

50

выходного напряжения в режиме инерционного звена.

В результате использования усилителя 15 тока, имеющего входное сопротивление, близкое к .нулю, уменьшается постоянная времени цепи обратной связи. Ценным свойством усилителя 15 тока является также то, что увеличение его коэ(3зфициента передачи за счет уменьшения сопротивления резистора 8, последовательного с его входом, не приводит практически к снижению частоты среза fpp и тзеличению времени установления его выходного напряжения, пока величина сопротивления резистора 8 останется больше входного сопротивления усилителя 15 тока.

Усилитель 16 напряжения, подключенный к выходу усилителя 15 тока, позволяет снять ограничения, связанные с выбором входных параметров нуль-органов. В предложенном интеграторе входной ток нуль-органа не влияет на точность определения момента равенства ВЬЕХОДНОГО напряжения уровню ограничения, а недостаточная чувствительность нуль-органа легко компенсируется увеличением коэффициента усиления усилителя 16 напряжения. Режим ограничения выходного напряжения интегратора чередуется с режимом собственно интегрирования.

Для того, чтобы изменился знак /j производной выходного напряжения интегратора, т.е. для того, чтобы ин- те .гратор вьшел из режима ограничения, необходимо изменение знака входного напряжения. Это изменение регистри313

руется нуль-органом 13. После переключения нуль-органа 13 срабатывает триггер 14, и интегратор переходит в режим интегрирования. При этом усилительный контур, образующий инер- ционное звено, размыкается с помощью ключа 11. Входной резистор 5, задающий интегрирующий ток, который перезаряжает конденсатор 2, с помощью ключа 7 подключается к суммирующей точке 4 операционного усилителя 1. Благодаря элементу 18 задержки устраняются паразитные всплески выходного напряжения интегратора вследствие действия заряда переключения ключа 7

Интегратор в таком исполнении обладает повьшенной точностью в обоих режимах работы - в режиме ограничения выходного напряжения и в режиме собственно интегрирования. Сокращается время установления переходных процессов в режиме ограничения, так как в усилительном контуре применен активный элемент с низким входным со- - противлением в виде усилителя тока. Уменьшая влияние паразитных емкостей усилитель тока способствует скорейшему успокоению переходных процессов с заданной степенью точности, и тем самым повьш ается точность интеграто- ра. Применение в усилительном контуре усилителя напряжения снимает высокие требования к входным параметрам нуль-органа, регистрирующего рассогласование между выходным напря- жением интегратора и уровнем его сигнала ограничения.

Точность предложенного интеграто- тора повьш1ается за счет того, что устраняются паразитные всплески выходного напряжения интегратора за счет действия заряда переключения его размыкающего ключа, Это происходит вследствие того, что управляющий сигнал другого замыкающего ключа форми-

Редактор В.Данко

Составитель Т.Толстоброва

Техред Л. Сердюкова Корректоре. Черни.

Заказ 1455/49 Тираж 673Подписное

- ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

244

руется элементом задержки и у,иер:кивл ет ключ в замкнутом состояини псе то время, которое отводится на переключение размыкающего ключа.

Формула изобретения

Интегратор с управляемым orpaHH ie нием выходного сигнала, содержащий операционный усилитель, интегрирующий конденсатор, включенный между выходом и входом операционного усилителя, соединенным с одним выводом замыкающего .ключа и через цепочку из последовательно соединенных размыкающего ключа и входного масштабного резистора с информационным входом интегратора, цепь сравнения, выполнен- на двух последовательно соединенных токозадающих резисторах и включен ную между входом задания уровня ограничения и выходом интегратора, триггер, два нуль-органа, вход первого из которых соединен с информационным входом .интегратора, выходы нуль-органов соединены с соответствующими входами триггера, прямой выход которого связан с управляющим входом размыкающего ключа, и третий токозадающий резистор, отличающийся тем, что, с целью повышения точности, в него введены элемент задержки, усилитель напряжения и усилитель тока, вход которого подключен к общему выводу токозадающих резисторов цепи сравнения, а выход соединен с первым вьшодом третьего токозадающего резистора и через усилитель напряжения подключен к входу второго нуль-органа и к другому вьшоду замыкающего ключа, управляющий вход которого через элемент задержки соединен с инверсным выходом триггера, второй вывод третьего токозадающего резистора соединен с шиной нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор с управляемым ограничением выходного сигнала | 1978 |

|

SU744631A1 |

| Генератор линейно-изменяющегося напряжения | 1978 |

|

SU947875A1 |

| Преобразователь емкостных параметров двухполюсника в интервал времени | 1988 |

|

SU1564569A1 |

| Устройство для моделирования м-фазного вентильного преобразователя | 1974 |

|

SU524200A1 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1298671A1 |

| Интегрирующий преобразовательНАпРяжЕНия B иНТЕРВАл ВРЕМЕНи | 1979 |

|

SU809560A1 |

| Цифровой интегрирующий вольтметр | 1990 |

|

SU1798711A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015444A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841056A1 |

| Интегрирующий электрометр | 1982 |

|

SU1104426A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах моделирования сложных объектов. Цель изобретения - повышение точности интегратора. Интегратор с управляемым ограничением выходного сигнала содержит операционный усилитель 1, интегрирующий конденсатор 2, масштабньш резистор 5, размыкающий ключ 7, цепь сравнения, состоящую из резисторов 8 и 9 и уровня ограничения 10, замыкающий ключ П, нуль-органы 12 и 13, триггер 14, усилитель тока 15, усилитель напряжения 16, элемент задержки 18. Интегратор имеет повьшенную точность, т.к. в усилительном контуре применен активньй элемент с низким входным сопротивлением в виде усилителя тока. Применение усилителя тока и усилителя напряжения улучшает динамические свойства интегратора, снижает требование к параметрам нуль- органов, ВХОДЯ1Г1ИХ в его структуру. За счет применения элемента задержки достигается уменьшение паразитных всплесков выходного напряжения интегратора в момент переключения размы- каюшего ключа. 1 ил. сл СП vj ю 4:

| Патент США № 3514635, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Интегратор с управляемым ограничением выходного сигнала | 1978 |

|

SU744631A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1986-01-16—Подача