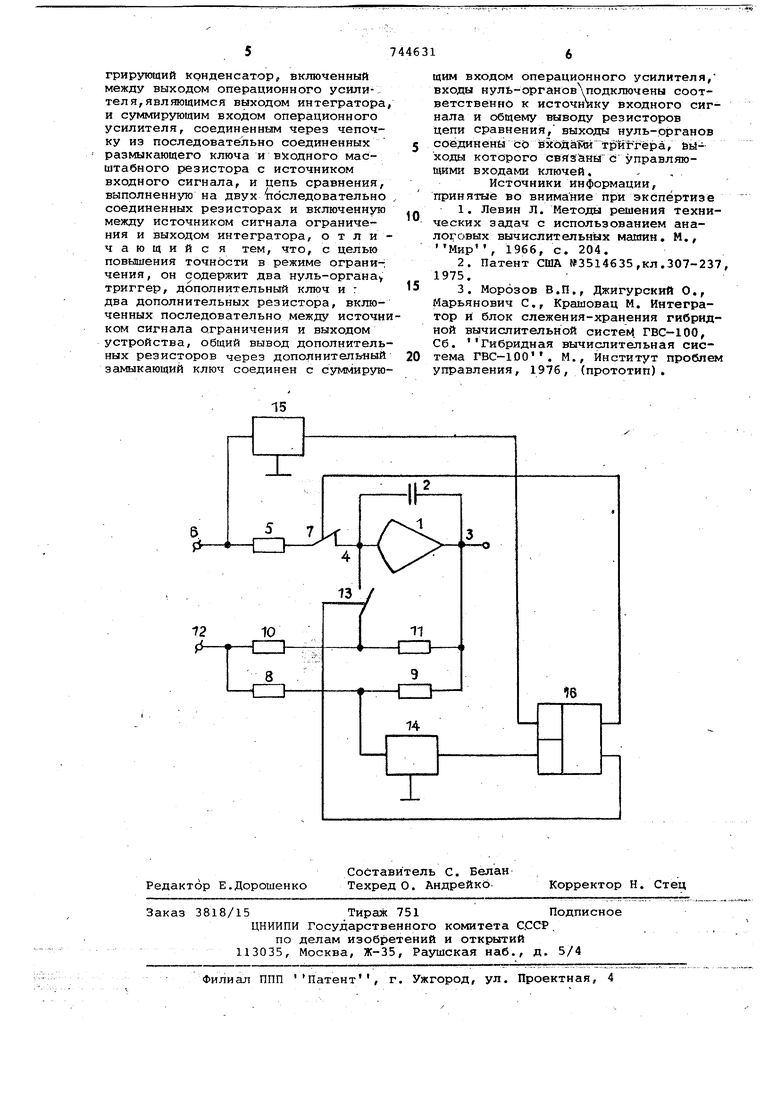

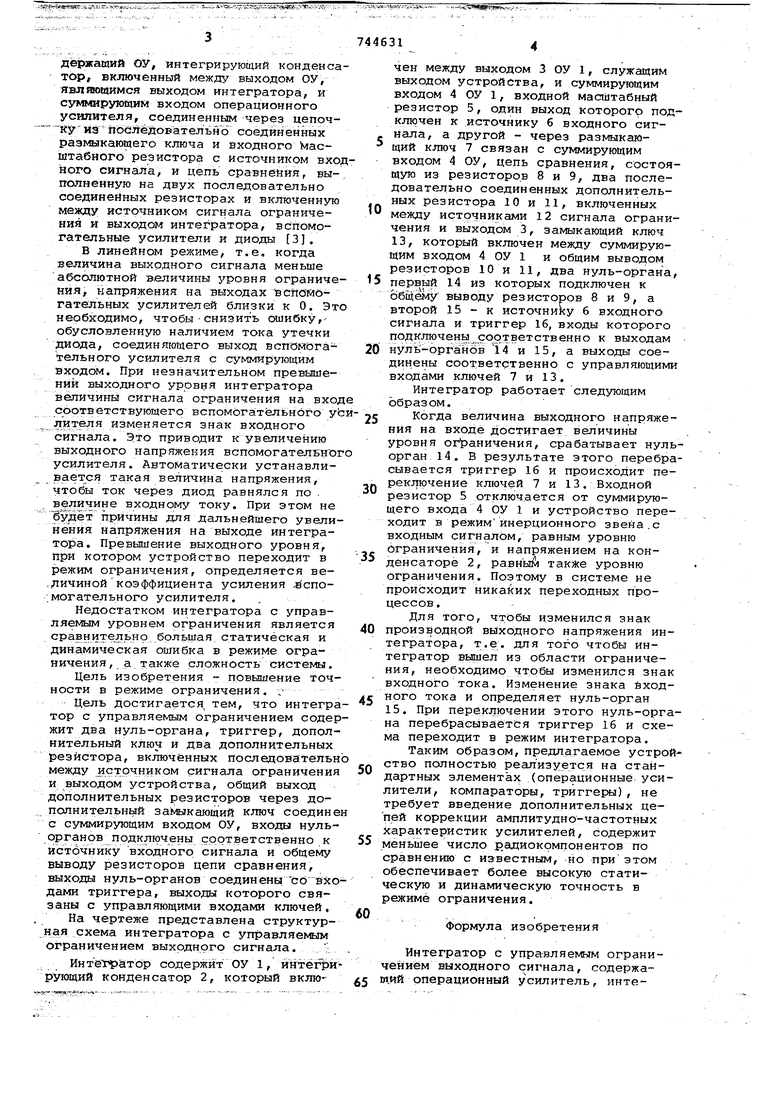

Изобретение относится к автомати ке и вычислительной технике. Известны интеграторы с управляемым ограничением выходного сигнала, в состав которых входят основной операционный усилитель, входной резистор, интегрирующий конденсатор и управляемая нелинейная цепь обрат ной связи. Для управления режимом работы интеграторы содержат ключи. В одном из этих интеграторов параллельно интегрирующему конденсатору включен диод с дополнительным смещением, которое создано резистив ным делителем, включенным между, выходом интегратора и источником .опор ного напряжения 1. Такое включение ограничиёающего диода не только не обеспечивает высокую точность ограничения, но ухуд шает точностные характеристики инте гратора в линейном режиме.Это ухудшение вызвано наличием тока утечки у закрытых диодов. Известен также интегратор, в кот рый введены два вспомогательных уси лителя (один для реализации ограничения максимальной величины, второй минимат ьной) . Выходы вспомогательны неинвертирующих усилителей связаны с суммирующим входом основного операционного усилителя (ОУ) через диодные цепи. На вход вспомогательного усилителя подается разность выходного напряжения интегратора и напряжения ограничения. При превышении величины выходного сигнала уровня ограничений, вспомогательный усилитель обеспечивает дополнительный ток на суммирующем входе основного ОУ, которь1й по величине равен входному току интегратора, но противоположной по направлению. При выполнении этого условия прекращается заряд конденсатора интегратора 2 . Недостатком этого типа интеграторов является наличие значительной динамической ошибки, возникающей при переходе схемы из линейного режима (режим интегрирования) в режим ограничения и наличие дополнительной статической ошибки, обусловленной конечностью коэффициента усиления вспомогательного усилителя. Наиболее близким техническим решением к предлагаемому является интегратор с управляемым уровнем ограничения выходного сигнала, содержащий ОУ, интегрирующий конденса тор, включенный между выходом ОУ, явлгаощимся выходом интегратора/ и суммирующим входом операционного усилителя, соединенным через цепоч---Kjr- ИЗ последовательно соединенных размыкающего ключа и входного Kiacштабного резистора с источником вхо ного сигнала, и цепь сравнения, выгголненную на двух последовательно соединенных резисторах и включенную между источником сигнала ограничения и выходог интегратора, вспомогательные усилители и диоды 3, В линейном режиме, т.е. когда величина выходного сигнала меньше абсолютной величины уровня ограниче ния, напряжения на выходах всиомогатеЛьных усилителей близки к О, Эт необходимо, чтобыснизить ошибку, обусловленную наличием тока утечки диода, соединяющего выход вспомогательного усилителя с суммирующим входом. При незначительном превышений выходного уровня интегратора величины сигнала ограничения на вхо соответствующего вспомога тёльнбг о у липгеля изменяется знак входного сигнала. Это приводит к увеличению выходного напряжения вспомогательно усилителя. Автоматически устанавливает ся такая величина напряжения, чтобы ток через диод равнялся по . в еличине входному току. При этом не будет причины для дальнейшего увели нения напряжения на выходе интегратора. Превышение выходного уровня, при котором устройство переходит в режим ограничения, определяется ве,личиной коэффициента усиления .могательного усилителя. Недостатком интегратора с управляемым уровнем ограничения является сравнительно большая статическая и динамическая ошибка в режиме ограничения , а также сложность системы. Цель изобретения - повышение точ ности в режиме ограничения. ;Цель достигается, тем, что интегр тор с управляемым ограничением соде жит два нуль-органа, триггер, допол нительный ключ и два дополнительных резистора, включенных последовательн между источником сигнала ограничения и выходом устройства, общий выход дополнительных резисторов через дополнительный замыкающий ключ соедин с суммирующим входом ОУ, входаа нульорганов подключены соответственно к истбчнику входного сигнала и общему выводу резисторов цепи сравнения, выходы нуль-органов соединены сО вхо дами триггера, выходы которого связаны с управляющими входами ключей. На чертеже представлена структурная схема интегратора с управляемым ограничением выходного сигнала. , Интетратор содержит ОУ 1, HHTefpn рующий конденсатор 2, который включен между выходом 3 ОУ 1, служащим выходом устройства, и суммирующим входом 4 ОУ 1, входной масштабный резистор 5, один выход которого подключен к источнику б входного сигнала, а другой - через размыкающий ключ 7 связан с суммирующим входом 4 ОУ, цепь сравнения, состоящую из резисторов 8 и 9, два последовательно соединенных дополнительных резистора 10 и II, включенных между источниками 12 сигнала ограничения и выходом 3, замыкающий ключ 13, который включен между суммирующим входом 4 ОУ 1 и общим выводом резисторов 10 и 11, два нуль-органа, первый 14 из которых подключен к обйбму выводу резисторов 8 и 9, а второй 15 - к источнику 6 входного сигнала и триггер 16, входы которого подключены соответственно к выходам нуль-органов 14 и 15, а выходы соединены соответственно с управляющими входами ключей 7 и 13. Интегратор работает следующим образом. Когда величина выходного напряжения на входе достигает величины уровня ог аничения, срабатывает нульорган 14, В результате этого перебрасывается триггер 16 и происходит переключение ключей 7 и 13. Входной резистор 5 отключается от суммирующего входа 4 ОУ 1 и устройство переходит в режиминерционного звена .с входным сигналом, равным уровню ограничения, и напряжением на конденсаторе 2, paBHbrfii уровню ограничения. Поэтому в системе не происходит никаких переходных процессов . Для того, чтобы изменился знак производной выходного напряжения интегратора, т.е. для того чтобы интегратор вышел из области ограничения, необходимо ч:трбы изменился знак входного тока. Изменение знака входного тока и определяет нуль-орган 15. При переключении этого нуль-органа перебрасывается триггер 16 и схема переходит в режим интегратора. Таким образом,предлагаемое устройство полностью реализуется на стандартных элементах (операционные усилители, компараторы, триггеры), не требует введение дополнительных цепей коррекции амплитудно-частотных характеристик усилителей, содержит меньшее число радиокомпонентов по сравнению с известным, но при этом обеспечивает более высокую статическую и динамическую точность в режиме ограничения. Формула изобретения Интегратор с управляемым ограничением выходного сигнала, содержащ,ИЙ операционный усилитель, инте

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Интегратор с управляемым ограничением выходного сигнала | 1986 |

|

SU1305724A1 |

| Устройство для моделирования м-фазного вентильного преобразователя | 1974 |

|

SU524200A1 |

| СИСТЕМА УПРАВЛЕНИЯ ДВИГАТЕЛЕМ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1994 |

|

RU2096906C1 |

| Преобразователь напряжения в частоту | 1982 |

|

SU1077048A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Пьезополупроводниковый стабилизатор напряжения | 1984 |

|

SU1241369A1 |

| Измерительный преобразователь активной мощности | 1989 |

|

SU1659890A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Способ импульсной стабилизации постоянного напряжения и устройство для его осуществления | 1982 |

|

SU1120304A1 |

Авторы

Даты

1980-06-30—Публикация

1978-04-18—Подача