1

Изобретение относится к вычисли тельной технике и может быть использовано при разработке в испытаниях измерительных Приборов, а также в радиотехнике.

Цель изобретения - повьппение точности моделирования петли гистерезиса вследствие учета явления остаточной намагниченности материала.

13057272

своим выходом подключен к третьему входу селектора 19 каналов и второму входу селектора 21 каналов.

Три выхода селектора 19 каналов подключены соответственно к трем управляющим входам кодоуправляемого

усилителя , причем первый выход селектора 19 каналов через инвертор 22 связан с управляющим входом ключа

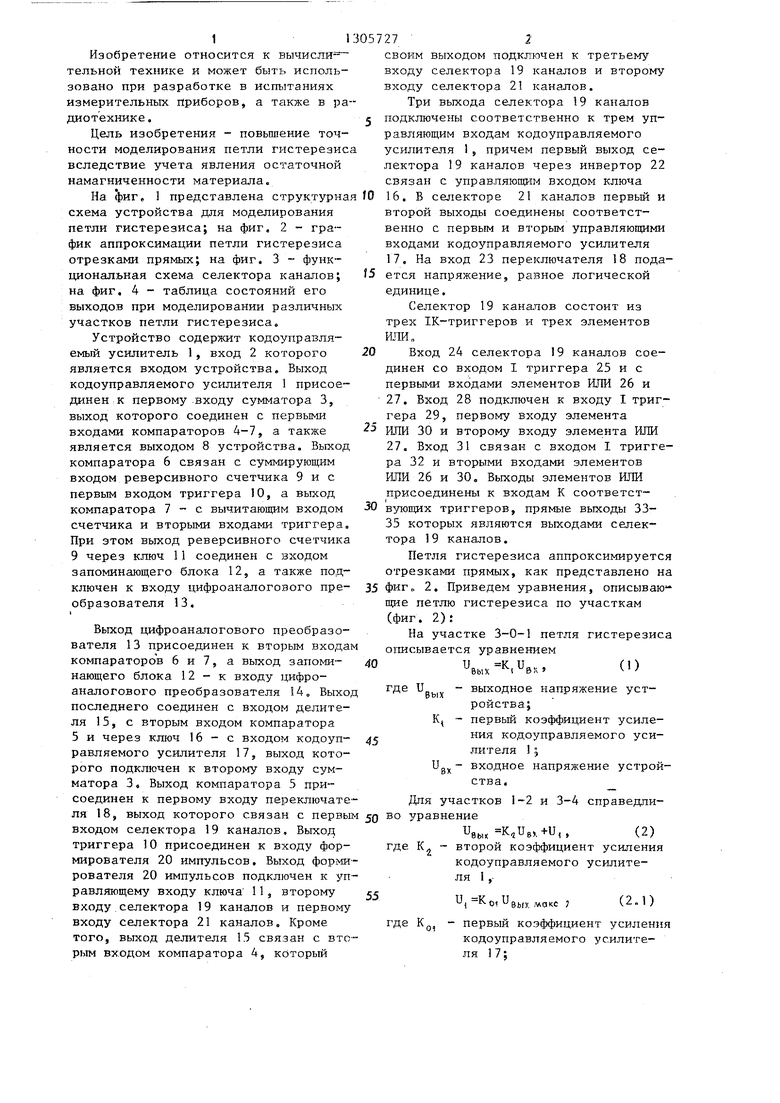

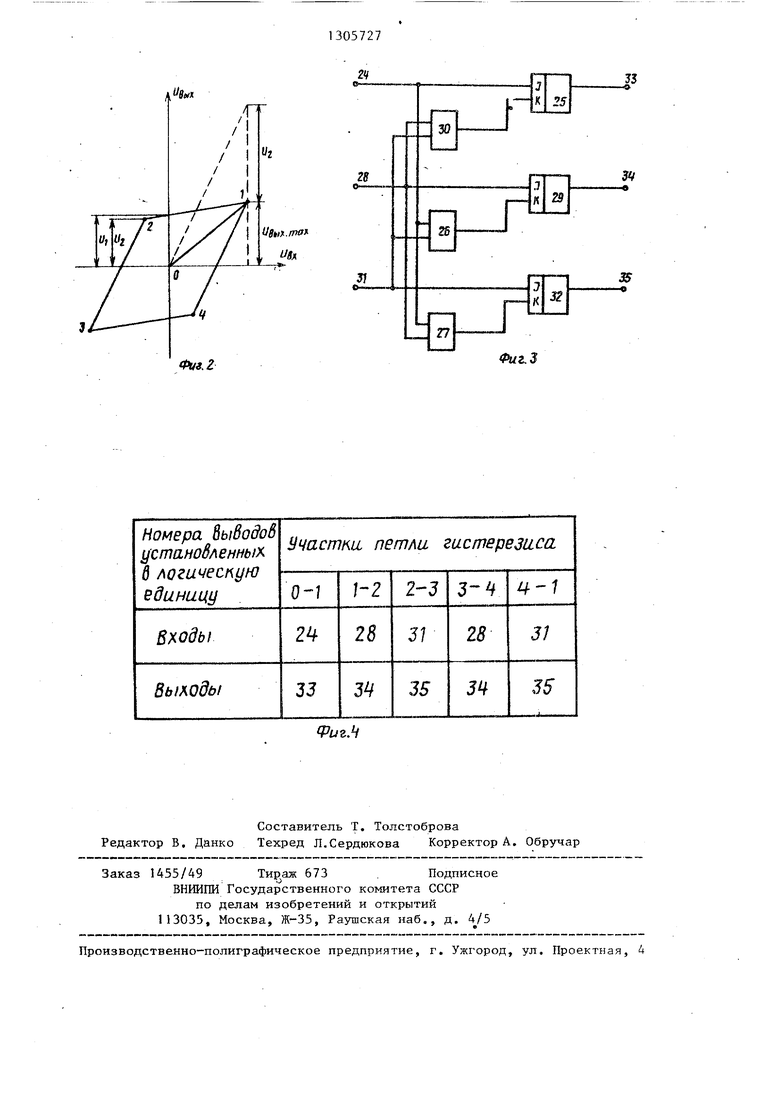

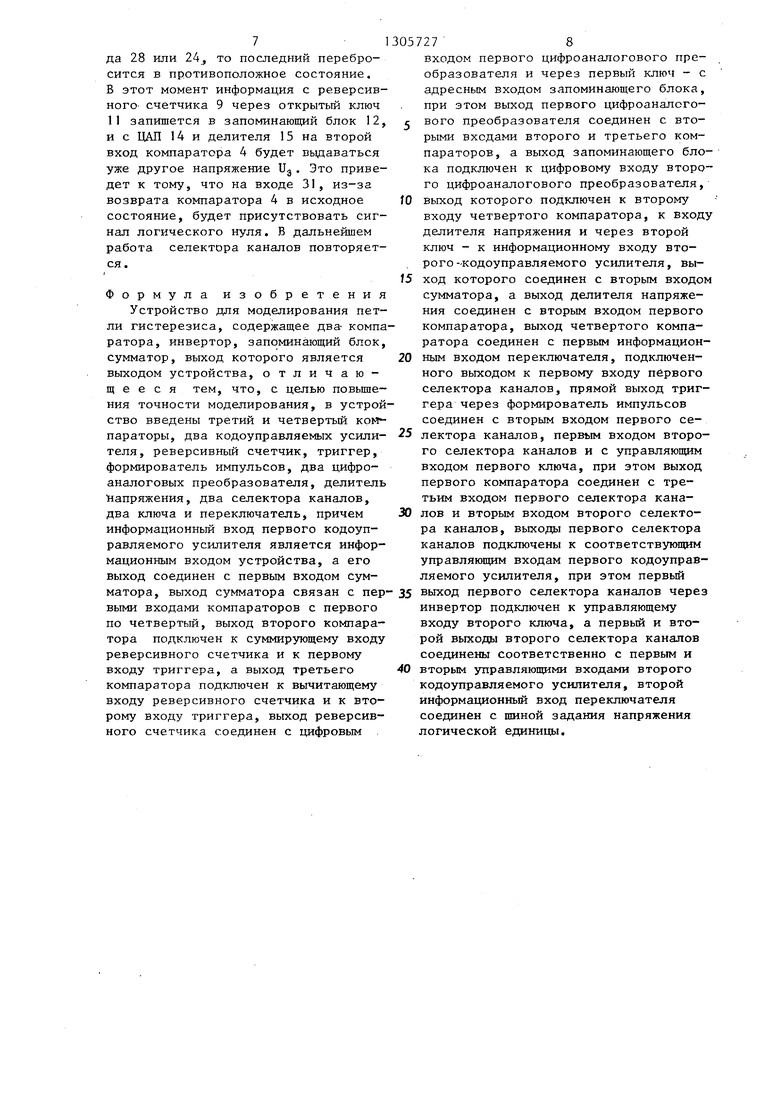

На (иг, 1 представлена структурная fO 16, В селекторе 21 каналов первый и

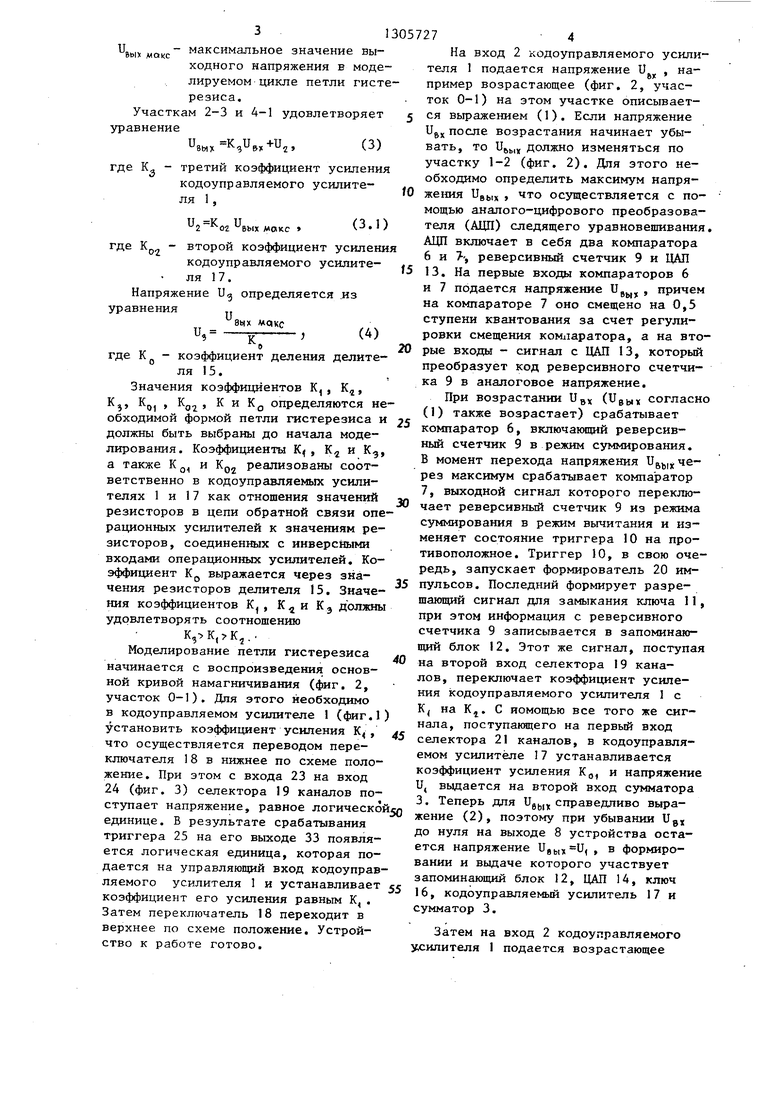

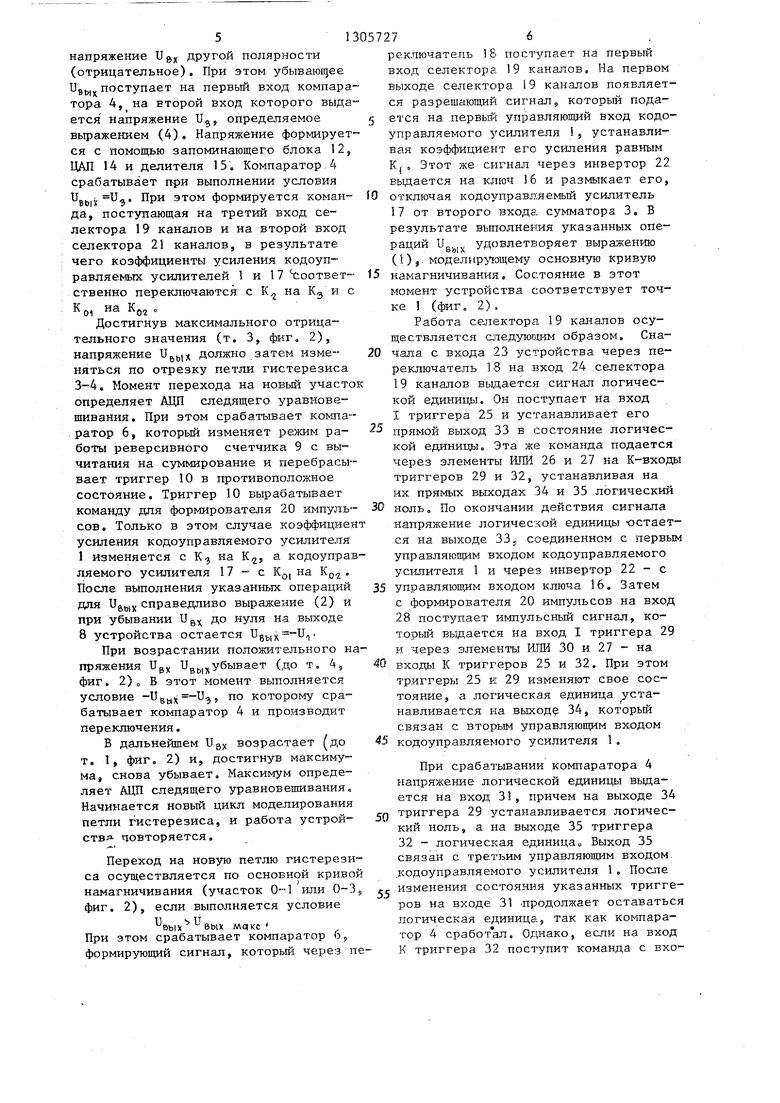

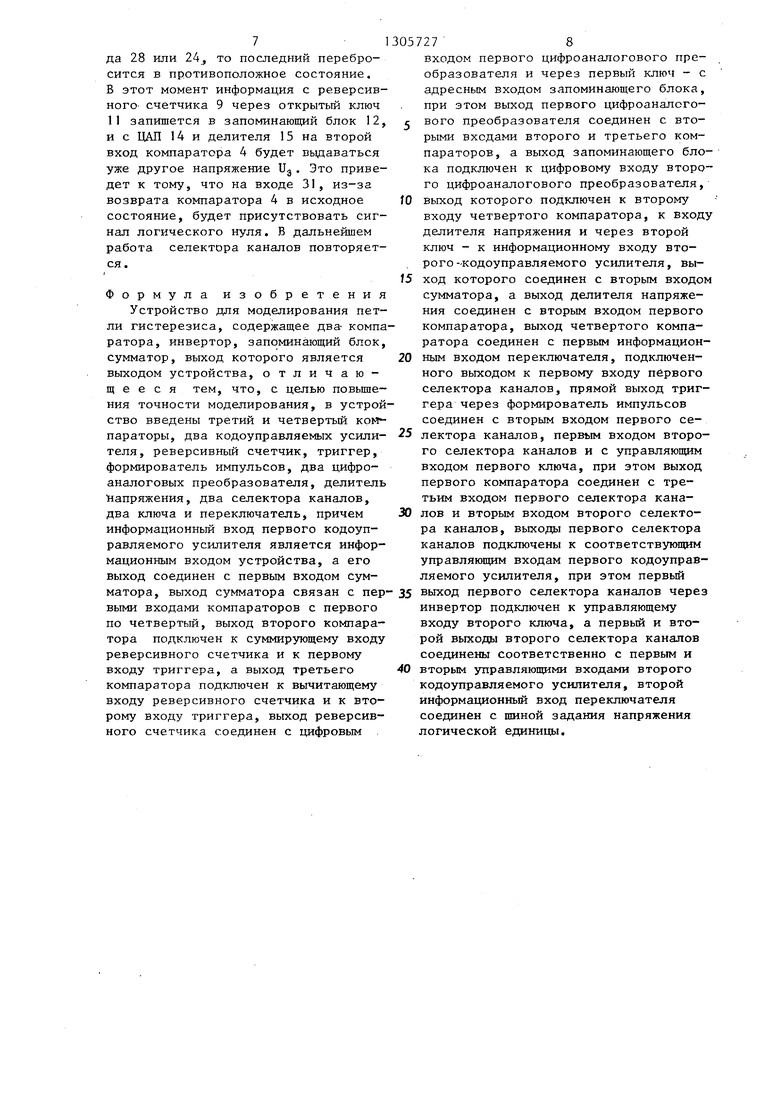

схема устройства для моделирования петли гистерезиса; на фиг, 2 - график аппроксимации петли гистерезиса отрезками прямых; на фиг, 3 - функциональная схема селектора каналов; на фиг, 4 - таблица состояний его выходов при моделировании различных участков петли гистерезиса.

Устройство содержит кодоуправля- емый усилитель 1, вход 2 которого является входом устройства. Выход кодоуправляемого усилителя 1 присоединен: к первому входу сумматора 3, выход которого соединен с первыми входами компараторов А-7, а также является выходом 8 устройства. Выход компаратора 6 связан с суммирующим входом реверсивного счетчика 9 и с первым входом триггера 10, а выход компаратора 1-е вычитающим входом счетчика и вторыми входами триггера. При этом выход реверсивного счетчика 9 через ключ 11 соединен с входом запоминающего блока 12, а также подключен к входу цифроаналогового преобразователя 13,

Выход цифроаналогового преобразователя 13 присоединен к вторым входам компараторо в 6 и 7, а выход запоми- 40 нающего блока 12 - к входу цифро- аналогового преобразователя 14, Выход последнего соединен с входом делителя 15, с вторым входом компаратора 5 и через ключ 16 - с входом кодоуправляемого усилителя 17, выход которого подключен к второму входу сумматора 3. Выход компаратора 5 присоединен к первому входу переключате35 фиг,, 2, Приведем уравнения, описывающие петлю гистерезиса по участкам (фиг, 2):

На участке 3-0-1 петля гистерезиса описывается уравнением

(1)

ивык.и..

где и

Bbix К.

45

UBXвыходное напряжение устройства;

первый коэффициент усиления кодоуправляемого усилителя 1 входное напряжение устройства,

Лпя участков 1-2 и 3-4 справедли- ля 18, выход которого связан с первым 50 о уравнение

входом селектора 19 каналов. ВыходUg К,гив. U, , (2)

триггера 10 присоединен к входу фор- где К - второй коэффициент усиления мирователя 20 импульсов, Выход формирователя 20 импульсов подключен к уп55

кодоуправляемого усилителя 1 ,равляющему входу ключа 11, второму входу селектора 19 каналов и первому входу селектора 21 каналов. Кроме того, выход делителя 15 связан с вторым входом компаратора 4, который

Uj -KOI Ugj,,, ,дкс J

(2.1)

где К

Q, - первый коэффициент усиления кодоуправляемого усилителя 7 5

усилителя , причем первый выход селектора 19 каналов через инвертор 22 связан с управляющим входом ключа

второй выходы соединены соответственно с первым и вторым управляющими входами кодоуправляемого усилителя 17, На вход 23 переключателя 18 подается напряжение, равное логической единице.

Селектор 19 канапов состоит из трех 1К-триггеров и трех элементов ИЛИ,,

Вход 24 селектора 19 каналов соединен со входом I триггера 25 к с первыми входами элементов ИЖ 26 и 27, Вход 28 подключен к входу I триггера 29, первому входу элемента

ИЛИ 30 и второму входу элемента ИЛИ 27. Вход 31 связан с входом I триггера 32 и вторыми входами элементов ИЛИ 26 и 30, Выходы элементов ИЛИ присоединены к входам К соответствуюпщх триггеров, прямые выходы 33- 35 которых являю тся выходами селектора 19 каналов,

Петля гистерезиса аппроксимируется отрезками прямых, как представлено на

фиг,, 2, Приведем уравнения, описывающие петлю гистерезиса по участкам (фиг, 2):

На участке 3-0-1 петля гистерезиса описывается уравнением

(1)

ивык.и..

де и

Bbix К.

UBXвыходное напряжение устройства;

первый коэффициент усиления кодоуправляемого усилителя 1 входное напряжение устройвторой коэффициент усилени

кодоуправляемого усилителя 1 ,Uj -KOI Ugj,,, ,дкс J

(2.1)

где К

Q, - первый коэффициент усиления кодоуправляемого усилителя 7 5

и.

- максимальное значение выВЫУ MQKC

ходного напряжения в моделируемом цикле петли гистерезиса.

Участкам 2-3 и 4-1 удовлетворяет уравнение

. (3)

где К - третий коэффициент усиления кодоуправляемого усилителя 1 ,

(3.1)

где К - второй коэффициент усиления кодоуправляемого усилителя 17. Напряжение 1) определяется .из

и

и

вых

К.

где Kjj - коэффициент деления делителя 15.

Значения коэффициентов К,, К, Kj, KQI , ог о определяются необходимой формой петли гистерезиса и должны быть выбраны до начала моделирования. Коэффициенты К,

Kj и К,

а также К и К реализованы соответственно в кодоуправляемых усилителях 1 и 17 как отношения значений резисторов в цепи обратной связи операционных усилителей к значениям резисторов, соединенных с инверсными входами операционных усилителей. Коэффициент Кр выражается через значения резисторов делителя 15. Значения коэффициентов К, удовлетворять соотношению

К и Kj должны

к,к,к,,.

40

Моделирование петли гистерезиса начинается с воспроизведения основной кривой намагничивания (фиг. 2, участок 0-1). Для этого необходимо в кодоуправляемом усилителе 1 (фиг.1) установить коэффициент усиления К|, что осуществляется переводом переключателя 18 в нижнее по схеме положение. При этом с входа 23 на вход 24 (фиг. 3) селектора 19 каналов поПри возрастании (Uebtx соглас (1) также возрастает) срабатывает компаратор 6, включающий реверсивный счетчик 9 в режим суммирования. В момент перехода напряжения U, че рез максимум срабатывает компаратор 7, выходной сигнал которого переклю чает реверсивный счетчик 9 из режим суммирования в режим вычитания и из меняет состояние триггера 10 на про тивоположное. Триггер 10, в свою оч редь, запускает формирователь 20 им пульсов. Последний формирует разре- щающий сигнал для замыкания ключа 1 при этом информация с реверсивного счетчика 9 записывается в запоминаю щий блок 12. Этот же сигнал, поступ на второй вход селектора 19 каналов, переключает коэффициент усиления кодоуправляемого усилителя I с К| на Kj. С помощью все того же сиг нала, поступающего на первый вход селектора 21 каналов, в кодоуправля емом усилителе 17 устанавливается коэффициент усиления К, и напряжени и, выдается на второй вход сумматор

ступает напряжение, равное логическойсл ,, справедливо выра- - результате гп.«.™«.«„а ™ 2), поэтому при убывании U,

единице. В результате срабатывания триггера 25 на его выходе 33 появляется логическая единица, которая подается на управляющий вход кодоуправляемого

до нуля на выходе 8 устройства остается напряжение ,, в формировании и выдаче которого участвует

,запоминающий блок 12, ЦАП 14,ключ

усилителя 1 и устанавливает « , х „, -,

.,,,16, кодоуправляемыи усилитель17 и

коэффициент его усиления равным К, .

Затем переключатель 18 переходит в У Р

верхнее по схеме положение. Устройство к работе готово.

я 15

20

25

40

) На вход 2 кодоуправляемого усилителя 1 подается напряжение 1} , например возрастающее (фиг. 2, участок 0-1) на этом участке описьшает-

5 ся вьфажением (1). Если напряжение Ug после возрастания начинает убывать, то U(,b,y должно изменяться по участку 1-2 (фиг. 2). Для этого необходимо определить максимум иапря 0 жения Ugbi, , что осуществляется с помощью аналого-цифрового преобразователя (АЦП) следящего уравновешивания. АЦП включает в себя два компаратора 6 и , реверсивный счетчик 9 и ЦАП 13. На первые входы компараторов 6 и 7 подается напряжение Ug , причем на компараторе 7 оно смещено на 0,5 ступени квантования за счет регулировки смещения компаратора, а на вторые входы - сигнал с ЦАП 13, который преобразует код реверсивного счетчика 9 в аналоговое напряжение.

При возрастании (Uebtx согласно (1) также возрастает) срабатывает компаратор 6, включающий реверсивный счетчик 9 в режим суммирования. В момент перехода напряжения U, через максимум срабатывает компаратор 7, выходной сигнал которого переключает реверсивный счетчик 9 из режима суммирования в режим вычитания и изменяет состояние триггера 10 на противоположное. Триггер 10, в свою очередь, запускает формирователь 20 импульсов. Последний формирует разре- щающий сигнал для замыкания ключа 11, при этом информация с реверсивного счетчика 9 записывается в запоминающий блок 12. Этот же сигнал, поступая на второй вход селектора 19 каналов, переключает коэффициент усиления кодоуправляемого усилителя I с К| на Kj. С помощью все того же сигнала, поступающего на первый вход селектора 21 каналов, в кодоуправляемом усилителе 17 устанавливается коэффициент усиления К, и напряжение и, выдается на второй вход сумматора

30

35

,, справедливо выра- ™ 2), поэтому при убывании U,

до нуля на выходе 8 устройства остается напряжение ,, в формировании и выдаче которого участвует

Затем на вход 2 кодоуправляемого Зьсилителя 1 подается возрастающее

5

напряжение U другой полярности (отрицательное) . При этом убываюп}ее вых поступает на первый вход компаратора А, на второй вход которого выдается Напряжение U, определяемое выражением (4), Напряжение формируется с помощью запоминающего блока 12, ЦАП 14 и делителя 15. Компаратор 4 срабатывает при выполнении условия ,U. При этом формируется команда, поступающая на третий вход селектора 19 каналов и на второй вход селектора 21 каналов, в результате. чего коэффициенты усиления кодоуп- равляемых усилителей 1 и 17 оответК на Kg и с

твенно переключаются с о, иа KO, .

Достигнув максимального отрицательного значения (т. 3, фиг. 2), апряжение должно затем измеяться по отрезку петли гистерезиса 3-4. Момент перехода на новый участок определяет АЦП следящего уравновеивания . При этом срабатывает компа-- ратор 6, который изменяет режим работы реверсивного счетчика 9 с вычитания на суммирование и перебрасывает триггер 10 в противоположное состояние. Триггер 10 вырабатывает команду для формирователя 20 импульсов. Только в этом случае коэффициент усиления кодоуправляемого усилителя 1 изменяется с К на а кодоуправляемого усилителя 17 - с К, на К . После выполнения указанных операций для Ugj справедливо выражение (2) и при убывании UB; до нуля на выходе 8 устройства остается ,,

При возрастании положительного напряжения Ugy Ugjji убывает (до т, 4, фиг. 2)„ В этот момент .выполняется условие Wgt, которому срабатывает компаратор 4 и производит переключения.

В дальнейшем Ug)( возрастает до т. 1, фиг, 2) и, достигнув максимума J снова убывает. Максимум определяет АЦП следящего уравновешивания. Начинается новый цикл моделирования петли гистерезиса, и работа устрой- 50 CTBJ повторяется.

20

25

30

35

40

5

Переход на новую петлю гистерезиса осуществляется по основной кривой намагничивания (участок 0--1 или 0-3, фиг, 2), если выполняется условие

11 S 1Т

Bblx вых макс При этом срабатывает компаратор 6,

формирующий сигнал, который через пе3057276

реключатель 8 поступает на первый вход селектора )9 каналов. На первом выходе селектора 19 каналов появляется разрешающий сигнал, который подается на первьт управляющий вход кодо- управляемого усилителя 1, устанавливая коэффициент его усиления равным К,, Этот же сигнал через инвертор 22

Ш

к т50

М вьщается на ключ 16 и размыкает его,

отключая кодоуправляемый усилитель 17 от второго входа сумматора 3, В результате выполнения указанных операций , удовлетворяет выражению (1) 5. моделир ющему основную кривую

tS намагничивания. Состояние в этот

момент устройства соответствует точке 1 (фиг. 2),

Работа селектора 19 каналов осуществляется слецующкм образом. Сна20 чала с входа 23 устройства через переключатель 18 на вход 24 селектора 19 каналов вьщается сигнал логической единицы. Он поступает на вход I триггера 25 и устанавливает его

25 прямой выход 33 в состояние логической единицы. Эта же команда подается через элементы ИЛИ 26 и 27 на К-входы триггеров 29 и 32, устанавливая на их прямых выходах 34 и 35 логический

30 ноль, По окончании действия сигнала напряжение логической единицы -остается на выходе 33., соединенном с первым управляющим входом кодоуправляемого ус1 пителя 1 и через инвертор 22 - с

35 управляющим входом ключа 16. Затем с формирователя 20 импульсов на вход 28 поступает импульсный сигнал, ко- торьш вьщается на вход I триггера 29 и через элементы ИПИ 30 и 27 - на

40 входы К триггеров 25 и 32. При этом триггеры 25 и 29 изменяют свое состояние, а логическая единица устанавливается на выходе 34, который связан с вторым управляющим входом

5 кодоуправляемого усилителя 1.

0

5

При срабатывании компаратора 4 напряжение логической единицы вьщается на вход 3I, причем на выходе 34 триггера 29 устанавливается логический ноль, а на выходе 35 триггера 32 - логическая единица„ Выход 35 связан с третьим управляющим входом, .кодоуправляемого усилителя 1, После изменения состояния указанных триггеров на входе 31 -продолжает оставаться логическая единица, так как компаратор 4 сработ ал. Однако, если на вход К триггера 32 поступит команда с вхо7

да 28 или 24, то последний перебросится в противоположное состояние. В этот момент информация с реверсивного счетчика 9 через открытый ключ 11 запишется в запоминающий блок 12, и с ЦАП 14 и делителя 15 на второй вход компаратора 4 будет выдаваться уже другое напряжение Uj. Это приведет к тому, что на входе 31, из-за возврата компаратора 4 в исходное состояние, будет присутствовать сигнал логического нуля. В дальнейшем работа селектора каналов повторяется.

Формула изобретения Устройство для моделирования петли гистерезиса, содержащее два- компаратора, инвертор, запоминающий блок, сумматор, выход которого является выходом устройства, отличающееся тем, что, с целью повышения точности моделирования, в устройство введены третий и четвертый крм параторы, два кодоуправляемых усилителя, реверсивный счетчик, триггер, формирователь импульсов, два цифро- аналоговых преобразователя, делитель напряжения, два селектора каналов, два ключа и переключатель, причем информационный вход первого кодоуп- равляемого усилителя является информационным входом устройства, а его выход соединен с первым входом сумматора, выход сумматора связан с первыми входами компараторов с первого по четвертый, выход второго компаратора подключен к суммирующему входу реверсивного счетчика и к первому входу триггера, а выход третьего компаратора подключен к вычитающему входу реверсивного счетчика и к второму входу триггера, выход реверсивного счетчика соединен с цифровым

057278

входом первого цифроаналогового преобразователя и через первый ключ - с адресным входом запоминающего блока, при этом выход первого цифроаналого- с вого преобразователя соединен с вторыми входами второго и третьего компараторов , а выход запоминающего блока подключен к цифровому входу второго цифроаналогового преобразователя,

fO выход которого подключен к второму входу четвертого компаратора, к входу делителя напряжения и через второй ключ - к информационному входу второго -кодоуправляемого усилителя, вы15 ход которого соединен с вторым входом сумматора, а выход делителя напряжения соединен с вторым входом первого компаратора, выход четвертого компаратора соединен с первым информацион20 ным входом переключателя, подключенного выходом к первому входу первого селектора каналов, прямой выход триггера через формирователь импульсов соединен с вторым входом первого се25 лектора каналов, первым входом второго селектора каналов и с управляющим входом первого ключа, при этом выход первого компаратора соединен с третьим входом первого селектора кана-

30 лов и вторым входом второго селектора каналов, выходы первого селектора каналов подключены к соответствующим управляющим входам первого кодоуправляемого усилителя, при этом первый 35 выход первого селектора каналов через инвертор подключен к управляющему входу второго ключа, а первый и второй выходы второго селектора каналов соединены соответственно с первым и

-40 вторым управляющими входами второго кодоуправляемого усилителя, второй информационный вход переключателя соединен с шиной задания напряжения логической единицы.

Фиг. г

Фиг.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Способ обработки сигналов вторичного магнитного поля при геоэлектроразведке и устройство для его осуществления | 1990 |

|

SU1744663A1 |

| Цифровой акселерометр | 1984 |

|

SU1242831A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Цифровой калибратор девиации частоты | 1985 |

|

SU1250975A1 |

| Устройство для решения обратной задачи теплопроводности | 1986 |

|

SU1401488A1 |

| Устройство для управления трехфазным мостовым инвертором | 1984 |

|

SU1297194A1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

| Устройство для решения обратной задачи теплопроводности | 1988 |

|

SU1522248A1 |

Изобретение касается информационно-измерительной техники, а также радиотехники и вычислительной техники. Цель изобретения - повьшение точности моделирования петли гистерезиса за счет учета явления остаточной намагниченности материала. Устройство содержит кодоуправляемые усилители 1 и 17, сумматор 3, компараторы 4, 5, 6, 7, реверсивный счетчик 9, триггер 10, ключи 11 и 16, запоминающий блок 12,цифроаналоговые преобразователи 13,14, делитель 15, переключатель 18, селектор каналов 19, 21, формирователь импульсов 20, инвертор 22. Аппроксимация петли гистерезиса отрезками прямых с учетом явления остаточной намагниченности осуществляется путем изменения коэффициентов передачи кодоуправляемых усилителей и запоминания максимального значения выходного сигнала. Возможно моделирование семейства возрастающих петель гистерез иса, 4 ил. с ю (Л со СП ю Фиг.1

Риг.Ч

Составитель Т. Толстоброва Редактор В, Данко Техред Л.Сердюкова Корректор А. Обручар

Заказ 1455/49 Тир.аж 673 . Подписное ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий П3035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для моделирования гистерезисной характеристики | 1979 |

|

SU785878A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО для МОДЕЛИРОВАНИЯ ГИСТЕРЕЗИСНЫХ | 0 |

|

SU398974A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1987-04-23—Публикация

1985-12-27—Подача