W

t5

Изобретение относится к электросвязи и может быть использовано в системах передачи дискретной информации.

Цель изобретения - повышение поме- 5 хоустойчивости.

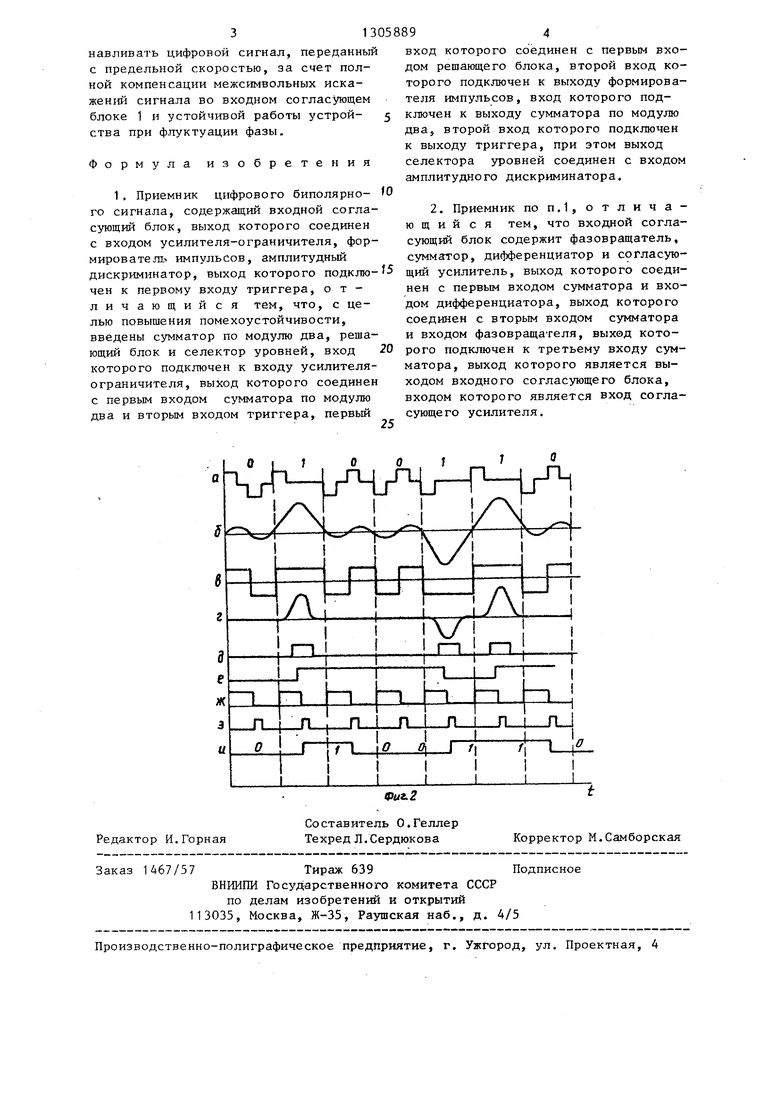

На фиг.1 приведена структурная электрическая схема предлагаемого приемника; на фиг,2 - временная ди- аграмма„

Приемник цифрового биполярного сигнала содержит входной согласующий блок 1, усилитель-ограничитель 2 триггер 3, сумматор 4 по модулю два, формирователь 5 импульсов, селектор

6уровней, амплитудньй дискриминатор

75 решающий блок 8.

Входной согласующий блок 1 содержит согласующий усилитель 9, дифференциатор 10, сумматор 11, фазовраща- тель 12.

Приемник работает следующим образом.

Сформированный на передающей сто- ,,,

роне цифровой биполярньй сигнал (например, фиг, 2а) затухает в линии за счет потерь в проводниках и искажается за счет неравномерности амплитудно-частотной характеристики (АЧХ) и нелинейности фазочастотной характеристики (ФЧХ), Согласующий усилитель 9, согласованньй с конкретной лин,ией связи, частично компенсирует потери в линии, Коэффш.щент уси

30

гфизнаками информационных символов 1 и О,

Дальнейгиая обработка сигнала осу- П1,ествляется следующим образом.

Сигнал (фиг.26) поступает на вход усилителя-ограничителя 2, который содержит схему усиления с амплитудным ограничением и схему нулькомпаратора. Сформированный сигнал (2в) поступает на второй вход триггера 3, на первый вход которого подается импульсный сигнал, сформированньй в селекторе 6 -уровня (фиг.2г) и в амплитудном дискриминаторе 7 (фиг,2д). Триггер 3 устанавливается в единичное состояние по переднему фронту импульсов, поступающих с амплитудного дискриминатора 7 на первьй вход триггера 3, тогда, когда на втором входе сигнал единичного уровня, и устанавливается в нулевое состояние, когда на втором входе сигнал нулевого уровня (фиг,2е). На входы сумматора 4 по модулю два поступают сигналы с выхода триггера 3 и с выхода усилителя-ограничителя 2, на входе которого формируется тактовая частота посылок (фиг,2ж). Сумматор 4 по модулю два является логической схемой ИСКЛЮЧАЮЩЕЕ ИЛИ.

Формирователь 5 импульсов по заднему фронту импульсов тактовой- частоты формирует короткие импульсы необходимой длительности (фиг.2з) и выполнен по схеме одновибратора. Решаления его постоянный в полосе пропус- ющий блок В являетсй синхронным триг- кания информационных частот и умень- гером, если информация в дальнейшем

шается в полосе задержания, обеспечивающей подавление высокочастотной помехи,, Дифференциатор 10 выполнен на операционном усилителе и обеспечивает линейную фильтрацию, т.е. подавление низкочастотной помехи и компенсацию больших неравпомерностей затухания амплитуд при лршейной ФЧХ, Фазовращатель 12 осуществляет фазовый сдвиг сигнала О 180°.

Такой вращатель 12 является фазовым фильтром с коэффициентом передачи, равным единице, который позволяет с использованием сумматора 11 осуществлять компенсацию фазовых искажений, вносимых нелинейностью ФЧХ линии связи. В комплексе входной согласующий блок 1 позволяет и йключить

40

,-, 45

50

транслируется в последовательном коде (фиг,2и), либо СД1ЭИГОВЫМ регистром., если информацию необходимо пред ставить в параллельном коде.

На первый вход решающего блока 8 поступает информация с амплитудного дискриминатора 7, а на второй - стро бирующие импульсы с формирователя 5 импульсов. По стробирующим импульсам решающий блок 8 устанавливается либо в нулевое состояние (определяет логический О), либо единичное (определяет логическую 1) в зависимости от уровня информационного сигнала (фиг.2д). Причем любые флуктуации по рога (фазы) информационного импульса (фиг.2д) автоматически сказываются на флуктуации стробирующих импульсов

межсимвольные искажения и другие по-(фиг,2ж), чем обеспечивается помехомехи,устойчивая работа решающего блока 8.

После такой обработки сигнал при-Таким образом обретает форму (фиг,26) с выраженными

устройство позволя ет с высокой достоверностью восста

5

,,

0

гфизнаками информационных символов 1 и О,

Дальнейгиая обработка сигнала осу- П1,ествляется следующим образом.

Сигнал (фиг.26) поступает на вход усилителя-ограничителя 2, который содержит схему усиления с амплитудным ограничением и схему нулькомпаратора. Сформированный сигнал (2в) поступает на второй вход триггера 3, на первый вход которого подается импульсный сигнал, сформированньй в селекторе 6 -уровня (фиг.2г) и в амплитудном дискриминаторе 7 (фиг,2д). Триггер 3 устанавливается в единичное состояние по переднему фронту импульсов, поступающих с амплитудного дискриминатора 7 на первьй вход триггера 3, тогда, когда на втором входе сигнал единичного уровня, и устанавливается в нулевое состояние, когда на втором входе сигнал нулевого уровня (фиг,2е). На входы сумматора 4 по модулю два поступают сигналы с выхода триггера 3 и с выхода усилителя-ограничителя 2, на входе которого формируется тактовая частота посылок (фиг,2ж). Сумматор 4 по модулю два является логической схемой ИСКЛЮЧАЮЩЕЕ ИЛИ.

Формирователь 5 импульсов по заднему фронту импульсов тактовой- частоты формирует короткие импульсы необходимой длительности (фиг.2з) и выполнен по схеме одновибратора. Реша

40

45

50

транслируется в последовательном коде (фиг,2и), либо СД1ЭИГОВЫМ регистром., если информацию необходимо представить в параллельном коде.

На первый вход решающего блока 8 поступает информация с амплитудного дискриминатора 7, а на второй - стро- бирующие импульсы с формирователя 5 импульсов. По стробирующим импульсам решающий блок 8 устанавливается либо в нулевое состояние (определяет логический О), либо единичное (определяет логическую 1) в зависимости от уровня информационного сигнала (фиг.2д). Причем любые флуктуации порога (фазы) информационного импульса (фиг.2д) автоматически сказываются на флуктуации стробирующих импульсов

Таким образом

устройство позволяет с высокой достоверностью восстанавливать цифровой сигнал, переданны с предельной скоростью, за счет полной компенсации межсимвольных иска- жен1ш сигнала во входном согласующем блоке 1 и устойчивой работы устрой- ства при ф.пуктуации фазы.

Формула изобретения

1. Приемник цифрового биполярно- го сигнала, содержащий входной согласующий блок, выход которого соединен с входом усилителя-ограничителя, формирователь импульсов, амплитудный дискриминатор, выход которого подключен к первому входу триггера, отличающий ся тем, что, с целью повышения помехоустойчивости, введены сумматор по модулю два, решающий блок и селектор уровней, вход которого подключен к входу усилителя- ограничителя, выход которого соединен с первым входом сумматора по модулю два и вторым входом триггера, первый

Редактор И.Горная

Составитель О.Геллер Техред Л.Сердюкова

Заказ 1467/57Тираж 639Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

вход которого соединен с первым входом решающего блока, второй вход которого подключен к выходу формирователя импульсов, вход которого подключен к выходу сумматора по модулю два, второй вход которого подключен к выходу триггера, при этом выход селектора уровней соединен с входом амплитудного дискриминатора.

2. Приемник поп.1,отлича- ю щ и и с я тем, что входной согласующий блок содержит фазовращатель, сумматор, дифференциатор и согласующий усилитель, выход которого соединен с первым входом сумматора и входом дифференциатора, выход которого соединен с вторым входом суыматора и входом фазовращателя, выход которого подключен к третьему входу сумматора, выход которого является выходом входного согласующего блока, входом которого является вход согласующего усилителя.

Корректор М.Самборская

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник цифрового линейного сигнала | 1986 |

|

SU1462509A1 |

| Декодер кода линии | 1988 |

|

SU1510094A1 |

| Устройство для передачи и приема цифровых сигналов | 1986 |

|

SU1415452A1 |

| Регенератор цифрового биполярного сигнала | 1985 |

|

SU1415456A1 |

| Устройство для дуплексной цифровой связи | 1986 |

|

SU1408537A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕХНИЧЕСКОГО СОСТОЯНИЯ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ И ЭКСПЕРТНАЯ СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2293962C1 |

| ИЗМЕРИТЕЛЬ ОТНОСИТЕЛЬНЫХ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 2017 |

|

RU2668951C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕХНИЧЕСКОГО СОСТОЯНИЯ ДВИГАТЕЛЕЙ ВНУТРЕННЕГО СГОРАНИЯ И ЭКСПЕРТНАЯ СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2175120C2 |

| СПОСОБ РЕГИСТРАЦИИ СЛАБЫХ СВЕТОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2190196C1 |

| Амплитудный селектор | 1990 |

|

SU1755392A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Приемник содержит входной согласующий блок (ВСЕ) 1, состоящий из согласующего усилителя 9, дифференциатора 10, сумматора 11, фазовращателя 12, усилитель-ограничитель 2, триггер 3, сумматор 4 по модулю два, формирователь 5 импульсов, селектор 6 уровней, амплитудный дискриминатор 7 и решающий блок (РБ) 8. Приемник позволяет с высокой достоверностью восстанавливать цифровой сигнал, переданный с предельной скоростью, за счет полной компенсации межсимвольных искажений сигнала в ВСБ 1 и устойчивой работы устр-ва при флуктуации фазы. Цель достигается введением сумматора 4 по модулю два, селектора 6 уровней и РБ 8. Приемник по п.2 ф-лы отличается выполнением ВСБ 1. 1 3.п.ф-лы, 2 ил. ( (Л СП 00 00 со

| Устройство для передачи и приема двоичной дискретной информации | 1984 |

|

SU1218489A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-04-23—Публикация

1985-11-29—Подача