СП

U9

4

10

15

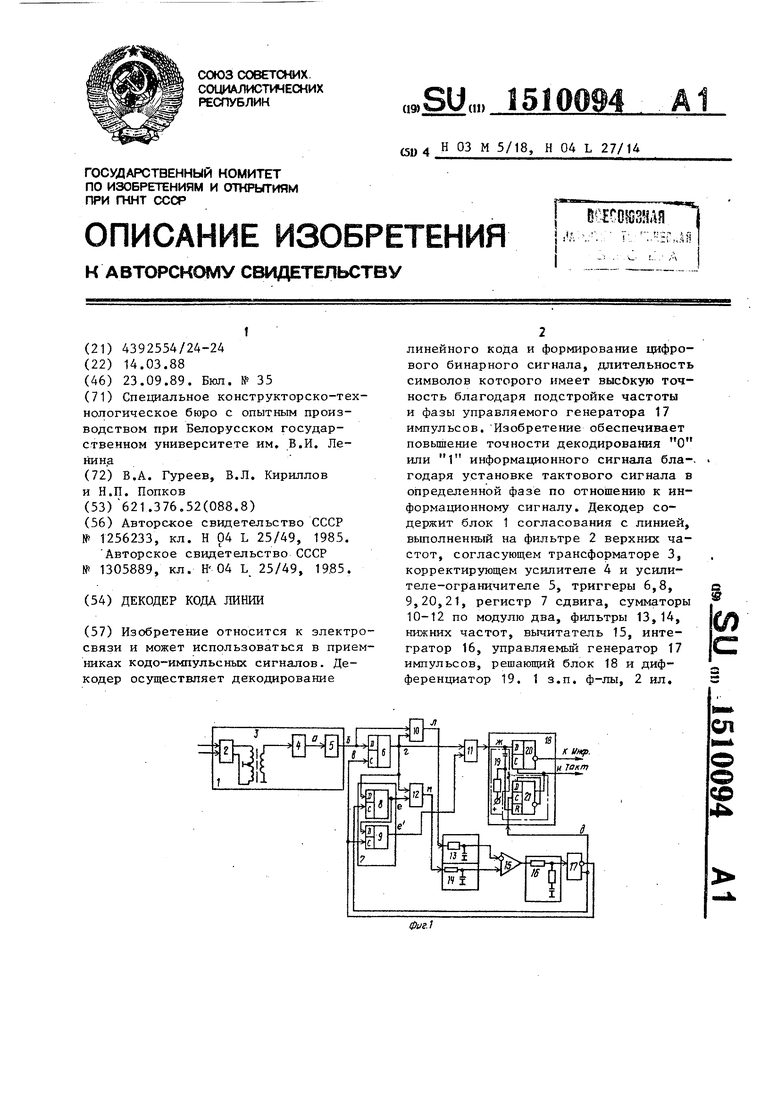

Изобретение относится к электросвязи и может использоваться в приемниках кодо-импульсных сигналов.

Цель изобретения - повышение точности декодирования.

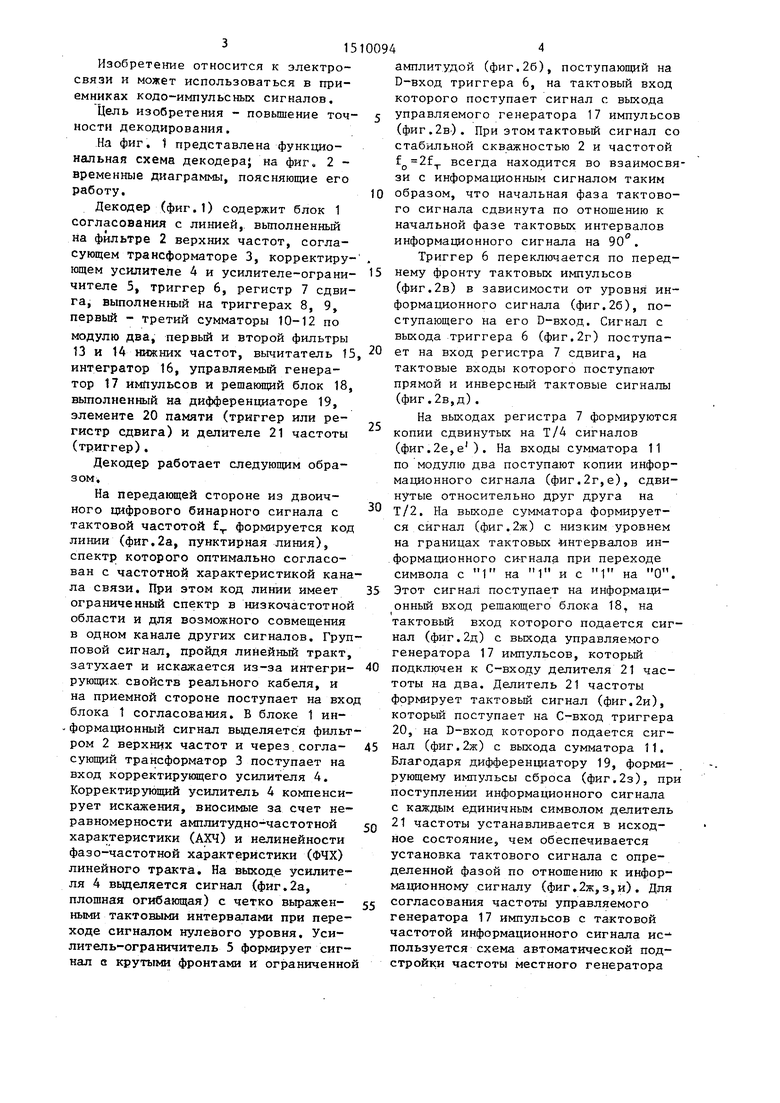

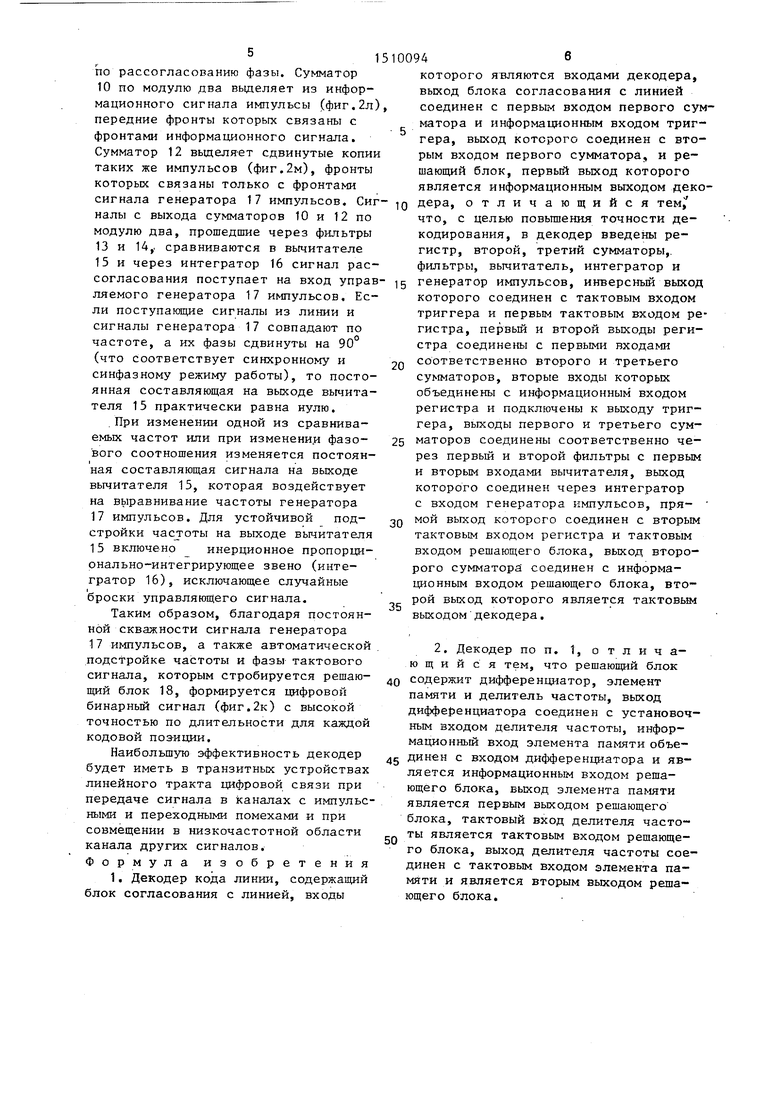

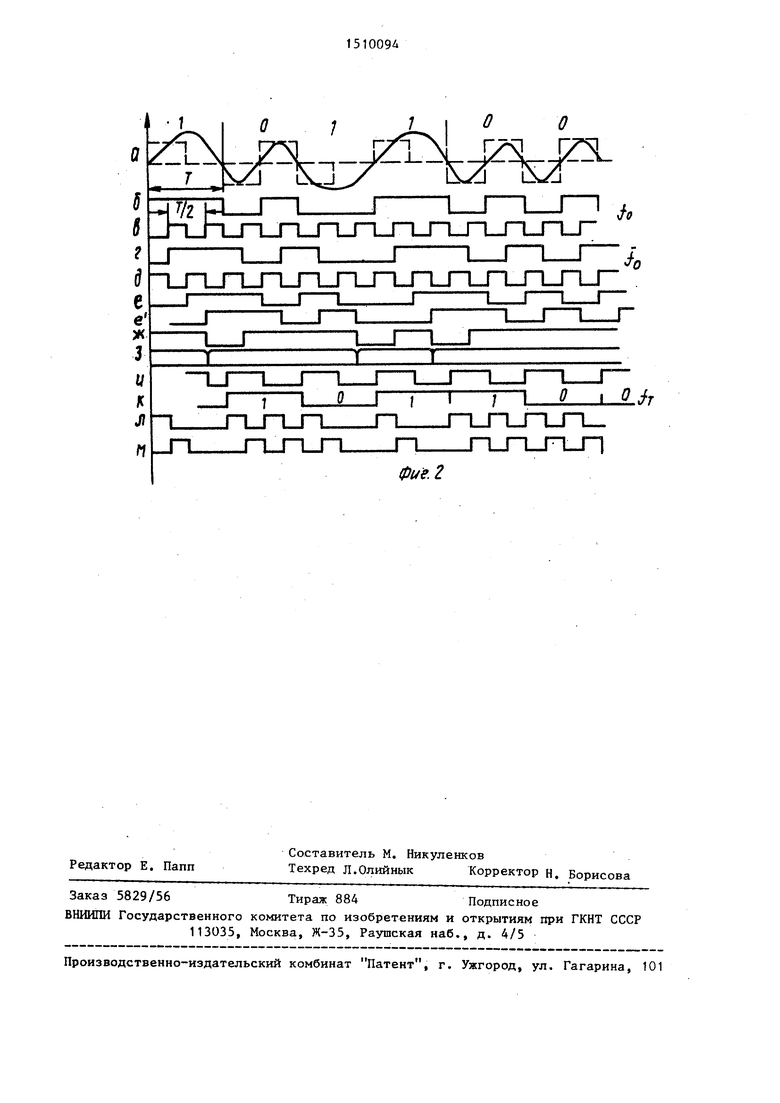

На фиг. 1 представлена функциональная схема декодера; на фиг. 2 - временные диаграммы, поясняющие его работу.

Декодер (фиг.1) содержит блок 1 согласования с линией, вьтолненньш на фильтре 2 верхних частот, согласующем трансформаторе 3, корректирующем усилителе 4 и усилителе-ограничителе 5, триггер 6, регистр 7 сдвига, выполненный на триггерах 8, 9, первый - третий сумматоры 10-12 по модулю два, первый и второй фильтры 13 и 14 нижних частот, вычитатель 15, 0 интегратор 16, управляемый генератор 17 импульсов и решающий блок 18, выполненный на дифференциаторе 19, элементе 20 памяти (триггер или регистр сдвига) и делителе 21 частоты (триггер).

Декодер работает следующим образом.

На передающей стороне из двоичного цифрового бинарного сигнала с тактовой частотой f формируется код линии (фиг.2а, пунктирная линия), спектр которого оптимально согласован с частотной характеристикой канала связи. При этом код линии имеет 35 ограниченный спектр в низкочастотной области и для возможного совмещения в одном канале других сигналов. Групповой сигнал, пройдя линейный тракт.

25

30

амплитудой (фиг.26), поступающий на D-вход триггера 6, на тактовый вход которого поступает сигнал с выхода управляемого генератора 17 импульсов (фиг.2в). При этом тактовый сигнал со стабильной скважностью 2 и частотой всегда находится во взаимосвязи с информационным сигналом таким образом, что начальная фаза тактового сигнала сдвинута по отношению к начальной фазе тактовых интервалов информационного сигнала на 90 .

Триггер 6 переключается по переднему фронту тактовых импульсов (фиг.2в) в зависимости от уровня информационного сигнала (фиг.26), поступающего на его D-вход. Сигнал с выхода триггера 6 (фиг.2г) поступает на вход регистра 7 сдвига, на тактовые входы которого поступают прямой и инверсный тактовые сигналы (фиг.2в,д).

На выходах регистра 7 формируются копии сдвинутых на Т/4 сигналов (фиг.2е,е ). На входы сумматора 11 по модулю два поступают копии информационного сигнала (фиг,2г,е), сдвинутые относительно друг друга на Т/2. На выходе сумматора формируется сигнал (фиг.2ж) с низким уровнем на границах тактовых интервалов информационного си-гнала при переходе символа с 1 на 1 и с 1 на О. Этот сигнал поступает на информационный вход решающего блока 18, на I

тактовьй вход которого подается сигнал (фиг.2д) с выхода управляемого генератора 17 импульсов, который

и искажается из-за интегри- 40 подключен к С-входу делителя 21 час0

0

5

5

0

амплитудой (фиг.26), поступающий на D-вход триггера 6, на тактовый вход которого поступает сигнал с выхода управляемого генератора 17 импульсов (фиг.2в). При этом тактовый сигнал со стабильной скважностью 2 и частотой всегда находится во взаимосвязи с информационным сигналом таким образом, что начальная фаза тактового сигнала сдвинута по отношению к начальной фазе тактовых интервалов информационного сигнала на 90 .

Триггер 6 переключается по переднему фронту тактовых импульсов (фиг.2в) в зависимости от уровня информационного сигнала (фиг.26), поступающего на его D-вход. Сигнал с выхода триггера 6 (фиг.2г) поступает на вход регистра 7 сдвига, на тактовые входы которого поступают прямой и инверсный тактовые сигналы (фиг.2в,д).

На выходах регистра 7 формируются копии сдвинутых на Т/4 сигналов (фиг.2е,е ). На входы сумматора 11 по модулю два поступают копии информационного сигнала (фиг,2г,е), сдвинутые относительно друг друга на Т/2. На выходе сумматора формируется сигнал (фиг.2ж) с низким уровнем на границах тактовых интервалов информационного си-гнала при переходе символа с 1 на 1 и с 1 на О. Этот сигнал поступает на информационный вход решающего блока 18, на I

тактовьй вход которого подается сигнал (фиг.2д) с выхода управляемого генератора 17 импульсов, который

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ЦИФРОВОГО ПРИЕМНИКА | 1996 |

|

RU2138907C1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

| Дельта-кодек | 1989 |

|

SU1688412A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Устройство для корреляционного приема фазоманипулированных сигналов | 1984 |

|

SU1197137A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1988 |

|

SU1647901A1 |

Изобретение относится к электросвязи и может использоваться в приемниках кодоимпульсных сигналов. Декодер осуществляет декодирование линейного кода и формирование цифрового бинарного сигнала, длительность символов которого имеет высокую точность благодаря подстройке частоты и фазы управляемого генератора 17 импульсов. Изобретение обеспечивает повышение точности декодирования "0" или "1" информационного сигнала благодаря установке тактового сигнала в определенной фазе по отношению к информационному сигналу. Декодер содержит блок 1 согласования с линией, выполненный на фильтре 2 верхних частот, согласующем трансформаторе 3, корректирующем усилителе 4 и усилителе-ограничителе 5, триггеры 6, 8, 9, 20, 21, регистр 7 сдвига, сумматоры 10-12 по модулю два, фильтры 13, 14 нижних частот, вычитатель 15, интегратор 16, управляемый генератор 17 импульсов, решающий блок 18 и дифференциатор 19. 1 з.п. ф-лы. 2 ил.

рующих свойств реального кабеля, и на приемной стороне поступает на вход блока 1 согласования. В блоке 1 информационный сигнал вьщеляется фильтром 2 верхних частот и через, согла- сующий трансформатор 3 поступает на вход корректирующего усилителя 4. Корректирующий усилитель 4 компенсирует искажения, вносимые за счет неравномерности амплитудно-частотной характеристики (АХЧ) и нелинейности фазо-частотной характеристики (ФЧХ) линейного тракта. На выходе усилителя 4 вьщеляется сигнал (фиг.2а, плотная огибающая) с четко вьфажен- ными тактовыми интервалами при переходе сигналом нулевого уровня. Усилитель-ограничитель 5 формирует сигнал а крутыми фронтами и ограниченной

тоты на два. Делитель 21 частоты формирует тактовый сигнал (фиг.2и), который поступает на С-вход триггера 20, на D-вход которого подается сигнал (фиг.2ж) с выхода сумматора 11. Благодаря дифференциатору 19, формирующему импульсы сброса (фиг.2з), пр поступлении информационного сигнала с каждым единичным символом делитель 21 частоты устанавливается в исходное состояние, чем обеспечивается установка тактового сигнала с определенной фазой по отношению к информационному сигналу (фиг,2ж,3,и). Для согласования частоты управляемого генератора 17 импульсов с тактовой частотой информационного сигнала ис- пользуется схема автоматической подстройки частоты местного генератора

по рассогласованию фазы. Сумматор 10 по модулю два выделяет из информационного сигнала импульсы (фиг.2л передние фронты которых связаны с фронтами информационного сигнала. Сумматор 12 выдаля-ет сдвинутые копи таких же импульсов (фиг.2м), фронты которых связаны только с фронтами сигнала генератора 17 импульсов. Синалы с выхода сумматоров 10 и 12 по модулю два, прошедшие через фильтры 13 и 14,. сравниваются в вьгчитателе 15 и через интегратор 16 сигнал рассогласования поступает на вход управляемого генератора 17 импульсов. Если поступающие сигналы из линии и сигналы генератора 17 совпадают по частоте, а их фазы сдвинуты на 90 (что соответствует синхронному и синфазному режиму работы), то постоянная составляющая на выходе вычита- теля 15 практически равна нулю.

. При изменении одной из сравниваемых частот или при изменении фазового соотношения изменяется постоянная составляющая сигнала на выходе вычитателя 15, которая воздействует на выравнивание частоты генератора 17 импульсов. Для устойчивой подстройки частоты на выходе вычитателя 15 включено инерционное пропорционально-интегрирующее звено (интегратор 16), исключающее случайные броски управляющего сигнала.

Таким образом, благодаря постоянной скважности сигнала генератора 17 импульсов, а также автоматической подстройке частоты и фазы тактового сигнала, которым стробируется решающий блок 18, формируется цифровой бинарный сигнал (фиг.2к) с высокой точностью по длительности для каждой кодовой позиции.

Наибольшую эффективность декодер будет иметь в транзитных устройствах линейного тракта цифровой связи при передаче сигнала в каналах с импульсными и переходными помехами и при совмещении в низкочастотной области канала других сигналов. Формула изобретения 1. Декодер кода линии, содержащий блок согласования с линией, входы

4б

которого являются входами декодера, выход блока согласования с линией соединен с первым входом первого сумматора и информационным входом триггера, выход которого соединен с вторым входом первого сумматора, и решающий блок, первый выход которого является информационным выходом декодера, отличающийся что, с целью повышения точности декодирования, в декодер введены регистр, второй, третий сумматоры,, фильтры, вычитатель, интегратор и

генератор импульсов, инверсньй выход которого соединен с тактовым входом триггера и первым тактовым входом регистра, первый и второй выходы регистра соединены с первыми входами

20

соответственно второго и третьего

сумматоров, вторые входы которых объединены с информационным входом регистра и подключены к выходу триггера, выходы первого и третьего сум-

маторов соединены соответственно через первый и второй фильтры с первым и вторым входами вычитателя, выход которого соединен через интегратор с входом генератора импульсов, прямой выход которого соединен с вторым тактовым входом регистра и тактовым входом решающего блока, выход второ- рого сумматора соединен с информационным входом решающего блока, второй выход которого является тактовьм

выходом декодера.

содержит дифференциатор, элемент памяти и делитель частоты, выход дифференциатора соединен с установоч- Hbw входом делителя частоты, информационный вход элемента памяти объединен с входом дифференциатора и является информационным входом решающего блока, выход элемента памяти является первым выходом решающего блока, тактовый вход делителя частоты является тактовым входом решающего блока, выход делителя частоты соединен с тактовым входом элемента памяти и является вторым выходом решающего блока.

rLTL-FL-n

Фиг. 2

| Система для передачи цифровой информации по проводным каналам связи | 1985 |

|

SU1256233A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приемник цифрового биполярного сигнала | 1985 |

|

SU1305889A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-09-23—Публикация

1988-03-14—Подача