Изобретение относится к информационно-измерительной технике и мо- жет быть использовано как в аналого вьк, так и в цифровых приборах для измерения сдвига фаз,.

Цель изобретения - повышение точности измерения сдвига фаз.

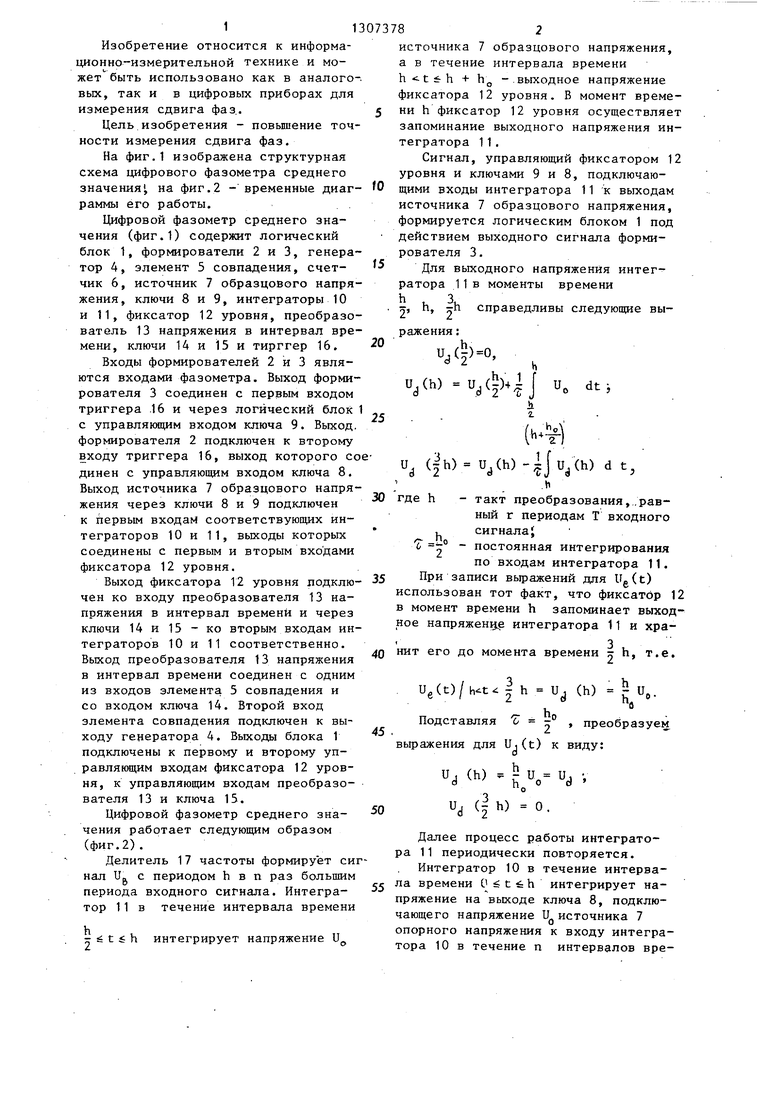

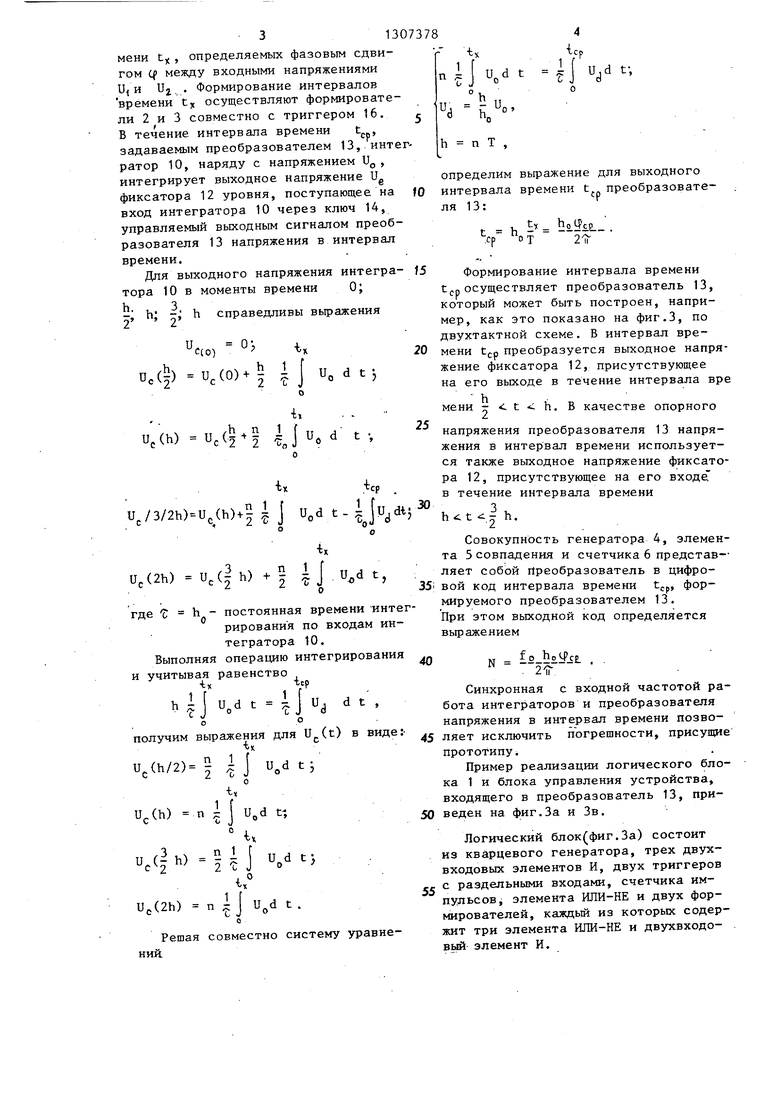

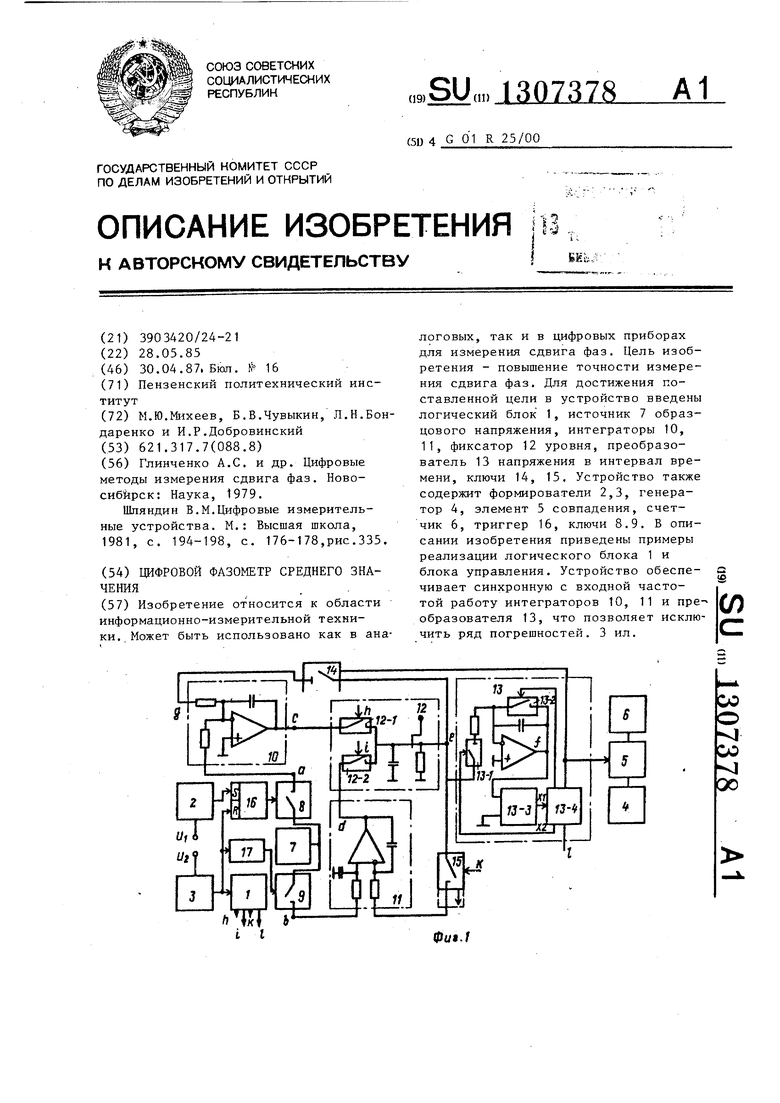

На фиг.1 изображена структурная схема цифрового фазометра среднего значения на фиг.2 - временные диаг раммы его работы..

Цифровой фазометр среднего значения (фиг.1) содержит логический блок 1, формирователи 2 и 3, генератор 4, элемент 5 совпадения, счетчик 6, источник 7 образцового напряжения, ключи 8 и 9, интеграторы 10 и 11, фиксатор 12 уровня, преобразователь 13 напряжения в интервал вре мени, ключи 14 и 15 и тирггер 16,

Входы формирователей 2 и 3 являются входами фазометра. Выход формирователя 3 соединен с первым входом триггера .16 и через логический блок с управляющим входом ключа 9. Выход формирователя 2 подключен к второму входу триггера 16, выход которого содинен с управляющим входом ключа 8. Выход источника 7 образцового напряжения через ключи 8 и 9 подключен к первым входам соответствующих интеграторов 10 и 11, выходы которьпс соединены с первым и вторым входами фиксатора 12 уровня.

Выход фиксатора 12 уровня подключен ко входу преобразователя 13 напряжения в интервал времени и через ключи 14 и 15 - ко вторым входам интеграторов 10 и 11 соответственно. Выход преобразователя 13 напряжения в интервал времени соединен с одним из входов элемента 5 совпадения и со входом ключа 14. Второй вход элемента совпадения подключен к выходу генератора 4. Выходы блока 1 подключены к первому и второму управляющим входам фиксатора 12 уровня, к управляющим входам преобразователя 13 и ключа 15.

Цифровой фазометр среднего значения работает следующим образом (фиг.2).

Делитель 17 частоты формирует синал и с периодом h в п раз большим периода входного сигнала. Интегратор 11 в течение интервала времени

интегрирует напряжение U

ражения:

источника 7 образцового напряжения, а в течение интервала времени + hg -.выходное напряжение фиксатора 12 уровня. В момент времени h фиксатор 12 уровня осуществляет запоминание выходного напряжения интегратора 11.

Сигнал, управляющий фиксатором 12 уровня и ключами 9 и 8, подключающими входы интегратора 11 к выходам источника 7 образцового напряжения, формируется логическим блоком 1 под действием выходного сигнала формирователя 3.

Для выходного напряжения интегратора 11 в моменты времени

h . 3,

J, п, -п справедливы следующие выия:

и

,( )о.

d .dФЧJ d

i

i

d (|h)- Uj(h)-||u;(h) d t,

где h

llo

такт преобразования,.равный г периодам Т входного сигналаJ

постоянная интегрирования по входам интегратора 11. При записи выражений для ив(с)

использован тот факт, что фиксатор 12 в момент времени h запоминает выходное напряжену;е интегратора 11 и хра3нит его до момента времени « h, т.е.

и

, (t)/

.|ь

и, (h)

5

Подставляя вьфаженкя для U

hf 2

(t) к

преобразуем виду:

и

(h) 2 и

3 ° I (| h) 0.

и.

Далее процесс работы интегратора 11 периодически повторяется.

Интегратор 10 в течение интервала времени О t б h интегрирует напряжение на выходе ключа 8, подключающего напряжение U источника 7

опорного напряжения тора 10 в течение п

к входу интегра- интервалов вре 31307378

мени t, определяемых фазовым сдвигом if между входными напряжениями Uj. . Формирование интервалов времени t, осуществляют формирователи 2 и 3 совместно с триггером 16.

В течение интервала времени

-ср.

задаваемым преобразователем 13, интератор 10, наряду с напряжением U, ,, интегрирует выходное напряжение Ug фиксатора 12 уровня, поступающее на вход интегратора 10 через ключ 14, управляемый выходным сигналом преобразователя 13 напряжения в интервал времени.

Для выходного напряжения интегра- тора 10 в моменты времени 0;

- h- - h 2 2

и

справедливы выражения 0 -Ь,

CtO) tx

Оеф и,(0)| I и, d t j

i,

u,(h) u,(s и u d t

(h).|l J U,d t-ljUjdiV 3

о /

напряжения жения в ин ся также в ра 12, при в течение

х

иЛ2Ь) иЛ| h) +

S М и 2 -г J

где о h - постоянная времени интерирования по входам интегратора 10. Выполняя операцию интегрирования

и учитывая равенство

tx

Ij.

d t

i.cp

-U.

d t

о0

получим выражения для ) в виде:

t.

U(h/2) и od t;

О

t«

U(h) n I j tt

tx

U,(| h) I 1 J

t

i

Uc(2h) n 1J t .

Решая совместно систему уравнений

1

:

О

t

4

VP

Ujd f,

h n Т ,

W

определим вьфажение для выходного интервала времени t преобразователя 13:

. 27

а- J5

Формирование интервала времени t(vp осуществляет преобразователь 13,

diV 3

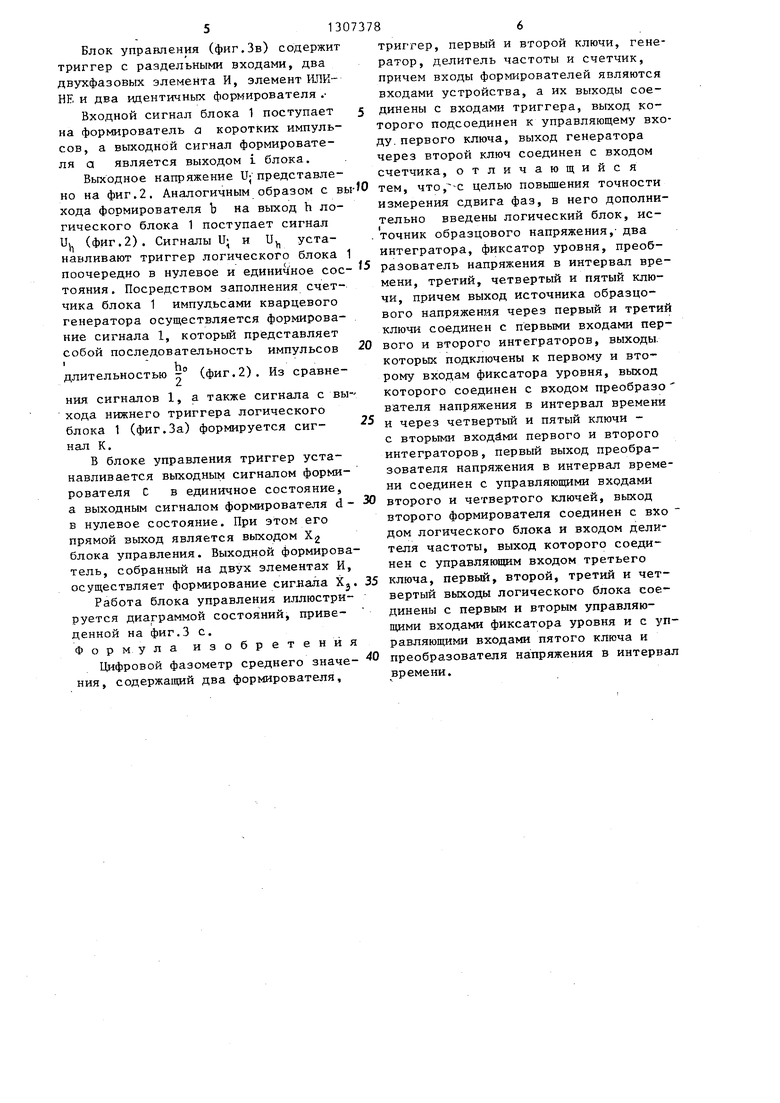

который может быть построен, например, как это показано на фиг.З, по двухтактной схеме. В интервал вре- 20 мени t(.p преобразуется выходное напряжение фиксатора 12, присутствующее на его выходе в течение интервала вре

мени - t : h. В качестве опорного

напряжения преобразователя 13 напряжения в интервал времени используется также выходное напряжение фиксатора 12, присутствующее на его входе в течение интервала времени

25

Совокупность генератора 4, элемента 5 совпадения и счетчика 6 представ - ляет собой Преобразователь в цнфро- 35i вой код интервала времени t,,.,, фор

ср мируемого преобразователем 13.

При зтом выходной код определяется выражением

N

fo he

2-

. .

Синхронная с входной частотой работа интеграторов и преобразователя напряжения в интервал времени позво- ляет исключить погрешности, присущие прототипу.

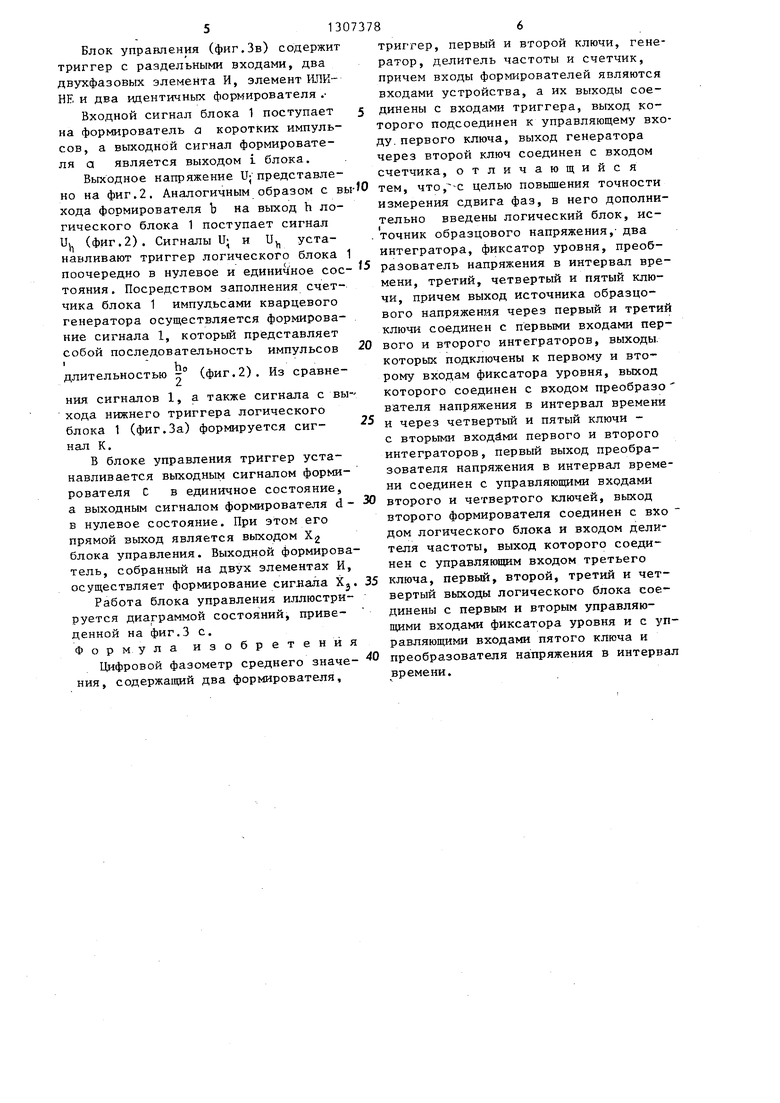

Пример реализации логического блока 1 и блока управления устройства, входящего в преобразователь 13, при- веден на фиг.За и Зв.

Логический блок(фиг.За) состоит из кварцевого генератора, трех двух- входовых элементов И, двух триггеров с раздельными входами, счетчика импульсов, элемента ИЛИ-НЕ и двух формирователей, каждый из которых содержит три элемента ИЛИ-НЕ и двухвходо- вый элемент И.

513

Блок управления (фиг.Зв) содержит триггер с раздельными входами, два двухфазовых элемента И, элемент ИЛИ- НЕ и два идентичных формирователя .

Входной сигнал блока 1 поступает на формирователь а коротких импульсов, а выходной сигнал формирователя а является выходом i блока.

Выходное напряжение U; представлено на фиг.2. Аналогичным образом с в хода формирователя Ъ на выход h логического блока 1 поступает сигнал и (фиг.2). Сигналы U; и U, устанавливают триггер логического блока поочередно в нулевое и единичное состояния. Посредством заполнения счетчика блока 1 импульсами кварцевого генератора осуществляется формирование сигнала 1, который представляет собой последовательность импульсов

длительностью -° (фиг.2). Из сравневы

НИН сигналов 1, а также сигнала с хода нижнего триггера логического блока 1 (фиг.За) формируется сигнал К.

В блоке управления триггер устанавливается выходным сигналом формирователя С в единичное состояние, а выходным сигналом формирователя d - в нулевое состояние. При этом его прямой выход является выходом Х блока управления. Выходной формирователь, собранный на двух элементах И, осуществляет формирование сигнала Х.

Работа блока управления иллюстрируется диаграммой состояний, приведенной на фиг.З с. Формула изобретения

Цифровой фазометр среднего значения, содержащий два формирователя.

5

О

5

0

5

триггер, первый и второй ключи, генератор, делитель частоты и счетчик, причем входы формирователей являются входами устройства, а их выходы соединены с входами триггера, выход которого подсоединен к управляющему входу, первого ключа, выход генератора через второй ключ соединен с входом счетчика, отличающийся тем, что,с целью повьшения точности измерения сдвига фаз, в него дополнительно введены логический блок, источник образцового напряжения,- два интегратора, фиксатор уровня, преобразователь напряжения в интервал времени, третий, четвертый и пятый ключи, причем выход источника образцового напряжения через первый и третий ключи соединен с первыми входами первого и второго интеграторов, выходы, которых подключены к первому и второму входам фиксатора уровня, выход которого соединен с входом преобразо вателя напряжения в интервал времени и через четвертый и пятый ключи - с вторыми входами первого и второго интеграторов, первый выход преобразователя напряжения в интервал времени соединен с управляющими входами второго и четвертого ключей, выход второго формирователя соединен с вхо дом логического блока и входом делителя частоты, выход которого соединен с управляющим входом третьего

5 ключа, первый, второй, третий и четвертый выходы логического блока соединены с первым и вторым управляющими входами фиксатора уровня и с управляющими входами пятого ключа и

0 преобразователя напряжения в интервал времени.

t

-t t

ipu. 2

К шунтирующему еяоквя f}

ff) -Т-t .

Фи9. 3

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ НИЗКОЧАСТОТНЫЙ ФАЗОМЕТР-ЧАСТОТОМЕР МГНОВЕННОГО ЗНАЧЕНИЯ | 1990 |

|

RU2024027C1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Преобразователь фазового сдвига в напряжение | 1981 |

|

SU953590A1 |

| Устройство для измерения температуры | 1987 |

|

SU1490504A1 |

| Устройство для измерения вихревого компонента скорости потока | 1984 |

|

SU1265619A1 |

| Низкочастотный цифровой фазометр | 1990 |

|

SU1784924A1 |

| Устройство для измерения вихревого компонента скорости потока | 1982 |

|

SU1016746A1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

| НИЗКОЧАСТОТНЫЙ ИЗМЕРИТЕЛЬ ФАЗОВОГО СДВИГА | 1992 |

|

RU2024028C1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1525915A1 |

Изобретение относится к области информационно-измерительной техники. Может быть использовано как в аналоговых, так и в цифровых приборах для измерения сдвига фаз. Цель изобретения - повышение точности измерения сдвига фаз. Для достижения поставленной цели в устройство введены логический блок 1, источник 7 образцового напряжения, интеграторы 10, 11, фиксатор 12 уровня, преобразователь 13 напряжения в интервал времени, ключи 14, 15. Устройство также содержит формирователи 2,3, генератор 4, элемент 5 совпадения, счетчик 6, триггер 16, ключи 8.9. В описании изобретения приведены примеры реализации логического блока 1 и блока управления. Устройство обеспечивает синхронную с входной частотой работу интеграторов 10, 11 и пре- образователя 13, что позволяет исключить ряд погрешностей. 3 ил. (О (Л W V i I 0U9.f

| Глинченко А.С | |||

| и др | |||

| Цифровые методы измерения сдвига фаз | |||

| Новосибирск: Наука, 1979 | |||

| Шляндин В.М.Цифровые измерительные устройства | |||

| М.: Высшая школа, 1981, с | |||

| Кран машиниста для автоматических тормозов с сжатым воздухом | 1921 |

|

SU194A1 |

| Приспособление для удаления таянием снега с железнодорожных путей | 1920 |

|

SU176A1 |

Авторы

Даты

1987-04-30—Публикация

1985-05-28—Подача