Изобретение относится к электроизмерительной технике и может быть использовано для построения высокоточных средств измерений.

Цель изобретения - повышение точности преобразования.

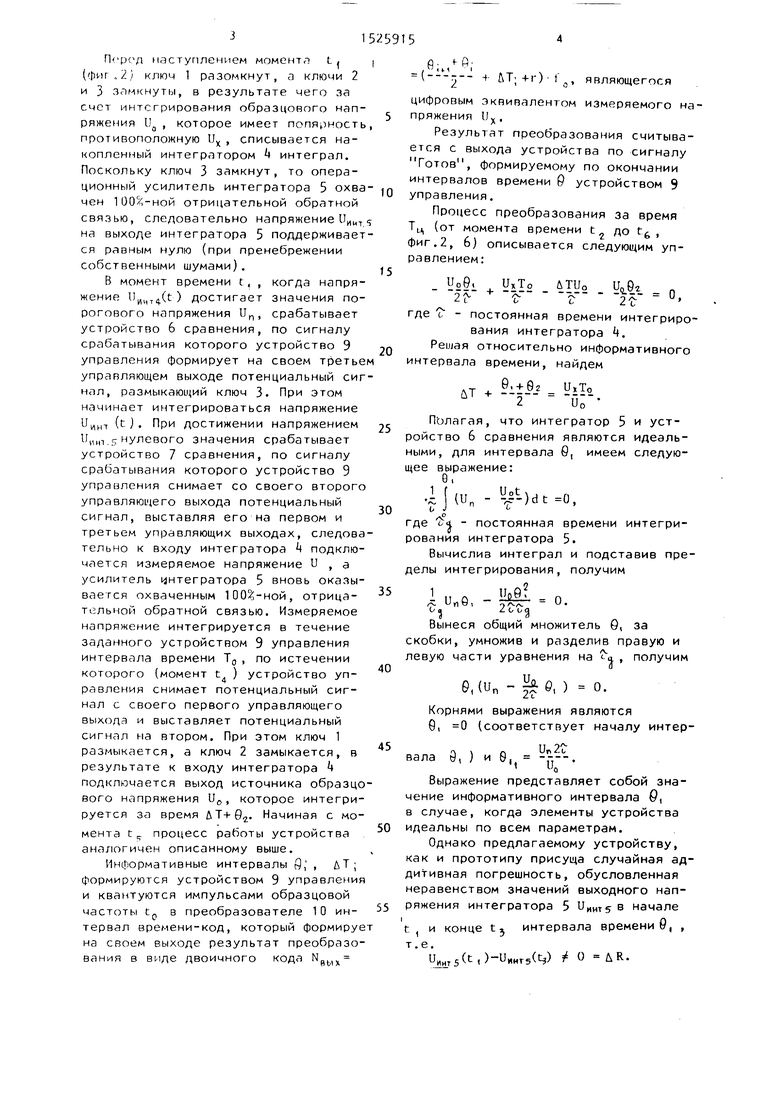

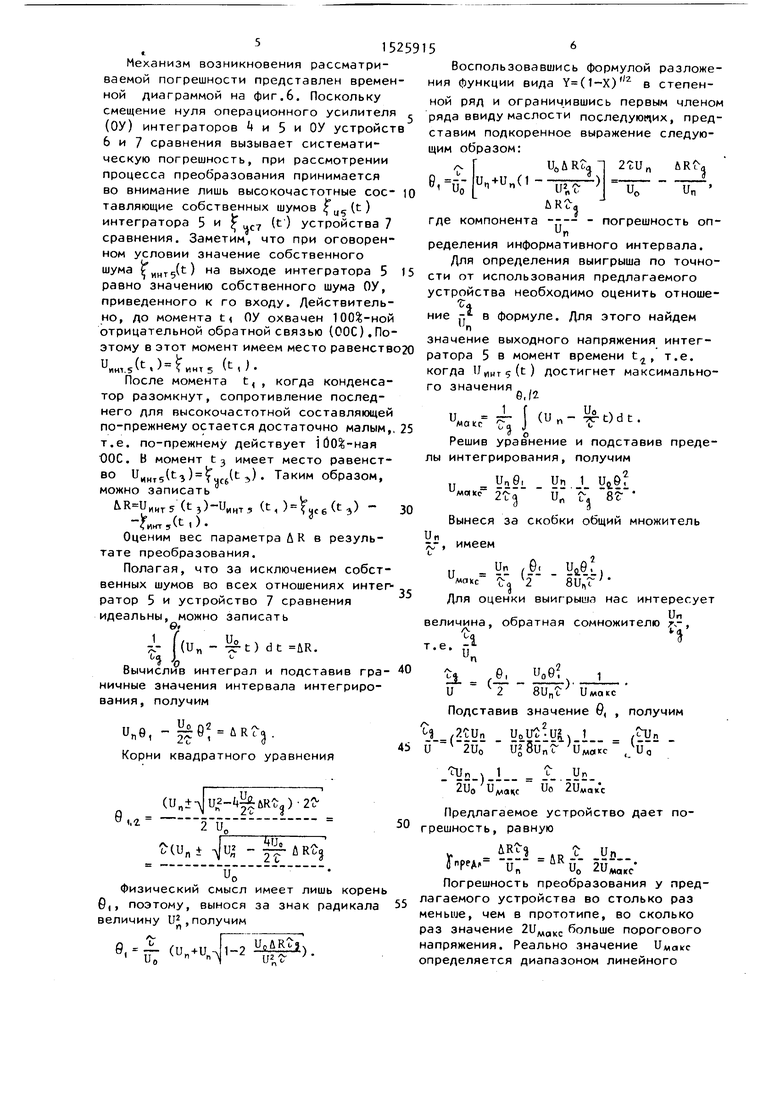

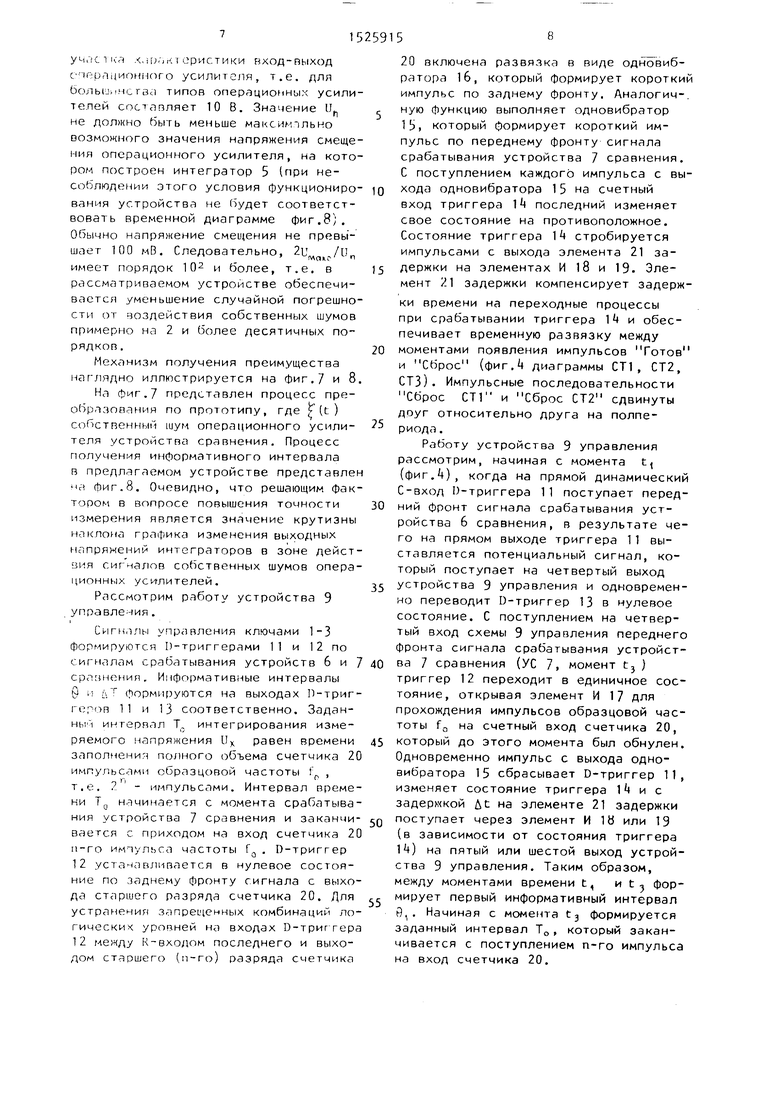

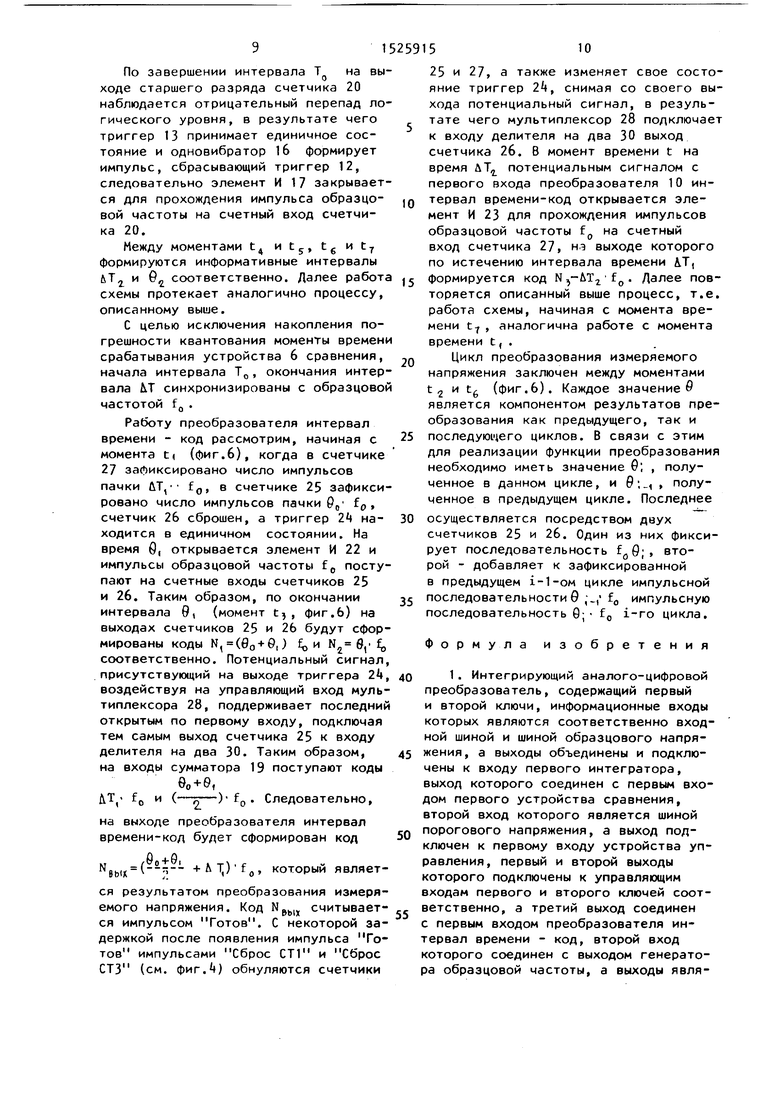

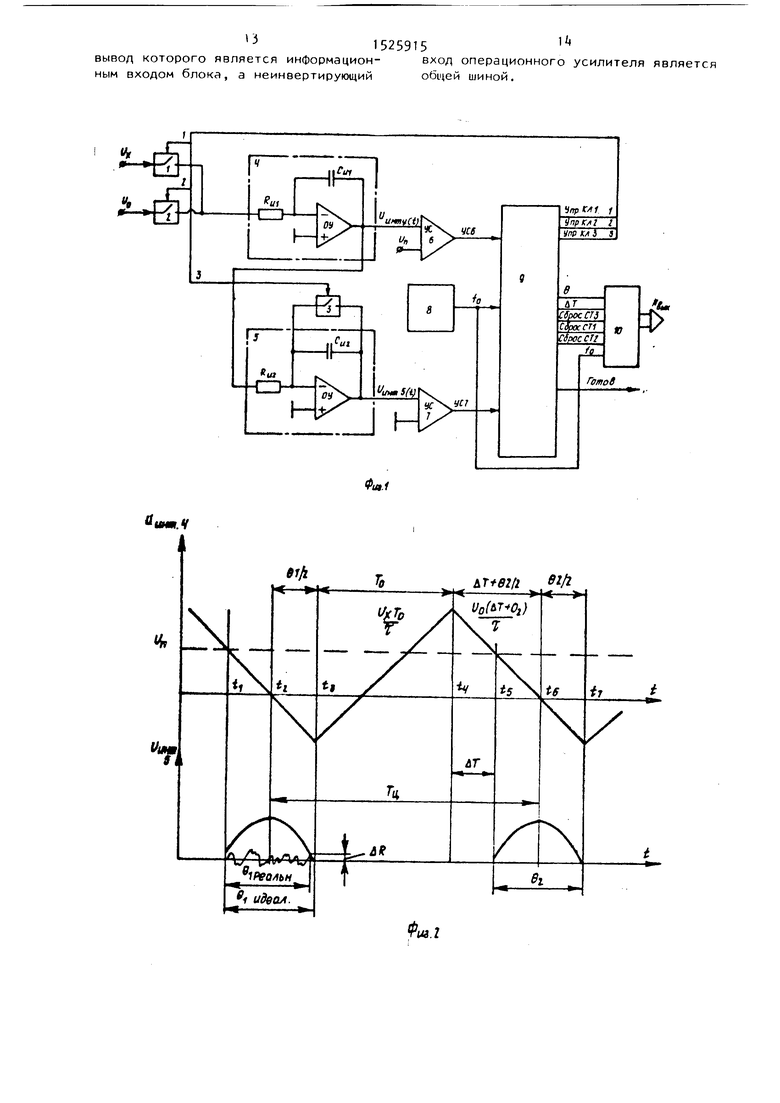

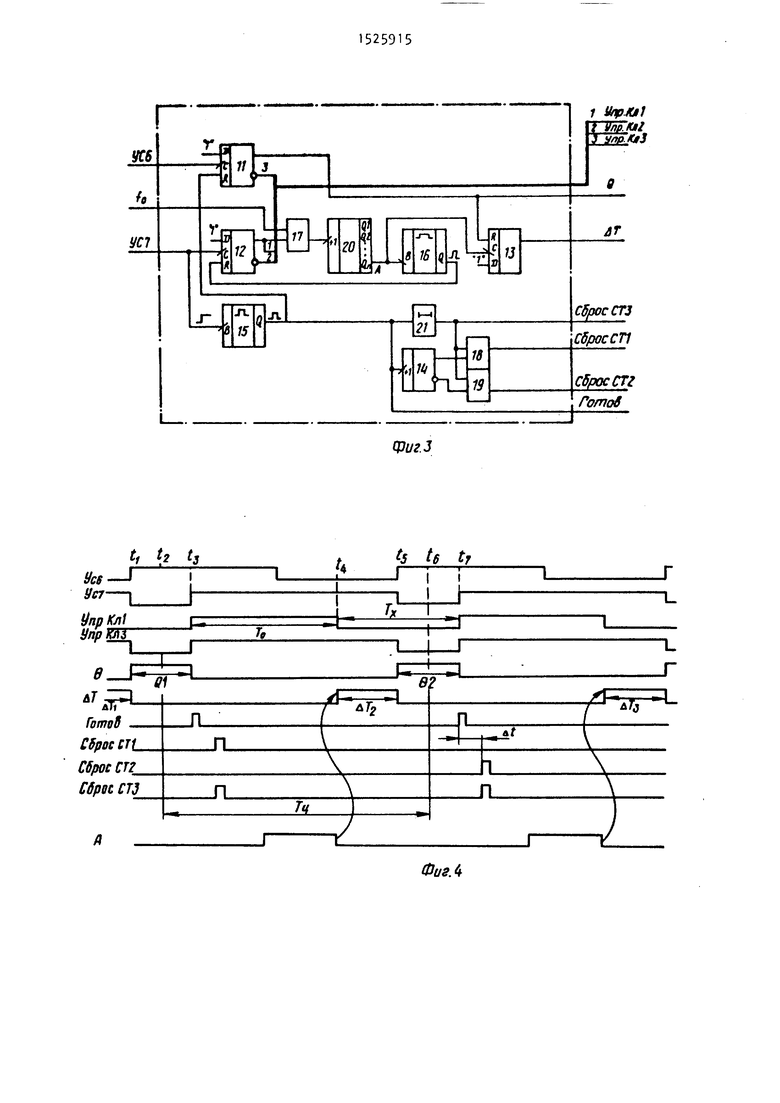

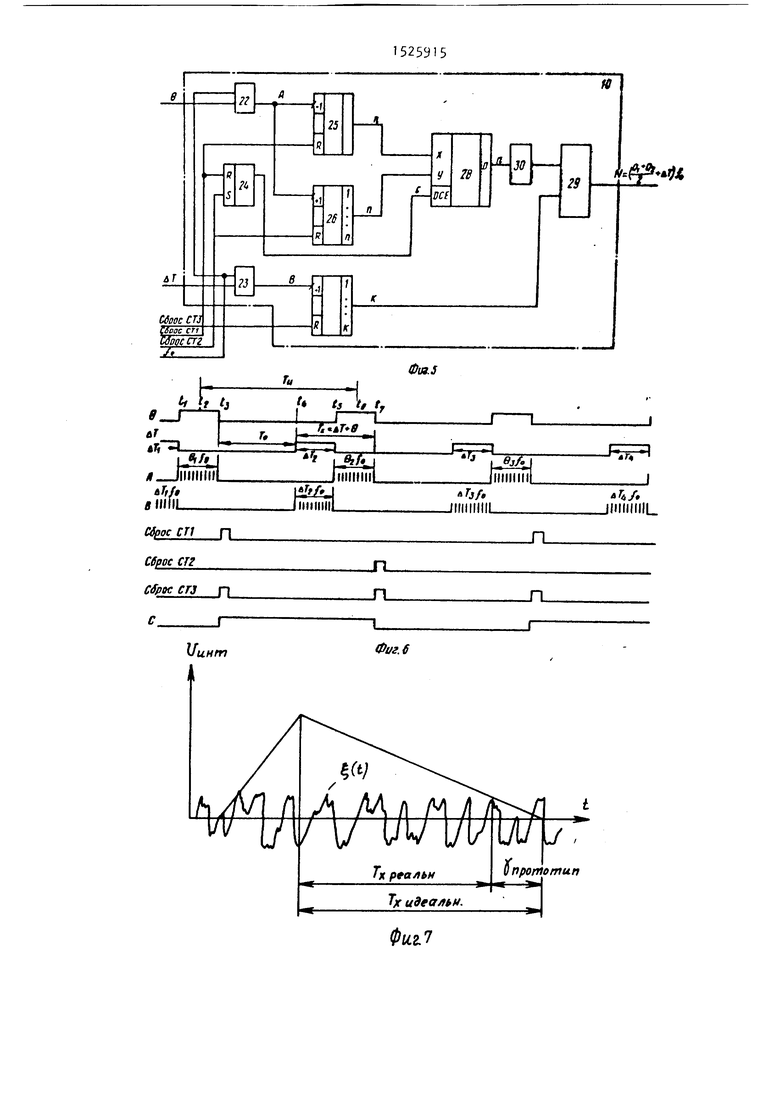

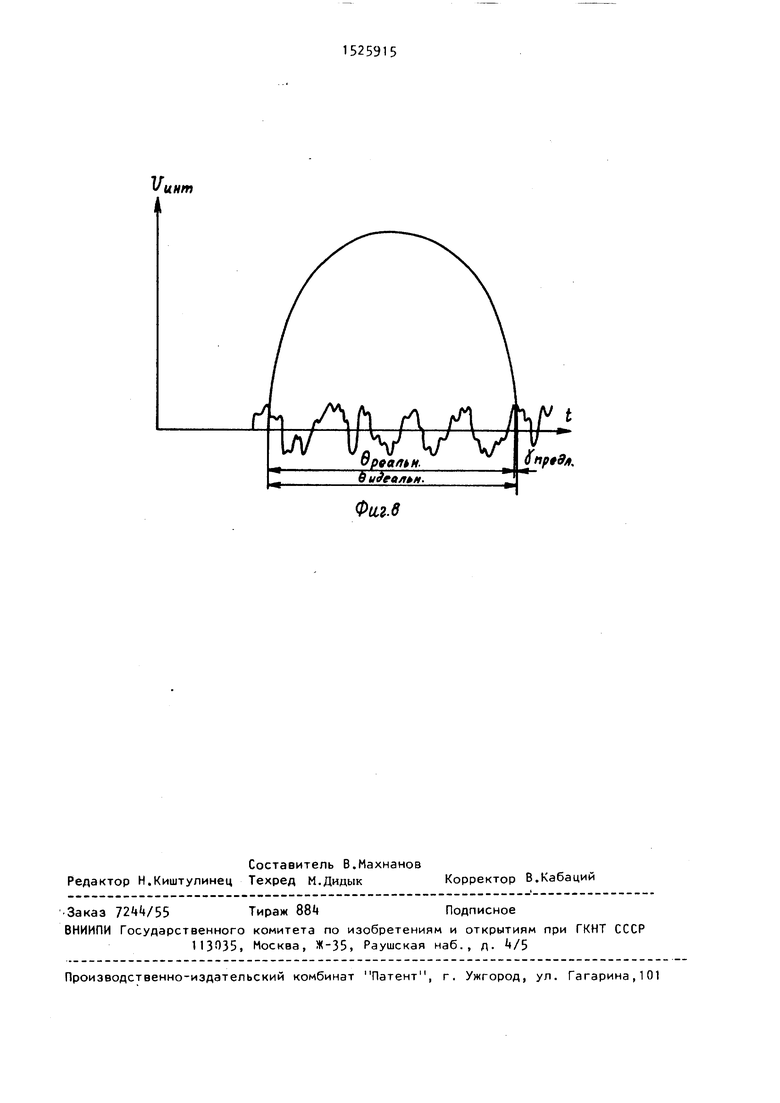

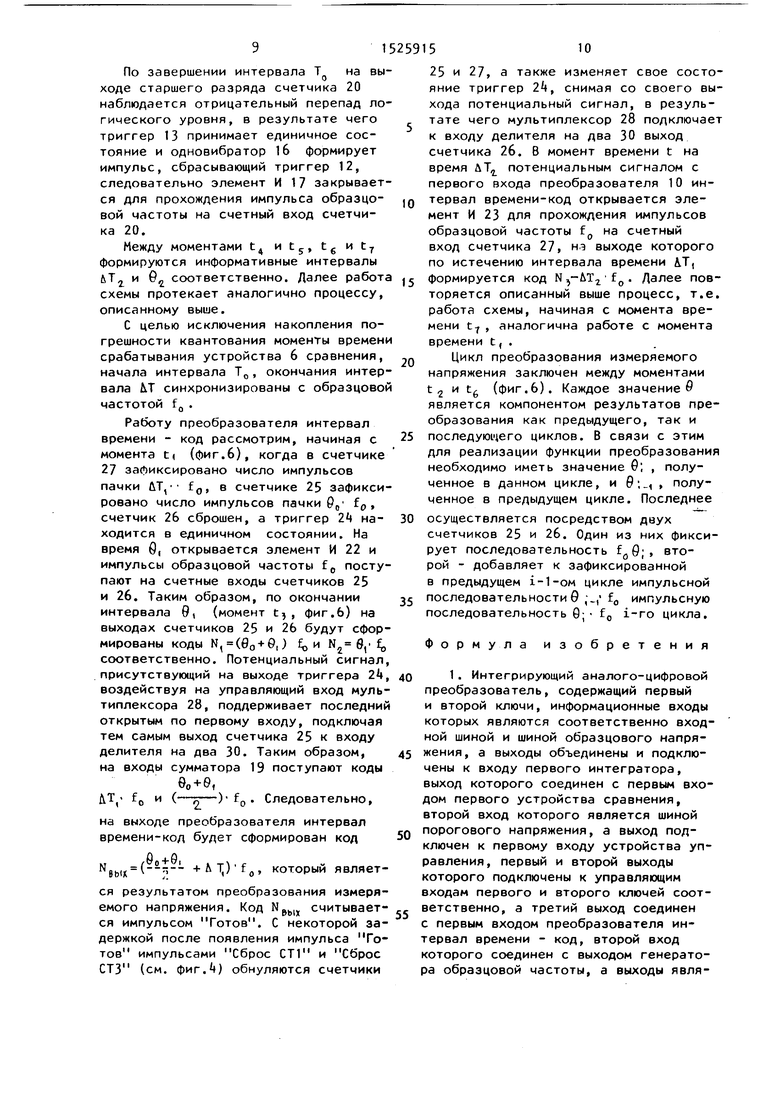

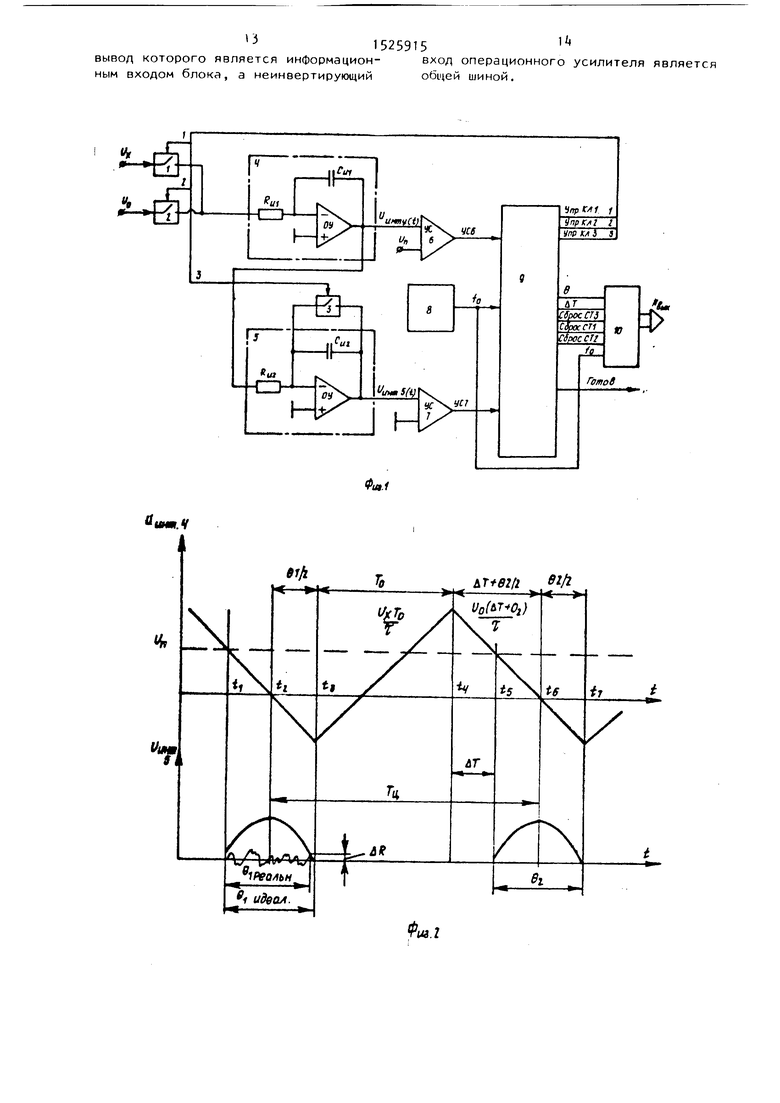

На фиг.1 представлена структурная схема устройства; на фиг.2 - временная диаграмма, поясняющая работу устройства; на фиг.З - один из возможных вариантов реализации устройства управления; на фиг. 4 - временная диаграмма, поясняющая работу устройства управления; на фиг.5 - одна из возможных реализаций преобразователя интервал времени-код; на фиг.6 - временная диаграмма работы преобразователя интервал времени-код; на фиг.7 процесс преобразования по прототипу; на фиг.8 - процесс получения информативного интервала в предлагаемом устройстве.

Интегрирующий АЦП содержит ключи 1-3, интеграторы и 5, устройства 6 и 7 сравнения, генератор 8 образцовой частоты, устройство 9 управления, преобразователь 10 интервал времени-код, устройство 3 управления содержит D-триггеры 11 - 13, триггер I со счетным входом, одновибраторы 15 и 16, элементы И 17 - 19, счетчик 20, элемент 21 задержки.

Преобразователь 10 интервал времени-код содержит элементы И 22 и 23, триггер , счетчики 25 - 27, мультиплексор 28, сумматор 29, делитель на два 30.

Временные диаграммы, представленные на фиг.2, полностью отражают процесс изменения напряжения на выходах - интеграторов + и 5.

Устройство работает следующим образом.

(Д наступлением момента L (фиг,/) ключ 1 разомкнут, а ключи 2 и 3 замкнуты, в результате чего за счет интегрирования образцового напряжения

которое имеет полярность,

противоположную и, списывается накопленный интегратором интеграл. Поскольку ключ 3 замкнут, то операционный усилитель интегратора 5 охвачен 100/,-ной отрицательной обратной связью, следовательно напряжение на выходе интегратора 5 поддерживается равным нулю (при пренебрежении собственными шумами),

В момент времени t, , когда напряжение n,(t ) достигает значения порогового напряжения U, срабатывает устройство 6 сравнения, по сигналу срабатывания которого устройство 9 управления формирует на своем третье управляющем выходе потенциальный сигнал, размыкающий ключ 3- При этом начинает интегрироваться напряжение (tj. При достижении напряжением tAMi.s улевого значения срабатывает устройство 7 сравнения, по сигналу срабатывания которого устройство 9 управления снимает со своего второго управляющего выхода потенциальный сигнал, выставляя его на первом и третьем управляющих выходах, следовательно к входу интегратора 4 подключается измеряемое напряжение U , а усилитель (интегратора 5 вновь оказывается охваченным , отрицательной обратной связью. Измеряемое напряжение интегрируется в течение заданного устройством 9 управления интервала времени Тд, по истечении которого (момент t ) устройство управления снимает потенциальный сигнал с своего первого управляющего выхода и выставляет потенциальный сигнал на втором. При этом ключ 1 размыкается, а ключ 2 замыкается, в результате к входу интегратора подключается выход источника образцового напряжения U, которое интегрируется за время ДТ+Ог- Начиная с момента t процесс работы устройства аналогичен описанному выше.

Информативные интервалы Я; , ДТ; формируются устройством 9 управления и квантуются импульсами образцовой частоты tp в преобразователе 10 интервал времени-код, который формируе на своем выходе результат преобразования в виде двоичного кода Npyj

fl. f fi

,...y:

-t- UT. +r)

являющегося измеряемого нацифровым эквивалентом пряжения Uj(.

Результат преобразования считывается с выхода устройства по сигналу Готов, формируемому по окончании интервалов времени 9 устройством 9 управления.

Процесс преобразования за время Тц (от момента времени t до t, фиг.2, 6) описывается следующим управлением:

-i:- . yil° uTUo Uo0j

л F - - -1

0.

где

Уо9.

2F г 2V г - постоянная времени интегрирования интегратора k. Решая относительно информативного интервала времени, найдем

йТ

9,+ 02 UxTo

2 иГ

Пьлагая, что интегратор 5 и устройство 6 сравнения являются идеальными, для интервала б, имеем следующее выражение: 0.

.11№„-а/-Ы.о,

где - постоянная времени интегрирования интегратора 3.

Вычислив интеграл и подставив пределы интегрирования, получим

1 „ Q - Ml д. и fl У , - „ ,4 о 11 / о oq

0.

Вынеся общий множитель О, за скобки, умножив и разделив правую и левую части уравнения на t a , получим

е, (Un - j е,) 0.

Корнями выражения являются

0, 0 (соответствует началу интер

вала

9, .. Up 2 (у , ) и 0,, ----.

Выражение представляет собой значение информативного интервала 9 в случае, когда элементы устройства идеальны по всем параметрам.

Однако предлагаемому устройству, как и прототипу присуща случайная аддитивная погрешность, обусловленная неравенством значений выходного напряжения интегратора 5 UMHTS в начале t и конце tj интервала времени 0, ,

т.е.

U,,,5((t) О ЛК.

515

Механизм возникновения рассматриваемой погрешности представлен временной диаграммой на фиг,6. Поскольку смещение нуля операционного усилителя (ОУ) интеграторов t и 5 и ОУ устройст 6 и 7 сравнения вызывает систематическую погрешность, при рассмотрении процесса преобразования принимается во внимание лишь высокочастотные сое- тавляющие собственных шумов (t) интегратора 5 и f с () устройства 7 сравнения. Заметим, что при оговоренном условии значение собственного

шума интз выходе интегратора 5 равно значению собственного шума ОУ, приведенного к го входу. Действительно, до момента ti ОУ охвачен 100%-ной отрицательной обратной связью (СОС). Поэтому в этот момент имеем место равенство

и„и,.5(.)нГ5 (tj.

После момента

{ t

когда конденса

тор разомкнут, сопротивление последнего для высокочастотной составляющей по-прежнему остается достаточно малым т.е. по-прежнемУ действует 1йО%-ная ООС. В момент t имеет место равенство инI5(tг) uc6(t ,). Таким образом, можно записать

&К ииИТ5 (tj) (t, ) uc6(t3) (t , ).

3

Оценим вес параметра ЛR в результате преобразования.

Полагая, что за исключением собственных шумов во всех отношениях интегратор 5 и устройство 7 сравнения идеальны, можно записать

Qf

J. f(u Ms -i Г

t) dt UR.

Вычислив интеграл и подставив гра- ничные значения интервала интегрирования, получим

Ur

UR

и„9,-ge

Корни квадратного уравнения

9,,.

(и,±д|и2- У|№)-21

2 и„

(и,

± л|и. 2t

URog

Uo Физический смысл имеет лишь корень

б,, поэтому, вынося за знак радикала 55 величину Ш, получим

е, (u uJi-2

Воспользовавшись формулой разложения функции вида Y(1-X) в степенной ряд и ограничившись первым членом ряда ввиду маслости последую их, представим подкоренное выражение следующим образом:

е,

U,AR6

2 ги,

где компонента --- - погрешность опии

ределения информативного интервала. Для определения выигрыша по точности от использования предлагаемого устройства необходимо оценить отношение

h и.

в формуле. Для этого найдем

значение выходного напряжения интегратора 5 в момент времени t, т.е. когда Пинт5(с) достигнет максимального значения

е./2

и

Maicc

j (u,)dt.

n

Решив уравнение и подставив предеинтегрирования, получим

5

0

5

0

5

и

макс

- Уй§1 УП. J. Ув.

и.

В с

; 5 Вынеся за скобки общий множитель

Un

яг, имеем

t

УП .0. . .

макс 2 8U,f Для оценки выигрыша нас интересует

,.Ur,

величина, обратная сомножителю ,

%

п

е, оО 1

SUnt UMOKC

Подставив значение О, , получим

..tUn . 1 ,Un U 2Uo UfSUn /u7

т.е.

tt r-1 - и 2

0

5

.4-.).l

Л

L

Uo

УП 2UA,

U/vanf

Предлагаемое устройство дает погрешность, равную

у. - 13 - AR -У- Ггред,- и„ , 2има.с- Погрешность преобразования у предлагаемого устройства во столько раз меньше, чем в прототипе, во сколько раз значение 2V больше порогового напряжения. Реально значение определяется диапазоном линейного

учг С1Ч л x.uJ. jK f ористики вход-выход С Пврлциониого усилителя, т.е. длл бoлы J.чcTSti типов оперяционных усилителей состагаляет 10 В. Значение 11 не должно быть меньше максимпльно возможного значения напряжения смещения операционного усилителя, на котором построен интегратор 5 (при несоблюдении этого условия функциониро- вания устройства не будет соответствовать временной диаграмме фиг.8). Обычно напряжение смещения не превышает ТОО мВ. Следовательно, 2u.,/Ur, имеет порядок 10 и более, т.е. в рассматриваемом устройстве обеспеми- вается уменьшение случайной погрешности от воздействия собственных шумов примерно на 2 и более десятичных порядков,

Механизм получения преимущества наглядно иллюстрируется на фиг.7 и 8.

На фиг.7 представлен процесс преобразования по прототипу, где Г() собственный шум операционного усили- теля устройства сравнения. Процесс получения информативного интервала в предлагаемом устройстве представлен на фиг.8. Очевидно, что решающим фактором в вопросе повышения точности измерения является значение крутизны наклона графика изменения выходных напряжений интеграторов в зоне действия сигналов собственных шумов операционных усилителей.

Рассмотрим работу устройства 9 управления.

Сигналы управления ключами 1-3 формируются 1)-триггерами 11 и 12 по сигналам срабатывания устройств 6 и 7 срагйнения. Информативные интервалы 0 : и формируются на выходах П-триг- геров 11 и 13 соответственно. Задан- ньг-1 интервал Т, интегрирования измеряемого напряжения 11 равен времени заполнения полного объема счетчика 20 импульсами образцовой частоты f , т.е. 2. - импульсами. Интервал времени Тд начинается с момента срабатывания устройства 7 сравнения и заканчи вается с приходом на вход счетчика 20 п-го импульса частоты Г . D-триггер 12 устанавливается в нулевое состояние по заднему фронту сигнала с выхода старшего разряда счетчика 20. Для устранения запре1ченных комбинаций логических уровней на входах D-триг гера 12 между К-входом последнего и выходом старшего (,п-го) разряда счетчика

20 включена развязка в виде одновиб- ратора 1б, который формирует короткий импульс по заднему фронту. Аналогичную функцию выполняет одновибратор 15, который формирует короткий импульс по переднему фронту сигнала срабатывания устройства 7 сравнения. С поступлением каждого импульса с выхода одновибратора 15 на счетный вход триггера последний изменяет свое состояние на противоположное. Состояние триггера 1А стробируется импульсами с выхода элемента 21 задержки на элементах И 18 и 19. Элемент 21 задержки компенсирует задержки времени на переходные процессы при срабатывании триггера Т и обеспечивает временную развязку между моментами появления импульсов Готов и Сброс (фиг. диаграммы СТ1 , СТ2, СТЗ). Импульсные последовательности Сброс СТ1 и Сброс СТ2 сдвинуты друг относительно друга на полпериода.

Работу устройства 9 управления рассмотрим, начиная с момента t (фиг.), когда на прямой динамический С-вход 1)-триггера 11 поступает передний фронт сигнала срабатывания устройства 6 сравнения, в результате чего на прямом выходе триггера 11 выставляется потенциальный сигнал, который поступает на четвертый выход устройства 9 управления и одновременно переводит D-триггер 13 в нулевое состояние. С поступлением на четвертый вход схемы 9 управления переднего фронта сигнала срабатывания устройства 7 сравнения (УС 7, момент tj ) триггер 12 переходит в единичное состояние, открывая элемент И 17 для прохождения импульсов образцовой частоты fo на счетный вход счетчика 20, который до этого момента был обнулен. Одновременно импульс с выхода одно- вибратора 15 сбрасывает D-триггер 11, изменяет состояние триггера 1 « и с зaдep кoй At на элементе 21 задержки поступает через элемент И 1Ь или 19 (в зависимости от состояния триггера I ) на пятый или шестой выход устройства 9 управления. Таким образом, между моментами времени t, и t формирует первый информативный интервал 9,. Начиная с момента t формируется заданный интервал „, который заканчивается с поступлением п-го импульса на вход счетчика 20.

По завершении интервала Т на выходе старшего разряда счетчика 20 наблюдается отрицательный перепад логического уровня, в результате чего триггер 13 принимает единичное состояние и одновибратор 1б формирует импульс, сбрасывающий триггер 12, следовательно элемент И 17 закрывается для прохождения импульса образцо- вой частоты на счетный вход счетчика 20.

Между моментами t ис.ь t формируются информативные интервалы ЬТ и 0 соответственно. Далее работа схемы протекает аналогично процессу, описанному выше.

С целью исключения накопления погрешности квантования моменты времени срабатывания устройства 6 сравнения, начала интервала Т, окончания интервала М синхронизированы с образцовой частотой fg.

Работу преобразователя интервал времени - код рассмотрим, начиная с момента t( (фиг.6), когда в счетчике 27 зафиксировано число импульсов пачки ЛТ, fg, в счетчике 25 зафиксировано число импульсов пачки 0ц fg, счетчик 26 сброшен, а триггер 2Ц на- ходится в единичном состоянии. На время 0, открывается элемент И 22 и импульсы образцовой частоты fp поступают на счетные входы счетчиков 25 и 26. Таким образом, по окончании интервала 9, (момент t, фиг.6) на выходах счетчиков 25 и 26 будут сформированы коды N,(00 + 0,) и , соответственно. Потенциальный сигнал, присутствующий на выходе триггера 2k, воздействуя на управляющий вход мультиплексора 28, поддерживает последний открытым по первому входу, подключая тем самым выход счетчика 25 к входу делителя на два 30. Таким образом, на входы сумматора 19 поступают коды

Эо+е,

fp и (-г--) fo. Следовательно,

на выходе преобразователя интервал времени-код будет сформирован код

N

,00+01

-

вых - +& Ij) f,, который является результатом преобразования измеряемого напряжения. Код f, считывается импульсом Готов. С некоторой задержкой после появления импульса Готов импульсами Сброс СТ1 и Сброс СТЗ (см. фиг.) обнуляются счетчики

25 и 27, а также изменяет свое состояние триггер 2, снимая со своего выхода потенциальный сигнал, в результате чего мультиплексор 28 подключае к входу делителя на два 30 выход счетчика 26. В момент времени t на время ДТ потенциальным сигналом с первого входа преобразователя 10 интервал времени-код открывается элемент И 23 для прохождения импульсов образцовой частоты f, на счетный вход счетчика 27, на выходе которого по истечению интервала времени iT, формируется код ,. Далее повторяется описанный выше процесс, т.е работа схемы, начиная с момента времени t-, , аналогична работе с момента времени t, .

Цикл преобразования измеряемого напряжения заключен между моментами t2 и t (фиг.6). Каждое значение б является компонентом результатов преобразования как предыдущего, так и последующего циклов. В связи с этим для реализации функции преобразовани необходимо иметь значение б; , полученное в данном цикле, и 0;, , полученное в предыдущем цикле. Последнее

осуществляется посредством двух счетчиков 25 и 26. Один из них фиксирует последовательность , второй - добавляет к зафиксированной в предыдущем i-1-ом цикле импульсной последовательности© ;, f импульсную последовательность 0; f i-ro цикла.

Форм у л а изобретения

1. Интегрирующий аналого-цифровой преобразователь, содержащий первый и второй ключи, информационные входы которых являются соответственно входной шиной и шиной образцового напряжения , а выходы объединены и подключены к входу первого интегратора, выход которого соединен с первым входом первого устройства сравнения, второй вход которого является шиной порогового напряжения, а выход подключен к первому входу устройства управления, первый и второй выходы которого подключены к управляющим входам первого и второго ключей соответственно, а третий выход соединен с первым входом преобразователя интервал времени - код, второй вход которого соединен с выходом генератора образцовой частоты, а выходы являются выходной шиной, отличающийся тем, что, с целью повышения точности преобразования, в него введены второй интегратор, второе устройство сравнения и третий ключ, информационный вход и выход которого подключены к первому и второму управляющим входам второго интегратора соответственно, информационный вход которого соединен с выходом первого интегратора, выход подключен к первому входу второго устройства сравнения, второй вход которого является общей шиной, а выход подключен к вто- рому входу устройства управления, третий вход которого соединен с выходом генератора образцовой частоты, четвертый выход - с управляющим входом третьего ключа, пятый, шестой, седьмой и восьмой выходы соединены соответственно с третьим, четвертым, пятым и шестым входами преобразователя интервал времени - код, девятый выход является шиной готовности ре- зультата.

2. Интегрирующий аналого-цифровой преобразователь по п.1, отличающий с я тем, что устройство управления выполнено на трех D-тригге- pax и триггере со счетным входом, двух одновибраторах, трех элементах И, счетчике и элементе задержки, причем первым входом устройства является

С-вход первого Г)-триггера, R-вход ко- торого соединен с выходом первого одновибратора и объединен со счетным входом триггера со счетным входом, входом элемента задержки и является девятым выходом устройства, шестым выходом которого является выход элемента задержки, седьмым и восьмым выходами - соответственно выходы первого и второго элементов И, первые входы которых подключены к выходу элемента задержки, а вторые входы соединены соответственно с прямым и инверсным выходами триггера со счетным входом, вход первого одновибрат.о- ра является вторым входом устройства и объединен с С-входом второго D- триггера, R-вход которого через второй одновибратор подключен к выходу старшего разряда счетчика, который подключен к С-входу третьего D-триг- гера, R-вход которого является пятым выходом устройства и соединен с прямым выходом первого D-триггера, инверсный выход которого является четвертым выходом устройства, а прямой и инверсный выходы второго П-триггер являются соответственно первым и вторым выходами устройства, при этом прямой выход второго D-триггера соединен с первым входом третьего элемента И, второй вход которого является третьим входом устройства, третьи выходом которого является выход третего D-триггера, а выход третьего элемента И соединен со счетным входом счетчика, D-входы первого, второго и третьего D-триггеров являются шино логической единицы.

3. Преобразователь по п.1, о т - лишающийся тем, что преобразователь интервала времени - код выполнен на двух элементах И, трех счетчиках, триггере, мультиплексоре, сумматоре и делителе частоты на два, через который выход мультиплексора соединен с первым входом сумматора, выходы которого являются выходами преобразователя, а второй вход соединен с выходом первого счетчика, вход сброса которого является четвертым входом преобразователя, а счетный вход соединен с выходом первого элемента И, первый вход которого является первым входом преобразователя, а второй вход является вторым входом преобразователя и объединен с первым входом второго элемента И, второй вход которого является третьим входо преобразователя, а выход соединен со счетными входами второго и третьего счетчиков, входы сбросов которых являются соответственно пятым и шестым входами преобразователя, а выходы соединены соответственно с первым и вторым информационными входами мультиплексора, управляющий вход которого подключен к выходу триггера, К- и S-входы которого являются пятым и шестым входами преобразователя соответственно.

k. Преобразователь по п.1, о т - личающийся тем, что второй интегратор выполнен на резисторе, конденсаторе и операционном усилителе, выход которого является выходом интегратора, вторым управляющим входом и через конденсатор соединен с инвертирующим входом операционного усилителя, который является первым управляющим входом блока и соединен с первым выводом резистора, второй

1525915

вывод которого является информацион- вход операционного усилителя является ным входом блока, а неинвертирующий общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ НИЗКОЧАСТОТНЫХ КОЛЕБАНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2028628C1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1345345A1 |

| Многоканальный преобразователь сопротивления в код | 1986 |

|

SU1411684A1 |

| Устройство для измерения температуры | 1987 |

|

SU1490504A1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Нелинейный преобразователь | 1988 |

|

SU1674172A1 |

| Способ интегрирующего аналого-цифрового преобразования | 1987 |

|

SU1438002A1 |

| Цифровой вольтметр эффективных значений | 1976 |

|

SU605312A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

Изобретение относится к области электроизмерительной техники и предназначено для создания высокоточных аналого-цифровых преобразователей постоянного напряжения. Целью изобретения является повышение точности преобразования. Поставленная цель достигается тем, что в интегрирующий аналого-цифровой преобразователь, содержащий преобразователь интервал времени - код, устройство управления, устройство сравнения, интегратор, генератор образцовой частоты и три ключа, введены второй интегратор, второе устройство сравнения и дополнительные связи. 3 з.п. ф-лы, 8 ил.

KUI

-сэsn

ОУ У

.J И

шт.Ч

УлрГ/ff /

/

УДО W 3 J

itg

Готов

ti f2 t,

y te tf

ФигЛ

Л

лг

Сбоос СГЗ

t

Ги

Мрос СП П

Сброс сгг

1инт

Ш

.5

Л

Фиг. 6

Фи.г,7

инт

Фиг-в

Авторы

Даты

1989-11-30—Публикация

1988-03-31—Подача