Изобретение относится к импу.тьсной технике и может быть использовано в устройствах автоматики и вычислительной техники.

Цель изобретения - повышение надежности.

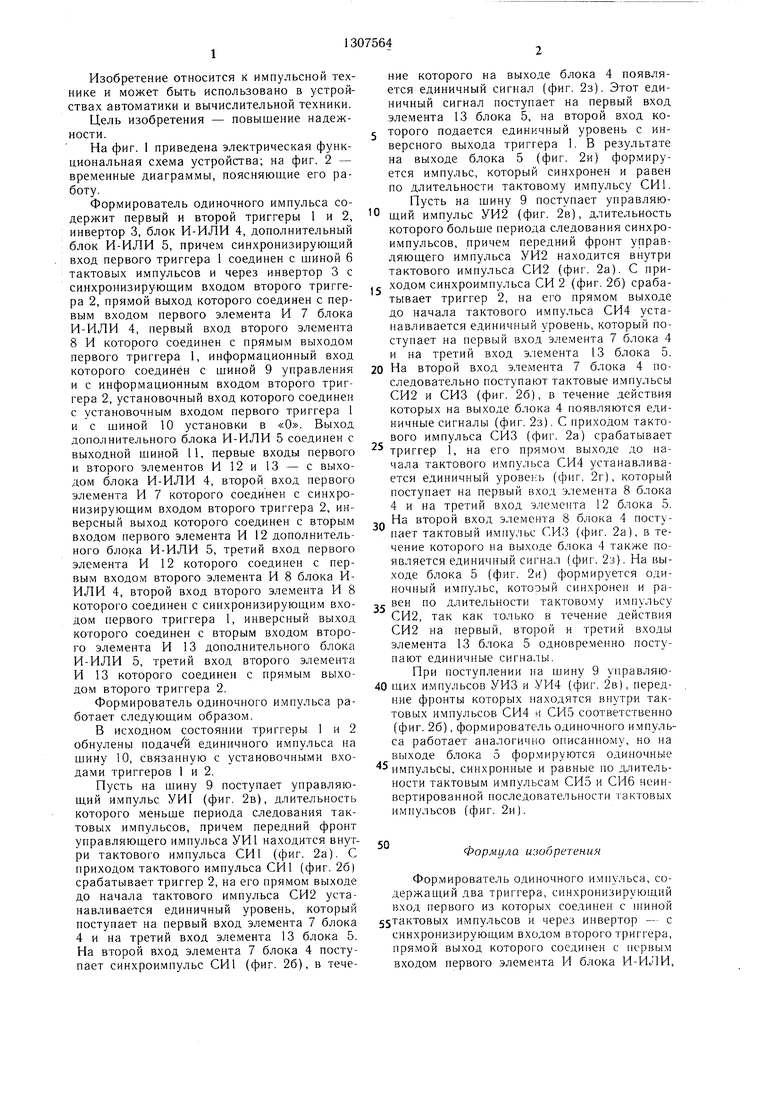

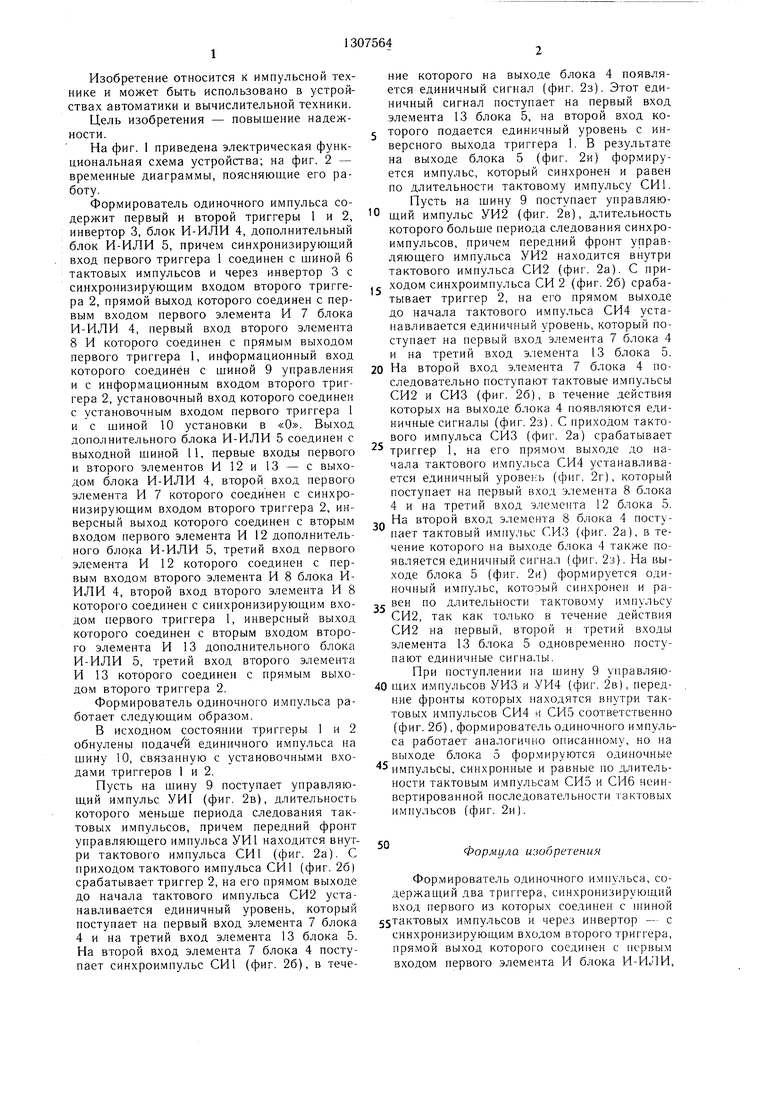

На фиг. 1 приведена электрическая функциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Формирователь одиночного импульса содержит первый и второй триггеры 1 и 2, инвертор 3, блок И-ИЛИ 4, дополнительный блок И-ИЛИ 5, причем синхронизирующий вход первого триггера 1 соединен с щиной 6 тактовых импульсов и через инвертор 3 с синхронизирующим входом второго триггера 2, прямой выход которого соединен с первым входом первого элемента И 7 блока И-ИЛИ 4, первый вход второго элемента 8 И которого соединен с прямым выходом первого триггера 1, информационный вход которого соединён с тиной 9 управления и с информационным входом второго триггера 2, установочный вход которого соединен с установочным входом первого триггера 1 и с шиной 10 установки в «О. Выход дополнительного блока И-ИЛИ 5 соединен с выходной шиной 11, первые входы первого и второго элементов И 12 и 13 - с выходом блока И-ИЛИ 4, второй вход первого элемента И 7 которого соединен с синхронизирующим входом второго триггера 2, инверсный выход которого соединен с вторым входом первого элемента И 12 дополнительного блока И-ИЛИ 5, третий вход первого элемента И 12 которого соединен с первым входом второго элемента И 8 блока И- ИЛИ 4, второй вход второго элемента И 8 которого соединен с синхронизирующим входом первого триггера 1, инверсный выход которого соединен с вторым входом второго элемента И 13 дополнительного блока И-ИЛИ 5, третий вход второго элемента И 13 которого соединен с прямым выходом второго триггера 2.

Формирователь одиночного импульса работает следующим образом.

В исходном состоянии триггеры 1 и 2 обнулены подачей единичного импульса на шину 10, связанную с установочными входами триггеров 1 и 2.

Пусть на шину 9 поступает управляющий импульс УИ1 (фиг. 2в), длительность которого меньще периода следования тактовых импульсов, причем передний фронт управляющего импульса УИ1 находится внутри тактового импульса СИ1 (фиг. 2а). С приходом тактового импульса СИ1 (фиг. 26) срабатывает триггер 2, на его прямом выходе до начала тактового импульса СИ2 устанавливается единичный уровень, который поступает на первый вход элемента 7 блока 4 и на третий вход элемента 13 блока 5. На второй вход элемента 7 блока 4 поступает синхроимпульс СИ1 (фиг. 26), в течение которого на выходе блока 4 появляется единичный сигнал (фиг. 2з). Этот единичный сигнал поступает на первый вход элемента 13 блока 5, на второй вход которого подается единичный уровень с инверсного выхода триггера 1. В результате на выходе блока 5 (фиг. 2и) формируется импульс, который синхронен и равен по длительности тактовому импульсу СИ1. Пусть на шину 9 поступает управляющий импульс УИ2 (фиг. 2в), длительность которого больше периода следования синхроимпульсов, причем передний фронт управляющего импульса УИ2 находится внутри тактового импульса СИ2 (фиг. 2а). С приходом синхроимпульса СИ 2 (фиг. 26) срабатывает триггер 2, на его прямом выходе до начала тактового импульса СИ4 устанавливается единичный уровень, который поступает на первый вход элемента 7 блока 4 и на третий вход элемента 13 блока 5.

На второй вход элемента 7 блока 4 последовательно поступают тактовые импульсы СИ2 и СИЗ (фиг. 26), Б течение действия которых на выходе блока 4 появляются единичные сигналы (фиг. 2з). С приходом тактового импульса СИЗ (фиг. 2а) срабатывает

триггер 1, на его прямом выходе до начала тактового импульса СИ4 устанавливается единичный уровень (фиг. 2г), который поступает на первый вход элемента 8 блока 4 и на третий вход элемента 12 блока 5. На второй вход элемента 8 блока 4 поступает тактовый импульс СИЗ (фиг. 2а), в течение которого на выходе блока 4 также появляется единичный сигнал (фиг. 2з). На выходе блока 5 (фиг. 2и) формируется одиночный импульс, котооый синхронен и ра

35

вен по длительности тактовому и.

СИ2, так как только в течение действия СИ2 на первый, второй и третий входы элемента 13 блока 5 одновре.менно поступают единичные сигналы.

При поступлении на шину 9 управляю- 40 щих импульсов УИЗ и УИ4 (фиг. 2 в), передние фронты которых находятся внутри тактовых импульсов СИ4 и СИ5 соответственно (фиг. 26), формирователь одиночного импульса работает аналогично описанному, но на выходе блока 5 фор.мируются одиночные импульсы, синхронные и равные по длительности тактовым импульсам СИ5 и СИ6 неин- вертнрованной последовательности тактовых импульсов (фиг. 2и).

45

50

Формула и:юбретения

Формирователь одиночного импульса, содержащий два триггера, синхронизирующий вход первого из которых соединен с пжной 55тактовых импульсов и через инвертор - с синхронизируюа1и.м входом второго триггера, прямой выход которого соединен с первым входом первого элемента И блока И-ИЛИ,

первый вход второго элемента И которого соединен с прямым выходом первого триггера, информационный вход которого соединен с шиной управления и с информационным входом второго триггера, установочный вход которого соединен с установочным входом первого триггера и с шиной установки в «О, выходную шину, отличающийся тем, что, с целью повышения надежности, в него введен дополнительный блок-И-ИЛИ, выход которого соединен с выходной шиной, первые входы первого и второго элементов И - с выходом блока Й-ИЛИ, второй вход первого элемента И которого соеff сйг и 1 Z И IZrl 1от Г,

е ж

ГЦ

динен с синхронизируюшим входом второго триггера, инверсный выход которого соединен с вторым входом первого элемента И дополнительного блока Й-ИЛИ, третий вход первого элемента И которого соединен с первым входом второго элемента И блока И-ИЛИ, второй вход второго элемента И которого соединен с синхронизирующим входом первого триггера, инверсный выход которого соединен с вторым входом второго элемента И дополнительного блока И- ИЛИ, третий вход второго элемента И которого соединен с прямым выходом второго триггера.

П Г

Ц)иг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь одиночного импульса | 1983 |

|

SU1150740A1 |

| Устройство для сопряжения модулей процессора | 1982 |

|

SU1056176A2 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1983 |

|

SU1133597A1 |

| Устройство для управления ленточным перфоратором | 1982 |

|

SU1049934A1 |

| Устройство для формирования маркера на экране двухгорловой электронно-лучевой трубки | 1983 |

|

SU1280432A1 |

| Устройство кодирования блоков информации | 1990 |

|

SU1785084A1 |

| Устройство для сдвига информации | 1985 |

|

SU1291962A1 |

| Масштабный преобразователь кодов | 1988 |

|

SU1569994A1 |

| Устройство для управления обменом информацией процессора с памятью | 1986 |

|

SU1325494A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

Изобретение может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения - повышение надежности устройства. Формирователь одиночного импульса содержит триггеры I и 2, инвертор 3 и блок И-ИЛИ 4. Для достижения поставленной цели в устройство введен блок И-ИЛИ 5 и образованы новые функциональные связи. 2 ил. (Л /J 7/ L . 12. оо о СП Oi 4 фиг./

| Устройство для формирования импульсов по перепадам потенциалов | 1979 |

|

SU855978A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Формирователь одиночного импульса | 1983 |

|

SU1150740A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1987-04-30—Публикация

1985-12-29—Подача