Предлагаемое изобретение относится к области вычислительной техники и передачи данных и предназначено для помехоустойчивого кодирования цифровой информации, например для защиты от ошибок устройств со-страничной организацией данных. Использование его целесообразно в случае кодирования с помощью пяти проверочных символов, обеспечивающих максимальную возможность исправления и обнаружения ошибок при декодировании.

Целью изобретения является увеличение помехоустойчивости устройства.

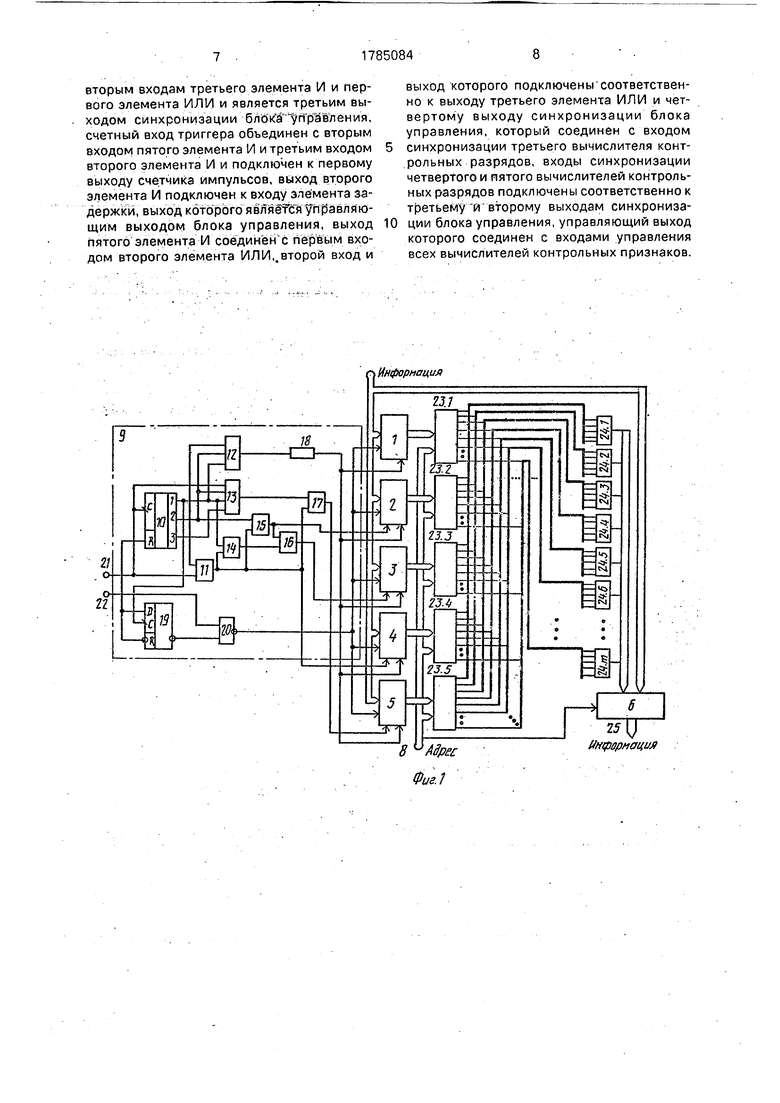

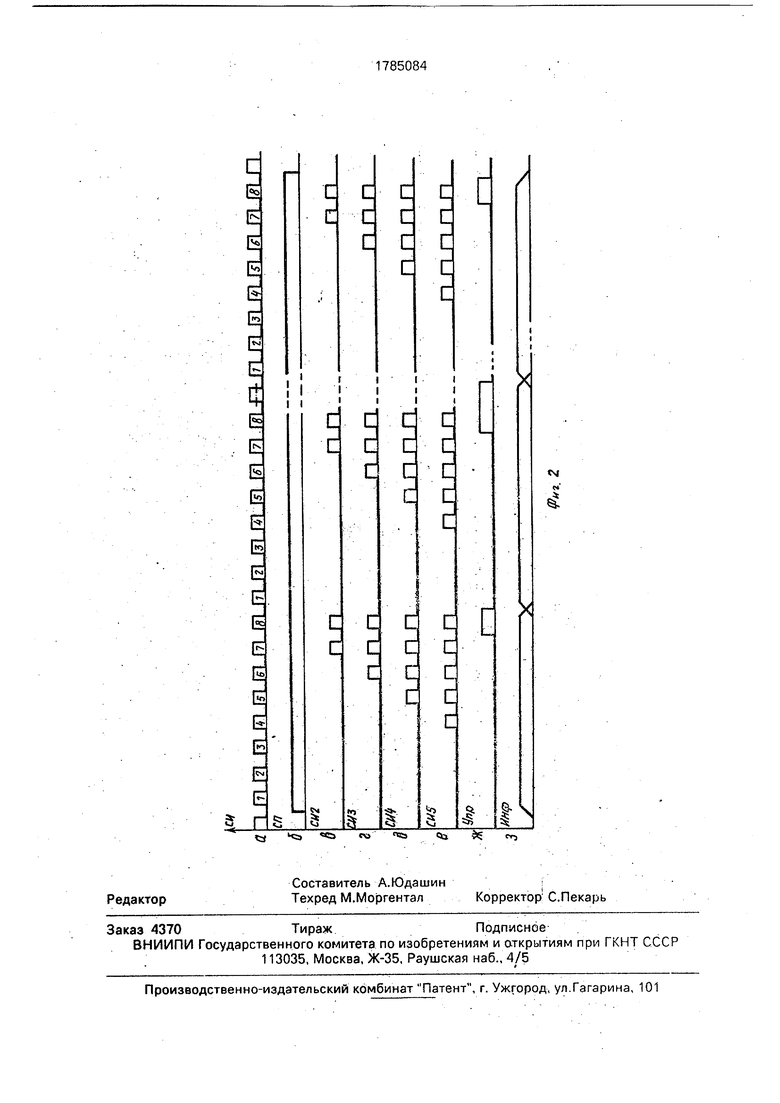

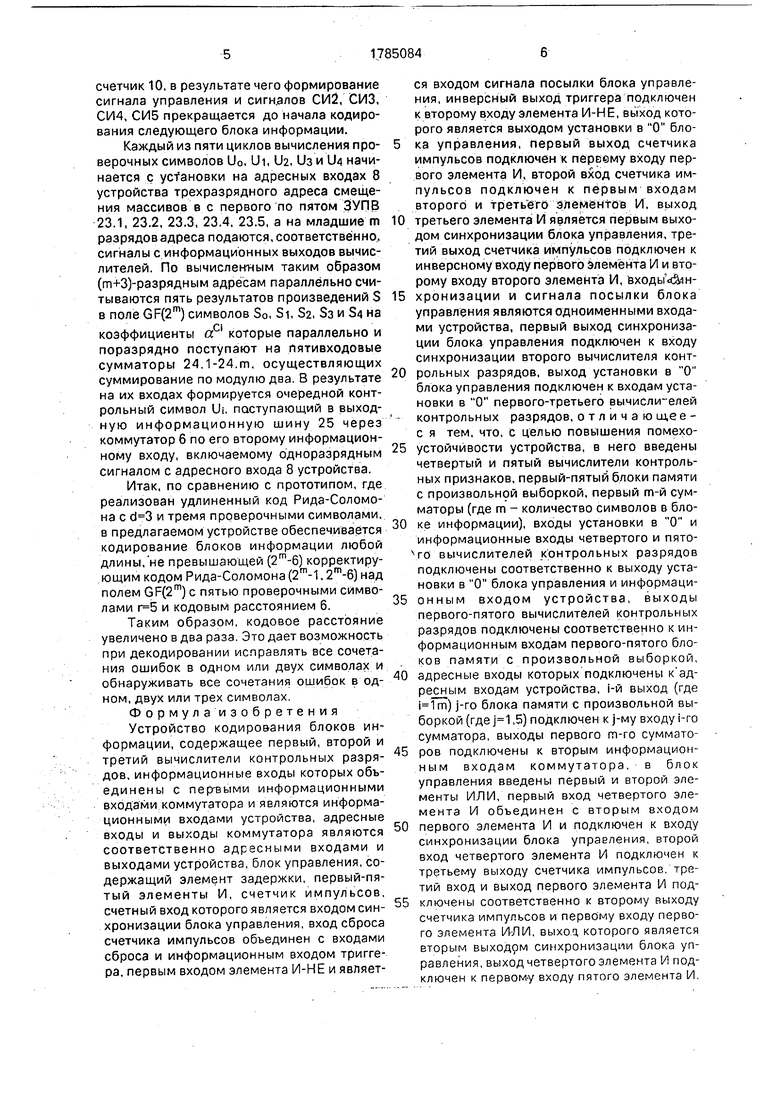

На фиг,1 представлена блок-схема устройства кодирования на фиг 2 - временная диаграмма работы предлагаемого устройства.

Устройство кодирования (фиг 1) содержит с первого пр пятый вычислители 1 2, 3 4 и 5, коммутатор 6, входную информационную шину 7, адресные входы 8, блок 9 управления, содержащий счетчик 10, с первого по пятый элементы И 13,12,15,11 и 14, первый и второй элементы ИЛИ 17 и 16, элемент 18 задержки, триггер 19, элемент И-НЕ 20, вход 21 синхронизации вход 22 сигнала посылки, а также параллельно подключенные с первого по пятое ЗУПВ 23.1-23 5, с первого по m-й сумматоры 24.1-24 гл и выходную информационную шину 25

Устройство работает следующим образом

От источника кодируемой информации на входную информационную шину 7 устройства поступают параллельно поразрядXI

00

ел о

00

N

но символы блока информации (фиг.2а), на вход 21 синхронизации блока 9 управления устройства подаются тактовые импульсы (фиг.2а), сигнал на входе 22 сигнала посылки блока 9 управления (фиг.2б), сопровождает поступление всех символов кодируемого блока информации. От получателя закодированной информации на адресные входы 8 устрЪйства предварительно подается код, соответствующий разрешению на передачу информации через первые входы коммутатора 6 на информационную выходную шину 25 устройства.

Кодирование каждого блока информации начинается с установки устройства в исходное состояние. Сигнал посылки блока 9 управления совместно с сигналом с инверсного выхода триггера 19 блока 9 управления поступает на вход элемента I/I-HE 20, на выходе которого вырабатывается сигнал установки в ноль блока 9 управления, устанавливающий в нулевое состояние триггеры первого вычислителя 1, регистры со второго по пятый вычислителей 2, 3, 4 и 5. После этого по заднему фронту первого сигнала с первого выхода счетчика 10 триггер 19 блока 9 управления устанавливается в единичное состояние и закрывает элемент И-НЕ 20. Далее в устройстве осуществляется формирование контрольных символов Sj ) из поступающих информационных символов X0,XiXk-1.

Период кодирования каждого символа Xi составляет восемь тактовых импульсов (ТИ). В блоке 9 управления в течение этого периода на выходе элемента 18 задержки вырабатывается один сигнал управления (фиг.2ж), на выходе третьего элемента И 15 два сигнала синхронизации второго вычислителя СИ2 (фиг.2в), на выходе второго элемента ИЛИ 16 три сигнала синхронизации третьего вычислителя СИЗ (фиг.2г), на выходе четвертого элемента И 11 четыре сигнала синхронизации четвертого вычислителя СИ4 (фиг.2д), на выходе первого элемента ИЛИ 17 пять сигналов синхронизации пятого вычислителя СИ5 (фиг.2). Сигналы ТИ с входа 21 синхронизации блока 9 управления поступают на счетный вход счетчика 10 и на входы четвертого и первого элементов И 11м 13. Элемент 18 задержки должен обеспечивать окончание сигнала управления после окончания последнего в каждом периоде сигнала синхронизации СИ5.

Первый сигнал синхронизации блока 9 управления СИ2 формируется на выходе третьего элемента И 15 при совпадении на его входах сигнала со второго выхода счетчика 10 и с выхода четвертого элемента И 11. Третий сигнал синхронизации блока 9

управления СИЗ формируется на выходе второго элемента ИЛИ 16 при наличии на его входах сигнала с выхода третьего элемента И 15 или сигнала с выхода пятого

элемента И 14, входы которого соединены с первым выходом счетчика 10 и с выходом четвертого элемента И 11 Второй сигнал синхронизации блока 9 управления СИ4 формируется на выходе четвертого элемен0 та И 11 при совпадении на его входах сигнала с третьего выхода счетчика 10 и сигнала ТИ. Четвертый сигнал синхронизации блока 9 управления СИ5 формируется на выходе первого элемента ИЛИ 17 при наличии на

5 его входах сигнала с выхода четвертого элемента И 11 или сигнала с выхода первого элемента И 13, два входа которого соединены с первым и вторым выходами счетчика 10, инверсный вход соединен с третьим вы0 ходом счетчика 10, а на четвертый вход поступает сигнал ТИ. Сигнал управления блока 9 управления формируется на выходе 18 задержки, вход которого соединен с выходом второго элемента И 12, три входа

5 которого соединены с тремя выходами счетчика 10, на счетный вход которого поступает сигнал ТИ, а на вход установки нуля-сигнал посылки.

Формирование контрольного символа

0 So осуществляется накапливанием в триггерах первого вычислителя 1 поразрядной суммы по модулю два поступающих на их счетные входы символов кодируемого блока информации. Синхронизация работы триг5 геров первого вычислителя осуществляется

по переднему фронту сигнала управления.

Формирование контрольных символов

Si, Sa, Зз и ЗА осуществляется в со второго

по пятом вычислителях 2, 3, 4 и 5. Символы

0 кодируемой информации поступают на первые входы первых блоков сумматоров. На входы синхронизации регистров в со второго по пятом вычислителях поступают соответственно сигналы СИ2, СИЗ, СИ4 и СИ5,

5 на входы управления поступает сигнал управления, низкий уровень которого задает режим циклического сдвига, а высокий уровень - режим занесения через соответствующие входы регистров.

0 После снятия сигналов последнего в блоке кодируемого информационного символа с входной информационной шины 7 в с первого по пятом вычислителях 1, 2, 3. 4 и 5 содержатся контрольные символы So, Si, 82.

5 5з и $4 кодируемого информационного блока, готовые для поочередного вычисления проверочных символов U0. Ui, U2, Us и U4.

Одновременно в блоке 9 управления по заднему фронту сигнала посылки устанавливаются в нулевое состояние триггер 19 и

счетчик 10, в результате чего формирование сигнала управления и сигналов СИ2, СИЗ, СИ4, СИ5 прекращается до начала кодирования следующего блока информации.

Каждый из пяти циклов вычисления проверочных символов Uo, Ui, U2. Us и U4 начинается с установки на адресных входах 8 устройства трехразрядного адреса смещения массивов в с первого по пятом ЗУПВ 23.1, 23.2, 23.3, 23.4, 23.5, а на младшие m разрядов адреса подаются, соответственно, сигналы с информационных выходов вычислителей. По вычисленным таким образом (т+3)-разрядным адресам параллельно считываются пять результатов произведений S в поле GF(2m) символов So, Si, 82, Зз и $4 на

коэффициенты сР которые параллельно и поразрядно поступают на пятивходовые сумматоры 24.1-24.т, осуществляющих суммирование по модулю два. В результате на их входах формируется очередной контрольный символ Ui. наступающий в выходную информационную шину 25 через коммутатор 6 по его второму информационному входу, включаемому одноразрядным сигналом с адресного входа 8 устройства.

Итак, по сравнению с прототипом, где реализован удлиненный код Рида-Соломона с и тремя проверочными символами, в предлагаемом устройстве обеспечивается кодирование блоков информации любой длины, не превышающей (2т-6) корректирующим кодом Рида-Соломона (2m-1, 2m-6) над полем GF(2m) с пятью проверочными символами и кодовым расстоянием 6.

Таким образом, кодовое расстояние увеличено в два раза. Это дает возможность при декодировании исправлять все сочетания ошибок в одном или двух символах и обнаруживать все сочетания ошибок в одном, двух или трех символах.

Формула изобретения

Устройство кодирования блоков информации, содержащее первый, второй и третий вычислители контрольных разрядов, информационные входы которых объединены с пер-выми информационными входами коммутатора и являются информационными входами устройства, адресные входы и выходы коммутатора являются соответственно адресными входами и выходами устройства, блок управления, содержащий элемент задержки, первый-пя- тый элементы И, счетчик импульсов, счетный вход которого является входом синхронизации блока управления, вход сброса счетчика импульсов объединен с входами сброса и информационным входом триггера, первым входом элемента И-НЕ и является входом сигнала посылки блока управления, инверсный выход триггера подключен к второму входу элемента И-НЕ, выход которого является выходом установки в О бло- ка управления, первый выход счетчика импульсов подключен к первему входу первого элемента И, второй вход счетчика импульсов подключен к первым входам второго и третьего элементов И, выход

0 третьего элемента И является первым выходом синхронизации блока управления, третий выход счетчика импульсов подключен к инверсному входу первого элемента И и второму входу второго элемента И, входьй&ж5 хронизации и сигнала посылки блока управления являются одноименными входами устройства, первый выход синхронизации блока управления подключен к входу синхронизации второго вычислителя конт0 рольных разрядов, выход установки в О блока управления подключен к входам установки в О первого-третьего вычисли елей

- контрольных разрядов, о т л и ч а ю ш,е е - с я тем, что, с целью повышения помехо5 устойчивости устройства, в него введены четвертый и пятый вычислители контрольных признаков, первый-пятый блоки памяти с произвольной выборкой, первый m-й сумматоры (где m - количество символов в бло0 ке информации), входы установки в О и информационные входы четвертого и пято- Чо вычислителей контрольных разрядов подключены соответственно к выходу установки в О блока управления и информаци5 онным входом устройства, выходы первого-пятого вычислителей контрольных разрядов подключены соответственно к информационным входам первого-пятого блоков памяти с произвольной выборкой,

0 адресные входы которых подключены к ад- входам устройства, i-й выход (где ) j-ro блока памяти с произвольной выборкой (где ,5) подключен к j-му входу i-ro сумматора, выходы первого гл-го суммато5 ров подключены к вторым информационным входам коммутатора, в блок управления введены первый и второй элементы ИЛИ, первый вход четвертого элемента И объединен с вторым входом

0 первого элемента И и подключен к входу синхронизации блока управления, второй вход четвертого элемента И подключен к третьему выходу счетчика импульсов третий вход и выход первого элемента И под5 ключены соответственно к второму выходу счетчика импульсов и первому входу первого элемента ИЛИ, выхоа которого является вторым выходрм синхронизации блока управления, выход четвертого элемента И подключен к первому входу пятого элемента И

вторым входам третьего элемента И и первого элемента ИЛИ и является третьим выходом синхронизации блок а управления, счетный вход триггера объединен с вторым входом пятого элемента И и третьим входом второго элемента И и подключен к первому выходу счетчика импульсов, выход второго элемента И подключен к входу элемента задержки, выход которого явля§тсяуправляющим выходом блока управления, выход пятого элемента И соединен с первым входом второго элемента ИЛ И,.второй вход и

0

выход которого подключены соответственно к выходу третьего элемента ИЛИ и четвертому выходу синхронизации блока управления, который соединен с входом синхронизации третьего вычислителя контрольных разрядов, входы синхронизации четвертого и пятого вычислителей контрольных разрядов подключены соответственно к третьему и второму выходам синхронизации блока управления, управляющий выход которого соединен с входами управления всех вычислителей контрольных признаков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования маркера на экране двухгорловой электронно-лучевой трубки | 1983 |

|

SU1280432A1 |

| Устройство кодирования блоков информации | 1984 |

|

SU1302439A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| Устройство управления загрузкой микропрограмм | 1983 |

|

SU1119019A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Устройство для сдвига информации | 1985 |

|

SU1291962A1 |

| Устройство для обработки видеоинформации | 1990 |

|

SU1732354A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1983 |

|

SU1133597A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

Изобретение относится к области вычислительной техники и передачи данных и предназначено для помехоустойчивого кодирования цифровой информации, например, для защиты от ошибок устройств со страничной организацией данных. Целью изобретения является увеличение помехоустойчивости устройства. Это достигается за счет реализации в устройстве процесса обработки кодируемой информации в соответствии с алгоритмом кода Рида-Соломона над полем CF(2m) с кодовым расстоянием , предназначенным для исправления ошибок в одном или двух символах и обнаружения ошибок в одном, двух или трех символах. Для этого в устройство кодирования блоков информации введены четвертый и пятый вычислители, с первого по пятое запоминающие устройства с произвольной выборкой, с первого по m-й сумматоры, а в блок управления введены первый и второй элементы ИЛИ. 1 п. ф-лы, 2 ил ел

Информация

АЗрес

w

Информация

| БИС обнаружения и исправления ошибок для систем памяти | |||

| - Зарубежная электронная техника, 1983 | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-30—Публикация

1990-10-26—Подача