Изобретение относится к автоматизации технологических процессов и может быть использовано для контроля разности углового, а также линейного перемещения двух объектов. Такими объектами могут быть два тела, вращающиеся в прямом или обратном направлении вокруг одной оси или линейно перемещающиеся в прямом или обратном направлении.

Целью изобретения является расширение функциональных возможностей при одновременном повышении функциональной надежности.

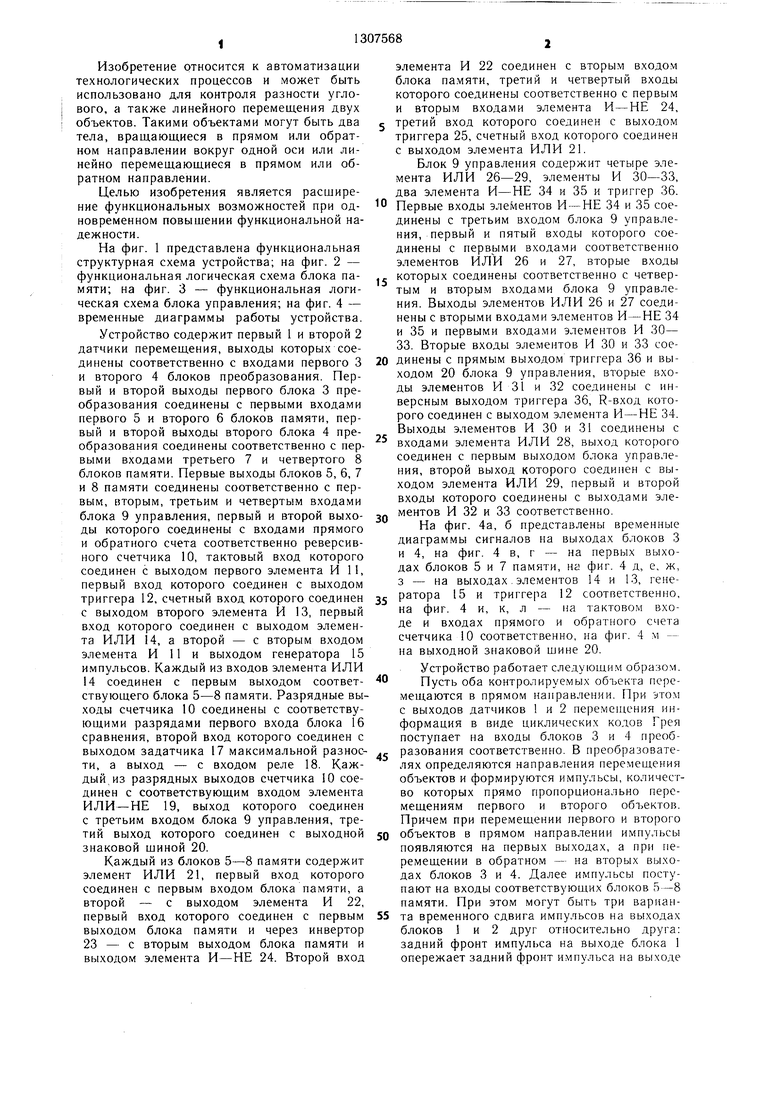

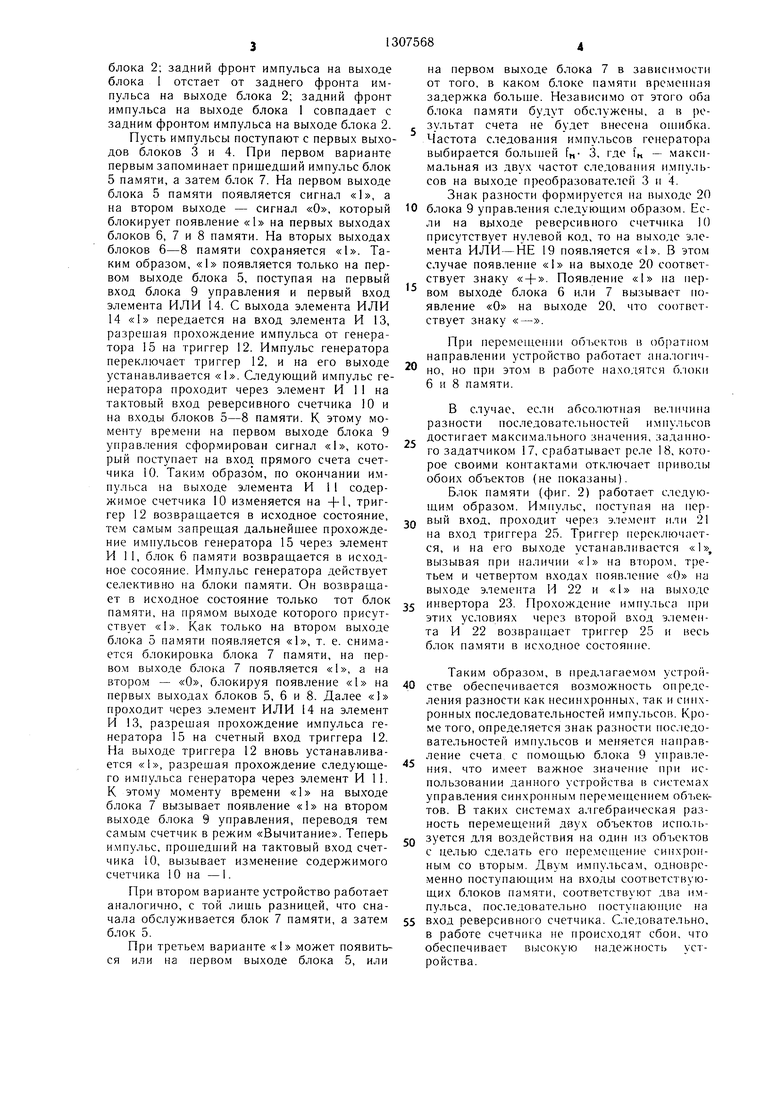

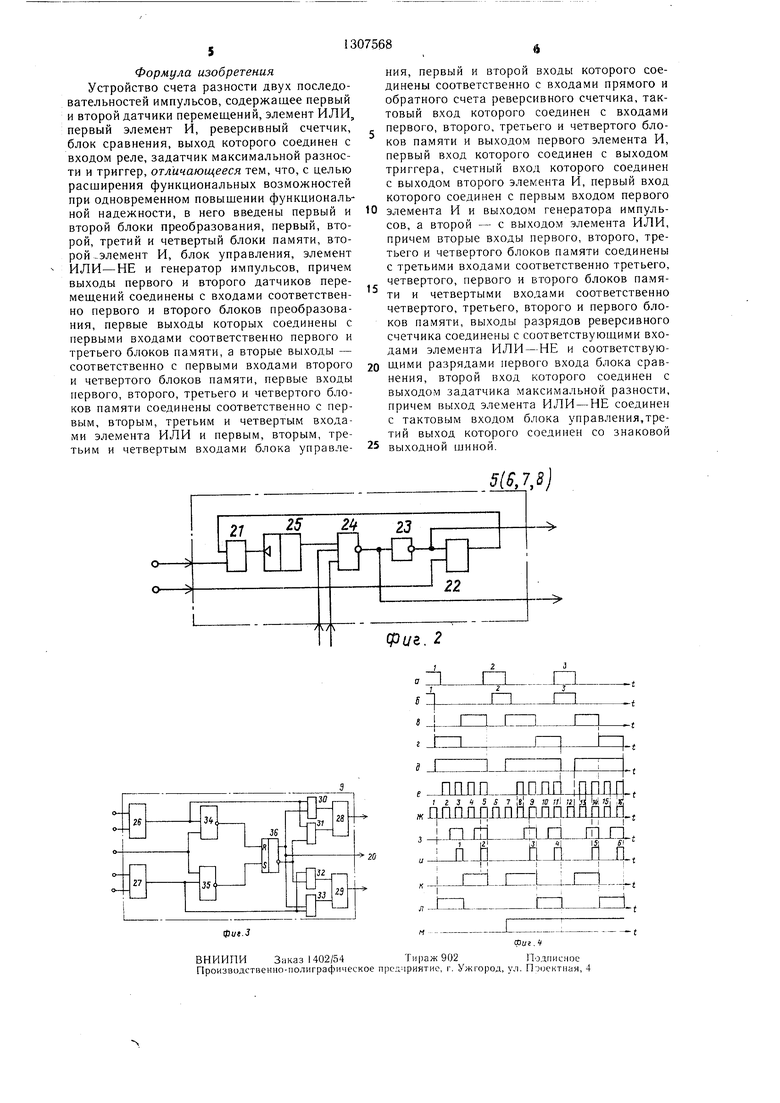

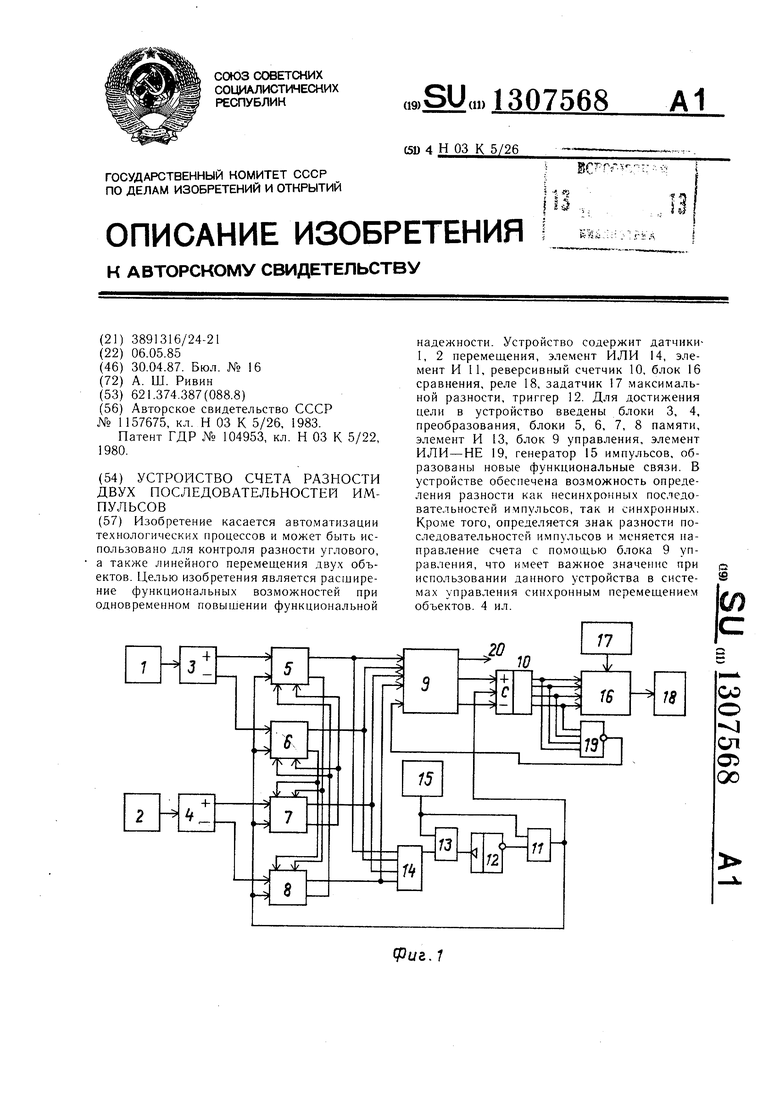

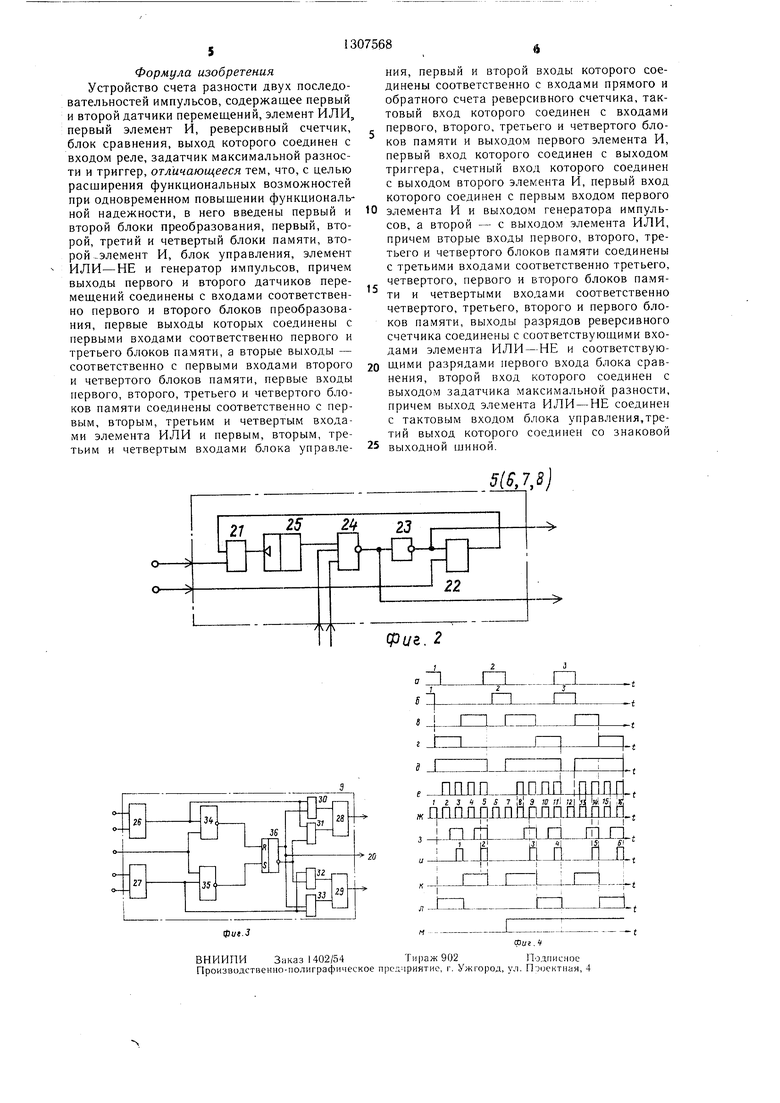

На фиг. 1 представлена функциональная структурная схема устройства; на фиг. 2 - функциональная логическая схема блока памяти; на фиг. 3 - функциональная логическая схема блока управления; на фиг. 4 - временные диаграммы работы устройства.

Устройство содержит первый 1 и второй 2 датчики перемещения, выходы которых соединены соответственно с входами первого 3 и второго 4 блоков преобразования. Первый и второй выходы первого блока 3 преобразования соединены с первыми входами первого 5 и второго 6 блоков памяти, первый и второй выходы второго блока 4 преобразования соединены соответственно с первыми входами третьего 7 и четвертого 8 блоков памяти. Первые выходы блоков 5, 6, 7 и 8 памяти соединены соответственно с первым, вторым, третьим и четвертым входами блока 9 управления, первый и второй выходы которого соединены с входами прямого и обратного счета соответственно реверсивного счетчика 10, тактовый вход которого соединен с выходом первого элемента И 11, первый вход которого соединен с выходом триггера 12, счетный вход которого соединен с выходом второго элемента И 13, первый вход которого соединен с выходом элемента ИЛИ 14, а второй - с вторым входом элемента И 11 и выходом генератора 15 импульсов. Каждый из входов элемента ИЛИ 14 соединен с первым выходом соответствующего блока 5-8 памяти. Разрядные выходы счетчика 10 соединены с соответствующими разрядами первого входа блока 16 сравнения, второй вход которого соединен с выходом задатчика 17 максимальной разности, а выход - с входом реле 18. Каждый из разрядных выходов счетчика 10 соединен с соответствующим входом элемента ИЛИ-НЕ 19, выход которого соединен с третьим входом блока 9 управления, третий выход которого соединен с выходной знаковой щиной 20.

Каждый из блоков 5-8 памяти содержит элемент ИЛИ 21, первый вход которого соединен с первым входом блока памяти, а второй - с выходом элемента И 22, первый вход которого соединен с первым выходом блока памяти и через инвертор 23 - с вторым выходом блока памяти и выходом элемента И-НЕ 24. Второй вход

элемента И 22 соединен с вторым входом блока памяти, третий и четвертый входы которого соединены соответственно с первым и вторым вхо.аами элемента И-НЕ 24, третий вход которого соединен с выходом триггера 25, счетный вход которого соединен с выходом элемента ИЛИ 21.

Блок 9 управления содержит четыре элемента ИЛИ 26-29, элементы И 30-33, два элемента И-НЕ 34 и 35 и триггер 36.

Первые входы элементов И - НЕ 34 и 35 соединены с третьим входом блока 9 управления, первый и пятый входы которого соединены с первьгми входами соответственно элементов ИЛИ 26 и 27, вторые входы

г которых соединены соответственно с четвертым и вторым входами блока 9 управления. Выходы элементов ИЛИ 26 и 27 соединены с вторыми входами элементов И-НЕ 34 и 35 и первыми входами элементов И 30- 33. Вторые входы элементов И 30 и 33 сое0 динены с прямым выходом триггера 36 и выходом 20 блока 9 управления, вторые входы элементов И 31 и 32 соединены с инверсным выходом триггера 36, Н-вход которого соединен с выходом элемента И-НЕ 34. Выходы элементов И 30 и 31 соединены с

входами элемента ИЛИ 28, выход которого соединен с первым выходом блока управления, второй выход которого соединен с выходом элемента ИЛИ 29, первый и второй входы которого соединены с выходами эле- ментов И 32 и 33 соответственно.

На фиг. 4а, б представлены временные диаграммы сигналов на выходах блоков 3 и 4, на фиг. 4 в, г - на первых выходах блоков 5 и 7 памяти, на фиг. 4 д, е, ж, 3 - на выходах, элементов 14 и 13, генес ратора 15 и триггера 12 соответственно, на фиг. 4 и, к, л - на тактовом входе и входах прямого и обратного счета счетчика 10 соответственно, на фиг. 4 м - на выходной знаковой шине 20.

Устройство работает следующим образом.

Пусть оба контролируемых объекта перемещаются в прямом направлении. При этом с выходов датчиков 1 и 2 перемещения информация в виде циклических кодов Грея поступает на входы блоков 3 и 4 преоб5 разования соответственно. В преобразователях определяются направотения перемещения объектов и формируются импульсы, количество которых прямо пропорционально перемещениям первого и второго объектов. Причем при перемещении первого и второго

0 объектов в прямом направлении импульсы появляются на первых выходах, а при перемещении в обратном - на вторых выходах блоков 3 и 4. Далее импульсы поступают на входы соответствующих блоков 5-8 памяти. При этом могут быть три вариан5 та временного сдвига импульсов на выходах блоков i и 2 друг относительно друга: задний фронт импульса на выходе блока 1 опережает задний фронт импульса на выходе

блока 2; задний фронт импульса на выходе блока 1 отстает от заднего фронта импульса на выходе блока 2; задний фронт импульса на выходе блока 1 совпадает с задним фронтом импульса на выходе блока 2.

Пусть импульсы поступают с первых выходов блоков 3 и 4. При первом варианте первым запоминает пришедший импульс блок 5 памяти, а затем блок 7. На первом выходе блока 5 памяти появляется сигнал «1, а на втором выходе - сигнал «О, который блокирует появление «1 на первых выходах блоков 6, 7 и 8 памяти. На вторых выходах блоков 6-8 памяти сохраняется «1. Таким образом, «1 появляется только на первом выходе блока 5, поступая на первый вход блока 9 управления и первый вход элемента ИЛИ 14. С выхода элемента ИЛИ 14 «1 передается на вход элемента И 13, разрешая прохождение импульса от генератора 15 на триггер 12. Импульс генератора переключает триггер 12, и на его выходе устанавливается «1. Следуюш,ий импульс генератора проходит через элемент И 11 на тактовый вход реверсивного счетчика 10 и на входы блоков 5-8 памяти. К этому моменту времени на первом выходе блока 9 управления сформирован сигнал «1, кото- рый поступает на вход прямого счета счетчика 10. Таким образом, по окончании импульса на выходе элемента И 11 содержимое счетчика 10 изменяется на + . триггер 12 возвращается в исходное состояние, тем самым запрещая дальнейшее прохождение импульсов генератора 15 через элемент И II, блок 6 памяти возвращается в исходное сосояние. Импульс генератора действует селективно на блоки памяти. Он возвращает в исходное состояние только тот блок памяти, на пря.мо.м выходе которого присутствует «I. Как только на втором выходе блока 5 памяти появляется «1, т. е. снимается блокировка блока 7 памяти, на первом выходе блока 7 появляется «1, а на втором - «О, блокируя появление «1 на первых выходах блоков 5, 6 и 8. Далее «1 проходит через элемент ИЛИ 14 на элемент И 13, разрешая прохождение импульса генератора 15 на счетный вход триггера 12. На выходе триггера 12 вновь устанавливается «I, разрешая прохождение следующе- го импульса генератора через элемент И 11. К этому моменту времени «1 на выходе блока 7 вызывает появление «1 на втором выходе блока 9 управления, переводя тем самым счетчик в режим «Вычитание. Теперь импульс, пропгедшнй на тактовый вход счетчика 10, вызывает изменение содержимого счетчика 10 на - I.

При втором варианте устройство работает аналогично, с той лишь разницей, что сначала обслуживается блок 7 памяти, а затем блок 5.

При третьем варианте «I может появиться или на первом выходе блока 5, или

5

0 5 0 5

5

0

0

на первом выходе блока 7 в зависимости от того, в каком блоке памяти временная задержка больше. Независимо от этого оба блока памяти будут обслужены, а в результат счета не будет внесена оп1ибка. Частота следования импульсов генератора выбирается большей Г„- 3, где Гц - максимальная из двух частот следования импульсов на выходе преобразователей 3 и 4.

Знак разности формируется на выходе 20 блока 9 управления следующим образом. Если на выходе реверсивного счетчика И) присутствует нулевой код, то на выходе элемента ИЛИ-НЕ 19 появляется «1. В этом случае появление «1 на выходе 20 соответствует знаку «-(-. Появление «1 на первом выходе блока 6 или 7 вызывает появление «О на выходе 20, что соответствует знаку «-.

При перемещении об ьектов в об)атиом направлении устройство работает аналогично, но при этом в работе находятся б/юки 6 и 8 памяти.

В случае, если абсолютная величина разности последовательностей имнульсов достигает максимального значения, заданного задатчиком 17, срабатывает реле 18, которое своими контактами отключает приводы обоих объектов (не показаны).

Блок памяти (фиг. 2) работает следую- щи.м образо.м. Импульс, поступая на первый вход, проходит через элемент или 21 на вход триггера 25. Триггер переключается, и на его выходе устанавливается «1, вызывая при наличии «1 на втором, третьем и четвертом входах появление «О на выходе элемента И 22 и «1 на выходе инвертора 23. Прохождение и.мпульса при этих условиях через второй вход э;1емен- та И 22 возвран 1ает триггер 25 и весь блок памяти в исходное состояние.

Таким образом, в предлагаемом устройстве обеспечивается возможность определения разности как несинхронных, так и синхронных последовательностей импу. 1ьсов. Кроме того, определяется знак разности последовательностей импульсов и меняется направление счета с помощью блока 9 управления, что имеет важное значение при использовании данного устройства в системах управления синхронным перемещением обт.ек- тов. В таких системах а.чгебраическая разность перемещений дгзух объектов используется для воздействия на один из об ьектов с целью сделать его перемещение синхронным со вторым. Двум импульсам, одновременно поступаюп1им на входы соответствующих блоков памяти, соответствуют два импульса, последовательно поступающие на вход реверсивного счетчика. Следовательно, в работе счетчика не происходят сбои, что обеспечивает высокую надежность устройства.

Формула изобретения Устройство счета разности двух последовательностей импульсов, содержащее первый и второй датчики перемещений, элемент ИЛИ, первый элемент И, реверсивный счетчик, блок сравнения, выход которого соединен с входом реле, задатчик максимальной разности и триггер, отличающееся тем, что, с целью расщирения функциональных возможностей при одновременном повышении функциональной надежности, в него введены первый и второй блоки преобразования, первый, второй, третий и четвертый блоки памяти, второй элемент И, блок управления, элемент ИЛИ-НЕ и генератор импульсов, причем выходы первого и второго датчиков перемещений соединены с входами соответственно первого и второго блоков преобразования, первые выходы которых соединены с первыми входами соответственно первого и третьего блоков памяти, а вторые выходы - соответственно с первыми входами второго и четвертого блоков памяти, первые входы первого, второго, третьего и четвертого блоков памяти соединены соответственно с первым, вторым, третьим и четвертым входами элемента ИЛИ и первым, вторым, третьим и четвертым входами блока управления, первый и второй входы которого соединены соответственно с входами прямого и обратного счета реверсивного счетчика, тактовый вход которого соединен с входами . первого, второго, третьего и четвертого блоков памяти и выходом первого элемента И, первый вход которого соединен с выходом триггера, счетный вход которого соединен с выходом второго элемента И, первый вход которого соединен с первым входом первого

0 элемента И и выходом генератора импульсов, а второй - с выходом элемента ИЛИ, причем вторые входы первого, второго, третьего и четвертого блоков памяти соединены с третьими входами соответственно третьего, четвертого, первого и второго блоков памяти и четвертыми входами соответственно четвертого, третьего, второго и первого блоков памяти, выходы разрядов реверсивного счетчика соединены с соответствующими входами элемента ИЛИ - НЕ и соответствую0 щими разрядами первого входа блока сравнения, второй вход которого соединен с выходом задатчика максимальной разности, причем выход элемента ИЛИ - НЕ соединен с тактовым входом блока управления,третий выход которого соединен со знаковой

5

выходной шиной.

,5(6,7,в)

fpuz. 2

фus.J

-lf- лгшБппЖдщЙ

г J 5 5 7 Is 9 /г1 и: У W 5j Is;

jqjiDJHjnjiiiunjnnilMili

I I I I Ij i

4„С11ЙCtLJTLDULL.

, 21li . M

,.flii

f

hhf t -sT

ВНИИПИ

Заказ 1402/54

Тираж 902

Подписное

Производственно-полиграфическое прсдчриятие, г. Ужгород, у,п. Пэоектиан, 4

Тираж 902

Подписное

риятие, г. Ужгород, у,п. Пэоектиан,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления параметров нелинейных колебательных систем | 1985 |

|

SU1302243A1 |

| Устройство для определения разностидВуХ п-РАзРядНыХ чиСЕл | 1979 |

|

SU824208A1 |

| Измеритель линейных перемещений | 1986 |

|

SU1401273A1 |

| Устройство для счета количества изображений объекта | 1987 |

|

SU1494021A1 |

| Программно-временное устройство | 1981 |

|

SU960737A1 |

| Устройство для измерения и регулирования соотношения скоростей | 1985 |

|

SU1364993A1 |

| Устройство для моделирования процесса передачи информации | 1989 |

|

SU1777149A1 |

| Емкостно-электронный преобразователь перемещения | 1989 |

|

SU1721434A1 |

| Генератор псевдослучайных последовательностей | 1987 |

|

SU1443141A1 |

| Устройство задержки последовательности импульсов с цифровым управлением | 1985 |

|

SU1285576A1 |

Изобретение касается автоматизации технологических процессов и может быть использовано для контроля разности углового, а также линейного перемещения двух объектов. Целью изобретения является расширение функциональных возможностей при одновременном повышении функциональной надежности. Устройство содержит датчики- I, 2 перемещения, элемент ИЛИ 14, элемент И 11, реверсивный счетчик 10, блок 16 сравнения, реле 18, задатчик 17 максимальной разности, триггер 12. Для достижения цели в устройство введены блоки 3, 4, преобразования, блоки 5, 6, 7, 8 памяти, элемент И 13, блок 9 управления, элемент ИЛИ-НЕ 19, генератор 15 импульсов, образованы новые функциональные связи. В устройстве обеспечена возможность определения разности как несинхронных последовательностей импульсов, так и синхронных. Кроме того, определяется знак разности последовательностей импульсов и меняется направление счета с помощью блока 9 управления, что имеет важное значение при использовании данного устройства в системах управления синхронным перемещением объектов. 4 ил. о фуг. Г

| Устройство для определения разности частот следования двух серий импульсов | 1983 |

|

SU1157675A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Гладильная подушка | 1955 |

|

SU104953A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-04-30—Публикация

1985-05-06—Подача