Изобретение относится к специализированным средствам вычислительной техники.

Цель изобретения - расширение функциональных возможностей устройства за счет моделирования процесса непрерывной передачи команд Б командных радиолиниях с информационной обратной связью.

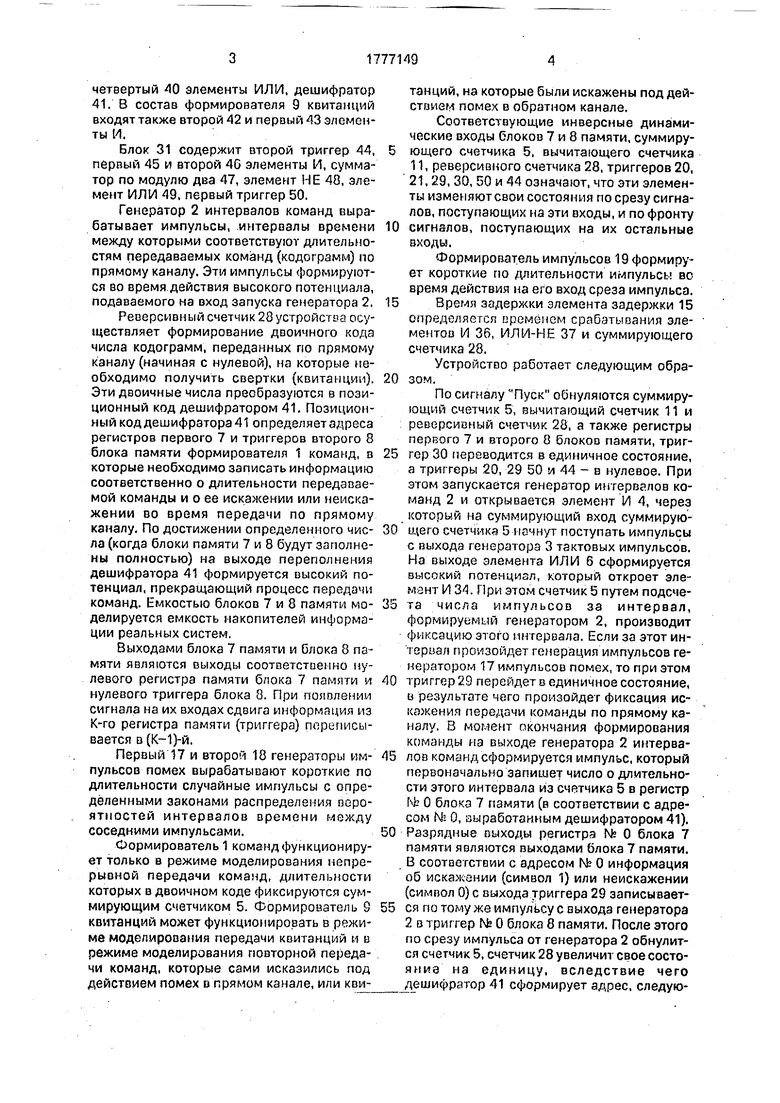

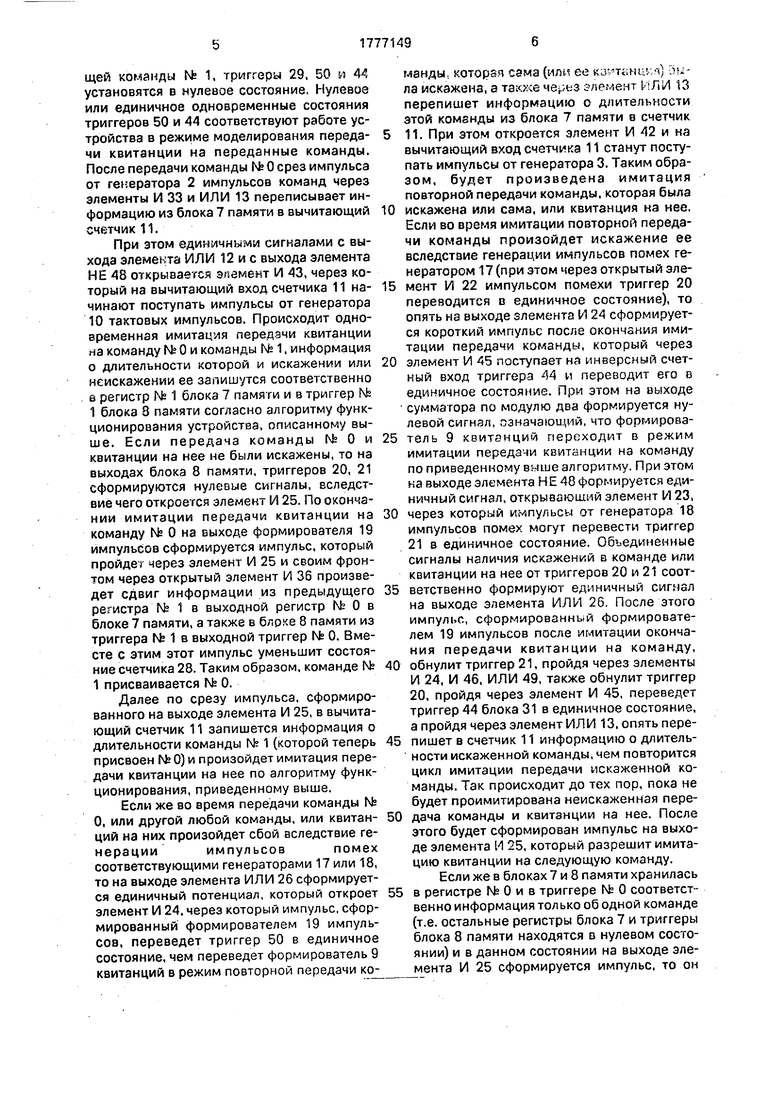

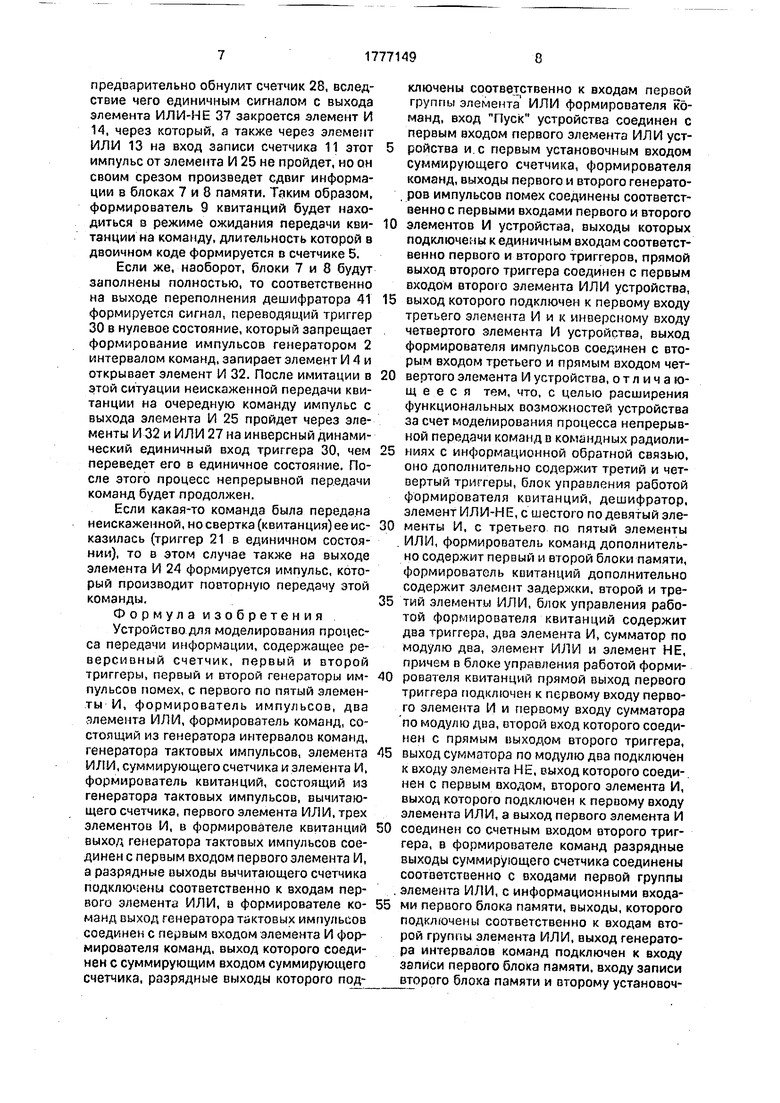

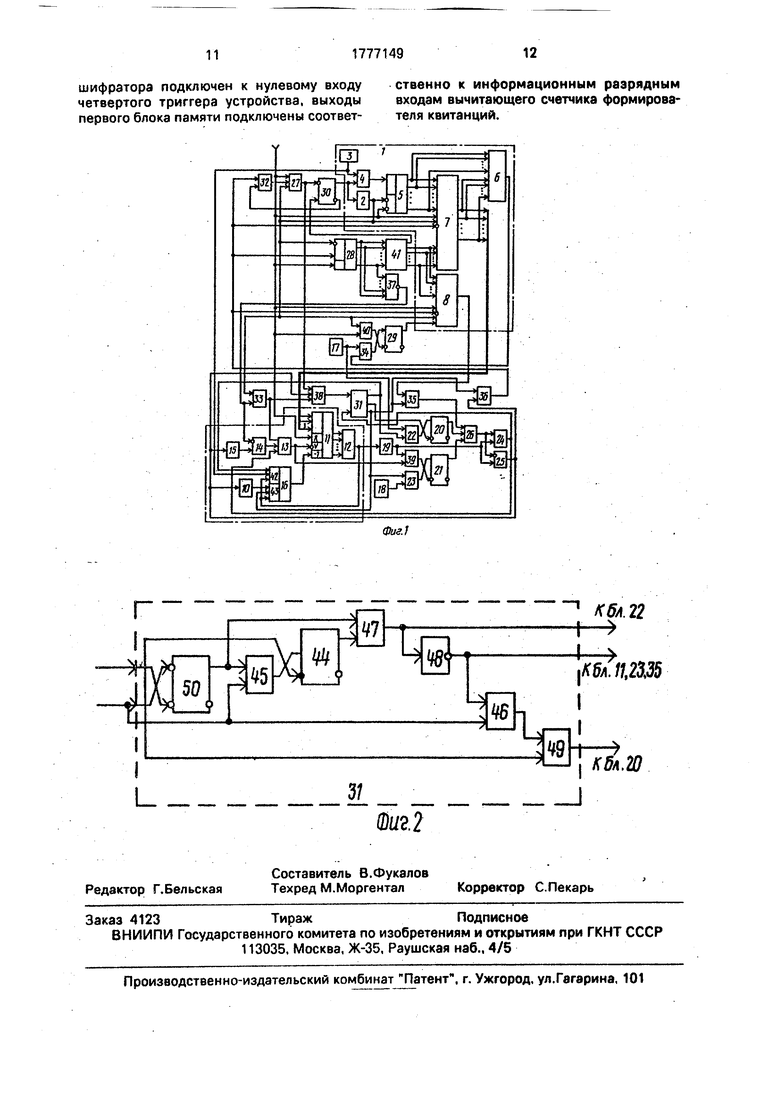

На фиг. 1 приведена функциональная схема устройства для моделирования процесса передачи информации; на фиг. 2 - функциональная схема блока управления работой формирователя квитанций.

Устройство содержит формирователь 1 команд, состоящий из генератора 2 интервалов команд, генератора 3 тактовых импульсов, элемента И 4. суммирующего

счетчика 5, элемента ИЛИ 6, первого 7 л второго 8 блоков памяти, формирователь 9 квитанций, состоящий из генератора 10 тактовых импульсов, вычитающего счетчика 11, первого 12, третьего 13 элементов ИЛИ, третьего элемента И 14, элемента 15 задержки, второго элемента ИЛИ 16, первый 17 и второй 18 генераторы импульсов помех, формирователь 19 импульсов, третий 20 и второй 21 триггеры, восьмой 22, второй 23, третий 24, четвертый 25 элементы И, второй 26 и первый 27 элементы ИЛИ. реверсивный счетчик 28, первый 29 и четвертый 30 триггеры, блок 31 управления работой формирователя квитанций, шестой 32, седьмой 33, первый 34, пятый 35 и девятый 36 элементы И, элемент ИЛИ-НЕ 37, пятый 38, третий 39,

XJ

х|

ч

«i

четвертый 40 элементы ИЛИ, дешифратор 41. В состав формирователя 9 квитанций входят также второй 42 и первый 43 элементы И.

Блок 31 содержит второй триггер 44, первый 45 и второй 40 элементы И, сумматор по модулю два 47, элемент НЕ 48, элемент ИЛИ 49, первый триггер 50.

Генератор 2 интервалов команд вырабатывает импульсы, интервалы времени между которыми соответствуют длительностям передаваемых команд (кодограмм) по прямому каналу. Эти импульсы формируются во время действия высокого потенциала, подаваемого на вход запуска генератора 2.

Реверсивный счетчик 28 устройства осуществляет формирование двоичного кода числа кодограмм, переданных по прямому каналу (начиная с нулевой), на которые необходимо получить свертки (квитанции). Эти двоичные числа преобразуются в позиционный код дешифратором 41. Позиционный код дешифратора 41 определяет адреса регистров первого 7 и триггеров второго 8 блока памяти формирователя 1 команд, в которые необходимо записать информацию соответственно о длительности передаваемой команды и о ее искажении или неискажении во время передачи по прямому каналу. По достижении определенного чис- ла (когда блоки памяти 7 и 8 будут заполнены полностью) на выходе переполнения дешифратора 41 формируется высокий потенциал, прекращавший процесс передачи команд. Емкостью блоков 7 и 8 памяти мо- делируется емкость накопителей информации реальных систем.

Выходами блока 7 памяти и блока 8 памяти являются выходы соответственно нулевого регистра памяти блока 7 памяти и нулевого триггера блока 8. При появлении сигнала на их входах сдвига информация из К-го регистра памяти (триггера) переписывается в(К-1)-й.

Первый 17 и второй 18 генераторы им- пульсов помех вырабатывают короткие по длительности случайные импульсы с определенными законами распределения вероятностей интервалов времени между соседними импульсами.

Формирователь 1 команд функционирует только в режиме моделирования непрерывной передачи команд, длительности которых в двоичном коде фиксируются суммирующим счетчиком 5. Формирователь 9 квитанций может функционировать в режиме моделирования передачи квитанций и в режиме моделирования повторной передачи команд, которые сами исказились под действием помех в прямом канале, или квитанций, на которые были искажены под действием помех в обратном канале.

Соответствующие инверсные динамические входы блоков 7 и 8 памяти, суммирующего счетчика 5, вычитающего счетчика 11, реверсивного счетчика 28, триггеров 20, 21,29, 30, 50 и 44 означают, что эти элементы изменяют свои состояния по срезу сигналов, поступающих на эти входы, и по фронту сигналов, поступающих на их остальные входы.

Формирователь импульсов 19 формирует короткие по длительности импульсы вс время действия на его вход среза импульса.

Время задержки элемента задержки 15 определяется цременсм срабатывания элементов I/I 36, ИЛИ-НЕ 37 и суммирующего счетчика 28.

Устройство работает следующим образом.

По сигналу Пуск обнуляются суммирующий счетчик 5, вычитающий счетчик 11 и реверсивный счетчик 28, а также регистры первого 7 и второго 8 блоков памяти, триггер 30 переводится в единичное состояние, а триггеры 20, 29 50 и 44 в нулевое. При этом запускается генератор интервалов команд 2 и открывается элемент И 4, через который на суммирующий вход суммирующего счетчика 5 начнут поступать импульсы с выхода генератора 3 тактовых импульсов. На выходе элемента ИЛИ б сформируется высокий потенциал, который откроет элемент И 34. При этом счетчик 5 путем подсчета числа импульсов за интервал, формируемый генератором 2, производит фиксацию этого интервала. Если за этот интервал произойдет генерация импульсов генератором 17 импульсов помех, то при этом

1риггер 29 перейдет в единичное состояние, ь результате чего произойдет фиксация ис коженич передачи команды по прямому каналу, в момент окончания формирования команды на выходе генератора 2 интервалов команд сформируется импульс, который первоначально запишет число о длительности этого интервала из считчика 5 в регистр № 0 блока 7 памяти (в соответствии с адресом N: 0, аиработзнным дешифратором 41). Разрядные пыходы регистра № 0 блока 7 памяти являются выходами блока 7 памяти. В соответствии с адресом № 0 информация об искажении (символ 1) или неискажении (символ 0) с выхода триггера 29 записывается по тому же импульсу с выхода генератора

2в триггер Мз 0 блока 8 памяти. После этого по срезу импульса от генератора 2 обнулит- ся счетчик 5, счетчик 28 увеличит свое состо- яние на единицу, вследствие чего дешифратор 41 сформирует адрес, следующей команды № 1, триггеры 29, 50 н 44 установятся в нулевое состояние. Нулевое или единичное одновременные состояния триггеров 50 и 44 соответствуют работе устройства в режиме моделирования передачи квитанции на переданные команды. После передачи команды № 0 срез импульса от генератора 2 импульсов команд через элементы И 33 и ИЛИ 13 переписывает информацию из блока 7 памяти в вычитающий счетчик 11.

При этом единичными сигналами с выхода элемента ИЛИ 12 и с выхода элемента НЕ 48 открывается элемент И 43, через который на вычитающий вход счетчика 11 начинают поступать импульсы от генератора 10 тактовых импульсов. Происходит одновременная имитацмя передачи квитанции на команду NJ 0 и команды № 1, информация

0длительности которой и искажении или неискажении ее запишутся соответственно а регистр N21 блока 7 памяти и в триггер №

1блока 8 памяти согласно алгоритму функционирования устройства, описанному выше. Если передача команды № 0 и квитанции на нее не были искажены, то на выходах блока 8 памяти, триггеров 20, 21 Сформируются нулевые сигналы, вследствие чего откроется элемент И 25. По окончании имитации передачи квитанции на команду № 0 на выходе формирователя 19 импульсов сформируется импульс, который пройдет через элемент И 25 и своим фронтом через открытый элемент И 36 произведет сдвиг информации из предыдущего регистра № 1 в выходной регистр № 0 в блоке 7 памяти, а также в блрке 8 памяти из триггера № 1 в выходной триггер № 0. Вместе С этим этот импульс уменьшит состояние счетчика 28. Таким образом, команде № 1 присваивается № 0.

Далее по срезу импульса, сформированного на выходе элемента И 25, в вычитающий счетчик 11 запишется информация о длительности команды № 1 (которой теперь присвоен № 0) и произойдет имитация передачи квитанции на нее по алгоритму функционирования, приведенному выше.

Если же во время передачи команды № О, или другой любой команды, или квитанций на них произойдет сбой вследствие генерацииимпульсовпомехсоответствующими генераторами 17 или 18, то на выходе элемента ИЛИ 26 сформируется единичный потенциал, который откроет элемент И 24, через который импульс, сформированный формирователем 19 импульсов, переведет триггер 50 в единичное состояние, чем переведет формирователь 9 квитанций в режим повторной передачи команды, которая сама (или ее .ЬА) . ла искажена, а таюке элемент ИЛИ 13 перепишет информацию о длительности этой команды из блока 7 памяти в счетчик

11. При этом откроется элемент И 42 и на вычитающий вход счетчика 11 станут поступать импульсы от генератора 3. Таким образом, будет произведена имитация повторной передачи команды, которая была

0 искажена или сама, или квитанция на нее. Если во время имитации повторной передачи команды произойдет искажение ее вследствие генерации импульсов помех генератором 17 (при этом через открытый эле5 мент И 22 импульсом помехи триггер 20 переводится в единичное состояние), то опять на выходе элемента И 24 сформируется короткий импульс после окончания имитации передачи команды, который через

0 элемент И 45 поступает на инверсный счетный вход триггера 44 и переводит его в единичное состояние. При этом на выходе сумматора по модулю два формируется нулевой сигнал, означающий, что формирова5 тель 9 квитанций переходит в режим имитации передачи квитанции на команду по приведенному выше алгоритму. При этом ка выходе элемента НЕ 48 формируется единичный сигнал, открывающий элемент И 23,

0 через который импульсы от генератора 18 импульсов помех могуг перевести триггер 21 в единичное состояние. Объединенные сигналы наличия искажений в команде или квитанции на нее от триггеров 20 и 21 соот5 ветственно формируют единичный сигнал на выходе элемента ИЛИ 26. После этого импульс, сформированный формирователем 19 импульсов после имитации окончания передачи квитанции на команду,

0 обнулит триггер 21, пройдя через элементы И 24, И 46, ИЛИ 49, также обнулит триггер 20, пройдя через элемент И 45, переведет триггер 44 блока 31 в единичное состояние, а пройдя через элемент ИЛИ 13, опять пере5 пишет в счетчик 11 информацию о длительности искаженной команды, чем повторится цикл имитации передачи искаженной команды. Так происходит до тех пор, пока не будет проимитирована неискаженная пере0 дача команды и квитанции на нее. После этого будет сформирован импульс на выходе элемента И 25, который разрешит имитацию квитанции на следующую команду. Если же в блоках 7 и 8 памяти хранилась

5 в регистре № 0 и в триггере № 0 соответственно информация только об одной команде (т.е. остальные регистры блока 7 и триггеры блока 8 памяти находятся в нулевом состоянии) и в данном состоянии на выходе элемента И 25 сформируется импульс, то он

предварительно обнулит счетчик 28, вследствие чего единичным сигналом с выхода элемента ИЛИ-НЕ 37 закроется элемент И 14, через который, а также через элемент ИЛИ 13 на вход записи счетчика 11 этот импульс от элемента И 25 не пройдет, но он своим срезом произведет сдвиг информации в блоках 7 и 8 памяти. Таким образом, формирователь 9 квитанций будет находиться 0 режиме ожидания передачи квитанции на команду, длительность которой в двоичном коле формируется в счетчике 5.

Если же, наоборот, блоки 7 и 8 будут заполнены полностью, то соответственно на выходе переполнения дешифратора 41 формируется сигнал, переводящий триггер 30 в нулевое состояние, который запрещает формирование импульсов генератором 2 интервалом команд, запирает элемент И 4 и открывает элемент И 32. После имитации в этой ситуации неискаженной передачи квитанции на очередную команду импульс с выхода элемента И 25 пройдет через элементы И 32 и ИЛИ 27 на инверсный динамический единичный вход триггера 30, чем переведет его в единичное состояние. После этого процесс непрерывной передачи команд будет продолжен.

Если какая-то команда была передана неискаженной, но свертка (квитанция) ее исказилась (триггер 21 в единичном состоянии), то в этом случае также на выходе элемента И 24 формируется импульс, который производит повторную передачу этой команды.

Формула изобретения

Устройство для моделирования процесса передачи информации, содержащее реверсивный счетчик, первый и второй триггеры, первый и второй генераторы импульсов помех, с первого по пятый элементы И, формирователь импульсов, два элемента ИЛИ, формирователь команд, со- столщий из генератора интервалов команд, генератора тактовых импульсов, элемента ИЛИ, суммирующего счетчика и элемента И, формирователь квитанций, состоящий из генератора тактовых импульсов, вычитающего счетчика, первого элемента ИЛИ, трех элементов И, в формирователе квитанций выход генератора тактовых импульсов соединен с первым входом первого элемента И, а разрядные выходы вычитающего счетчика подключены соответственно к входам первого элемента ИЛИ, а формирователе команд выход генератора тактовых импульсов соединен с первым входом элемента И формирователя команд, выход которого соединен с суммирующим входом суммирующего счетчика, разрядные выходы которого подключены соответственно к входам первой группы элемента ИЛИ формирователя команд, вход Пуск устройства соединен с первым входом первого элемента ИЛИ устройства и с первым установочным входом суммирующего счетчика, формирователя команд, выходы первого и второго генераторов импульсов помех соединены соответственное первыми входами первого и второго

0 элементов И устройства, выходы которых подключены к единичным входам соответственно первого и второго триггеров, прямой выход второго триггера соединен с первым входом второго элемента ИЛИ устройства,

5 выход которого подключен к первому входу третьего элемента И и к инверсному входу четвертого элемента И устройства, выход формирователя импульсов соединен с вторым входом третьего и прямым входом чет0 вертого элемента И устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет моделирования процесса непрерывной передачи команд в командных радиоли5 ниях с информационной обратной связью, оно дополнительно содержит третий и четвертый триггеры, блок управления работой формирователя квитанций, дешифратор, элемент ИЛ И-Н Е, с шестого по девятый эле0 менты И, с третьего по пятый элементы . ИЛИ, формирователь команд дополнительно содержит первый и второй блоки памяти, формирователь квитанций дополнительно содержит элемент задержки, второй и тре5 тий элементы ИЛИ, блок управления работой формирователя квитанций содержит два триггера, два элемента И, сумматор по модулю два, элемент ИЛИ и элемент НЕ, причем в блоке управления работой форми0 рователя квитанций прямой выход первого триггера подключен к первому входу первого элемента И и первому входу сумматора по модулю два, второй вход которого соединен с прямым выходом второго триггера,

5 выход сумматора по модулю два подключен к входу элемента НЕ, выход которого соединен с первым входом, второго элемента И, выход которого подключен к первому входу элемента ИЛИ, а выход первого элемента И

0 соединен со счетным входом второго триггера, в формирователе команд разрядные выходы суммирующего счетчика соединены соответственно с входами первой группы . элемента ИЛИ, с информационными входа5 ми первого блока памяти, выходы, которого подключены соответственно к входам второй группы элемента ИЛИ, выход генератора интервалов команд подключен к входу записи первого блока памяти, входу записи второго блока памяти и второму установочному входу суммирующего счетчика, входы обнуления первого и второго блоков памяти объединены и соединены с входом Пуск устройства, в формирователе квитанций выходы первого и второго элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого подключен к вычитающему входу вычитающего счетчика, инверсный дифференциальный вход записи которого подключен к выходу третьего элемента ИЛИ формирователя квитанций и первому входу третьего элемента ИЛИ устройства, выход которого подключен к инверсному дифференциальному нулевому входу второго триггера устройства, выход элемента задержки формирователя квитанций подключен к прямому входу третьего элемента И формирователя квитанций, выход которого соединен с первым входом третьего элемента ИЛИ формирователя квитанций, установочный вход вычитающего счетчика которого, установочный вход реверсивного счетчика устройства и первый вход четвертого элемента ИЛИ устройства объединены и подключены к входу Пуск устройства, выход четвертого элемента ИЛИ устройства соединен с инверсным динамическим нулевым входом первого триггера устройства, прямой выход которого подключен к информационному входу второго блока памяти формирователя команд, выход которого соединен с первым входом пятого элемента И устройства, выход которого подключен к второму входу второго элемента ИЛИ устройства, третий вход которого соединен с прямым выходом третьего триггера устройства, инверсный динамический нулевой вход которого соединен с выходом элемента ИЛИ блока управления работой формирователя квитанций, инверсные динамические нулевые входы первого и второго триггеров и второй вход элемента ИЛИ которого объединены и подключены к выходу пятого элемента ИЛИ устройства, первый вход которого и инверсный динамический единичный вход четвертого триггера устройства подключены к выходу первого элемента ИЛИ устройства, второй вход которого соединен с выходом шестого элемента И устройства, первый вход которого подключен к инверсному выходу четвертого триггера, прямой выход которого соединен с вторым входом элемента И и входом запуска генератора интервалов команд формирователя команд, выход генератора интервалов команд соединен с суммирующим входом реверсивного счетчика устройства, с вторым входом четвертого элемента ИЛИ устройства и с первым входом седьмого элемента И

устройства, выход которого подключен к второму входу пятого элемента ИЛИ устройства и к второму входу третьего элемента ИЛИ формирователя квитанций, третий

вход которого соединен с выходом третьего элемента И устройства, вторым входом второго элемента И и инверсным динамическим единичным входом первого триггера блока управления работой формирователя

0 квитанций, выход сумматора по модулю два которого подключен к первому входу второго элемента И формирователя квитанций и к первому входу восьмого элемента И устройства, выход которого соединен с единич5 ным входом третьего триггера устройства, а

второй вход восьмого элемента И устройст ва соединен с выходом первого генератора

импульсов помех, выход элемента НЕ блока

управления работой формирователя квитан0 ций соединен с вторым входом второго элемента И устройства, вторым входом первого элемента И формирователя квитанций, вторым входом пятого и первым входом девятого элементов И устройства, выход

5 которого подключен к второму входу шестого элемента И устройства, входам управления считыванием информации первого и второго блоков памяти и к вычитающему входу реверсивного счетчика устройства,

0 разрядные выходы которого подключены соответственно к входам дешифратора и входам элемента ИЛИ-НЕ, выход которого соединен с вторым входом седьмого элемента И устройства и инверсным входом

5 третьего элемента И формирователя квитанций, второй вход второго элемента И которого подключен к выходу генератора тактовых импульсов, формирователя команд, выход генератора интервалов команд

0 которого соединен с третьим входом первого элемента ИЛИ устройства, а выход элемента ИЛИ формирователя команд подключен к второму входу первого элемента И устройства, выход первого элемента

5 ИЛИ формирователя квитанций подключен к третьим входам первого и второго элементов И формирователя квитанций и к входу формирователя импульсов, выход которого соединен с вторым входом третьего элемен0 та ИЛИ устройства, выход четвертого элемента И устройства подключен к второму входу девятого элемента И устройства, входу останова генератора тактовых импульсов формирователя квитанций, к входу элемен5 та задержки формирователя квитанций и к третьему входу пятого элемента ИЛИ устройства, К выходов дешифратора соединены соответственно с адресными входами первого и второго блоков памяти (где К - число адресных входов), а (К+1)-й выход дешифратора подключен к нулевому входу ственно к информационным разрядным четвертого триггера устройства, выходы входам вычитающего счетчика формирова- первого блока памяти подключены соответ- теля квитанций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования процесса передачи информации | 1989 |

|

SU1765829A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2020574C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2047901C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2047902C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2047900C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМ ПЕРЕДАЧИ ДАННЫХ | 1991 |

|

RU2011219C1 |

| Устройство для обмена информацией | 1982 |

|

SU1084776A1 |

| Цифровое устройство для автоматического управления движением шахтной подъемной машины | 1978 |

|

SU765173A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2115165C1 |

Изобретение относится к специализированным средствам вычислительной техники и предназначено для моделирования процесса передачи информации. Цель изобретения - расширение функциональных возможностей устройства за счет моделирования процесса непрерывной передачи команд в командных радиолиниях с информационной обратной связью. Цель изобретения достигается введением в формирователь команд первого и второго блоков памяти, в формирователь квитанций - элементов ИЛИ, элемента задержки, а также в устройство - триггеров, блока управления работой формирователя квитанций, элементов И, элемента ИЛИ-НЕ, элементов ИЛИ и дешифратора. Сущность изобретения состоит в придании устройству возможности моделирования непрерывной передачи по прямому каналу на приемную сторону сигналов команд, имитируемых интервалами времени определенной длительности, с повторной передачей тех команд, квитанции на которые были приняты по обратному каналу с искажениями, возникающими из-за помех, действующих в прямом и обратном каналах. 2 ил. (Л С

| Авторское свидетельство СССР Ms 1688699,кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1616378, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-11-23—Публикация

1989-02-22—Подача