Изобретение относится к электроизмерительной технике и предназначено для измерения величины сдвига фаз двух синусоидальных сигналов.

Цель изобретения - повышение точности измерения фазового сдвига.

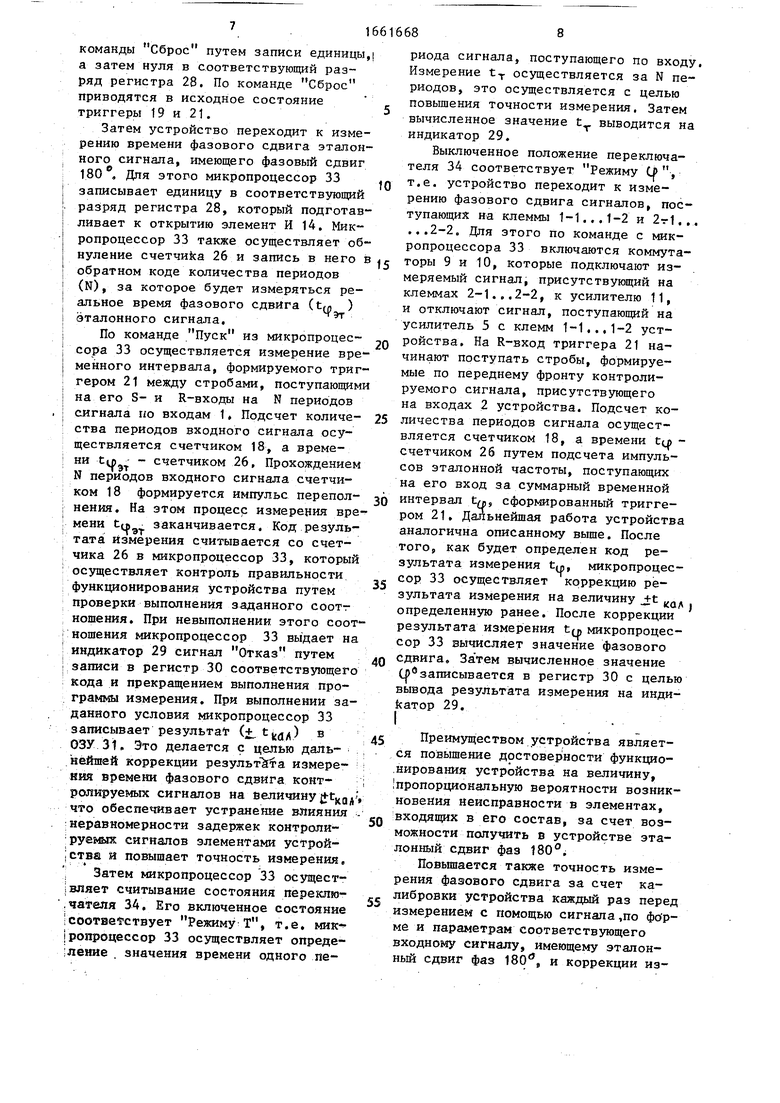

На фиг.1 представлена функциональная схема устройства на фиг.2 - схема блока управления.

Устройство (фиг. 1) содержит входные клеммы 1т1...1-2, 2т1... уст- ройства, коммутаторы 3 и 4, первый усилитель 5, формирователь 6 импульсов, элемент НЕ 7, элемент И 8, коммутаторы 9 и 10, второй усилитель 11 формирователь 12 импульсов, элемент НЕ 13, элементы И 14 и 15, триггер 16, элемент И 17, счетчик 18 импульсов, триггер 19, элемент ИЛИ 20, триггер 21, элемент И 22, блок 23 управления, генератор 24 импульсов, элемент И 25, счетчик 26 импульсов, ключ 27 электронный.

Блок 23 управления (фиг. 2) содержит регистр 28, индикатор 29, регист 30, оперативное запоминающее устрой- ство (ОЗУ) 31, постоянное запоминающее устройство (ПЗУ) 32, микропроцессор 33, переключатель 34, элемент И 35, дешифратор 36, шину адреса (ША) 37, шину управления (ШУ) 38, шину данных на запись () 9, шину данных на считывание () 40.

Клемма 1-2 соединена с первым входом коммутатора 3, управляющий вход которого подключен к первому уп- равляющему выходу блока 23, а выход к инверсному входу усилителя 5 и к второму входу коммутатора 10, первый вход которого соединен с клеммой 2-1 управляющий вход - к второму управляющему выходу блока 23, а выход к прямому входу усилителя 11, инверсный вход которого подключен к выходу коммутатора 9, первый вход кото

0

5

рого соединен с клеммой 2-2, второй вход - с выходом коммутатора 4, а управляющий вход - с вторым управляющим входом блока 23, Первый вход второго коммутатора 4 соединен с клеммой 1-1, управляющий вход - с первым управляющим выходом блока 23, а выход - с первым входом усилителя 5, выход которого подключен к первому входу формирователя 6, второй вход которого соединен с корпусом устройства, а выход - с вторым входом элемента И 8, через элемент НЕ 7 с первым входом элемента И 8 и с вторым входом элемента И 15. Выход элемента И 8 подключен к второму входу элемента И 17 и к входу триггера 21, Выход усилителя 11 подключен к первому входу формирователя 12, второй вход которого соединен с корпусом устройства, а выход - с вторым входом элемента И 14, а через элемент НЕ 13 с первым входом элемента И 14, выход которого подключен к входу триггера 21. Третий управляющий выход блока 23 соединен с третьим входом элемента И 14 и с первым входом элемента И 15, выход которого подключен к S-входу триггера 16, выход которого соединен с первым входом элемента И 17 и с С-входом триггера 21, выход которого подключен к второму входу элемента И 25, первый вход которого соединен с выходом генератора 24, а выход - с информационным входом счетчика 26, адресный вход которого подключен к восьмому управляющему выходу блока 23, управляю - щий вход - через ШУ 38 соединен с блоком 23, информационный вход - через ШД 5аг 39 с блоком 23, а выходы подключены к информационным входам ключа 27, управляющий вход - к седьмому управляющему выходу блока 23, а выход - через П1ДС4ИТ 40 соединен с

5

блоком 23, четвертый управляющий выход которого подключен к первому входу элемента ИЛИ 20 и к R-входу триггера 19, выход которого соединен с третьим входом элемента И 22, с вторым входом элемента ИЛИ 20 и с R-вхо дом триггера 21, установочный R-вход которого подключен к выходу элемента ИЛИ 20. Выход первого триггера 16 по ключей к С-входу триггера 21 и к первому входу элемента И 17, выход которого соединен с информационным входо счетчика 18, адресный вход которого подключен к пятому управляющему выходу блока 23, управляющий вход - чере ШУ 38 к блоку 23, информационный вход - через ШЦсцит 40 к блоку 23, а выход - к S-входу триггера 19. Шестой управляющий выход блока 23 под- ключей к первому входу элемента И 22 третий вход которого соединен через ШУ 38 с блоком 23, а выход - через ШДл„и,. 40 с блоком 23.

счит

Устройство работает следующим образом.

При включении питания осуществляется пуск микропроцессора 33 в блоке 23, который начинает выполнение программы измерения, записанной в ПЗУ 32. Вначале осуществляется проверка работоспособности устройства. Микропроцессор 33 выдает команду Сброс, которая обеспечивает перевод всех элементов устройства в исходное состояние.

После этого микропроцессор 33 включает коммутатор 3 и 4, сигнал с клемм 1-1...1-2 поступает в устройство. Устройство после этого реализует цикл измерения фазового сдвига между двумя синусоидальными сигналами, присутствующими на клеммах 1г-1.. ...1-2 и 2т1...2-2. Сигнал с клемм 1-1... Н2 поступает на входы усилителя 5 и через коммутаторы 9 и 10 поступает на входы усилителя 11, который инвертирует этот сигнал. Сигналы с выходов усилителей 5 и 11 поступают на входы формирователей 6 и 12 соответственно. Они обеспечивают сравнение напряжения выходных сигналов с общим напряжением питания устройства по каждому-входу. На выходах формирователей 6 и 12 формируется последовательность прямоугольных импульсов с периодом повторения, равным периоду следования

0

1668

5

20

6

входного сигнала. Эти импульсы поступают на входы формирователей стро- бов, состоящих из элементов НЕ 7, И 8 и НЕ 13, И 14. С выхода элемента И 8 | по переднему фронту сигнала поступает последовательность стробирующих импульсов на вход элемента И 17 и на S-вход триггера 21. Затем по команде из микропроцессэра 33 осуществляется обнуление счетчика 26 путем. записи нулевого кода и кода, инверсного коду количества периодов измерения сигнала по первым входам.

После этого микропроцессор 33 блока 23 управления выдает команду Пуск, которая через регистр 28 поступает на вход элемента И 15, а затем при наличии отрицательной полуволны сигнала по входам поступает на S-вход триггера 16. Он переходит в единичное состояние. Сигнал, снимаемый с его выхода, разрешает прохождение стробов через элемент И 17

25 на вход счетчика 18 и поступает на Свход триггера 21.

По команде Пуск осуществляется измерение длительности N периодов сигнала. Подсчет количества периодов

30 входного сигнала осуществляется счетчиком 18, Фиксация прохождения N периодов сигнала осуществляется счетчиком 26 путем подсчета импульсов эталонной частоты, поступающих на его вход от генератора 24 за временной интервал, сформированный триггером 21.

По прохождении N периодов входного сигнала счетчиком 18 формирует40 ся импульс переполнения, поступающий на S-вход триггера 19. Сигнал, пос- тупаюший с его выхода, в этом случае, устанавливает в исходное состояние триггеры 16 и 21. Триггер 21 за45 прещает прохождение импульсов от

генератора 24 на счетчик 26. На этом измерение времени прохождения N периодов сигнала прекращается.

Одновременно микропроцессор 33 в

0 блоке 23 управления осуществляет считывание через элемент И 22 состояние триггера 19. При его единичном состоянии, что соответствует команде Конец измерения, микропроцессор 33 осуществляет считывание кода результата измерения со счетчика 26 и запись его в ОЗУ 31, снятие команды Пуск путем записи нуля в соответствующий разряд регистра 28 и выдачу

35

5

команды Сброс путем записи единицы,| а затем нуля в соответствующий разряд регистра 28. По команде Сброс приводятся в исходное состояние триггеры 19 и 21.

Затем устройство переходит к измерению времени фазового сдвига эталонного сигнала, имеющего фазовый сдвиг 180е, Для этого микропроцессор 33 записывает единицу в соответствующий разряд регистра 28, который подготавливает к открытию элемент И 14. Микропроцессор 33 также осуществляет обВыключенное положение переключателя 34 соответствует Режиму CJ, т.е. устройство переходит к измерению фазового сдвига сигналов, поступающих на клеммы 1-1...1-2 и 2т1. ...2-2. Для этого по команде с микропроцессора 33 включаются коммутануление счетчика 26 и запись в него в торы 9 и 10, которые подключают изобратном коде количества периодов (N), за которое будет измеряться реальное время фазового сдвига (tqj ) эталонного сигнала.

По команде Пуск из микропроцессора 33 осуществляется измерение временного интервала, формируемого триггером 21 между стробами, поступающими на его S- и R-входы на N периодов сигнала по входам 1, Подсчет количества периодов входного сигнала осуществляется счетчиком 18, а времени t|« - счетчиком 26, Прохождением N периодов входного сигнала счетчиком 18 формируется импульс переполнения. На этом процесс измерения времени Се заканчивается. Код резуль т эт

тата измерения считывается со счетчика 26 в микропроцессор 33, который осуществляет контроль правильности функционирования устройства путем проверки выполнения заданного соотношения. При невыполнении этого соотношения микропроцессор 33 выдает на индикатор 29 сигнал Отказ путем записи в регистр 30 соответствующего кода и прекращением выполнения программы измерения. При выполнении заданного условия микропроцессор 33 записывает результат (+, t) в ОЗУ 31. Это делается с целью дальнейшей коррекции результата измерения времени фазового сдвига конт- , ролируемых сигналов на величину ЈtKQA , что обеспечивает устранение влияния . неравномерности задержек контролируемых сигналов элементами устрой- ства и повышает точность измерения.

Затем микропроцессор 33 осущест- , вляет считывание состояния переключателя 34. Его включенное состояние соответствует Режиму Т, т.е. мик- |ропроцессор 33 осуществляет определение значения времени одного пе20

25

30

35

40

45

50

55

меряемый сигнал, присутствующий на клеммах 2-1...2-2, к усилителю 11, и отключают сигнал, поступающий на усилитель 5 с клемм 1-1..,1-2 устройства. На R-вход триггера 21 начинают поступать стробы, формируемые по переднему фронту контролируемого сигнала, присутствующего на входах 2 устройства. Подсчет количества периодов сигнала осуществляется счетчиком 18, а времени tq - счетчиком 26 путем подсчета импульсов эталонной частоты, поступающих на его вход за суммарный временной интервал ty, сформированный триггером 21. Дальнейшая работа устройства аналогична описанному выше. После того, как будет определен код результата измерения tqj, микропроцессор 33 осуществляет коррекцию результата измерения на величину j-t Ka/ определенную ранее. После коррекции результата измерения tg, микропроцессор 33 вычисляет значение фазового сдвига. Затем вычисленное значение (1 взаписывается в регистр 30 с целью вывода результата измерения на индикатор 29. I

Преимуществом устройства является повышение достоверности функционирования устройства на величину, пропорциональную вероятности возникновения неисправности в элементах, входящих в его состав, за счет возможности получить в устройстве эталонный сдвиг фаз 180°.

Повышается также точность измерения фазового сдвига за счет калибровки устройства каждый раз перед измерением с помощью сигнала ,по фо р- ме и параметрам соответствующего входному сигналу, имеющему эталонный сдвиг фаз 180е,, и коррекции из

риода сигнала, поступающего по входу. Измерение tT осуществляется за N периодов, это осуществляется с целью повышения точности измерения. Затем вычисленное значение tr выводится на индикатор 29.

Выключенное положение переключателя 34 соответствует Режиму CJ, т.е. устройство переходит к измерению фазового сдвига сигналов, поступающих на клеммы 1-1...1-2 и 2т1... ...2-2. Для этого по команде с микропроцессора 33 включаются коммутаторы 9 и 10, которые подключают из0

5

0

5

0

5

0

5

меряемый сигнал, присутствующий на клеммах 2-1...2-2, к усилителю 11, и отключают сигнал, поступающий на усилитель 5 с клемм 1-1..,1-2 устройства. На R-вход триггера 21 начинают поступать стробы, формируемые по переднему фронту контролируемого сигнала, присутствующего на входах 2 устройства. Подсчет количества периодов сигнала осуществляется счетчиком 18, а времени tq - счетчиком 26 путем подсчета импульсов эталонной частоты, поступающих на его вход за суммарный временной интервал ty, сформированный триггером 21. Дальнейшая работа устройства аналогична описанному выше. После того, как будет определен код результата измерения tqj, микропроцессор 33 осуществляет коррекцию результата измерения на величину j-t Ka/v определенную ранее. После коррекции результата измерения tg, микропроцессор 33 вычисляет значение фазового сдвига. Затем вычисленное значение (1 взаписывается в регистр 30 с целью вывода результата измерения на индикатор 29. I

Преимуществом устройства является повышение достоверности функционирования устройства на величину, пропорциональную вероятности возникновения неисправности в элементах, входящих в его состав, за счет возможности получить в устройстве эталонный сдвиг фаз 180°.

Повышается также точность измерения фазового сдвига за счет калибровки устройства каждый раз перед измерением с помощью сигнала ,по фо р- ме и параметрам соответствующего входному сигналу, имеющему эталонный сдвиг фаз 180е,, и коррекции измерения времени на величину калибровки.

41

Формула изобретенияУстройство для измерения фазового сдвига, содержащее блок управления, две входные клеммы, первый коммутатор, первый и второй формирователи импульсов, первый и второй элементы И, первый счетчик импульсов и генератор импульсов, причем первая входная клемма устройства соединена с первым входом первого коммутатора, ,выход генератора импульсов соединен с первым входом второго элемента И, выход которого подключен к информационному входу первого счетчика импульсов, выход первого формирователя импульсов подключен к второму входу первого элемента И, первый управляющий выход блока управления соединен с управляющим входом первого коммутатора, отличающееся тем что, с целью повышения точности измерения фазового сдвига, устройство дополнительно содержит три коммутатора два усилителя, первый и второй элементы НЕ, четыре элемента И, элемент ИЛИ, электронный ключ, второй счетчи импульсов, три триггера, причем первый управляющий выход блока управления соединен с управляющим входом коммутатора, второй управляющий выход - с управляющими входами третьего и четвертого коммутаторов, третий управляющий вход - с первым входом четвертого элемента И и с третьим входом третьего элемента И, четверты управляющий выход - с первым входом элемента ИЛИ и с R-входом второго триггера, пятый управляющий выход - с адресным входом второго счетчика импульсов, шестой управляющий выход с первым входом шестого элемента И седьмой управляющий выход - с управляющим входом электронного ключа, восьмой управляющий выход - с адресным входом первого счетчика импуль - сов, девятый выход - через шину упраления с управляющим входом первого и второго счетчиков импульсов и с вторым входом шестого элемента И, деся-

0 5 о ,. ,-

5

0

тый выход - через шину данных на зге пись с информационными входами первого и второго счетчиков импульсов, а вход - через шину данных на считывание с выходами электронного ключа и выходом шестого элемента И, выходы первого и второго коммутаторов соединены с входами первого усилителя и с вторыми входами соответственно четвертого и третьего коммутаторов, выходы которых подключены к входам второго усилителя, | выходы первого и второго усилителей подключены к первым входам соответственно первого и второго формирователей импульсов, выход первого формирователя импульсов подключен к входу первого элемента НЕ, выход которого соединен с первым входом первого элемента И и с вторым входом четвертого элемента И, выход второго формирователя импульсов подключен к входу второго элемента НЕ и к второму входу третьего элемента И, к первому входу которого подключен выход второго элемента И, выход четвертого элемента И соединен с S-входом первого триггера, прямой выход которого подключен к С входу третьего триггера и к первому входу пятого элемента И, выход первого элемента И соединен с вторым входом пятого элемента И и с S-входом третьего триггера, к R-входу которого подключен выход третьего элемента И, прямой выход третьего триггера соединен с вторым входом второго элемента И, выход пятого элемента И под- ключей к информационному входу второго счетчика импульсов, выход которого соединен с S-входом второго триггера, прямой выход которого соединен с третьим входом шестого элемента И, с вторым входом элемента ИЛИ и с R-входом первого триггера , информационные выходы первого счетчика импульсов подключены к входам электронного ключа, второй, третий и четвертый входы устройства соединены соответственно с информационными входами второго, третьего и четвертого коммутаторов, а выход элемента ИЛИ соединен с R-входом третьего триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля средств числового программного управления | 1988 |

|

SU1675852A1 |

| Устройство для контроля сопротивления | 1988 |

|

SU1651231A1 |

| Фазометр | 1985 |

|

SU1298685A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1992 |

|

RU2050552C1 |

| Устройство для измерения сдвига фаз в четырехполюснике | 1989 |

|

SU1675799A1 |

| Устройство для контроля параметров | 1989 |

|

SU1735871A1 |

| Цифровой фазометр | 1982 |

|

SU1114976A1 |

| Фазометр | 1985 |

|

SU1273837A1 |

| Устройство для контроля сдвига фаз двух сигналов | 1989 |

|

SU1716522A1 |

| Устройство измерения напряжения химического источника тока | 1983 |

|

SU1096719A1 |

Изобретение относится к электроизмерительной технике и предназначено для измерения величины сдвига фаз двух синусоидальных сигналов. Цель изобретения - повышение точности измерения фазового сдвига. Устройство содержит входные клеммы 1 - 1, 1 - 2, 2 - 1, 2 - 2, коммутатор 3, формирователи 6, 12 импульсов, элементы И 14, 15 счетчик 18 импульсов, блок 23 управления и генератор 24 импульсов. Введение в известное устройство коммутаторов 4, 9, 10, усилителей 5, 11, элементов НЕ 7, 13, триггеров 16, 19, 21, элементы ИЛИ 20, элементов И 22, 25, счетчика 26 и электронного ключа 27 позволяет за счет калибровки устройства каждый раз перед измерением, с помощью сигнала, по форме и параметрам соответствующего входному сигналу, имеющему эталонный сдвиг фаз 180°, и коррекции измерения времени на величину калибровки повысить точность измерения фазового сдвига. 2 ил.

Фиг.2

| Кончаловский В.Ю | |||

| Цифровые измерительные устройства | |||

| - М.: Энер- гоатомиздат, 1985, с | |||

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

Авторы

Даты

1991-07-07—Публикация

1988-07-05—Подача