1

(21)433523А/21-24

(22)27„11„87

(46) 15.12.90. Бюло № 46 (72) АоАо Плавильщиков (53) 621.317(088.8)

(56)Авторское свидетельство СССР №1308927, кл. G 01 R 23/16, 1984,

(54) СПЕКТРАЛЬНЫЙ АНАЛИЗАТОР

(57)Изобретение относится к измерительной технике, в частности к измерению характеристик случайных сигналов. Целью изобретения является повьппение точности анализа. Анализатор содержит входной усилитель

1,аналого-цифровой преобразователь

2,гщфровые фильтры 3j|-3f, буферные регистры 4,. „.4,„и f .int ЦИФРО- вой пиковый детектор 5, индикатор

6, цифровой коммутатор 7, логарифмический преобразователь 8, блок 9 извлечения квадратного корня, цифровой коммутатор 10, блок 11 детектирования, оперативное запоминающее устройство 12, дешифратор 13, блок 14 приоритетньк прерываний . и блок 15 управления, j з.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Третьоктавный спектральный анализатор | 1985 |

|

SU1308927A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Анализатор спектра | 1977 |

|

SU669295A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Устройство для предварительной обработки электроразведочных сигналов | 1986 |

|

SU1539708A1 |

| Ультразвуковой терапевтический аппарат | 1989 |

|

SU1717106A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

Изобретение относится к измерительной технике, в частности к измерению характеристик случайных сигналов. Целью изобретения является повышение точности анализа. Анализатор содержит входной усилитель 1, аналого-цифровой преобразователь 2, цифровые фильтры 31...3N, буферные регистры 411...41N и 421...42N, цифровой пиковый детектор 5, индикатор 6, цифровой коммутатор 7, логарифмический преобразователь 8, блок 9 извлечения квадратного корня, цифровой коммутатор 10, блок 11 детектирования, оперативное запоминающее устройство 12, дешифратор 13, блок 14 приоритетных прерываний и блок 15 управления. 2 з.п.ф-лы, 2 ил.

(Л

О5

( О5 СО

д 28 7 «S 6 15

II 3 Ji П в

1 11Г I 1ТТ

Шиг.1

i

Изобретение относится к измерительной технике, в частности к измерению характеристик случайных сигналов,,

Цель изобретения - повышение точности анализа.

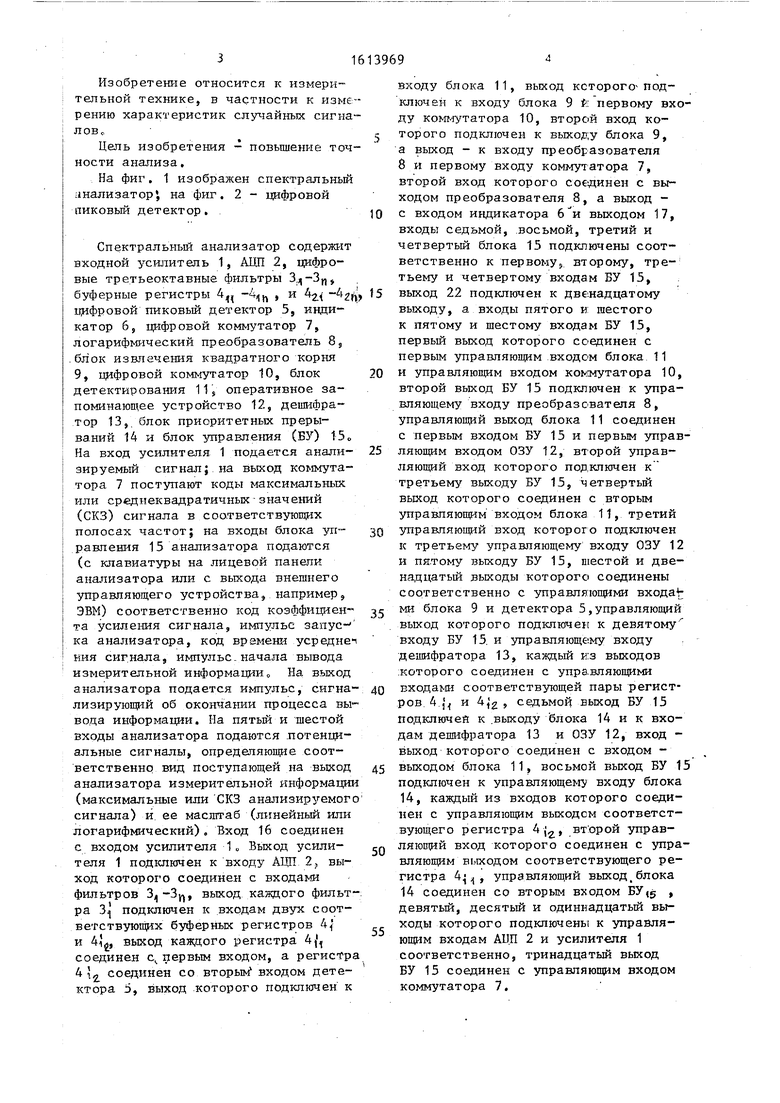

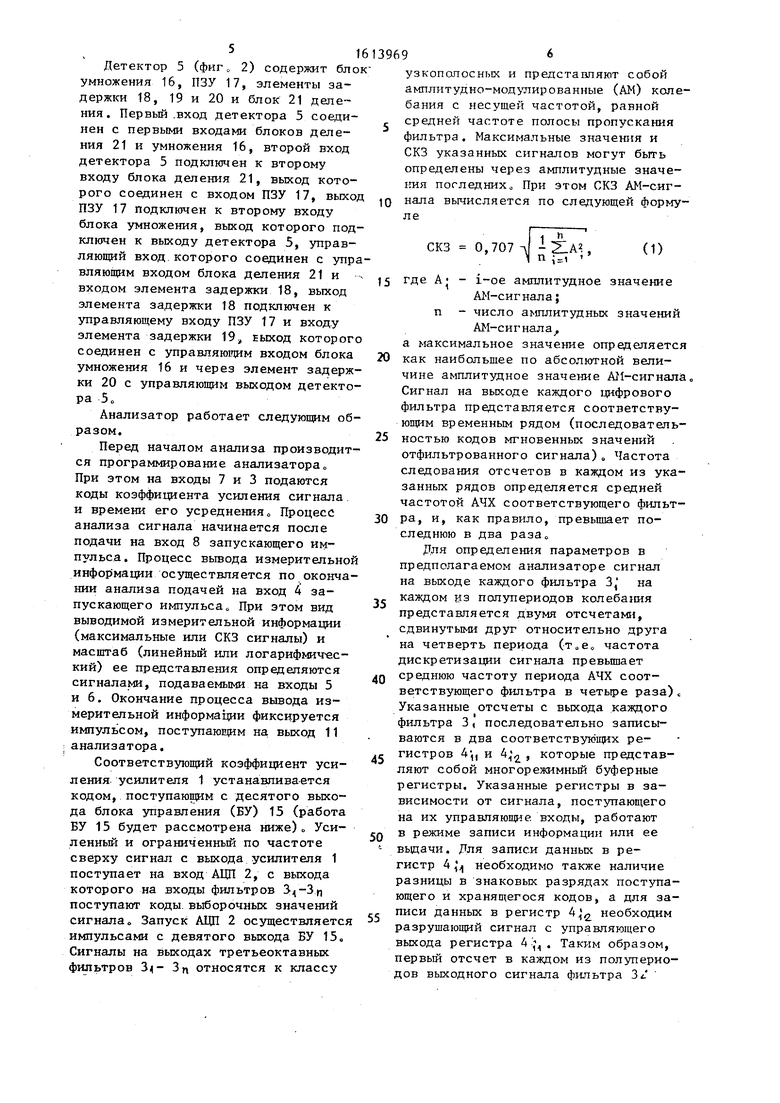

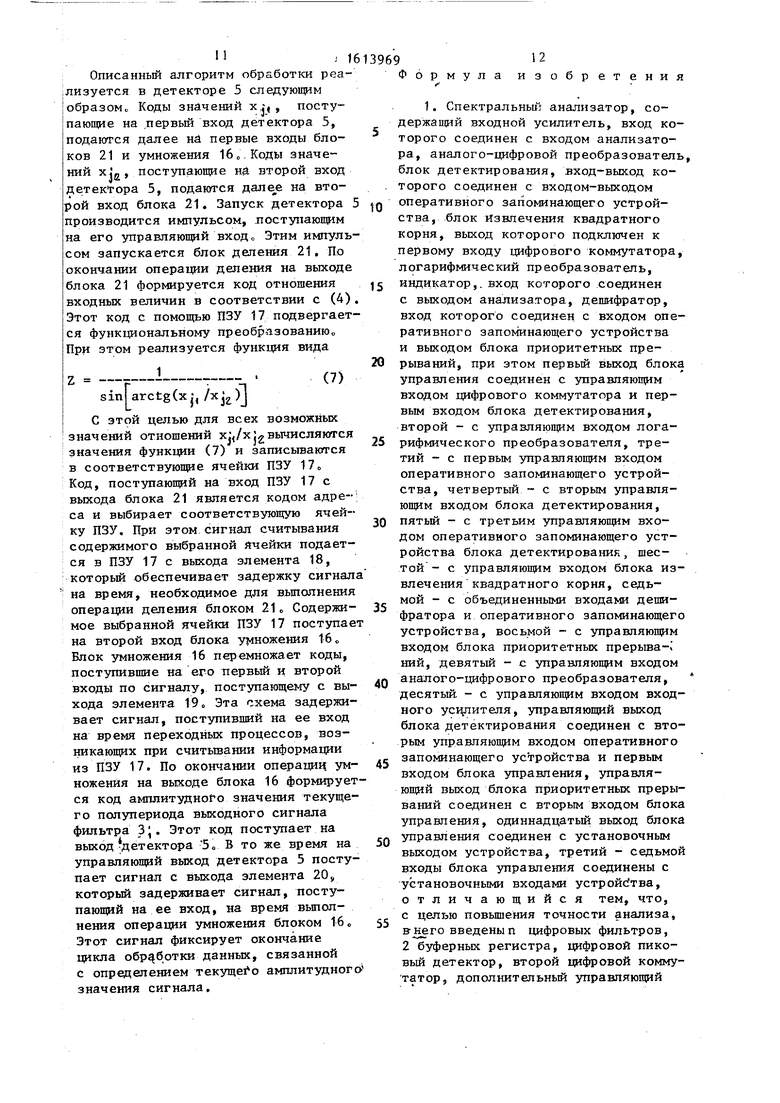

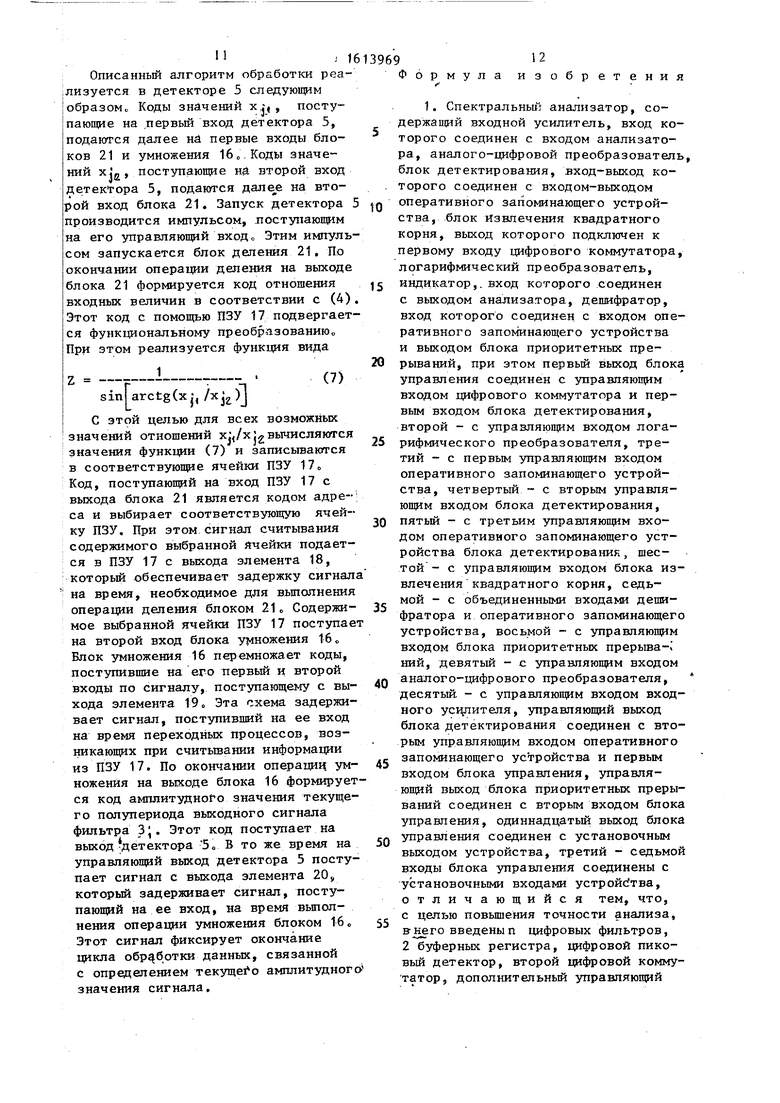

На фиг, 1 изображен снектральньй анализатор, на фиг, 2 - цифровой пиковый детектор,

Снектральный анализатор содержит входной усилитель 1, АЦП 2, дафро- вые третьеоктавные фильтры 3,j|-3| j буферные регистры 4, и Aj. 5 1ЩФРОВОЙ пиковьш детектор 5, индикатор 6, цифровой кoм ryтaтop 7, логарифмический нреобразователь 8, блок извлечения квадратного корня 9, цифровой коммутатор 10, блок20

детектирования 11s оперативное запоминающее устройство 12, дешифратор 13,, блок приоритетных прерываний 14 и блок управлеьшя (БУ) 15 На вход усилителя 1 подается анали- 25 зируемый сигнал; на выход коммутатора 7 поступают коды максимальных или среднеквадратичных - значений (СКВ) сигнала в соо.тветствую1Щ-1х полосах частот; на входы блока уп- зО .равления 15 анализатора подаются (с клавиатуры на лицевой панели анализатора или с выхода внешнего управляющего устройства, например, ЭВМ) соответственно код коэффициен 35 та усиления сигнала, импульс запус- ка анализатора, код времени усреднеч НИН сиг,нала, импульс начала вывода измерительной информации На выход анализатора подается импульс, сигна- 40 лизируюпщй об окончании процесса вы- во,да информации. На пятьш и шестой входы анализатора подаются .потенциальные сигналы, определяющие соответственно вид поступающей на выход 45 анализатора измерительной информации (максимальные или СКВ анализнрз емаго сигнала) и, ее масштаб (линейный или логарифмический). Вход 16 соединен с входом усилителя 1„ Выход усили- Q теля 1 подключен к входу АЦП, 2, выход которого соединен с входами фильтров , выход каждого фильт-. ра 3J подключен к входам двух соот- ветствующх буферных регистров 4 и 4i, выход каждого регистра 4,, соединен саперным входом, а регистра 4 2 соединен со вторым входом детектора 5, выход которого подключен к

входу блока 11, выход которого под- ключей к входу блока 9 Р. первому входу KOMi i TaTopa 10, второй вход которого подключен к выходу блока 9, а выход - к входу преобразователя 8 и первому входу коммутатора 7, второй вход которого соединен с выходом преобразователя 8, а выход - с входом и щикатора выходом 17, входы седьмой, восьмой, третий и четвертьй блока 15 подключены соответственно к первомур второму, третьему и четвертому входам БУ 15, выход 22 подключен к двенадцатому выходу, а входы пятого и: шестого к пятому и шестому входам БУ 15, первьй выход которого соединен с первым управляющим входом блока 11 и управляющим входом кокмутатора 10, второй выход БУ 15 подключен к управляющему входу преобразователя 8, управляющий выход блока 11 соединен с первым входом БУ 15 и первым управляющим входом ОЗУ 12, второй управляющий вход которого подключен к третьему выходу БУ 15, четвертый выход которого соединен с вторым управляюш;им входом блока 11, третий управляющий вход которого подключен к третьему управляющему входу ОЗУ 12 и пятому вьтходу БУ 15, шестой и две- надцатьш выходы которого соединены соответственно с управляющими входа ми блока 9 и детектора 5,управляющий выход которого подключен к девятому входу БУ 15, и управляюще;му входу дешифратора 13, каждьш и:з выходов ;которого соединен с упра.вляющими входами соответствующей пары регистров 4 j и 5 седьмой выход БУ 15 подключей к ,вькоду блока 14 и к входам дешифратора 13 и ОЗУ 12, вход - выход которого соединен с входом - выходом блока 11, восьмой выход БУ 1 подключен к управляющему входу блока 14, каждый из входов которого соединен с управляюш 1м выходом соответствующего регистра 4 j вт орой управ- ляюпо й вход которого соединен с управляющим выходом соответствующего регистра ( , управляюш,ий выход, блока 14 соединен со вторым входом БУ,5 девятьй, десятый и одиннадцатый выходы которого подключены к управляющим входам АЦП 2 и усилителя 1 соответственно, тринадцатый выход БУ 15 соединен с управляющим входом коммутатора 7.

5,6

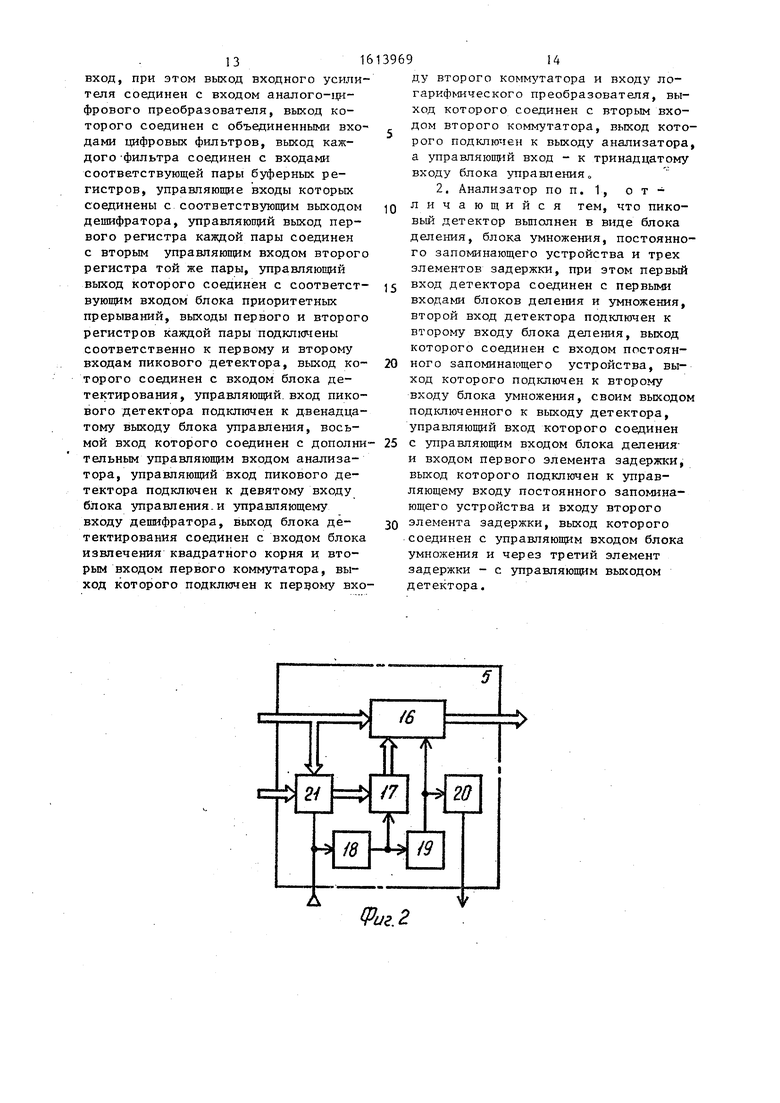

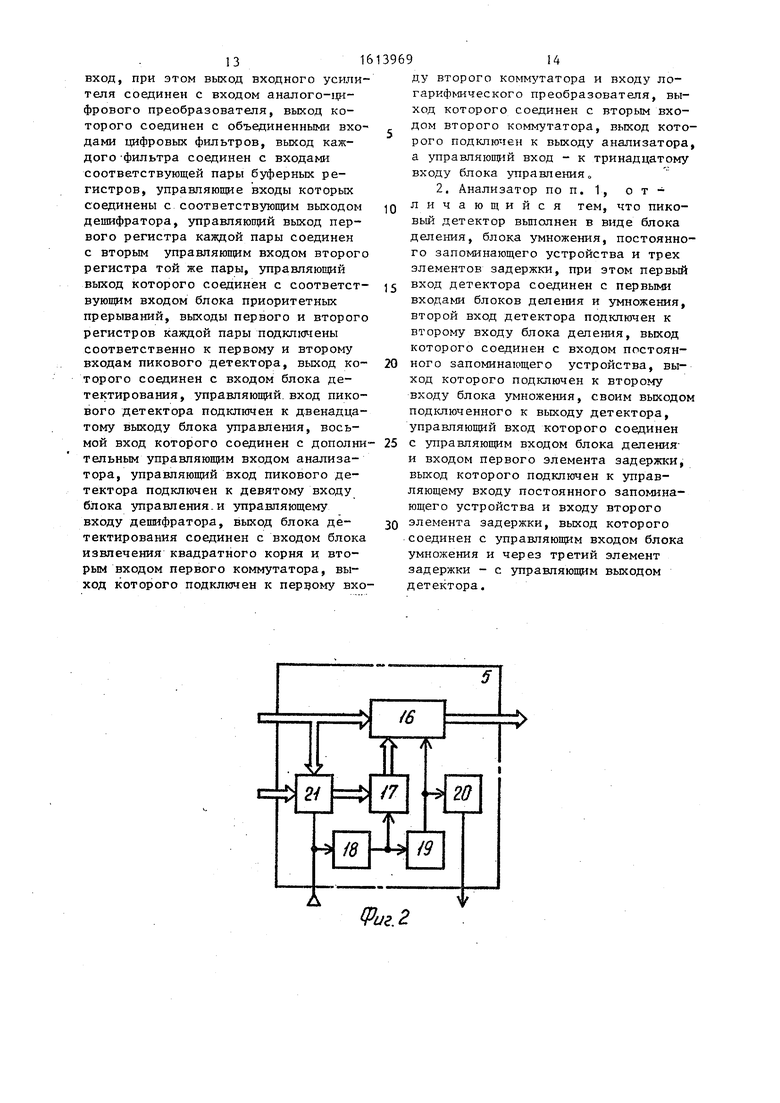

Детектор 5 (фиг 2) содержит блок умножения 16, ПЗУ 17, элементы задержки 18, 19 и 20 и блок 21 деления. Первый .вход детектора 5 соединен с первыми входами блоков деления 21 и умножения 16, второй вход детектора 5 подключен к второму входу блока деления 21, выход которого соединен с входом ПЗУ 17, выход ПЗУ 17 подключен к второму входу блока умножения, выход которого подключен к выходу детектора 5, управляющий вход которого соединен с управляющим входом блока деления 21 и . входом элемента задержки 18, выход элемента задержки 18 подключен к управляющему входу ПЗУ 17 и входу элемента задержки 19, ЕЫХОД которого соединен с управляющим входом блока умножения 16 и через элемент задержки 20 с управляющим выходом детектора 5о

Анализатор работает следующим образом.

Перед началом анализа производится программирование анализатора,, При этом на входы 7 и 3 подаются коды коэффициента усиления сигнала, и времени его усреднения о Процесс анализа сигнала начинается после подачи на вход 8 запускающего импульса. Процесс вьшода измерительной информации осуществляется по окончании анализа подачей на вход 4 запускающего импульса При этом вид выводимой измерительной информации (максимальные или СКЗ сигналы) и масштаб (линейный или логарифмический) ее представления определяются сигналами, подаваемыми на входы 5 и 6. Окончание процесса вывода измерительной информации фиксируется импульсом, поступающим на выход 11 анализатора.

Соответствующий коэффициент усиления усилителя 1 устанавлива-ется кодом, поступаюп1им с десятого выхода блока управления (БУ) 15 (работа БУ 15 будет рассмотрена ниже) Усиленный и ограниченный по частоте сверху сигнал с выхода усилителя 1 поступает на вход АЦП 2, с выхода которого на входы фильтров поступают коды, выборочных значений сигнала Запуск АЦП 2 осуществляется мпульсами с девятого выхода БУ 15, Сигналы на выходах третьеоктавных ильтров Зп относятся к классу

139696

узкополосных и представляют собой амплитудно-мод лированные (AM) колебания с несущей частотой, равной г средней частоте полосы пропускания фильтра. Максимальные значения и СКЗ указанных сигналов могут быть определены через амплитудные значения последних о При этом СКЗ АМ-сиг- 10 нала вычисляется по следующей формуле

СКЗ 0,707

щ.

(1)

15 где А- - i-oe амплитудное значение

АМ-сигнала; п - число амплитудных значений

АМ-сигнала а максимальное значение определяется

20 как наибольшее по абсолютной величине амплитудное значение AJI-сигнала, Сигнал на выходе каждого цифрового фильтра представляется соответству- Ю1ЦИМ временным рядом (последователь25 ностью кодов мгновенных значений отфильтрованного сигнала) „ Частота следования отсчетов в каждом из указанных рядов определяется средней частотой АЧХ соответствующего фильт-

30 ра, и, как правило, превышает последнюю в два раза

Для определения параметров в предполагаемом анализаторе сигнал на выходе каждого фильтра 3, на

каждом из полупериодов колебания представляется двумя отсчетами, сдвинутыми друг относительно друга на четверть периода (тое частота дискретизации сигнала превышает Q среднюю частоту периода АЧХ соответствующего фильтра в четыре раза) Указанные отсчеты с выхода каждого фильтра 3, последовательно записываются в два соответствующих ре- с гистров 4,, и . t которые представляют собой многорежимный буферные регистры. Указанные регистры в зависимости от сигнала, поступающего на их управляющие входы, работают Q в режиме записи информации или ее

- выдачи. Для записи данных в регистр 4, ;, необходимо также наличие разницы в знаковых разрядах поступающего и хранящегося кодов, а для за- j писи данных в регистр необходим разрушающий сигнал с управляющего выхода регистра 4, . Таким образом, первый отсчет в каждом из полуперио- дов выходного сигнала фильтра 3J

записывается в регистр 4, . После записи указанного кода в регистр 4-, на его управляющем выходе формируется сигнал запроса на прерывание, ко- торый в данном случае является разрешением на запись следующего кода в регистр А 2. После записи очередного кода в регистр 4,2. управляющем выходе последнего формируется д сигнал запроса на прерыва1ще, который в данном случае является запросом на обработку. Сигналы с управ- ЛЯЮП1ИХ выходов регистров .4п2. поступают каждый на соответствующий 5 вход блока 14 приоритетов. Основная функция блока 14 сводится к приему сигналов, поступающих с управляющих выходов регистров 4. П2 распознаванию и вьдаче управляющих сигна- 20 лов. Поскольку запросы на обработку вырабатываются независимо друг от друга, то для установления порядка их удовлетворения каждому из регистров 4 2 присваивается приоритет- 25 ньй номер, в соответствии с несущей частотой сигнала, отсчеты которого в него, записываются. Наивысший приоритет присваивается регистру, принимающему отсчеты сигнала с самойзО высокой несущей частотой. На выходе блока 14 формируется код обслуживаемого в данный момент канала, а на его управляющем вькоде - импульс сопровождения. Указанный код посту- пает на соответствующие входы ОЗУ 12, число ячеек которого равно числу фильтров анализатора, и дешифратора 13 и является по отношению к этим устройствам кодом адреса В зависи- Q мости от кода на входе дешифратора . 13 на одном из выходов последнего формируется сигнал, который переводит соответствующую пару регистров 4 j и 4 из режима приема р ре-, жим выдачи информации При этом выходные вентили этих регистров переводятся и з пассивного состояния высокого сопротивления в активное состояние и инфор мация, хранящаяся в этих регистрах, по двум соответствующим магистралям данных, поступает на первый и второй входы детектора 5« Запуск детектора 5 осуществляется импульсом, поступаюш 1м на его упрдв- ляюпщй вход с двенадцатого выхода БУ 15. Указанный импульс формируется при поступлегаи на второй вход БУ 15, импульса с управляющего выхода блока

50

55

0

5

14 о Детектор 5 по двум отсчетам, взятым в течение одного полупериода сигнала, вычисляет амплитудное значение этого полупериода,, По окончании процесса вычислений детектор 5 формирует на своем вькоде соответствующий код, а на управляющем выходе - импульс. Этот импульс поступает на девятый вход БУ 13 и ,на управляю- 1ЩЙ вход депшфратора 13, Разрешающий сигнал с соответствующего вькода дешифратора 13 снимается, а соответствующая пара регистров 4 и 4 режима вьиачи переводится в режим приема информации о При этом выходные вентили указанных регистров переводятся в режим высокого сопротивления и отключаются от соответствуюши х магистралей данных. В то же время, на пятом выходе БУ 15 формируется им- ульс, поступаюшдй на третий вход ОЗУ 12 и третий вход детектора 11. Этим импульсом производится считывание содержимого ячейки ОЗУ 12, определяемой кодом на входе последнего, и запись его в детектор 11с, В это же время производится запись в детектор 11 кода с выхода детектора 5о В детекторе 11 при наличии разрешающего сигнала, поступающего на его второй вход с четвертого выхода БУ 15, производится обработка поступивших данныхо В процессе обработки данных, поступаюш;их в детектор 11 с выхода детектора 5, определяется максимальное значение и текущее значение суммы квадратов отсчетов сигнала. После элементарного цикла обработки детектор 11 формирует на своем управляющем выходе импульс, который поступает на-первый вход БУ 15 и на первый вход ОЗУ 12о При этом результаты обработки из детектора 11 пере- . писываются в выбранную ранее ячейку ОЗУ 12 (первая группа разрядов в каждой ячейке ОЗУ отводится для кода максимального значения, вторая группа - для кода текущего значения суммы квадратов обработанных.значений и третья группа - для кода числа обработанных значений сигнала) Кроме того, на втором выходе БУ 15 формируется сигнал, разрешающий блоку 14 обслуживание очередной пары регистров.. Описанный процесс обработки продолжается до окончания заданного времени усреднения сигнала. Процесс вывода результатов анализа начина916

ется с подачи иа вход 4 анализатора и далее на четвертый вход БУ 15 импульсного сигнала. При этом на седьмом выходе БУ 15 формируется код адреса первой ячейки ОЗУ 12, а на пятом выходе - импульс о По этому импулсу происходит считывание содержимого первой ячейки ОЗУ 12 и запись его в детектор 11. При этом в зависимости от сигнала на первом управляющем входе детектора 11 на его выход подается код максимального значения или среднего значения квадрата. Если выводится максимальное значение, то в соответствии с управляющим сигналом коммутатор 10 пропускает на выход код, поступающий на его первый вход Если выводится СКЗ, то на выход коммутатора 10 проходит код, поступающий на его второй вход с выхода блока 9 . Блок 9 представляет собой ПЗУ, в ячейках которого записаны значения квадратного корня из кодов, поступающих на его вход, умноженные в соответствии с (1) на величину 0,707. При этом коды, поступающие на вход блока 9, являются кодами адреса его ячеек, а импульс поступающий на его управляющий вход - сигналом считывания содержимого выбранной ячейки Указанный импульс формируется на шестом выходе БУ 15 по окончании импульса на его пятом выходеk Таким образом, в зависимости от сигнал на управляющем входе коммутатора 10 на его выход будет поступать код СКЗ или максимальных значений. Указанный код поступает на вход логарифмического преобразователя 8 и на первый вход коммутатора 7. Преобразователь 8 представляет собой ПЗУ, в ячейках которого записаны значения логарифмов кодов, поступающих на его вход При этом коды, поступающие на вход преобразователя 8, являются кодами адреса его ячеек, а импульс, поступающий на его управляющий вход - сигналом считьтания содержимого выбранной ячейю. Указанны импульс формируется на втором выходе БУ 15 по окончании импульса на его шестом выходе. Б зависимости от сигнала на управляющем входе коммутатора 7 на его выход будет поступать код выбранного значения сигнала в линейном или логарифмическом масштабе Если используется линейный, масштаб ппедставления данных, то на выход

10

коммутатора 7 проходит код с его первого входа. Если используется логарифмический масштаб, то на выход коммутатора 7 проходит код, пост тгающий на его второй вход с выхода преобразователя В. С выхода коммутатора 7 код поступает на индикатор 6 и выход анализатора 17. На этом вьгоод содержимого

первой ячейки ОЗУ 12 заканчивается. Вьшод содержимого второй, третьей и т.До ячеек ОЗУ 12 осуществляется последовательно в соответствии с приведенным описанием. При этом на седьмом выходе БУ 15 каждый раз формируется код адреса соответствующей ячейки „

Детектор 5 (фиг. 2) работает следующим образом.

Данный блок вычисляет текущее амплитудные значения сигналов с выходов фильтров 3(,-3„. Каждый полупериод сигнала на выходе кавдого фильтра представляется двумя отсчетами, сдвинутыми друг относительно друга на четверть периода,, Указанные отсчеты представляются выражениями

30

ji wtj (j, (2)

7

i jmsi(wtj+ |) Xj.sin(o;; +

(3)

+ 5 -xj cosCe,

где х |И Xj2 - первый и второй отсче- ты j-ro папупериода

сигнала ; j М a mлитyднoe значение

j-ro полупериода; t j - момент выборки первого отсчета j-ro полупериода относительно начала послепнего„

Для вычисления (.2) или (3) -. необходимо определить величину . ля этого достаточно поделить (2) на U)

2i SiusiS j. t.,f.)

X.. x:..

Xj j,

Откуда Of arctg 2i

J-K.,

5iL .

(5)

x

Используя (2, и (5), получаем JM ГТ;Т г )

JM sinO(fT . Г , .xib Л isin arctg(---)

L)2. J

Таким образом, по двум отсчетам, используя (6), можно определить амплитудное значение j-ro полупериода.

11

1613969

Описанный алгоритм обработки реа- лизуется в детекторе 5 следующим |образомо Коды значений хj, посту- |паюшие на первый вход детектора 5, подаются далее на первые входы блоков 21 и умножения 16,,. Коды значений xjg, поступающие на второй вход детектора 5, подаются далее на второй вход блока 21. Запуск детектора 5 производится импульсом, .поступающим на его управляющий вход Этим импульсом запускается блок деления 21, По окончании операции деления на выходе блока 21 формируется код отношения входных величин в соответствии с (4). Этот код с помощью ПЗУ 17 подвергается функциональному преобразованию При этом реализуется функция вида

fj «

1

(7)

sin arctgCXj, /xj)j

С этой целью для всех возможных значений отношений xjj/xj вычисляются значения функции (7) и записьгааются в соответствующие ячейки ПЗУ 17 Код, поступающий на вход ПЗУ 17 с выхода блока 21 является кодом адреса и выбирает соответствующую ячейку ПЗУ. При этом сигнал считывания содержимого выбранной ячейки подается в ПЗУ 17 с выхода элемента 18, который обеспечивает задержку сигнала на время, необходимое для вьтолнения операции деления блоком 21« Содержимое выбранной ячейки ПЗУ 17 поступает на второй вход блока у 1ножения 16 Блок з ножения 16 перемножает коды, поступивщие на его первый и второй входы по сигналу, поступающему с выхода элемента 19 Эта схема задерживает сигнал, поступивщий на ее вход на время переходных процессов, возникающих при считьгаании информахри из ПЗУ 17. По окончании операциц умножения на выходе блока 16 формируется код амплитудного значения текущего полупериода выходного сигнала фильтра 3;. Этот код поступает на выход детектора 5о В то же время на управляющий вькод детектора 5 поступает сигнал с выхода элемента 20, который задерживает сигнал, поступающий на ее вход, на время выполнения операции умножения блоком 16. Этот сигнал фиксирует окончание цикла обработки данных, связанной с определением текуще1 о амплитудного значения сигнала.

о р м у л а

f

12 изобретения

5

0

5

0

5

0

5

0

55

1316

вход, при этом выход входного усилителя соединен с входом аналого-щ- фрового преобразователя, выход которого соединен с объединенными входами цифровых фильтров, выход каждого фильтра соединен с входами соответствующей пары буферных регистров, управляющие входы которых соединены с соответствующим выходом дешифратора, управляющий выход первого регистра каждой пары соединен с вторым управляюпщм входом второго регистра той же пары, управляющий выход которого соединен с соответствующим входом блока приоритетных прерываний, выходы первого и второго регистров каждой пары подключены соответственно к первому и второму входам пикового детектора, выход которого соединен с входом блока детектирования, управляющий, вход пикового детектора подключен к двенадцатому выходу блока управления, восьмой вход которого соединен с дополнительным управляющим входом анализатора, управляющий вход пикового детектора подключен к девятому входу блока управления.и управляющему входу дешифратора, выход блока детектирования соединен с входом блока извлечения квадратного корня и вторым входом первого коммутатора, выход которого подключен к первому вхо10

396914

ду второго коммутатора и входу логарифмического преобразователя, выход которого соединен с вторым входом второго коммутатора, выход которого подключен к выходу анализатора, а управляющий вход - к тринадцатому входу блока управления,

15

20

30

Авторы

Даты

1990-12-15—Публикация

1987-11-27—Подача