11308929

Изобретение относится к измери-. тельной технике и предназначено для анализа спектров сигналов в реальном масштабе времени.

Цель изобретения - повышение точности определения частот составляющих спектра сигнала путем совместной обработки фазовых спектров соприкасаю- П1НХСЯ реализаций сигнала и вычисления

2

блоков 6 и 7 памяти соответственно и с выходными шинами 25 и 26 устройства. Выходные шины сумматоров 5 и 8 соединены соответственно с информационными входами блоков 6 и 7 памяти и первым и вторым входами блока 9 вычисления фаз,- выход которого соеди нен с информационной входной шиной блока 10 памяти, выход последнего со

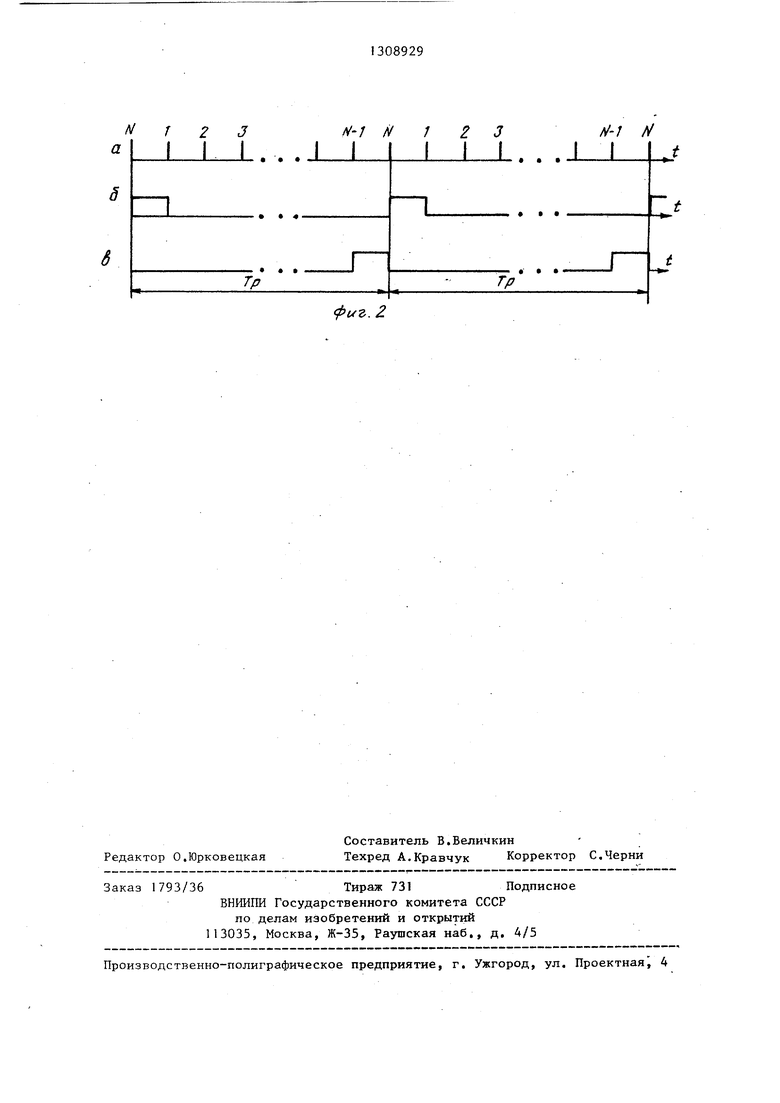

отклонений частот составляюш 1Х от со- fO единен с информационной входной шиответствуюших дискретных частот. , На фиг.1 приведена структурная схема цифрового анализатора спектра; на фиг.2 - временные диаграммы, поясняющие его работу.

Анализатор содержит аналого-цифровой преобразователь (АДП) 1, первый блок 2 умножения, цифровой генератор

3гармонических функций, второй .блок

4умножения, первый сумматор 5, первый и второй блоки 6 и 7 памяти, второй сумматор 8, блок 9 вычисления фаз, третий и четвертой блоки 10 и

11 памяти, блок 12 задания коэффициента 1/2П, третий блок 13 умножения, блок 14 вычитания, третий сумматор 15 первый счетчик 16, дешифратор 17, татовый генератор 18, второй счетчик 19, первый и второй элементы 20 и 21 :задержки, первый и второй элементы И 22 и 23.

Сигнальный вход АЦП 1 соединен с входной клеммой 24 устройства, так- товьй вход - с выходом второго счетчика 19 и входом первого счетчика 16 а выходная шина АЦП - с первыми входами блоков 2 и 4 умножения, вторые входы которых соединены с выходными шинами косинуса и синуса соответственно цифрового генератора 3 гармонических функций, информационный вход которого соединен с выходной шиной счетчика 16 и входной шиной дешифратора 17, первый выход (фиг,2в) которого соединен с входами разрешения считывания блоков 6 и 7 памяти, а второй выход (фиг,2в) - с первыми входами элементов И 22 и 23. Выход тактового генератора 18 соединен с тактовым входом цифрового генератора 3 гармонических функций, входом элемента 20 задержки, вторым входом элемента И 23 и входом счетчика 19, выходная шина которого соединена с адресными входами блоков 6, 7, 10 и 11 памяти и вторым входом сумматора 15, выходные шины блоков 2 и 4 умножения соединены с выходными шинами

2

блоков 6 и 7 памяти соответственно и с выходными шинами 25 и 26 устройства. Выходные шины сумматоров 5 и 8 соединены соответственно с информационными входами блоков 6 и 7 памяти и первым и вторым входами блока 9 вычисления фаз,- выход которого соединен с информационной входной шиной блока 10 памяти, выход последнего соной блока 11 памяти и шиной уменьшаемого блока 14 вычитания, шина вычитаемого которого соединена с выходом бл ока 1 1 памяти, а выход -. с первым 5 входом блока 13 умножения, второй вход которого соединен с выходной, шиной блока 12 задания коэффициента 1/2П, Первая входная шина сумматора 15 соединена с выходом блока 13 умножения , а выходная шина - с выходом 27 анализатора. Выход элемента 20 задержки соединен с входами записи блоков 6 и 7 памяти и через элемент 21 задержки с вторым входом элемента И 22, выход которого соединен со входом записи блока 10 памяти. Выход элемента И 23 соединен с входом записи бло0

5

0

0

ка 11 памяти. I

Анализатор работает следуюш 1м образом.

Блоки известного устройства обеспечивают вычисление пар коэффициентов Фурье путем обработки реализации сигнала длительностью Тр, что соот- - ветствует разрешению по частоте uf 1/Тр, Вычисления выполняются последовательно в паузах между отсчетами сигнала и заканчиваются до начала следующей реализации, что позволяет получить спектры соприкасающихся реализаций сигнала в реальном масштабе времени, АЦП 1 преобразует сигнал в ряд цифровых значений, формируемых по импульсам, поступающим со счетчика 19 (фиг,2а). При этом каждая реализация представляется N дискретными, отсчетами, N-й отсчет для данной реализации является нулевым для следующей. Цифровой г енератор 3 за каждый период дискретизации последовательно формирует m пар значений гармонических функций для всех дискретных частот. Порядок изменения значений гармонических функций при обработке каждого отсчета задается номером отсчета К, поступающим со счетчика 16. Каждое значение кода АЦП 1 последовательно умножается в блоках 2 и 4 на тп сопря5

0

5

i-го эквивалентного фильтра. Разрешая уравнение (2) относительно частоты составляющей с учетом того, что

Ol

1

uf, окончательно получают

ьФ.

(i + :;-) &f. (5)

женных значений косинуса и синуса соответственно, а результаты поступают на сумматоры 5 и 8, где складываются с числами, считываемыми с блоков 6 и 7 памяти. По N-му отсчету формирует- ся строб, длительность которого равна периоду дискретизации (фиг.26), который запрещает считывание информации. При этом на выходах блоков 6 и 7 формируются нулевые коды, цепь обратной fO связи разрывается, и в блоки 6 и 7 памяти производится запись первых для новой реализации произведений. На адресные входы этих блоков поступает номер дискретной частоты i, что обес- 15 печивает однозначное соответствие с генерируемыми блоком 3 гармоническими функциями. По окончании строба обрат- Hbie связи замь каются, и в блоках памяти формируются действительный и 20 Формирует на втором выходе строб мнимый коэффициенты Фурье для каждой (фиг.2в), разрешающий прохождение им- из m частот. Их вычисление завершается при обработке (N-l)-ro отсчета.

Учитывая, что значение -uf заранее задается и известно с большой точностью, аппаратурно достаточно определить безразмерную частоту i-й составляющей

Ф; 2 ir

р.

i + (6)

Регистрация фаз составляющих спектра в блоке 10 памяти производится в течение (N-l)-ro периода дискретизации. Для этого дешифратор 17

пульсов тактового генератора 18 на вход записи блока 10 памяти. Аналогично в блоке 11 памяти производится

Блок 9 вычисления фаз выдает результат при поступлении на его вход действительного и мнимого коэффициентов Фурье с выходов сумматоров 5 и 8. Фаза i-й составляющей спектра определяется выражением

(t) (Q; - COg, )-t , (1)

где CO; - угловая частота i-й гармо.НИКИ; COj) - угловая частота ближайшей,

дискреты; начальная фаза i-й составляющей.

Значения 9 (t) вьтисляются последовательно для следующих друг за другом реализаций сигнала со сдвигом во времени Тр 1/uf. Поэтому разность фаз i-й составляющей спектра для соседних реализаций равна

(со;-СО,-), i(2)

uf -

Предельные значения СО; определяются полосой пропускания эвивалентного

фильтра uf

uf

W.,;± lr.f. (3)

,; ± 21Г НПодставляя эти значения Q в выражение (2), находят пределы изменения разности фаз

Л. t ,(4)

откуда следует, что величина разности не превьшает f и имеет знак, соответствующий знаку отклонения частоты i-й составляющей от средней частоты

i-го эквивалентного фильтра. Разрешая уравнение (2) относительно частоты составляющей с учетом того, что

ормирует на втором выходе строб фиг.2в), разрешающий прохождение им-

Ol

1

uf, окончательно получают

ьФ.

(i + :;-) &f. (5)

ормирует на втором выходе строб фиг.2в), разрешающий прохождение им

Формирует на втором выходе строб (фиг.2в), разрешающий прохождение им-

Учитывая, что значение -uf заранее задается и известно с большой точностью, аппаратурно достаточно определить безразмерную частоту i-й составляющей

Ф; 2 ir

р.

i + (6)

Формирует на втором выходе строб (фиг.2в), разрешающий прохождение им-

Регистрация фаз составляющих спектра в блоке 10 памяти производится в течение (N-l)-ro периода дискретизации. Для этого дешифратор 17

Формирует на втором выходе строб (фиг.2в), разрешающий прохождение им-

пульсов тактового генератора 18 на вход записи блока 10 памяти. Аналогично в блоке 11 памяти производится

перезапись информации из блока 10 памяти. Запись в блоки 6 и 7 памяти производится с задержкой, учитьшаю- щей запаздывание формирования частных сумм на входах-блоков памяти. Запись значений фаз в блок 10 памяти производится с задержкой, учитывающей время формирования фаз на выходе блока 9. Запись информации в блок 11 памяти производится без задержки.

При ЭТОМ в течение (N-l)-ro периода дискретизации для каждой частотной- дискреты значений фазы предьщущей реализации переписывается из блока

10в блок 11, затем в блок 10 записывается значение фазы данной реализации. На выходе блока 14 вычитания формируется разность фаз , . Блоки 12, 13 и 15 обеспечивают вычисление уточненного значения безразмерной частоты каждой гармоники в соответствии с выражением (6). На второй вход сумматора 15 поступает номер частотной дискреты i с выхода счетчика 19. Согласованность работы всех узлов устройства достигается одновременным изменением адресов блоков 6, 7, 10 и

11памяти в соответствии с номером i частотной дискреты.

Эффект повьШ1ения точности определения частоты можно оценить по отношению ошибки, вносимой известным устройством, к ошибке, вносимой предлагаемым устройством

bf uf;

27

йТьФ;)

(7)

где йОдФ) - абсолютная величина

ошибки измерения разнос- ти фаз,

Из выражения (7) следует, что эффект повьшения точности определения частот составляющих спектра сигнала определяется величиной, обратной ошибке измерения разности фаз сойтав ляющей спектра для двух соседних реализаций сигнала. Например, если эта ошибка 3 , точность повьшается

)

более чем в 100 раз. Таким образом, предлагаемое устройство обеспечивает существенное повьшение точности определения частот составляющих .спектра сигнала.

Формула из Обретения

Цифровой анализатор спектра, содержащий аналого-цифровой преобразователь, первый и второй блоки умноже ния, первый и второй блоки памяти, тактовый генератор, первый и второй счетчики, причем сигнальный вход аналого-цифрового преобразователясоединен с входной клеммой прибора, тактовый вход - с выходом первого и входом второго счетчиков, а выход - с первыми входными шинами первого и второго блоков умножения, вторые входные шины которых соединены соответственно с выходами косинуса - и, синуса цифрового генератора гармонических функций, тактовый вход которого соединен с выходом тактового генератора и входом первого счетчика, первые входы пер- вого и второго,сумматоров соединены соответственно с выходньти шинами первого и второго блоков умножения, вторые входы этих сумматоров соединены с выходными шинами первого и второго блоков памяти соответственно и выходными шинами действительного и мнимого коэффициентов Фурье устройства, а выходы сумматоров - с информационны

ми входными шинами первого и второго блоков памяти соответственно, адрес5

Ю

15

20

25

30

Ш)1е входы последних соединены с вы- ходной шиной первого счетчика, о т личающийся тем, что, с целью повышения точности определения частот составляющих спектра сигнала путем совместной-обработки фазовых спектров соприкасающихся реализаций, в него введены блок вычисления фаз,. третий и четвертый блоки памяти, блок вычитания, третий блок умножения блок задания коэффициента 1/2П, третий сумматор, дешифратор, первьш и второй элементы задержки, первый и второй элементы И, причем первый и второй входы блока вычисления фаз соединены с выходными шинами первого и второго сумматоров соответственно, а выход - с входной информационной шиной третьего блока памяти, выходная шина которого соединена с информационным входом четвертого блока памяти и входом уменьшаемого блока вычитания, вход которого соединен с выходной шиной четвертого блока памяти, а выход - с первой входной шиной третьего блока умножения, вторая входная шина которого соединена с выходом блока задания коэффициента 1/2П, а выходная шина - с первым входом третьего сумматора, выход которого соединен с выходной шиной кодов частот устройства, а второй вход - с адресными входами третьего и четвертого блоков памяти и с вы35 ходной шиной первого счетчика, вход дешифратора соединен с входами разрешения считывания первого и второго блоков памяти, а второй его выход - с первыми входами первого и второго элементов И, выход тактового генератора соединен с вторым входом второго .элемента И и входом первого элемента задержки, выход которого соединен с входами записи первого и вто45 рого блоков памяти и через элемент задержки с вторым входом первого элемента И, выход которого соединен с входом записи третьего блока памяти, выход второго элемента И соединен с входом записи четвертого блока памяти.

50

фиг. Z

Редактор О.Юрковецкая

Составитель В.Величкин

Техред А.Кравчук Корректор С.Черни

Заказ 1793/36Тираж 731Подписное

ВНШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская иаб,, д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АНАЛИЗА СИГНАЛОВ В РЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ | 2009 |

|

RU2404438C1 |

| Цифровой анализатор мгновенного спектра | 1986 |

|

SU1456904A2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПСЕВДОСЛУЧАЙНОГО СИГНАЛА | 1989 |

|

SU1692272A1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА СИГНАЛОВ В РЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ | 2013 |

|

RU2550309C1 |

| Цифровой анализатор спектра | 1985 |

|

SU1322172A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СПЕКТРА | 1998 |

|

RU2125291C1 |

| Устройство для контроля функционирования аналого-цифровых преобразователей в динамическом режиме | 1988 |

|

SU1644378A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 1994 |

|

RU2060536C1 |

| Цифровой анализатор спектра | 1979 |

|

SU798615A1 |

Изобретение относится к измерительной технике и может быть использовано для анализа спектров сигналов в реальном масштабе времени. Цель изобретения - повышение точности определения частот составляющих спектра сигнала достигается путем совместной обработки фазовых спектров и вычисления отклонений частот составляющих от соответствующих дискретных частот. Устройство содержит аналого-цифровой преобразователь 1, блоки 2, 4 и 13 умножения, цифровой генератор 3 гармонических функций, сумматоры 5, 8 и 15, блоки 6, 7, 10 И 11 памяти, блок 9 вычисления фаз, блок 12 задания коэффициента, блок 12 задания коэффициента, блок 14 вычитания, счетчики 16 И 19, дешифратор 17, тактовый генератор 18, элементы 20 и 21 задержки, элементы И 22 и 23. Устройство обеспечивает существенное повьшение выполняемых измерений по сравнению с прототипом. 2 ИЛ. S (Л &: О эо х to х

| Евтеев Ю.И | |||

| и др | |||

| Аппаратурная реализация дискретного преобразования Фурье | |||

| - М.: Энергия, 1978, рис | |||

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

Авторы

Даты

1987-05-07—Публикация

1986-01-02—Подача