t13

Изобретение относится к цифровой обработке сигналов, а именно к устройствам измерения частоты, амплитуды и фазы гармоник цифровыми метода- ми,

Целью изобретения является повышение точности измерения частоты, амплитудь и фазы гармонических составляющих сигнала и сокращение вре- ,мени анализа,

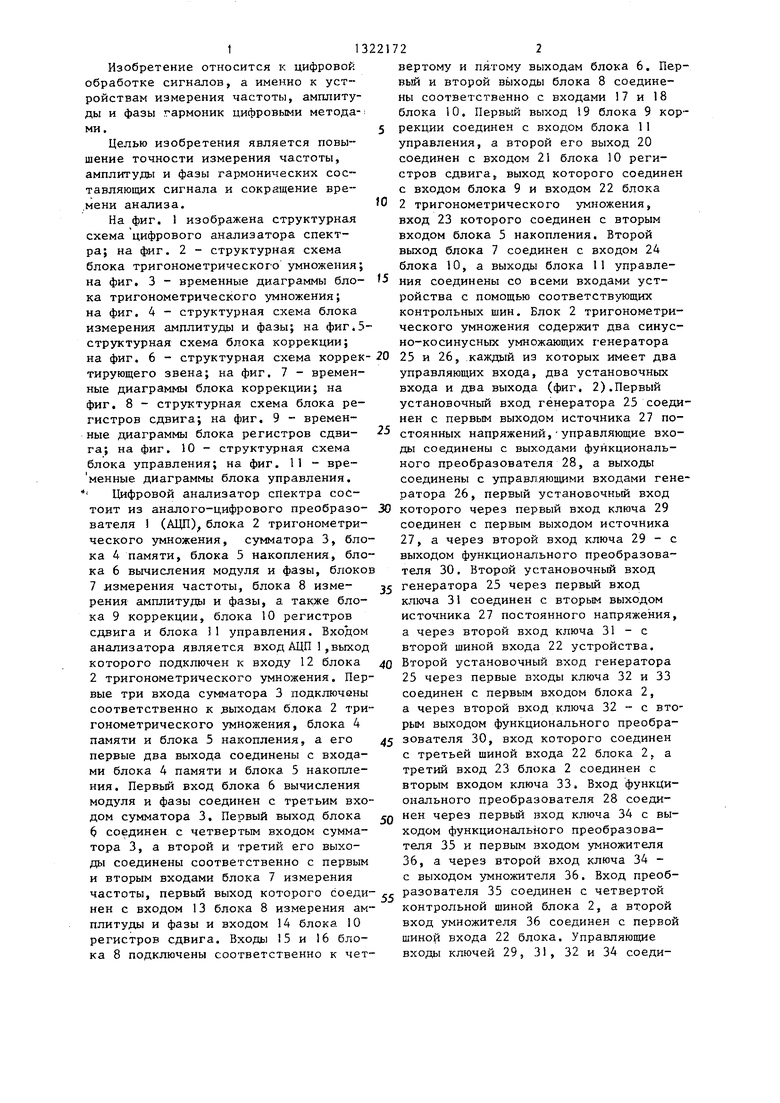

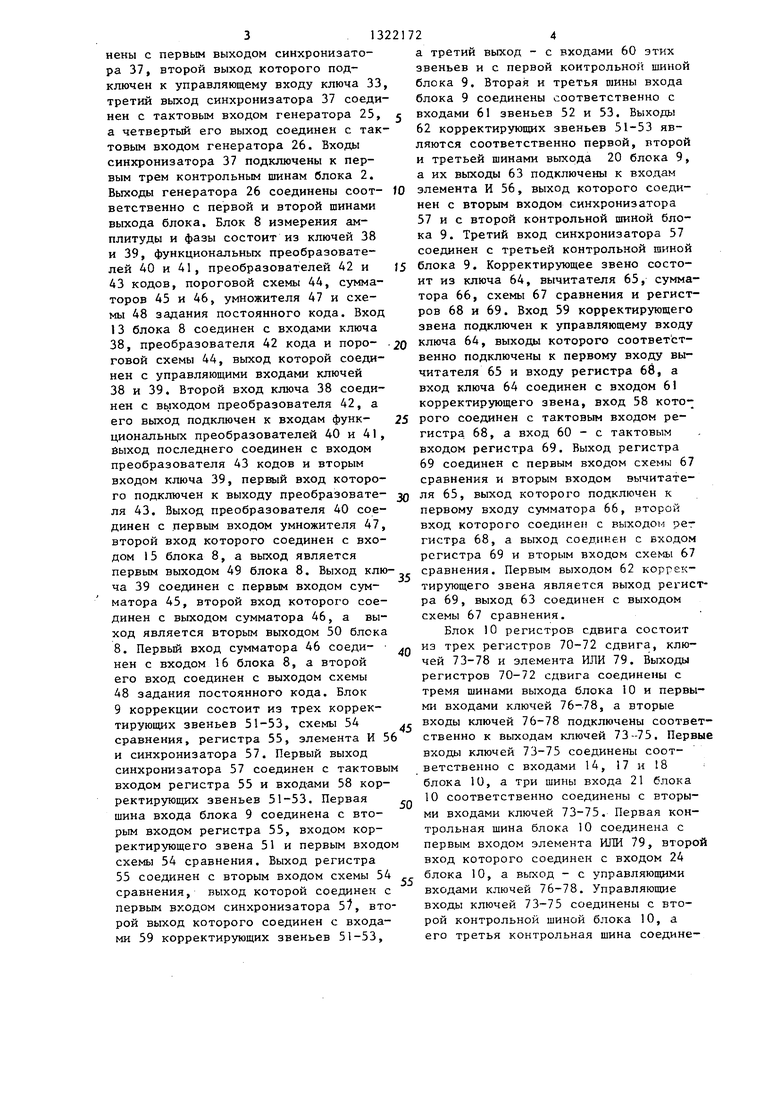

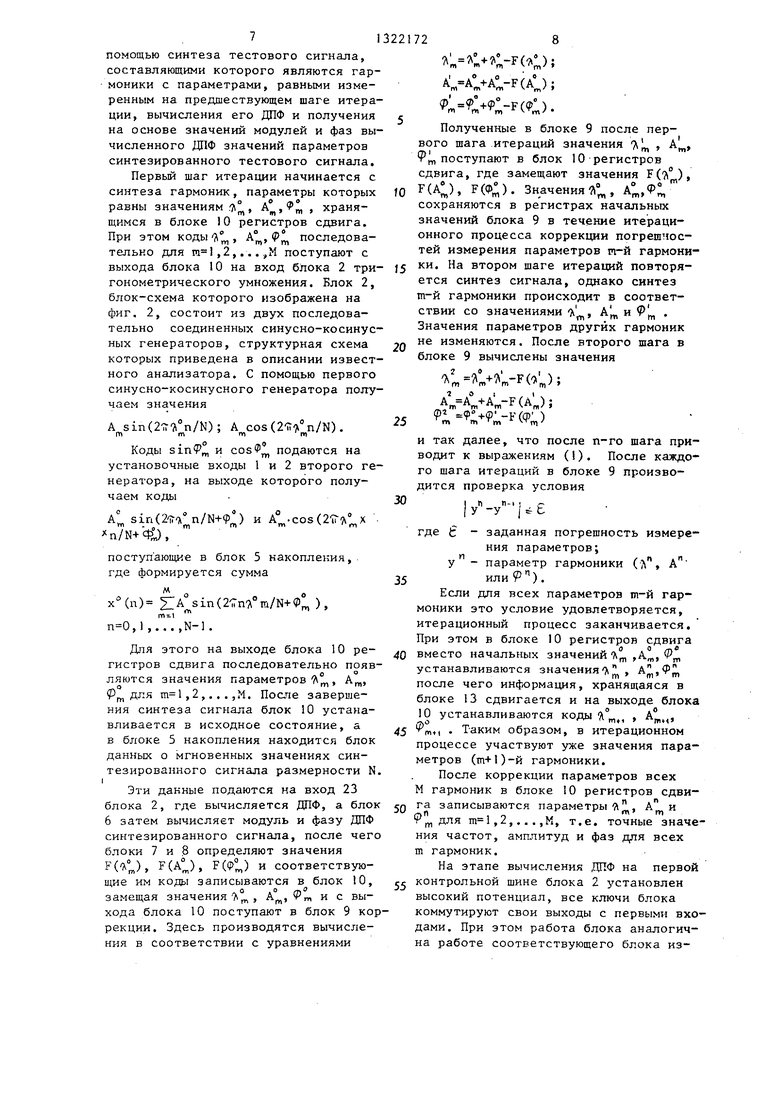

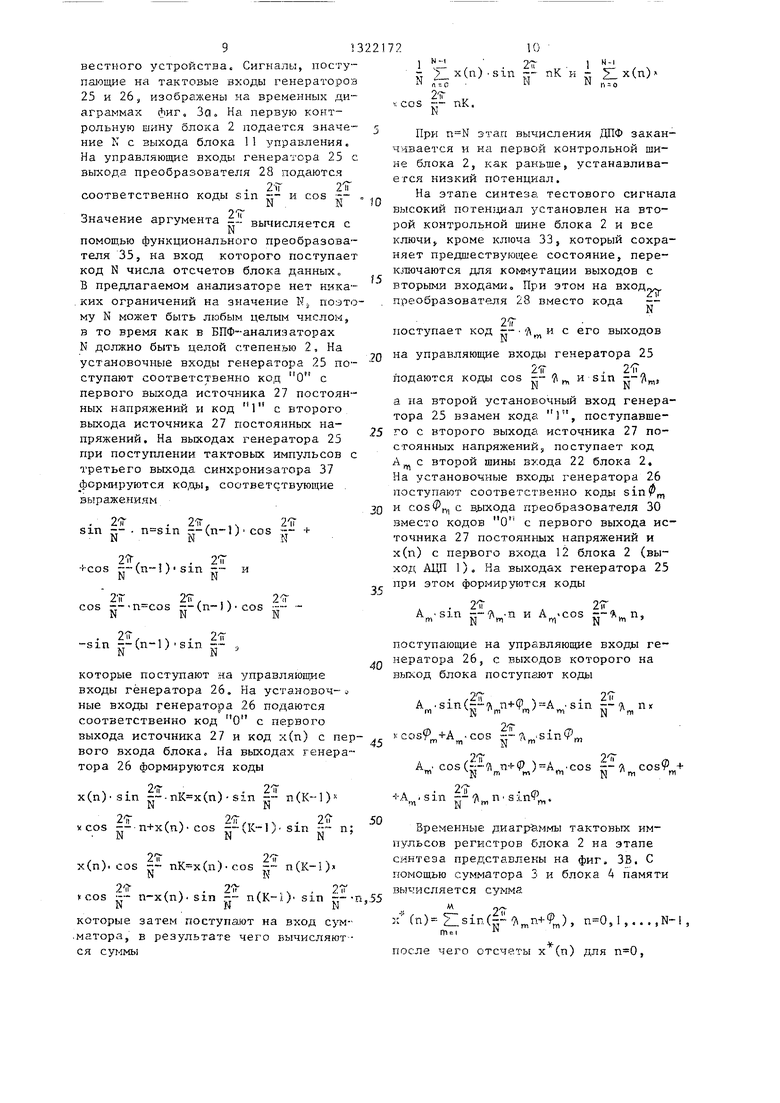

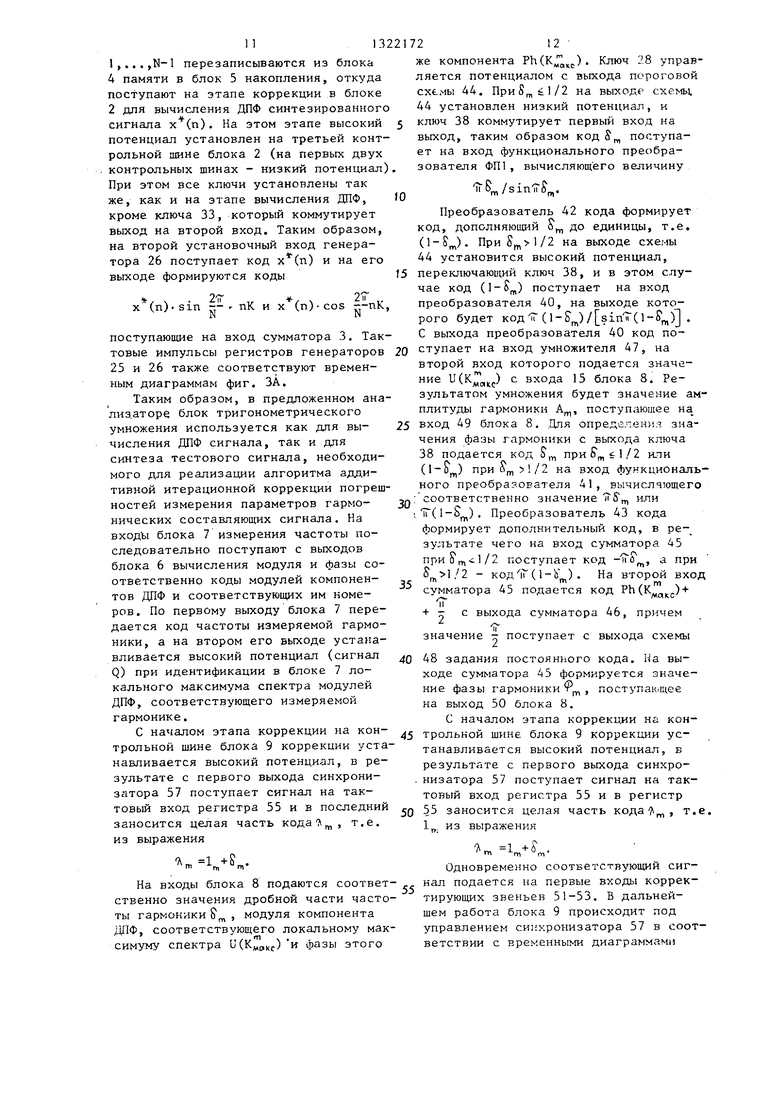

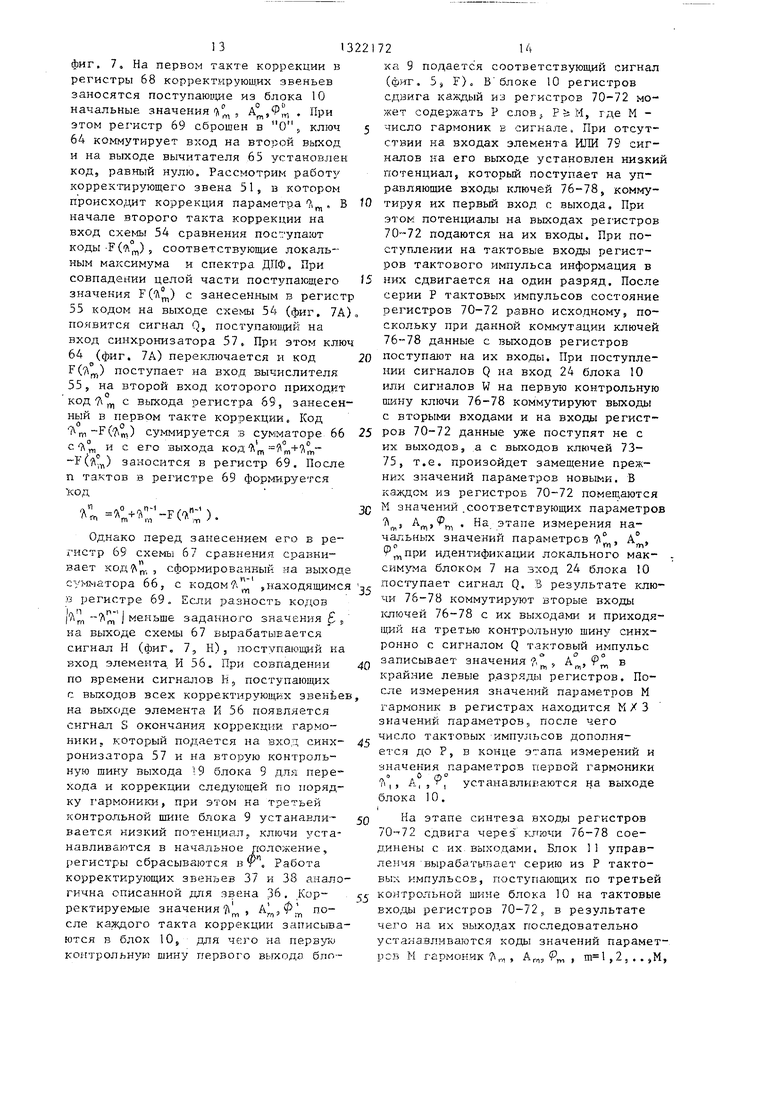

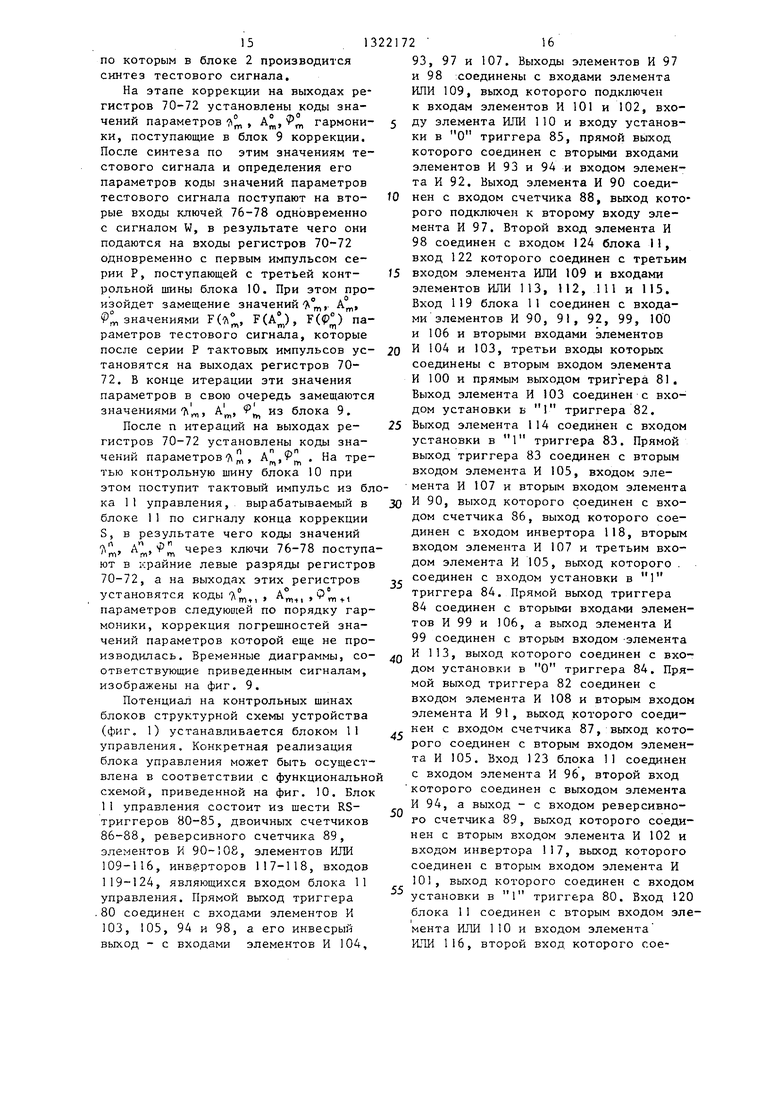

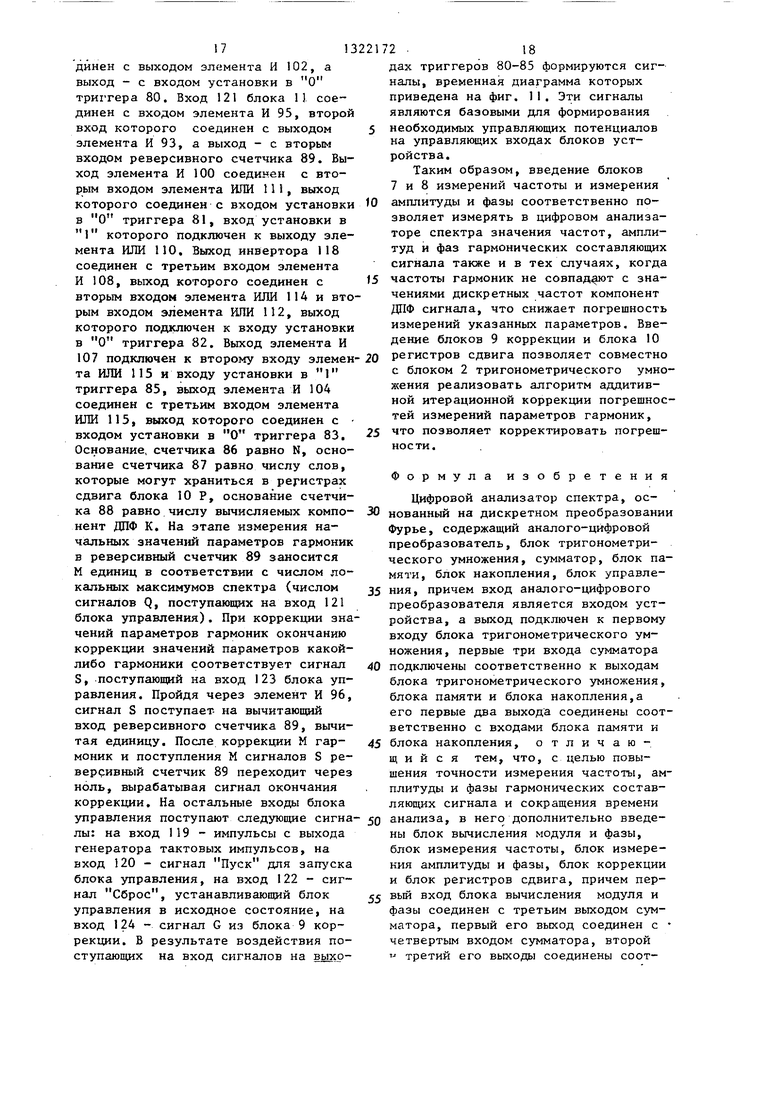

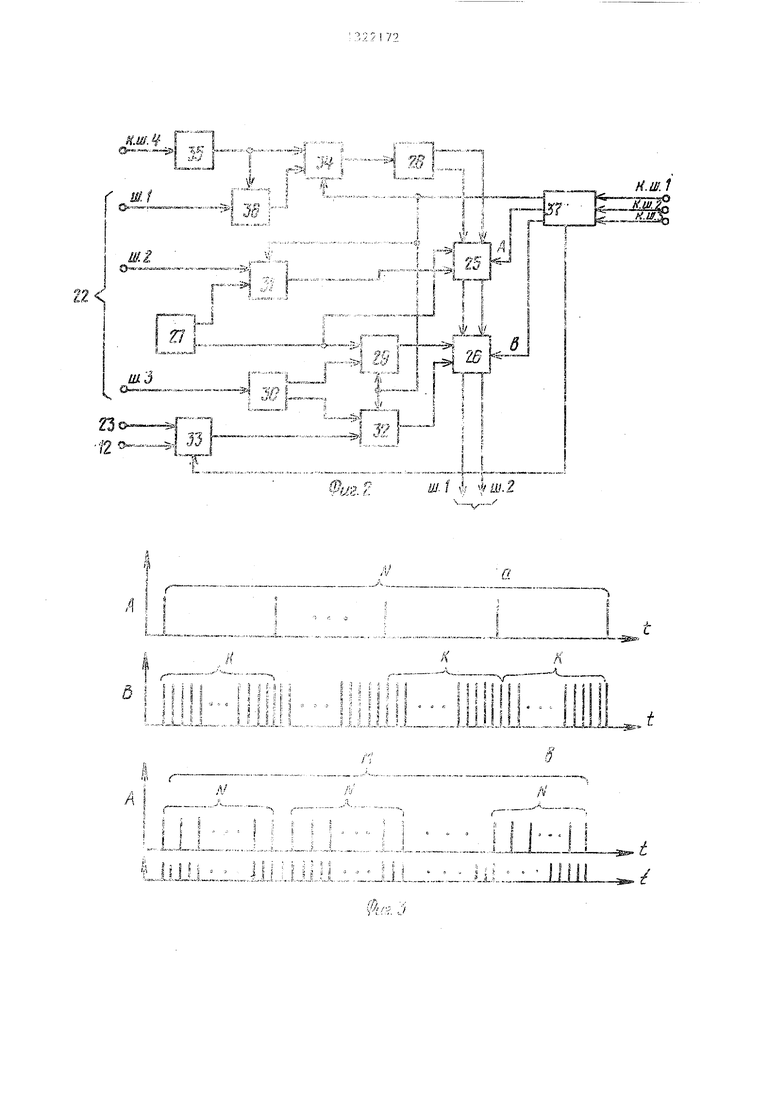

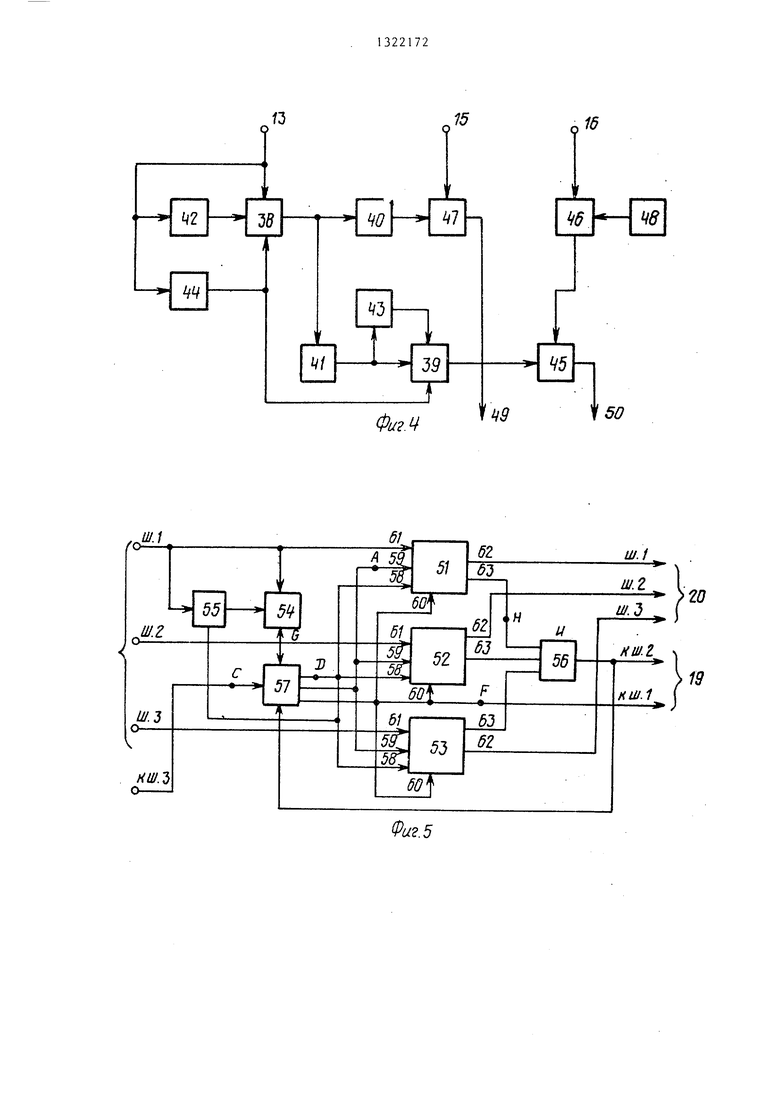

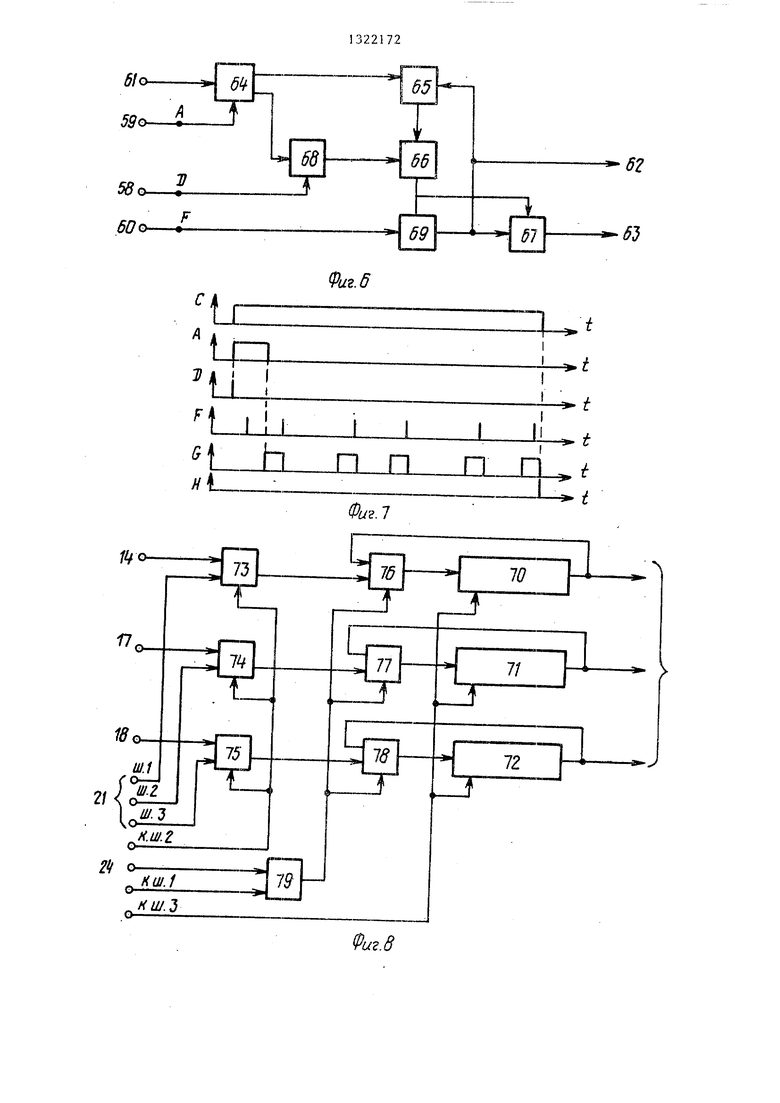

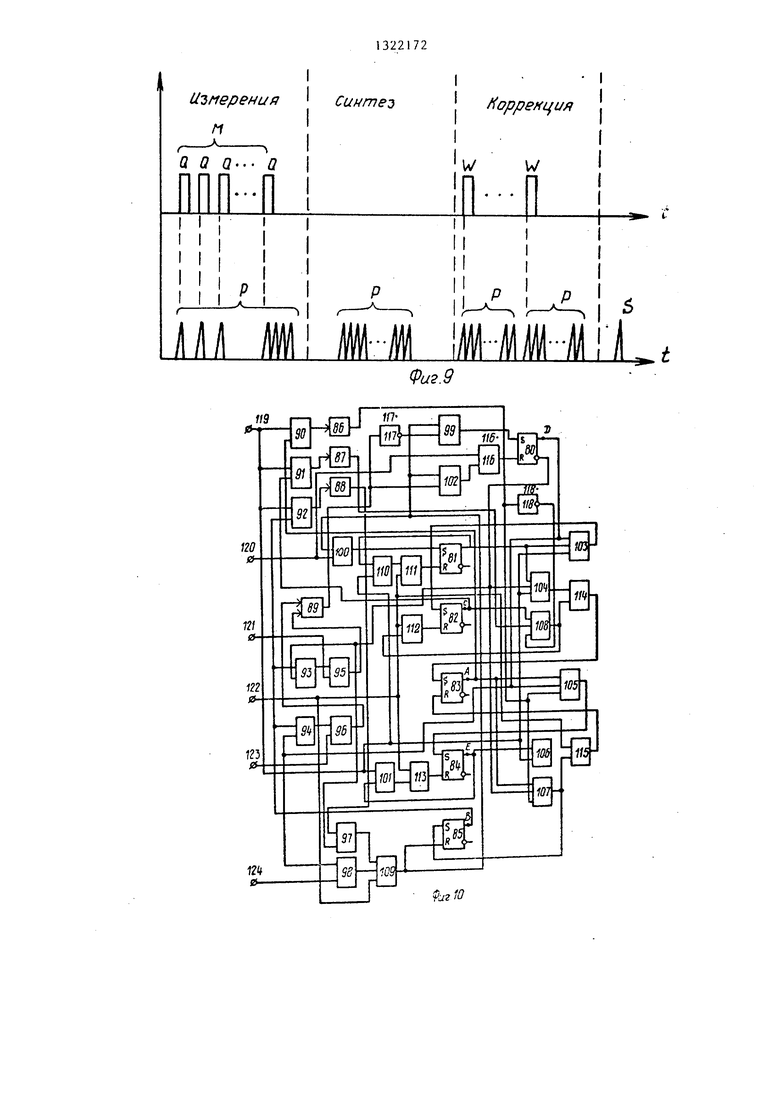

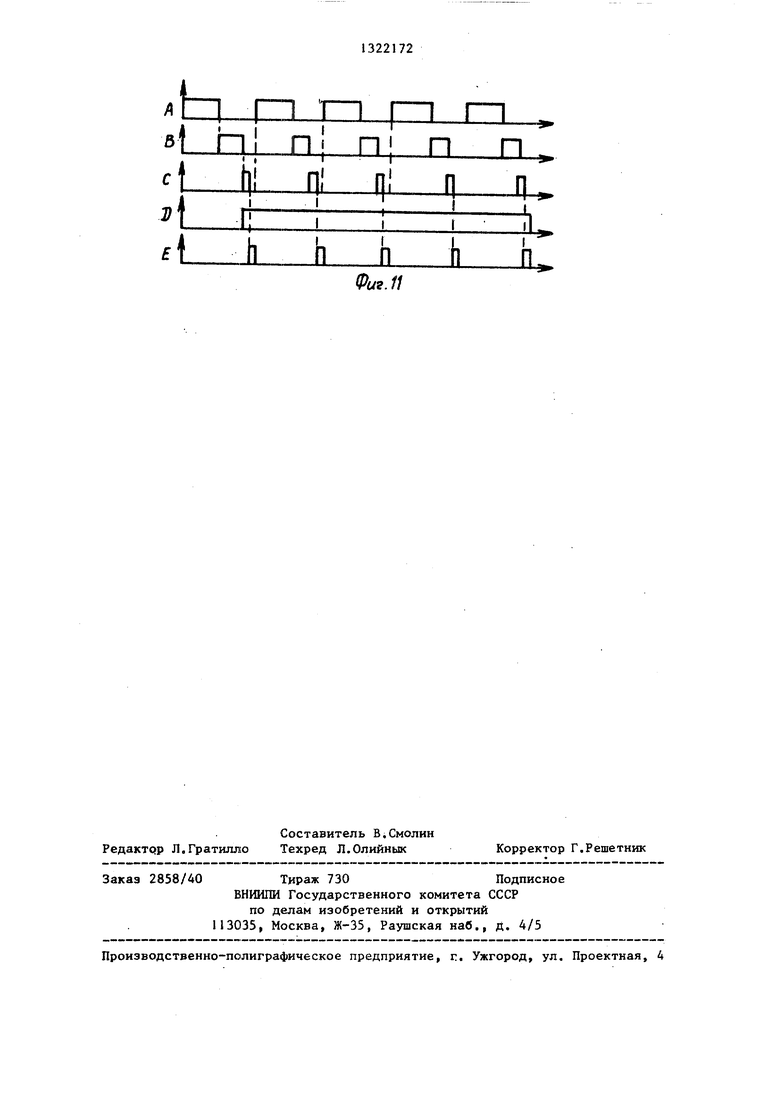

На фиг. 1 изображена структурная схема цифрового анализатора спектра; на фиг. 2 - структурная схема блока тригонометрического умножения; на фиг, 3 - временные диаграммы бло- ка тригонометрического умножения; на фиг. 4 - структурная схема блока измерения амплитуды и фазы; на структурная схема блока коррекции; на фиг. 6 - структурная схема коррек- тирующего звена; на фиг. 7 - временные диаграммы блока коррекции; на фиг, 8 - структурная схема блока регистров сдвига; на фиг. 9 - временные диаграммы блока регистров сдви- га; на фиг. 10 - структурная схема блока управления; на фиг. 11 - вре- менные диаграммы блока управления. Цифровой анализатор спектра состоит из аналого-цифрового преобразо- вателя (АЦП) блока 2 тригонометрического умножения, сумматора 3, блока 4 памяти, блока 5 накопления, блока 6 вычисления модуля и фазы, блоков 7 измерения частоты, блока 8 изме- рения амплитуды и фазы, а также блока 9 коррекции, блока 10 регистров сдвига и блока П управления. Входом анализатора является вход АЦП 1,выход которого подключен к входу 12 блока 2 тригонометрического умножения. Первые три входа сумматора 3 подключены соответственно к зыходам блока 2 тригонометрического умножения, блока 4 памяти и блока 5 накопления, а его первые два выхода соединены с входами блока 4 памяти и блока 5 накопления. Первый вход блока 6 вычисления модуля и фазы соединен с третьим входом сумматора 3, Первый выход блока ( соединен с четвертым входом сумматора 3, а второй и третий его выходы соединены соответственно с первым и вторым входами блока 7 измерения частоты, первый выход которого соеди- нен с входом 13 блока 8 измерения амплитуды и фазы и входом 4 блока 10 регистров сдвига. Входы 15 и 16 блока 8 подключены соответственно к чет722

вертому и пятому выходам блока 6. Певый и второй выходы блока 8 соединены соответственно с входами 17 и 18 блока 10. Первый выход 19 блока 9 корекции соединен с входом блока 11 управления, а второй его выход 20 соединен с входом 21 блока 10 регистров сдвига, выход которого соедине с входом блока 9 и входом 22 блока 2 тригонометрического умножения, вход 23 которого соединен с вторым входом блока 5 накопления. Второй выход блока 7 соединен с входом 24 блока 10, а выходы блока 1 управления соединены со всеми входами устройства с помощью соответствующих контрольных шин. БЛОК 2 тригонометрического умножения содержит два синус но-косинусных умножающих генератора 25 и 26, каждый из которых имеет два управляющих входа, два установочных входа и два выхода (фиг. 2).Первый установочный вход генератора 25 соеднен с первым выходом источника 27 постоянных напряжений,управляющие входы соединены с выходами функционального преобразователя 28, а выходы соединены с управляющими входами генратора 26, первый установочный вход которого через первый вход ключа 29 соединен с первым выходом источника 27, а через второй вход ключа 29 - с выходом функционального преобразователя 30, Второй установочный вход генератора 25 через первый вход ключа 31 соединен с вторым выходом источника 27 постоянного напряжения, а через второй вход ключа 31 - с второй шиной входа 22 устройства. Второй установочный вход генератора 25 через первые входы ключа 32 и 33 соединен с первым входом блока 2, а через второй вход ключа 32 с вторым выходом функционального преобразователя 30, вход которого соединен с третьей шиной входа 22 блока 2, а третий вход 23 блока 2 соединен с вторым входом ключа 33, Вход функционального преобразователя 28 соединен через первьш вход ключа 34 с выходом функционального преобразователя 35 и первым входом умножителя 36, а через второй вход ключа 34 - с выходом умножителя 36. Вход преобразователя 35 соединен с четвертой контрольной шиной блока 2, а второй вход умножителя 36 соединен с первой шиной входа 22 блока. Управляющие входы ключей 29, 31, 32 и 34 соеди

йены с первым выходом синхронизатора 37, второй выход которого подключен к управляющему входу ключа 33 третий выход синхронизатора 37 соединен с тактовым входом генератора 25, а четвертьш его выход соединен с тактовым входом генератора 26. Входы синхронизатора 37 подключены к первым трем контрольным шинам блока 2. Выходы генератора 26 соединены соответственно с первой и второй шинами выхода блока. Блок 8 измерения амплитуды и фазы состоит из ключей 38 и 39, функциональных преобразователей 40 и 41, преобразователей 42 и 43 кодов, пороговой схемы 44, сумматоров 45 и 46, умножителя 47 и схемы 48 задания постоянного кода. Вход 13 блока 8 соединен с входами ключа 38, преобразователя 42 кода и пороговой схемы 44, выход которой соединен с управляющими входами ключей 38 и 39. Второй вход ключа 38 соединен с выходом преобразователя 42, а его выход подключен к входам функциональных преобразователей 40 и 41, выход последнего соединен с входом преобразователя 43 кодов и вторым входом ключа 39, первый вход которого подключен к выходу преобразователя 43. Выход преобразователя 40 соединен с первым входом умножителя 47, второй вход которого соединен с входом 15 блока 8, а выход является первым выходом 49 блока 8. Выход ключа 39 соединен с первым входом сумматора 45, второй вход которого соединен с выходом сумматора 46, а выход является вторым выходом 50 блока 8. Первый вход сумматора 46 соеди- нен с входом 16 блока 8, а второй его вход соединен с выходом схемы 48 задания постоянного кода. Блок 9 коррекции состоит из трех корректирующих звеньев 51-53, схемы 54 сравнения, регистра 55, элемента И 5 и синхронизатора 57. Первый выход синхронизатора 57 соединен с тактовы входом регистра 55 и входами 58 корректирующих звеньев 51-53. Первая шина входа блока 9 соединена с вторым входом регистра 55, входом корректирующего звена 51 и первым входо

Блок 10 регистров сдвига состоит иэ трех регистров 70-72 сдвига, ключей 73-78 и элемента ИЛИ 79. Выходы регистров 70-72 сдвига соединены с тремя шинами выхода блока 10 и первыми входами ключей 76-78, а вторые входы ключей 76-78 подключены соответ ственно к выходам ключей 73--75, Первы входы ключей 73-75 соединены соответственно с входами 14, 17 и 18 блока 10, а три шины входа 21 блока 10 соответственно соединены с вторыми входами ключей 73-75. Первая контрольная шина блока 10 соединена с первым входом элемента ИЛИ 79, второй вход которого соединен с входом 24

схемы 54 сравнения. Выход регистра 55 соединен с вторым входом схемы 54 .. блока 10, а выход - с управляющими сравнения, выход которой соединен с входами ключей 76-78. Управляющие первым входом синхронизатора 5, вто- входы ключей 73-75 соединены с второй выход которого соединен с входа- рой контрольной шиной блока 10, а ми 59 корректирующих звеньев 51-53, его третья контрольная шина соединеto

J5

20

25

, , , , юа56ым ом

3221724

а третий выход - с входами 60 этих звеньев и с первой коитрольно1 шиной блока 9. Вторая и третья шины входа блока 9 соединены соответственно с входами 61 звеньев 52 и 53. Выходы 62 кoppeктиpyюшJ x звеньев 51-53 являются соответственно первой, второй и третьей шинами выхода 20 блока 9, а их выходы 63 подключены к входам элемента И 56, выход которого соединен с вторым входом синхронизатора 57 и с второй контрольной шиной блока 9. Третий вход синхронизатора 57 соединен с третьей контрольной шиной блока 9. Корректирующее звено состоит из ключа 64, вычитателя 65, сумматора 66, схемы 67 сравнения и регистров 68 и 69. Вход 59 корректирующего звена подключен к управляющему входу ключа 64, выходы которого соответственно подключены к первому входу вычитателя 65 и входу регистра б8, а вход ключа 64 соединен с входом 61 корректирующего звена, вход 58 которого соединен с тактовым входом регистра. 68, а вход 60 - с тактовым входом регистра 69. Выход регистра 69 соединен с первым входом схемы 67 сравнения и вторым входом вычитателя 65, выход которого подключен к первому входу сумматора 66, второй вход которого соединен с выходом per гистра 68, а выход соединен с входом регистра 69 и вторым входом схемы 67 сравнения. Первым выходом 62 корректирующего звена является выход регистра 69, выход 63 соединен с выходом схемы 67 сравнения.

Блок 10 регистров сдвига состоит иэ трех регистров 70-72 сдвига, ключей 73-78 и элемента ИЛИ 79. Выходы регистров 70-72 сдвига соединены с тремя шинами выхода блока 10 и первыми входами ключей 76-78, а вторые входы ключей 76-78 подключены соответственно к выходам ключей 73--75, Первые входы ключей 73-75 соединены соответственно с входами 14, 17 и 18 блока 10, а три шины входа 21 блока 10 соответственно соединены с вторыми входами ключей 73-75. Первая контрольная шина блока 10 соединена с первым входом элемента ИЛИ 79, второй вход которого соединен с входом 24

30

35

40

50

4 .. блока 10, а выход - с управляющими с входами ключей 76-78. Управляющие о- входы ключей 73-75 соединены с вто- рой контрольной шиной блока 10, а его третья контрольная шина соедине513221

на с тактовыми входами регистров 70- 72, входы которых соединены соответственно с выходами ключей 76-78.

Устройство работает следующим образом.5

Сигнал x(t) поступает на вход АЦП 1, где происходит его дискретизация, и его отсчет х(п) подается на вход блока 2 тригонометрического умножения, где в соответствии с заданными 10 значениями числа обрабатываемых отсчетов N и числа компонент ДПФ К формируются коды, соответствующие выражениям

27

г(п,К)х(п) .cos(-.;- пК);

iM о/1(п5К)х(.п). sin(-- пК),

поступающим в сумматор 3, в котором 20 с помощью блока 4 памяти вычисляются суммы

; S Zlx(n)cos(|- ПК);

N t

25

30

1;(К) x(n)sin(|- пК),

п.о

где ,N-1, ,1,...,К-1 .

Значения R;(K) и (К) передаются затем в блок 6 вычисления модуля и фазы ДПФ, откуда значения периодограммы

Р.(К)К;(К)(К)

через сумматор 3 подаются вблок 5 35

накопления, где формируетсясостоя-

тельная оценка спектральнойплот- ности мощности

s(K) - ГР-СЮ.

m :,.

Однако, если сигнал содержит гармонические составляю цие, приведенная оценка не позволяет точно измерить их частоты, амп.питудд и фазы. В этом случае блок 6 формирует коды модуля и фазы ДПФ

и(К) к(К)-и (К) ; Ph(K)-arctg l(K)/P(K) .

Значения U(K), ,l,..,,Ks поступают по мере готовности в блок 7 измерения частоты, где происходят поиск локальных макс:имумов спектра амплитуд и вычисление частоты гармо- НИКИ в соответствии с вырг1жениями

п , l jiaiitll wayjciyl iJasJlHiSiiajEil

у(к1,,)+и(к:,,,-1)

726

при b (C,,- l)U(lC,,+.l);

о, ,-Кис,((Кмс,«+11

u(K:;J-fu(K;:;;,,+T) при и(Скс+ ),,-1),

где KftaKc даФ5 соответствующий локальному максимуму спектра амплитуд; -Д , т.е. Л - частота гармоники в единицах бин ДПФ, при- ,

1... при и(,,+ 1)и( -1) и

fn «акс .11

V K-Kc-l) РИ U(K.,,,+ l)U(), .

Измеренное значение частоты гармоники 7 поступает с выхода блока 7 на первый вход 13 блока 8 измерения амплитуды и фазы. На входь 15 и 16 блока 8 с выходов блока 6 поступают коды и(К) и Ph(K). В блоке 8 измерения амплитуды и фазы используется дробная часть значения частоты гармоники &, причем если 5 п1 л/2, то амплитуда и фаза гармоники вычисляются по формулам

д

«1 jsIn-rr S T

.-l,

а при S 2

А 2lU((ir&cl TsinTO-)l

((.-l)4- |.

Измеренные значения параметров гармоник л , А. и Ф поступают на хранение в блок 10 регистров сдвигов. После завершения зтапа измерения в блоке 10 находятся М хЗ параметров, где М - число гармонических составляющих сигнала. Следующим этапом является этап коррекции, при котором осуществляется аддитивная итерационная коррекция погрешностей (АИКП) измерений первого зтапа. Обозначив измеренные значения параметров гармоник как Ti , А, Р , запишем уравнения коррекции для каждого параметра

,Y;: ); А,А Д- -Г(- ); (1) Ф::,s Ч P „- -F(ф-),

где п - номер итерации; F(-) - оператор обратной цепи итерационного процесса, который реализуется с

71

помощью синтеза тестового сигнала, составляющими которого являются гармоники с параметрами, равными измеренным на предшествующем шаге итерации, вычисления его ДПФ и получения на основе значений модулей и фаз вычисленного ДПФ значений параметров синтезированного тестового сигнала. Первый шаг итерации начинается с синтеза гармоник, параметры которых равны значениям .7i, А,Р , хранящимся в блоке 10 регистров сдвига. При этом коды ;, А, (р последовательно для ,2,,..,М поступают с выхода блока 10 на вход блока 2 три- гонометрического умножения. Блок 2, блок-схема которого изображена на фиг. 2, состоит из двух последовательно соединенных синусно-косинус- ных генераторов, структурная схема которых приведена в описании известного анализатора. С помощью первого синусно-косинусного генератора получаем значения

А sin(2 ;r/n/N); А cos(2 « t°п/Ю .

П1fnWП1

Коды и cos подаются на установочные входы 1 и 2 второго генератора, на выходе которого получаем коды

А°„ sin(2 ir A n/N+9) и А°„.cos( °„х n/NH-Ф,

поступающие в блок 5 накопле1шя,

где формируется сумма

м Qд

х (п) А sin(2 ;rп ; °и/N+Ф ),

m.i ,1,...,N-1.

Для этого на выходе блока 10 ре- гистров сдвига последовательно появляются значения параметров Д , А„, Р для ,2,...,М. После завершения синтеза сигнала блок 10 устанавливается в исходное состояние, а в блоке 5 накопления находится блок данных о мгновенных значениях синтезированного сигнала размерности N

Эти данные подаются на вход 23 блока 2, где вычисляется ДПФ, а блок 6 затем вычисляет модуль и фазу ДПФ синтезированного сигнала, после чего блоки 7 и 8 определяют значения (°), F(A°), Р(Ф°) и соответствующие им коды записываются в блок 10, замещая значения , А°, Фп, и с выхода блока 10 поступают в блок 9 коррекции. Здесь производятся вычисления в соответствии с уравнениями

728

;-F(;);

А А%А°„-Р(А;);

Z-FCC).

Полученные в блоке 9 после первого шага итераций значения , А, Ф|„ поступают в блок 10 регистров сдвига, где замещают значения FCT),

F(A;), F((p;). Значения °„, А;,Ф;

сохраняются в регистрах начальных значений блока 9 в течение итерационного процесса коррекции погрештшс- тей измерения параметров п-й гармоники. На втором шаге итераций повторяется синтез сигнала, однако синтез т-й гармоники происходит в соответствии со значениями , А и Ф . Значения параметров других гармоник не изменяются. После второго шага в блоке 9 вычислены значения

(,);

А1 А1+А„-(А „);

р ф +ф -р(Ф ) m m m m

И так далее, что после п-го шага приводит к выражениям (). После каждого шага итераций в блоке 9 производится проверка условия

и П-1

У -У ,

где fc - заданная погрешность измерения параметров;

параметр гармоники (Ji, ).

Если для всех параметров т-й гармоники это условие удовлетворяется, итерационный процесс заканчивается, При этом в блоке 10 регистров сдвига вместо начальных значений А ,А„, Р„ устанавливаются значения JJ, , AjJ,,PjJ, после чего информация, хранящаяся в блоке 13 сдвигается и на выходе блока 10 устанавливаются коды , , А,,, „,, . Таким образом, в итерационном процессе участвуют уже значения параметров (т+1)-й гармоники,

После коррекции параметров всех М гармоник в блоке 10 регистров сдвига записываются параметры f(, А и для ,2,...,М, т.е. точные значения частот, амплитуд и фаз для всех m гармоник.

На этапе вычисления ДПФ на первой контрольной шине блока 2 установлен высокий потенциал, все ключи блока коммутируют свои выходы с первыми входами. При этом работа блока аналогична работе соответствующего блока из

91

вестного устройства. Сигналы, поступающие на тактовые входы генераторов 25 и 26, изображены на временных диаграммах фиг о За о На первую контрольную шину блока 2 подается значе- ние N с выхода блока 11 управления. На управляющие входы генератора 25 с выхода преобразователя 28 подаются

. Z ir 2Т соответственно коды sin -- и cos г- N , N

Значение аргумента вьтисляется с

помощью функционального преобразователя 35, на вход которого поступает код N числа отсчетов блока данных„ В предлагаемом анализаторе нет вика- .ких ограничений на значение Nj поэтому N может быть любым целым числом, в то время как в БПФ-анализагорах N должно быть целой степенью 2, На установочные входы генератора 25 по- ступают соответственно код О с первого выхода источника 27 постоянных напряжений и код 1 с второго выхода источника 27 постоянных напряжений. На выходах генератора 25 при поступлении тактовых импульсов с третьего выхода синхронизатора 37 формируются кода, соответствующие выражениям

. 21Г . 21Г. ,. 2ТГ sin --- -(n-i) Cos - + N N N

2. ,. . 27 +COS (n-) Sin -- и

NN

2Т 21.,. 2 cos --(n-).cos -- . ,. . Zir -sin --(n-l) sin -- ,

которые поступают на управляющие

входы генератора 26. На установоч- ные входы генератора .26 подаются соответственно код О с первого выхода источника 27 и код х(п) с пер вого входа блока. На выходах генератора 26 формируются коды

2л-О

IIгг/Ч Ч/,, ,

x(,n; Sin (п) szn - п()

2Т , .2 ir..,, ,, . 2fl-

«COS -- n+x(nj-COS -(K J-sin - n: NNN

or -O/ x(n). COS -- (n)-cos - n(K-)x NN

О/ Ч-f f i-| ij

X COS -- n-x(n). sin - n(K-I) sin -

которые затем поступают на вход сум- .матера, в результате чего вычисляются суммы

и

2

i cos -:- пК,

И

При этап вычисления ДПФ заканчивается и на первой контрольной шине блока 2, как раньше, устанавливается низкий потенциал.

На этапе синтеза тестового сигнала высокий пoтeн. установлен на второй контрольной шине блока 2 и все ключи, кроме ключа 33, который сохраняет предшествующее состояние, переключаются для коммутации выходов с вторыми входами. При этом на вход

N

преобразователя 28 вместо кода

2 ir поступает код г, Л,„и с его выходов

на управляющие входа генератора 25

5

0

,

0

5

0

5

ZT

2

подаются коды cos -- J и sin ,

а на второй установочный вход генератора 25 взамен кода 1, поступавшего с второго выхода источника 27 постоянных напряжений, поступает код А1 с второй шины входа 22 блока 2, На установочные входы генератора 26 поступают соответственно коды sin и с вД)1хода преобразователя 30 вместо кодов О с первого выхода источника 27 постоянных напряжений и х(п) с первого входа 12 блока 2 (выход АДП 1). На выходах генератора 25 при этом формируются коды

л 2 ir „sin и A.cos ,

поступающие на управляющие входы генератора 26, с выходов которого на выход блока поступс ют коды

, . ,2 п лч . 2 || A.sin(,.sin .

.cos „.sin

А„, cos()A.cos , -.A.sin .sinC .

Временные диагрёшмы тактовых импульсов регистров блока 2 на этапе синтеза представлены на фиг. ЗВ, С помощью сумматора 3 и блока 4 памяти вычисляется сумма

/ Сп)-. ZlsinC „,пн-Ф„), ,1,... ,N-1 , m i

после чего отсчеты х (п) для ,

11132217212

1 перезаписываются из блока же компонента Ph(K

„ ляется потенциалом схемы Д4. При 8,1/ 44 установлен низки

4 памяти в блок 5 накопления, откуда

„„) . Ключ 28 управ ляется потенциалом с выхода пороговой схемы Д4. При 8,1/2 на выходе схемы, 44 установлен низкий потенциал, и

же, как и на этапе вычисления ДПФ, кроме ключа 33, который коммутирует выход на второй вход. Таким образом, на второй установочный вход генератора 26 поступает код х(п) и на его выходе формируются коды

/ ч . 21Г „ / 2Т X (n) Sin -- пК и X (n)-cos t;

n,/

m Sin-;.

поступают на этапе коррекции в блоке 2 для вычисления ДПФ синтезированного сигнала х(п). На этом этапе высокий 5 ключ 38 коммутирует первый вход на потенциал установлен на третьей конт- выход, таким образом код 5 поступа- рольной шине блока 2 (на первых двух ет на вход функционального преобра- . контрольных шинах - низкий потенциал), зователя ФП1, вычисляющего величину При этом все ключи установлены так

10

Преобразователь 42 кода формирует код, дополняющий S до единицы, т.е. (1-). на выходе схемы 44 установится высокий потенциал, f5 переключающий ключ 38, и в этом случае код () поступает на вход преобразователя 40, на выходе которого будет кодТ(1-)(1-5) .

поступающие на вход сумматора 3. Так- С выхода преобразователя 40 код потовые импульсы регистров генераторов 20 ступает на вход умножителя 47, на 25 и 26 также соответствуют времен- второй вход которого подается значе- ным диаграммам фиг. ЗА.

Таким образом, в предложенном анализаторе блок тригонометрического умножения используется как для вычисления ДПФ сигнала, так и для синтеза тестового сигнала, необходимого для реализации алгоритма аддитивной итерационной коррекции погрешностей измерения параметров гармонических составляющих сигнала. На входы блока 7 измерения частоты последовательно поступают с выходов блока 6 вычисления модуля и фазы соответственно коды модулей компонентов ДПФ и соответствующих им номеров. По первому выходу блока 7 передается код частоты измеряемой гармоние ) с входа 15 блока 8. Результатом умножения будет значение ам плитуды гармоники А, поступающее на 25 вход 49 блока 8. .Для определения зна чения фазы гармоники с выхода ключа 38 подается код J, при5 „ 1/2 или (1-0) прио„ /2 на вход функционал ного преобразователя 41, вычисляющег

30

соответственно значение TTfi m или T(l-S), Преобразователь 43 кода формирует дополнительный код, в результате чего на вход сумматора 45 при

поступает код - ii , а при

35

о-.

На второй вхо

- код

сумматора 45 подается код РЬ(К „) +

jf,гЛЯ КС

II + г с выхода сумматора 46, причем

1Г значение - поступает с выхода схемы

НИКИ, а на втором его выходе устанавливается высокий потенциал (сигнал Q) при идентификации в блоке 7 локального максимума спектра модулей ДПФ, соответствующего измеряемой гармонике.

40 48 задания постоянного кода. На выходе сумматора 45 формируется значение фазы гармоники , поступакадее на выход 50 блока 8.

С началом этапа коррекции на кон- С началом этапа коррекции на кон- трольной шине блока 9 коррекции ус- трольной шине блока 9 коррекции уста- танавливается высокий потенциал, Б навливается высокий потенциал, в результате с первого выхода синхронирезультате с первого выхода синхронизатора 57 поступает сигнал на тактовый вход регистра 55 и в регистр

Зсчтора 57 поступает сигнал на такрезультате с первого выхода син низатора 57 поступает сигнал на товый вход регистра 55 и в реги

товый вход регистра 55 и в последний 55 заносится целая часть кода заносится целая часть кода А , т.е. из выражения

,.

На входы блока 8 подаются соответственно значения дробной части частоты гармоники „ , модуля компонента ДПФ, соответствующего локальному максимуму спектра Ь (К„о,кс) и фазы этого

55

1„. из выражения

,+ LОдновременно соответствующий нал подается на первые входы ко тирующих звеньев 51-53. В дальн шем работа блока 9 происходит п управлением синхронизатора 57 в ветствии с временными диаграмма

же компонента Ph(K

„„) . Ключ 28 управляется потенциалом с выхода пороговой схемы Д4. При 8,1/2 на выходе схемы, 44 установлен низкий потенциал, и

ключ 38 коммутирует первый вход на выход, таким образом код 5 поступа- ет на вход функционального преобра- зователя ФП1, вычисляющего величину

n,/

m Sin-;.

коммутирует таким образом ход функциона я ФП1, вычисл

С выхода преобразователя 40 код по0 ступает на вход умножителя 47, на второй вход которого подается значе-

ние ) с входа 15 блока 8. Результатом умножения будет значение амплитуды гармоники А, поступающее на 5 вход 49 блока 8. .Для определения значения фазы гармоники с выхода ключа 38 подается код J, при5 „ 1/2 или (1-0) прио„ /2 на вход функционального преобразователя 41, вычисляющего

0

соответственно значение TTfi m или T(l-S), Преобразователь 43 кода формирует дополнительный код, в результате чего на вход сумматора 45 при

поступает код - ii , а при

5

о-.

На второй вход

- код

сумматора 45 подается код РЬ(К „) +

jf,гЛЯ КС

II + г с выхода сумматора 46, причем

1Г значение - поступает с выхода схемы

С началом этапа коррекции на кон- трольной шине блока 9 коррекции ус- танавливается высокий потенциал, Б

результате с первого выхода синхронизатора 57 поступает сигнал на тактовый вход регистра 55 и в регистр

55 заносится целая часть кода

55 заносится целая часть кода

т.е.

1„. из выражения

,+ LОдновременно соответствующий сигнал подается на первые входы корректирующих звеньев 51-53. В дальнейшем работа блока 9 происходит под управлением синхронизатора 57 в соответствии с временными диаграммами

фиг, 7, На первом такте коррекции в регистры 68 корректирующих звеньев заносятся поступаюище из блока 10 начальные значения i, , А,,-, . При этом регистр 69 сброшен в О ,, ключ 64 коммутирует вход на второй выход и на выходе вычитателя 65 установлен код, равный нулю. Рассмотрим работу корректирующего звена 51, ц котором происходит коррекция параметра , В начале второго такта коррекции на вход схемы 54 сравнения поступают коды-FC) 5 соответствующие локальным максимума и спектра ДПФ, При совпадении целой части поступающего значения F(7iJ) с занесенным в регистр 55 кодом на выходе схе:мы 54 (фиг. 7А) появится сигнал Q, nocrynaiouflift на вход синхронизатора 57, При этом ключ 64 (фиг. 7А) переключается и код ,) поступает на вход вычислителя 55, на второй вход которого приходит код 71 j с выхода регистра 69, занесенный в первом такте коррекции. Код ( m) суммируется в сумматоре 66 с Л „ и с его выхода код-л , { „f ; - -F( :) заносится в регистр 69. После п тактов в регистре 69 форми;руется од

C« --F«).

Однако перед занесением его в регистр 69 схемь 67 сравнени51 сравнивает кодТ., , сформированный на выходе сумматора 66, с кодомft 5находящимся в регистре 69, Если разность кодов

I меньше заданного значения на выходе схемы 67 вырабатывается сигнал Н (фиг, 7, Н), поступаю1дий на вход элемента. И 56. При совпадении по времени сигналов Н, поступающих с выходов всех корректирующих звеньев на выходе элемента И 56 появляется сигнал S окончания коррекудии гармоники, который подается на вход синх- ронизатора 57 и на вторую контрольную шину выхода 19 блока 9 для перехода и коррекции следующей по порядку 1 армоники, при этом на третьей контрольной шине блока 9 устанавли- вается низкий потени.иап., ключи устанавливаются в начальное положение, регистры сбрасываются в т . Работа корректирующих звеньев 37 и 38 аналогична описанной для звена 36, Кор- ректируемые значения Т s еле каждого такта коррекции записываются в блок 10, для чего на первук, контрольную шину первого вькоцв бло

5 O 5 0 5

С

;

0 5 0 j7214

ка 9 подается соответствующий сигнал (фиг, 5 F). В блоке 10 регистров сдвига каждый из регистров 70-72 может содержать Р слов j РЬМ, где М - число гармоник в сигнале. При отсутствии на входах элемента ИЛИ 79 сиг- нгшов на его выходе установлен низкий потенциал, который поступает на управляющие входы ключей 76-78, коммутируя их первый вход с выхода. При этом потенциалы на выходах рег истров 70-72 подаются на их входы. При поступлении на тактовые входы регистров тактового импульса информация в них сдвигается на один разряд. После серии Р тактовых импульсов состояние регистров 70-72 равно исходномуj поскольку при данной коммутации ключей 76-78 данные с выходов регистров поступают на их входы. При поступлении сигналов Q на вход 24 блока 10 или сигналов W на первую контрольную шину ключи 76-78 коммутируют выходы с вторыми входами и на входы регистров 70-72 данные уже поступят не с их выходов, ,а с выходов ключей 73- 75, т.е. произойдет замещение прежних значений параметров новыми. В каждом КЗ регистров 70-72 помещаются М значений .соответствующих параметров , . этапе измерения начальных значений параметров, А, идентификации локального мак- . симума блоком 7 на зход 24 блока 10 поступает сигнал Q. S результате ключи 76-78 коммутируют вторые входы ключей 76-78 с их выходами и приходящий на третью контрольную шину синхронно с сигналом Q тактовый импульс записывает значения f, , А, 9 в крайние левые разряды регистров. После измерения значений параметров М гармоник в регистрах находится К/3 значений параметров, после чего число тактовых импульсов дополняется до Р, в конце этапа измерений и значения параметров первой гармоники |, А, , , устанавливаются на выходе блока 10.

На этапе синтеза входь регистров 70-72 сдвига через ключи 76-78 соединены с их выходами, Блок II управления вырабатьпзает серию из Р такто- мпульсов, поступающих по третьей контрольной шине блока 10 на тактовые входа) регистров 70-72, в результате чего на их выходах последовательно устанавливаются коды значений параметров М гармоник 1г , Р.,9„, ,2,..,М,

по которым в блоке 2 производится синтез тестового сигнала.

На этапе коррекции на выходах регистров 70-72 установлены коды значений параметров TiJ , А, гармони- ки, поступающие в блок 9 коррекции. После синтеза по этим значениям тестового сигнала и определения его параметров коды значений параметров тестового сигнала поступают на вто- рые входы ключей 76-78 одновременно с сигналом W, в результате чего они подаются на входы регистров 70-72 одновременно с первым импульсом серии Р, поступающей с третьей конт- рольной шины блока 10. При этом произойдет замещение значений °,. А, Р значениями F((, F(A), F((p°) параметров тестового сигнала, которые после серии Р тактовых импульсов ус- тановятся на выходах регистров 70- 72. В конце итерации эти значения параметров в свою очередь замещаются значениями , А , Р из блока 9.

После п итераций на выходах ре- гистров 70-72 установлены коды значений параметров-Л третью контрольную шину блока 10 при этом поступит тактовый импульс из блка 11 управления, вырабатываемый в блоке 11 по сигналу конца коррекции S, в результате чего коды значений А А, Р через ключи 76-78 поступают в ;файние левые разряды регистров 70-72, а на выходах этих регистров установятся коды 7i°, , A°,, параметров следующей по порядку гармоники, коррекция погрешностей значений параметров которой еще не производилась. Временные диаграммы, со- ответствующие приведенным сигналам, изображены на фиг. 9.

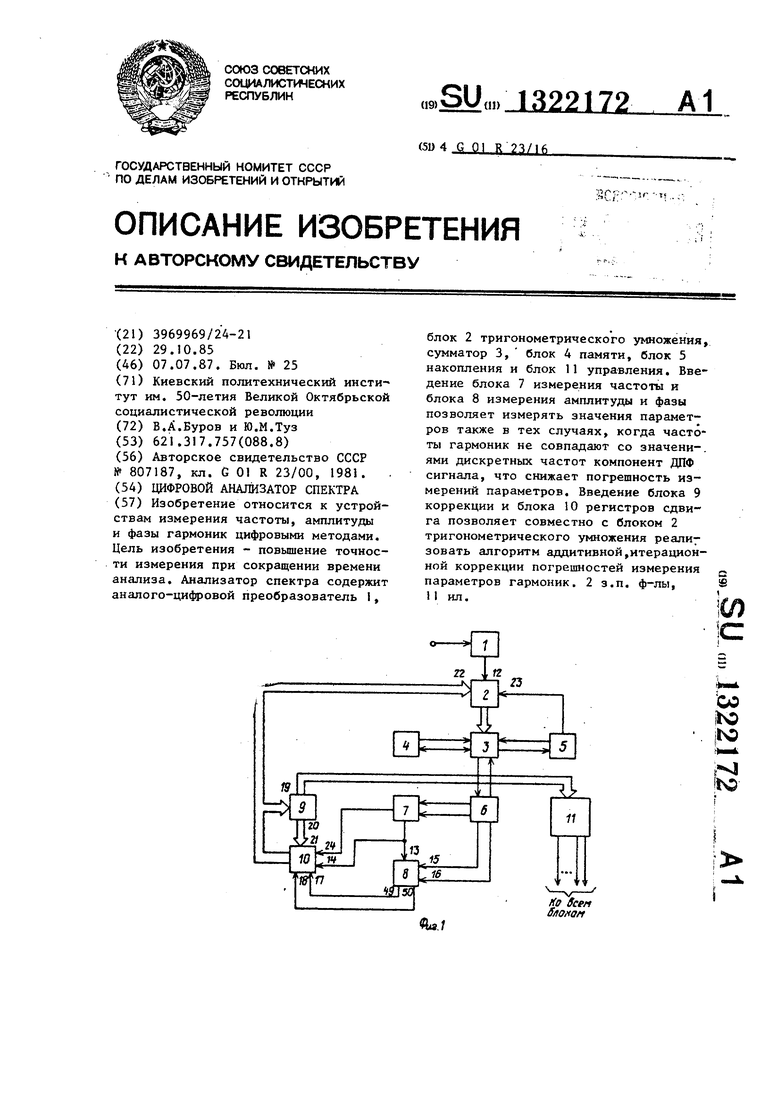

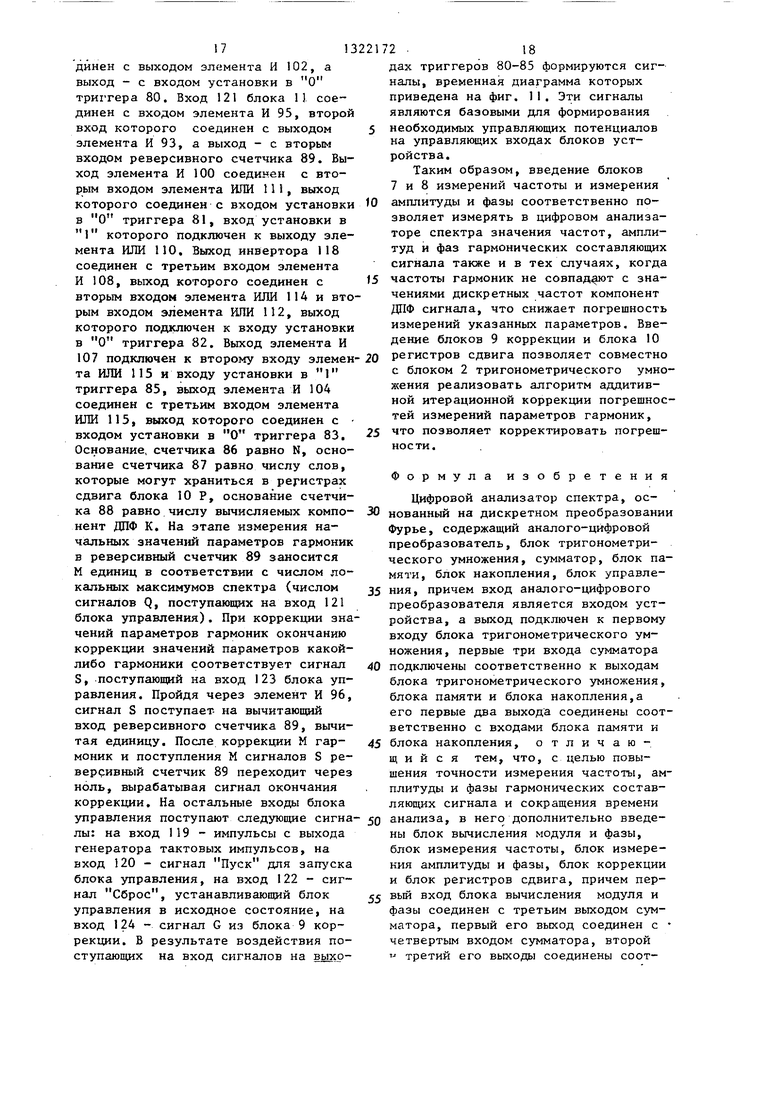

Потенциал на контрольных шинах блоков структурной схемы устройства (фиг. 1) устанавливается блоком 11 управления. Конкретная реализация блока управления может быть осуществлена в соответствии с функционально схемой, приведенной на фиг. 10. Блок 11 управления состоит из шести RS- триггеров 80-85, двоичных счетчиков 86-88, реверсивного счетчика 89, элементов И 90-108, элементов ИЛИ 109-116, инверторов 117-118, входов 119-124, являющихся входом блока 11 управления. Прямой выход триггера .80 соединен с входами элементов И 103, 105, 94 и 98, а его инвесрый выход - с входами элементов И 104,

93, 97 и 107. Выходы элементов И 97 и 98 ;соединены с входами элемента ИЛИ 109, выход которого подключен к входам элементов И 101 и 102, входу элемента ИЛИ 110 и входу установки в О триггера 85, прямой выход которого соединен с вторыми входами элементов И 93 и 94 и входом элемента И 92. Выход элемента И 90 соединен с входом счетчика 88, выход которого подключен к второму входу элемента И 97. Второй вход элемента И

98соединен с входом 124 блока II, вход 122 которого соединен с третьим входом элемента ИЛИ 109 и входами элементов ИЛИ 113, 112, 111 и 113. Вход 119 блока 11 соединен с входами элементов И 90, 91, 92, 99, 100

и 106 и вторыми входами элементов И 104 и 103, третьи входы которых соединены с вторым входом элемента И 100 и прямым выходом триггера 81, Выход элемента И 103 соединен с входом установки в 1 триггера 82. Выход элемента 114 соединен с входом установки в 1 триггера 83. Прямой выход триггера 83 соединен с вторым входом элемента И 105, входом элемента И 107 и вторым входом элемента И 90, выход которого соединен с входом счетчика 86, выход которого соединен с входом инвертора 118, вторым входом элемента И 107 и третьим входом элемента И 105, выход которого . соединен с входом установки в 1 триггера 84. Прямой выход триггера 84 соединен с вторыми входами элементов И 99 и 106, а выход элемента И

99соединен с вторым входом -элемента И 113, выход которого соединен с входом установки в О триггера 84. Прямой выход триггера 82 соединен с входом элемента И 108 и вторым входом элемента И 91, выход которого соединен с входом счетчика 87, выход которого соединен с вторым входом элемента И 105. Вход 123 блока 11 соединен с входом элемента И 96, второй вход которого соединен с выходом элемента И 94, а выход - с входом реверсивного счетчика 89, выход которого соединен с вторым входом элемента И 102 и входом инвертора 117, выход которого соединен с вторым входом элемента И 101, выход которого соединен с входом установки в 1 триггера 80. Вход 120 блока 11 соединен с вторым входом элемента ИЛИ ПО и входом элемента

ИЛИ 116, второй вход которого сое1713

дйнен с выходом элемента И 02, а выход - с входом установки в О триггера 80. Вход 121 блока 11 соединен с входом элемента И 95, второй вход которого соединен с выходом элемента И 93, а выход - с вторым входом реверсивного счетчика 89. Выход элемента И 100 соединен с вторым входом элемента ИЛИ 111, выход которого соединен с входом установки в О триггера 81, вход установки в 1 которого подключен к выходу элемента ИЛИ ПО. Выход инвертора 118 соединен с третьим входом элемента И 108, вьпсод которого соединен с вторым входом элемента ИЛИ 114 и вторым входом элемента ИЛИ 112, выход которого подключен к входу установки в О триггера 82. Выход элемента И 107 подключен к второму входу элемен та ИЛИ 115 и входу установки в 1 триггера 85, выход элемента И 104 соединен с третьим входом элемента ИЛИ 115, выход которого соединен с входом установки в О триггера 83. Основание, счетчика 86 равно N, основание счетчика 87 равно числу слов, которые могут храниться в регистрах сдвига блока 10 Р, основание счетчика 88 равно числу вычисляемых компо- нент ДПФ К. На этапе измерения начальных значений параметров гармоник в реверсивный счетчик 89 заносится М единиц в соответствии с числом локальных максимумов спектра (числом сигналов Q, поступающих на вход 121 блока управления). При коррекции значений параметров гармоник окончанию коррекции значений параметров какой- либо гармоники соответствует сигнал S, поступающий на вход 123 блока управления. Пройдя через элемент И 96, сигнал S поступает- на вычитающий вход реверсивного счетчика 89, вычитая единицу. После коррекции М гар- МОНИК и поступления М сигналов S реверсивный счетчик 89 переходит через ноль, вырабатывая сигнал окончания коррекции. На остальные входы блока управления поступают следующие сигна лы: на вход 119 - импульсы с выхода генератора тактовых импульсов, на вход 120 - сигнал Пуск для блока управления, на вход 122 - сигнал Сброс, устанавливающий блок управления в исходное состояние, на вход 124 - сигнал G из блока 9 коррекции. В результате воздействия поступающих на вход сигналов на выхо2 .18

дах триггеров 80-85 формируются сигналы, временная диаграмма которых приведена на фиг. 11. Эти сигналы являются базовыми для формирования

необходимых управляющих потенциалов на управляющих входах блоков устройства.

Таким образом, введение блоков 7 и 8 измерений частоты и измерения амплитуды и фазы соответственно позволяет измерять в цифровом анализаторе спектра значения частот, амплитуд и фаз гармонических составляющих сигнала также и в тех случаях, когда частоты гармоник не совпадет с значениями дискретных частот компонент ДПФ сигнала, что снижает погрешность измерений указанных параметров. Введение блоков 9 коррекции и блока 10 регистров сдвига позволяет совместно с блоком 2 тригонометрического умножения реализовать алгоритм аддитивной итерационной коррекции погрешностей измерений параметров гармоник, что позволяет корректировать погрешности.

Формула изобретения

Цифровой анализатор спектра, осованный на дискретном преобразовании урье, содержащий аналого-цифровой преобразователь, блок тригонометриеского умножения, сумматор, блок памяти, блок накопления, блок управления, причем вход аналого-цифрового преобразователя является входом устройства, а выход подключен к первому входу блока тригонометрического умножения, первые три входа сумматора подключены соответственно к выходам блока тригонометрического умножения, блока памяти и блока накопления,а его первые два выхода соединены соответственно с входами блока памяти и блока накопления, отличающийся тем, что, с целью повышения точности измерения частоты, амплитуды и фазы гармонических составляющих сигнала и сокращения времени анализа, в него дополнительно введены блок вычисления модуля и фазы, блок измерения частоты, блок измерения амплитуды и фазы, блок коррекции и блок регистров сдвига, причем первый вход блока вычисления модуля и фазы соединен с третьим выходом сумматора, первый его выход соединен с четвертым входом сумматора, второй третий его выходы соединены соот19.1

ветственно с первым и вторым входами блока измерения частоты, первый выход которого соединен с первыми входами блока измерения амплитуды и фазы и блока регистров сдвига, второй и третий входы блока измерения амплитуды и фазы подключены соответственно к четвертому и пятому выходам блока вычисления модуля и фазы, выходы блока измерения амплитуды и фазы соединены соответственно с вторым и третьим входом блока регистров сдвига, первый выход блока коррекции соединен с входом блока управления, а второй его выход соединен с четвер- тьтм входом блока регистров сдвига, выход KOTopoi o соединен с входом блока коррекции и вторым входом блока тригонометрического умножения, третий вход которого соединен с вторым выходом блока накопления, второй выход блока измерения частоты соединен с пятым входом блока регистров сдвига, а выходы блока управления соединены с управляющими входами всех блоков устройства,

2. Анализатор по п. 1, отличающийся тем, что блок коррекции состоит из трех кооректирую- щих звеньев, схемы сравнения, реги- стра, элемента И и синхронизатора, причем первый выход синхронизатора соединен с тактовым входом регистра и первыми входами корректирующих звеньев, первая шина входа блока коррекции соединена с вторым входом регистра, информационным входом первого корректирующего звена и первым входом схемы сравнения, а выход регистра соединен с вторым ее входом, выход схемы сравнения соединен с первым входом синхронизатора, второй выход которого соединен с вторыми входами корректирующих звеньев, а

0 5

0

7220

третий выход - с третьими входами корректирующих, звеньев и с первой контрольной шиной блока коррекции, вторая и третья шины входа блока коррекции соединены соответственно с информационными входами второго и третьего корректирующих звеньев, первые выходы всех корректирующих звеньев являются соответственно первой, второй и третьей шинами выхода блока коррекции, а их вторые выходы подключены к входам элемента И, выход которого соединен с вторым входом синхронизатора и с второй контрольной шиной блока коррекции, а третий вход синхронизатора соединен с третьей контрольной шиной блока коррекции,

3, Анализатор по пп. 1-2, отличающийся тем, что корректирующее звено состоит из ключа, вычи- тателя, сумматора, схемы сравнения и двух регистров, причем второй вход корректирующего звена подключен к управляющему входу ключа, выходы которого соответственно подключены к первому входу вычитателя и входу первого регистра, а вход ключа соединен с информационным входом корректирующего звена, первьш вход которого соединен с тактовым входом первого регистра, а третий вход - с тактовым входом второго регистра, выход которого соеди нен с первым входом схемы сравнения, и вторым входом вычитателя, выход которого подключен к первому входу сумматора, второй вход которого соединен с выходом первого регистра, а выход - с входом второго регистра и вторым входом схемы сравнения, выход второго регистра является первым выходом корректирующего звена, второй выход которого соединен с выходом схемы сравнения.

,,,::n

w I i

li

i

i Ml

шЗ

O«,j«,

Й L™J

l...-,.,

8

H J7 t™,™,

t:tf iir --- I i W

sF

fc J V- Ч

-,,,™. Ji. I

Й1/г

л

sF

j

йА / Ф Ifif/J

., ...x

я --I.-.

in

Lil

Л

Фиг. 5

Фиг.в

Фиг.9

113

iP

91

92

99

116т

И

SO

т 0121

092

122

05«

т

0П,-п гпИ5С

:итг 11

м

s-a

(hJ

g :з

т

12И 0-

97 s8

f

10

PU2 Ю

Составитель В.Смолин Редактор Л.Гратилло Техред Л.Олийнык

Заказ 2858/40

Тираж 730Подписное

БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Г.Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ преобразования перемещения в код | 1989 |

|

SU1686698A1 |

| Цифровой измеритель частоты и фазы гармонического сигнала | 1988 |

|

SU1626176A1 |

| Устройство для взвешивания движущихся объектов | 1990 |

|

SU1789877A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Устройство для измерения параметров трехфазной сети | 1985 |

|

SU1307396A1 |

| Измеритель сдвига фаз | 1986 |

|

SU1366966A1 |

| ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 2013 |

|

RU2541856C2 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1223248A1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБКИ ПРЕОБРАЗОВАТЕЛЕЙ УГЛА В КОД | 2020 |

|

RU2740511C1 |

Изобретение относится к устройствам измерения частоты, амплитуды и фазы гармоник цифровыми методами. Цель изобретения - повышение точности измерения при сокращении времени анализа. Анализатор спектра содержит аналого-цифровой преобразователь I, блок 2 тригонометрического умножения, сумматор 3, блок 4 памяти, блок 5 накопления и блок 11 управления. Введение блока 7 измерения частоты и блока 8 измерения амплитуды и фазы позволяет измерять значения параметров также в тех случаях, когда частоты гармоник не совпадают со значени-. ями дискретных частот компонент ДПФ сигнала, что снижает погрешность измерений параметров. Введение блока 9 коррекции и блока 10 регистров сдвига позволяет совместно с блоком 2 тригонометрического умножения реапи зовать алгоритм аддитивной,итерационной коррекции погрешностей измерения параметров гармоник. 2 з.п. ф-лы, 1 1 ил. с СО IND ю ы fto

| Устройство для определения фи-зичЕСКиХ СВОйСТВ ОбРАзцОВ гОРНыХпОРОд | 1978 |

|

SU807187A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-07-07—Публикация

1985-10-29—Подача